数字像素及其操作方法

1.优先权要求

2.本技术要求于2019年1月18日提交的题为“histogram

‑

assisted pixel(直方图辅助像素)”的第62/794,403号美国临时申请和于2019年2月1日提交的题为“digital pixel(数字像素)”的第62/800,050号美国临时申请的优先权,所述申请的全部内容和公开内容均通过引用并入本文。

技术领域

3.本发明涉及光探测与测距(lidar或lidar)系统,更具体地,涉及减少飞行时间lidar系统中的功耗的方法和装置。

背景技术:

4.基于飞行时间(tof)的成像用于多种应用,包括测距、深度剖析和3d成像(例如,光探测与测距(lidar))。直接飞行时间测量包括直接测量发射辐射和感测从物体或其他目标反射后的辐射之间的时间长度。由此,可以确定到目标的距离。在特定应用中,可以使用单光子探测器阵列(例如单光子雪崩二极管(spad)阵列)来感测反射的辐射。spad阵列可在需要高灵敏度和高时间分辨率的成像应用中用作固态探测器。

5.spad基于p

‑

n结器件,p

‑

n结器件偏置超出其击穿区域,例如,通过具有所需脉冲宽度的选通信号或响应于具有所需脉冲宽度的选通信号。高反向偏压产生足够大小的电场,使得引入器件的耗尽层的单个电荷载流子可以通过碰撞电离引起自持雪崩。雪崩由猝灭电路主动或被动猝灭,以允许器件“重置”以探测更多光子。起始电荷载流子可以通过单个入射光子撞击高场区而以光电方式产生。正是这一特性产生了“单光子雪崩二极管”这个名称。这种单光子探测运行模式通常被称为“盖革模式”。

6.为了对入射在spad阵列上的光子进行计数,某些tof像素方法可能使用数字计数器或模拟计数器。数字计数器可能更易于实现和扩展,但在面积方面可能很昂贵(例如,相对于阵列的物理尺寸)。模拟计数器可能更紧凑,但可能会受到有限的光子计数深度(位深度)、噪声和/或均匀性的影响。

7.为了给入射光子加上时间戳,某些基于spad阵列的tof像素方法已经使用了时间数字转换器(tdc)。tdc可用于tof成像应用中,以提高单个时钟周期的时间分辨率。这种数字方法的优点包括tdc的尺寸倾向于随技术节点而扩展,并且存储的值可以更稳健以防泄漏。

8.然而,tdc电路可能仅能够在单个测量周期中处理一个事件,因此,spad阵列可能需要多个tdc。tdc也可能非常耗电,使得更大的阵列更难以实现。tdc还可能产生大量数据,例如每个光子10

‑

16位时间戳。连接到tdc的单个spad可能每秒产生数百万个此类时间戳。因此,大于100000个像素的成像阵列可以产生不可行的大数据速率。

技术实现要素:

9.根据本公开的一些实施例,lidar测量电路包括:单光子探测器阵列,所述单光子探测器阵列被配置为响应于来自发射器的光信号发射而探测光子;以及像素处理电路,所述像素处理电路被配置为通过利用多个粗略直方图仓来计算入射到所述单光子探测器阵列上的光子的估计到达时间,其中所述多个粗略直方图仓中的各个粗略直方图仓与大于所述光信号的脉冲宽度的十六分之一的持续时间相关联。

10.在一些实施例中,发射器是激光器,并且多个粗略直方图仓中的各个粗略直方图仓的持续时间基于光信号的脉冲宽度。

11.在一些实施例中,多个粗略直方图仓中的各个粗略直方图仓的持续时间在大于或等于激光器的脉冲宽度的四分之一至小于或等于激光器的脉冲宽度之间。

12.在一些实施例中,像素处理电路还被配置为基于从单光子探测器阵列中的各个单光子探测器异步接收到的信号,利用边沿采样电路来计算探测到光子的单光子探测器阵列的数量,并根据时钟信号输出探测到光子的单光子探测器阵列的数量。

13.在一些实施例中,像素处理电路还被配置为基于质心计算来计算估计到达时间,并且其中,质心计算基于多个粗略直方图仓中的峰值直方图仓。

14.在一些实施例中,质心计算进一步基于多个粗略直方图仓中紧邻峰值直方图仓的相邻仓。

15.在一些实施例中,相邻仓是第一相邻仓,并且质心计算进一步基于多个粗略直方图仓中紧邻峰值直方图仓并且与第一相邻仓相对的第二相邻仓。

16.在一些实施例中,像素处理电路还被配置为探测所述粗略直方图仓的第一仓中的饱和并且响应于探测到饱和而阻止所述像素处理电路的操作。

17.在一些实施例中,像素处理电路还被配置为利用在50mhz至1ghz之间的时钟信号计算入射到所述单光子探测器阵列上的光子的所述估计到达时间。

18.在一些实施例中,时钟信号与发射器的脉冲频率同步。

19.在一些实施例中,像素处理电路还被配置为基于时钟信号确定用于访问多个粗略直方图仓中的各个粗略直方图仓的地址。

20.在一些实施例中,地址基于自所述光信号发射以来的时间量顺序地递增或递减。

21.在一些实施例中,多个粗略直方图仓存储在静态随机存取存储器(sram)中。

22.根据本公开的一些实施例,光探测与测距(lidar)测量电路包括:激活的探测器计数电路,所述激活的探测器计数电路耦接到多个探测器并被配置为输出在给定持续时间内探测到光子的所述多个探测器的数量的计数;加法器电路,所述加法器电路被配置为基于从所述激活的探测器计数电路输出的所述计数来更新多个粗略直方图仓中的一个粗略直方图仓;以及质心法(cmm)计算电路,所述cmm计算电路被配置为通过对所述多个粗略直方图仓的子集执行质心计算来计算入射到所述多个探测器上的光子的估计到达时间。

23.在一些实施例中,多个粗略直方图仓的子集包括峰值直方图仓,峰值直方图仓包含所述多个粗略直方图仓的最高计数。

24.在一些实施例中,多个粗略直方图仓的子集还包括多个粗略直方图仓中紧邻峰值直方图仓的相邻仓。

25.在一些实施例中,所述多个探测器被配置为响应于从发射器发射的光信号而探测

光子,并且多个粗略直方图仓中的各个粗略直方图仓与大于光信号脉冲宽度的十六分之一的持续时间相关联。

26.在一些实施例中,加法器电路还被配置为响应于在所述多个粗略直方图仓的第一仓中的饱和的探测而生成饱和探测信号。

27.在一些实施例中,激活的探测器计数电路还被配置为根据时钟信号,利用边沿采样电路输出探测到光子的所述探测器的数量。

28.在一些实施例中,cmm计算电路被配置为计算在所述时钟信号的周期期间入射到所述多个探测器上的光子的所述估计到达时间。

29.在一些实施例中,加法器电路还被配置为基于时钟信号确定用于访问所述粗略直方图仓的地址。

30.根据本公开的一些实施例,一种用于操作光探测与测距(lidar)测量电路的方法,包括:通过单光子探测器阵列探测与来自发射器的光信号发射相关联的光子;以及利用多个粗略直方图仓计算入射到所述单光子探测器阵列上的光子的估计到达时间,其中,所述粗略直方图仓中的各个粗略直方图仓与大于所述光信号的脉冲宽度的十六分之一的持续时间相关联。

31.在一些实施例中,该方法还包括:基于从单光子探测器阵列中的各个单光子探测器异步接收到的信号,计算探测到光子的单光子探测器阵列的数量;以及根据时钟信号同步输出探测到光子的单光子探测器阵列的数量。

32.在一些实施例中,该方法还包括基于质心计算来计算估计到达时间,所述质心计算基于所述多个粗略直方图仓中的峰值直方图仓。

33.在一些实施例中,该方法还包括:探测所述粗略直方图仓的第一仓中的饱和,以及响应于探测到所述饱和而阻止lidar测量电路的操作。

34.在一些实施例中,该方法还包括基于时钟信号确定用于访问多个粗略直方图仓中各个粗略直方图仓的地址。

附图说明

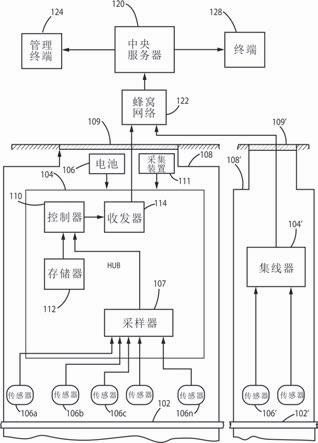

35.图1示出了根据本文描述的一些实施例的lidar应用中的tof测量系统或电路的组件。

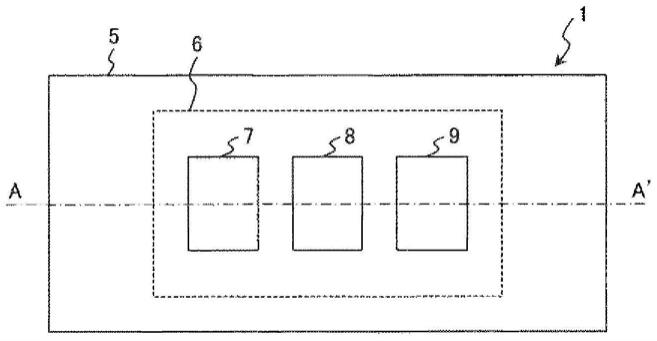

36.图2示出了根据本文描述的一些实施例的用于在数字像素内执行用于cmm计算的粗略直方图的系统和方法的框图。

37.图3示出了根据本文描述的一些实施例的用于使用粗略直方图来提供cmm操作的电路操作的示例流程图。

38.图4示出了根据本文描述的实施例的示例像素处理电路。

39.图5和图6示出了根据本文描述的一些实施例的可能用于图4的像素电路的spad接口电路。

40.图7示出了根据本文描述的一些实施例的边沿采样电路的示例的示意图。

41.图8示出了可能根据本文描述的一些实施例使用的示例并行计数器/求和器。

42.图9示出了可能根据本文描述的一些实施例使用的在sram存储体中提供仓的示例存储器。

43.图10示出了根据本文描述的一些实施例的用于冻结像素操作的电路配置和电路操作的示例的框图。

44.图11示出了根据本文描述的一些实施例的响应于探测器未探测到光子而将时钟信号选通到直方图的电路配置和电路操作的示例的框图。

45.图12a示出了根据本文描述的一些实施例的激光返回完全到达粗略直方图中给定仓内的情形的示意图。

46.图12b示出了根据本文描述的一些实施例的其中激光返回到达粗略直方图中的两个仓之间的情形的示意图。

47.图13示意性地示出了根据本文描述的一些实施例的基于tdc的直方图和粗略直方图的使用的示例比较。

48.图14以图形方式示出了根据本文描述的一些实施例的直方图辅助的质心计算。

49.图15示出了根据本文描述的一些实施例的用于略微变化的激光脉冲返回的直方图仓的附加示例。

具体实施方式

50.现在将在下文中参考附图更全面地描述本发明,其中示出了本发明的示例性实施例。在附图中,为了清楚起见,可能会夸大了区域或特征的相对尺寸。然而,本发明可能以许多不同的形式体现并且不应被解释为限于本文阐述的实施例;相反,提供这些实施例是为了使本公开彻底和完整,并将向本领域技术人员充分传达本发明的范围。

51.某些利用大量像素的常规tof系统可能产生大数据速率。数据速率可以通过直方图时间戳来压缩。直方图时间戳可以包括基于到达时间对“仓”内到达光子的计数进行分组。例如,可以生成的直方图数据储存库包括与持续时间或“窗口”相关联的各个仓。然而,这可能涉及大量的内存资源,而这些内存资源在典型的tof lidar可能使用效率不高。例如,直方图仓的存储深度通常由峰值到达窗口中可能出现的最大激光返回设置,而实际上,许多或大多数直方图仓将被稀疏地占用(例如,仅被背景噪声占用)。此外,传统上,通常会使用数千个时间仓来形成直方图,该直方图足以覆盖具有典型tdc分辨率(例如,50

‑

100ps)的lidar系统的典型时间范围(例如,微秒)。

52.质心法(cmm)tof像素由henderson等人在2019年11月19日提交的题为“数字像素”的第16/688,043号美国专利申请中进行了描述,其全部内容通过引用并入本文。cmm可配置为计算信号光子在相关窗口上的到达时间(toas)分布的质心,其可用于估计到目标的tof(从而估计距离)。

53.tof测量装置,包括那些结合了cmm运算的装置,可能会遇到许多挑战。例如,如果目标是中间选通窗口(例如,位于相应距离子范围的中间)和/或在更长的范围内(例如,使得相关光子计数的数量可能不容易测试并与背景选通窗口(例如被配置为主要捕获背景信号的选通窗口)进行比较,以确定是否存在信号),则测量可能被迫执行诸如抖动激光脉冲和读出另一组图像等操作。抖动可以包括将激光脉冲相对于选通窗口以在每个激光周期随机选择的时间段进行时间偏移。这些附加操作可能会增加装置的i/o速率和/或功耗,并且可能会减少有用的选通窗口的时间。

54.本公开的一些实施例涉及使用数字信号处理用于基于cmm的直接tof运算的单光

子探测器阵列,在本文中也称为“数字像素”或“cmm像素”。如本文所述的cmm像素可能被配置为在不使用tdc的情况下对入射光子进行计数,并且因此可以以比某些方法更少的计算密集和/或功率密集的方式在像素中集成许多时间戳。

55.图1示出了根据本文描述的一些实施例的lidar应用中的tof测量系统或电路100的组件。电路100可以包括数字信号处理器(dsp)110、控制照明源125的定时的定时发生器120和单光子探测器阵列(举例说明为spad阵列105,尽管本发明的实施例不限于此)。照明源125(例如,发射器阵列)在由定时发生器120控制的时间发射辐射脉冲130。辐射135从目标(举例说明为物体140)反射回来,并且被spad阵列105感测。在一些实施例中,诸如微控制器或微处理器的控制电路可以被配置为向spad阵列105提供信号(例如,选通信号)以启用/禁用阵列的一个或更多个元件(例如,单个spad探测器)以便探测来自目标物体140的反射辐射135。

56.dsp 110可以实施为cmm像素处理器,其测量照明脉冲130、135在从照明器125到物体140并返回spad阵列105的行程中的飞行时间(tof)。更具体地,dsp 110的cmm像素处理器计算在许多(例如,数百或数千)激光脉冲130和光子返回135上聚合的平均tof的估计。

57.在一些实施例中,发射器阵列中的每个发射器元件连接到驱动器电路并由其控制。在其他实施例中,发射器阵列中的各个发射器元件组(例如,空间上彼此接近的发射器元件)可以连接到驱动器电路。驱动器电路或电路系统可以包括一个或更多个驱动器晶体管,其被配置为控制光发射信号的时序和幅度。定时电路同样可以控制探测器阵列的时序和增益/灵敏度。来自一个或更多个发射器的光发射照射在一个或更多个目标上并被一个或更多个目标反射,并且反射光被一个或更多个探测器(例如,通过一个或更多个透镜)探测为光信号,转换为电信号表示,并经过处理(例如,基于飞行时间)以定义视场的3d点云表示。根据本文描述的本发明实施例的lidar系统的操作可以由一个或更多个处理器或一个或更多个控制电路执行,例如图1中所示的dsp 110。

58.dsp 110可被配置为通过实施根据本文描述的实施例的一个或更多个加法器电路来对反射辐射135中的入射光子进行计数。更具体地,加法器可以被配置为响应于spad阵列105上的入射光子而对从spad阵列105接收的输入进行求和。例如,加法器可以被配置为基于在每个选通间隔或部分激光周期触发的spad数量(而不是通过平均在激光周期内触发spad的时间,这将利用时间数字转换)计算在一个激光周期内探测到的入射光子的“滚动”质心。dsp 110(或其他数字实现方式)的使用可以足够小以允许三维堆叠实现,阵列105“堆叠”在尺寸适合阵列105的区域或覆盖区的dsp 110的顶部。

59.在本文所述的实施例中,探测器选通间隔(或选通窗口)可以指在发射器脉冲之间的时间段或时间内,一个或更多个探测器(例如,响应来自控制电路的相应选通信号)的激活和去激活的相应持续时间(其同样可以响应于来自控制电路的各个发射器控制信号)。脉冲之间的时间(其定义了激光周期,或更普遍地定义了发射器脉冲频率)可以被选择或者可以对应于lidar系统的期望成像距离范围。每个选通窗口可以相对于发射器脉冲不同地延迟,并且因此可以对应于距离范围的相应部分或子范围。每个选通窗口也可以对应于图像帧的相应图像采集子帧。即,每个图像帧可以包括多个子帧,其中每个子帧在时间段内采样或收集各个选通窗口的数据,每个选通窗口覆盖或对应于lidar系统的距离范围的各个距离子范围。如本文所述的距离测量和选通窗口子范围的对应基于发射脉冲的飞行时间。一

些传统的选通技术(例如,如banks等人在公开号为2017/0248796,题为“3d imaging system and method(3d成像系统和方法)”的美国专利申请所述)可以基于接收回波的选通窗口来测量距离。

60.一些堆叠像素可以被配置成为像素内数字电路提供更多区域。该额外区域可用于将cmm测量中使用的数字触发器(dff)重新配置为粗略直方图,该粗略直方图可用于在远距离更稳健地识别背景和信号选通窗口。在一些实施例中,可以在峰值仓上计算cmm以保持低i/o速率。如本文所用,“峰值仓”是指直方图中与直方图的其他仓相比已探测到最大数量的光子的仓。

61.图2示出了根据本文描述的一些实施例的用于在数字像素内执行用于cmm计算的粗略直方图的系统和方法的框图。参考图2,该方法可以包括被配置为探测入射光子的多个spad 210(例如,诸如图1中所示的那些探测器元件)。该系统可以包括系统时钟clock和系统时钟驱动的采样电路220,系统时钟驱动的采样电路220可以对给定时钟周期内发射的spad 210的数量进行采样。在时钟周期期间已发射的spad 210的数量的采样可提供该时间间隔期间光强度的度量。在一些实施例中,采样仅发生在或主要发生在感兴趣的选通窗口(例如,由选通信号strobe控制)内。采样电路220的输出可以被输入到激活的spad计数器电路280,激活的spad计数器电路280可以收集在特定周期期间已经被激活的那些探测器的计数。该计数可以作为输入提供给加法器电路240。

62.可以提供包括多个直方图仓230的直方图,例如可以在存储器中。从目标物体反射的辐射入射到探测器上的探测到的光子“计数”可以存储在直方图仓230中。在一些实施例中,直方图的各个直方图仓230中的每一个可以与不同的持续时间相关联,该不同的持续时间与特定选通窗口期间的lidar发射器的光发射相关联。例如,直方图仓230中的不同直方图仓可以与自光发射以来已经消逝的不同持续时间相关联。因此,直方图仓230中的不同直方图仓可以与选通窗口的距离子范围内的目标物体的不同可能距离相关联。例如,在2019年8月15日公布的题为“methods and systems for high

‑

resolution long

‑

range flash lidar(高分辨率远程闪光探测与测距的方法和系统)”、公开号为2019/0250257的美国专利申请中讨论了基于直方图探测目标距离的方法的示例,其内容以引用方式并入本文。一个称为读

‑

修改

‑

写的过程:加法器电路240可以从与选通窗口相关联的直方图仓230中读取已经存储的计数,将来自激活的spad计数器电路280的新采样的计数添加到已经存储的计数,并且将总和写回直方图仓230。

63.可以在感兴趣的选通周期内(基于选通信号strobe)由系统时钟clock驱动的地址来循环(例如,顺序地)通过直方图仓230。即,在一些实施例中,可以根据自发射器脉冲的发射起已经消逝的持续时间来确定放置有计数的直方图仓230的地址。结果,不必确定直方图仓230所在的地址,可以基于例如clock信号和/或strobe信号自动确定该地址。直方图仓230所在的地址可以基于自发射器脉冲被发射起的时间量自动地(例如,单调地和/或顺序地)例如在存储器中递增或递减。例如,在发射器脉冲发射之后的第一持续时间期间,lidar系统可以被配置为通过读取

‑

修改

‑

写入操作将探测到的光子的计数存储存储器位置中,存储器位置被指定为存储与第一直方图仓230(例如仓1)相关联的光子计数。在与仓1相关联的时间段消逝之后,存储光子计数的地址可以自动顺序地前进,例如,指向指定用于存储与第二直方图仓230(例如仓2)相关联的光子计数的存储器位置。光子计数将被存储的位置可

以基于clock信号和/或strobe信号继续递增(例如,指向仓3、仓4等)。以此方式,根据本发明的实施例操作的像素可以更有效地写入和/或写入直方图仓230。

64.对粗略直方图数据250,可以完全读出直方图和/或可以执行cmm计算260。在一些实施例中,当发现饱和时,饱和探测电路270可以冻结像素操作以节约功率。如本文所用的,饱和事件是指探测到的光子的“计数”超过特定仓的最大可用存储容量的情况。例如,如果直方图仓230配置有三位存储,则仓只能保持探测到的光子的计数为七(例如,0

‑

7)。因此,一旦探测到七个光子,给定的仓就饱和了。饱和探测电路270也可用作事件驱动读数。

65.图3示出了根据本文描述的一些实施例的用于使用粗略直方图来提供cmm操作的电路操作的示例流程图。图4示出了根据本文描述的实施例的像素处理电路400。在一些实施例中,像素处理电路400可以是cmm像素处理电路400或包括cmm像素处理电路400。示例像素处理电路400可以被配置为实现图3所示的一个或更多个操作。在一些实施例中,像素处理电路400可以由dsp实现。示例像素处理电路400被示为spad cmm像素处理器,其从n个spad的阵列接收输入,但是在不偏离本发明的情况下可以使用其他单光子探测器阵列。

66.参照图3和图4,根据本文描述的实施例的像素处理操作的操作可以包括在选通窗口期间启用像素310,例如由选通信号strobe<i>控制。在一些实施例中,像素可以是一个或更多个spad或包括一个或更多个spad。像素处理电路400可以包括使用时钟信号,例如全局时钟gclk和内部时钟fastclk。在一些实施例中,fastclk可以是全局时钟gclk的本地门控形式,其从子帧的开始直到探测到峰值一直有效,在探测到峰值时,fastclk被禁止。在一些实施例中,fastclk可能仅在选通窗口期间有效(如图4的像素处理电路400中的逻辑所示)。

67.图5和图6示出了根据本文描述的一些实施例的可能用于图4的像素电路的spad接口电路500、600。可以将spad接口电路500、600并入作为在n阱中实施的衬底隔离的spad。在一些实施例中,可能包括在spad上实施主动抑制的能力。

68.再次参考图3,一些数量(例如n个)的探测器(例如spad)可以被一些数量(例如m个)的像素激活320。例如,可以利用一个或更多个边沿采样电路来探测激活的spad的数量。来自n个探测器的输出可以被采样并且与时钟信号(例如,fastclk)对齐330。可以在时钟信号的时钟周期内对探测器探测到的光子数量进行计数340。在一些实施例中,时钟信号可以设置直方图仓的宽度(例如,就直方图仓所覆盖的时间量而言)。在一些实施例中,可以通过使用边沿采样电路(本文也称为边沿探测器)和计数电路来对探测器探测到的光子的数量进行计数。图4图示了提供信号corrq<log2(n)

‑

1:0>作为输出的边沿采样电路。在一些实施例中,信号corrq<log2(n)

‑

1:0>可以提供哪些探测器已探测到像素的按位指示。

69.图7示出了根据本文描述的一些实施例的边沿采样电路700的示例的示意图。示例边沿采样电路700可以确定是否在时钟周期(例如,fastclk或gclk)内出现指示探测到光子的至少一个spad上升沿(例如,图4中的spad<i>)。相关器可以包括来自并行计数器的输出,该并行计数器可以确定在最后一个时钟周期期间发射(例如,探测到光子)的探测器(例如,spad)的总数。使用并行计数器可以通过不激活直方图存储(例如,sram)的读

‑

修改

‑

写周期来节约功率,除非要集成非零数字。如果在时钟周期内出现上升沿,则输出corrq可能会在一个时钟周期内保持高电平。如果这不是真的(即,至少没有出现一个相关器上升沿),那么输出corrq可能会在一个时钟周期内保持低电平。此操作可用于将像素处理从异步域转换为同步边沿采样域。这可以避免例如相关器纹波计数器和时间加法器中的逻辑稳定问题。

在一些实施例中,同步边沿采样域可以与时钟信号(例如,fastclk或gclk)同步,其可以与发射器的脉冲频率同步。

70.图8示出了可能根据本文描述的一些实施例使用的示例并行计数器/求和器800。例如,在swartzlander,jr.,“parallel counters(并行计数器)”,ieee transactions on computers,vol c

‑

22,1973,pp.1021

‑

1024中描述了图8的示例并行计数器/求和器800。图8中所示的逻辑可用于15个输入(例如spad)示例。在利用2x2 spad配置的实施例中,并行计数器/求和器800对于四个输入可以仅使用2个半加器(ha)和2个全加器(fa)。图8中所示的swartzlander方法是完全并行的,但具有稳定速度限制,这可以通过以额外触发器为代价的流水线加法器树来解决。e.fisher、i.underwood和r.henderson在于2013年7月在《ieee journal ofsolid

‑

state circuits(ieee固态电路杂志)》第48卷,第7期,第1638

‑

1650页的“a reconfigurable single

‑

photon

‑

counting integrating receiver for optical communications(用于光通信的可重构单光子计数集成接收器)”中讨论了流水线加法器树的一个例子。在一些实施例中,并行计数器/求和器800可以替换为对同步探测器(例如,spad)输出执行逻辑或操作的电路配置。这种配置可能更容易实现,但在某些情况下可能不太有效,例如在高光级环境中。并行计数器的输出可以是在与相应直方图仓相关联的持续时间期间探测到像素的探测器(例如spad)的数量。该计数在图4中被图示为s<log2(l)

‑

1:0>,其中l是直方图仓的数量。

71.再次参考图3,时钟周期可以建立直方图的给定仓的宽度(例如,持续时间)。在时钟周期内探测到光子的探测器计数(例如,s<log2(l)

‑

1:0>)可以通过读

‑

修改

‑

写操作被添加到特定直方图仓中的当前计数(例如,ha<k

‑

1:0>,其中k是每个仓的位数)中350,其中由时钟周期索引的给定直方图仓的当前内容被读出并添加到该仓的确定的像素计数中。然后结果(例如,r<k

‑

1:0>)可以写回到相应的直方图仓。在感兴趣的选通周期内,可以按照由系统时钟驱动的地址来循环通过仓。在一些实施例中,随着选通窗口前进,直方图仓(例如,哪个仓与给定选通窗口相关联,在图4中图示为haddr<log2(l)

‑

1:0)的给定地址也前进,这样被分析/更新的直方图仓随着时钟的增加而增加。在一些实施例中,直方图可以存储在存储器中,例如静态随机存取存储器(sram)。图9示出了可能根据本文描述的一些实施例使用的在sram存储体中提供仓的示例存储器900。

72.在可选操作360中,当探测到饱和事件(例如,satdet)时,饱和探测电路可以冻结像素处理电路的操作。冻结像素的操作可以包括在不提供控制信号的情况下维持像素的状态以探测更多光子和/或阻止与像素相关联的toa值的进一步计算。冻结也可能意味着对上述spad接口电路的门输入取消置位以抑制spad的盖革(geiger)模式脉冲。该操作可以通过防止spad阳极切换(大电容)以及进一步防止像素中可能消耗功率的任何下游开关活动来节约功率。冻结也可以通过将全局时钟门控到像素来防止与像素中的时钟电路相关联的开关活动来实现。冻结像素的操作可以节约功率和/或避免数据损坏。

73.图10示出了根据本文描述的一些实施例的用于冻结像素操作的电路配置和电路操作的示例的框图。如图10所示,当探测到饱和事件(例如,satdet)时,spad和时钟生成(例如,fastclk)都可以被门控。在一些实施例中,算术逻辑单元(alu)(例如对直方图仓执行计数操作的alu)的进位,可以用作饱和探测信号。饱和探测可通过探测fa的进位已切换为高电平来实现,指示某个仓已超过2

k

‑

1(其中k是仓中的sram位数)。在一些实施例中,将不会

超过该值,因为像素在探测到饱和时立即冻结,并且像素在读出之前将处于非活动状态,从而在探测到饱和的时间点冻结局部直方图的状态。可能已经探测到的其他光子事件可以从此时(例如,当操作被门控时)被丢弃,直到像素被重置时的下一个子帧的开始。

74.在一些实施例中,响应于探测器(例如spad)没有探测到光子,可以对直方图(例如,直方图sram)的时钟信号进行门控。该操作的示例在图11中示出。图11所示的实施例可以避免与对直方图仓的访问相关联的读

‑

修改

‑

写操作。结果,可以避免sram位线的充电/放电和/或sram写入驱动器的激活或读取比较器的激活。这可能导致显著的功率节约,尤其是在低背景情况下,因为由于位线和地址线电容很大,sram的读/写功率可能相当大。在本实施例中可以继续其他操作,例如spad采样以生成corrq。

75.再次参考图3,在操作370中,可以执行数据读出,这可以提供来自生成的直方图的信息。然后可以基于存储的直方图信息、饱和仓计数以及在一些实施例中下一个或多个最高仓的计数来执行cmm操作380以解析飞行时间测量。

76.如本文所述的实施例可以提供用于为像素生成cmm计算作为计算具有多个优点的飞行时间测量的一部分的机制。例如,本文所述的操作可以利用由具有等于激光器(例如,垂直腔表面发射激光器(vcsel))脉冲宽度(pw)(例如,在一些实施例中为2

‑

10ns)的周期的时钟信号定义的仓大小(例如,tdc分辨率)。在这方面,“仓大小”是指由特定仓表示的选通窗口内的持续时间。例如,如果一个特定的选通窗口覆盖100ns并且有25个仓,则每个仓将代表4ns。

77.如上所述,在一些实施例中,仓大小可以等于发射器(例如激光器)脉冲宽度(例如,半峰全宽,fwhm),但本发明不限于此。在一些实施例中,仓大小可以是脉冲宽度的一部分,例如发射器脉冲宽度的二分之一、四分之一、八分之一或十六分之一。与典型的tdc操作相比,这种较低的分辨率可能会降低对时钟的高速要求,因为不需要更高级别的分辨率。例如,可以使用全局100mhz时钟频率,这与传统的高分辨率tdc频率相反,传统的高分辨率tdc频率可以使用/包含数ghz量级的环形振荡器。100mhz的时钟频率只是一个例子,也可以使用其他时钟频率,例如50mhz到300mhz之间的时钟频率。在一些实施例中,时钟频率可以高达1ghz。与传统方法相比,使用较低速度的时钟可能有利于功耗。在一些实施例中,可能不需要像素级定时生成。在一些实施例中,如果需要更短的距离范围和/或更高的范围分辨率(例如,大约几米),则可以将本文描述的实施例与本地时钟源组合以提供附加功能。

78.如本文所用的,“粗略”直方图可指其中与直方图的各个仓相关联的分辨率和/或持续时间(也称为“仓宽度”)更大(例如,覆盖持续时间大于)大于lidar系统使用的发射器的光信号脉冲宽度的十六分之一的直方图。在一些实施例中,仓宽可以等于发射器的光信号脉冲宽度。在一些实施例中,仓宽可以大于发射器的光信号脉冲宽度的二分之一。在一些实施例中,仓宽可以大于发射器的光信号脉冲宽度的四分之一或八分之一。

79.尽管具有较小粒度的仓宽,仍然可以以足够的准确度执行光子的到达时间的计算。例如,图12a示出了根据本文描述的一些实施例的激光返回1210a完全到达粗略直方图中给定仓内的情形的示意图。如图12a所示,如果激光返回1210a完全落在一个仓1220a内,则到达时间被估计为在仓中心,并且可以基于仓的时序特征被发现(例如,基于时钟信号的仓地址)。

80.图12b示出了根据本文描述的一些实施例的其中激光返回到达粗略直方图中的两

个仓之间的情形的示意图。如图12b所示,如果激光返回1210b落在两个仓1220b、1230b之间,则它们之间的计数比(例如,与每个仓相关联的像素计数)可以确定toa。因此,具有等于或小于激光器的脉冲宽度但大于激光器的脉冲宽度的十六分之一的仓宽(例如,仓被收集/采样的持续时间)足以用于toa计算。

81.此外,如本文所述的实施例提供的改进在于组合了选通窗口和粗略直方图的操作。在一些实施例中,选通窗口可以确定粗略直方图仓的宽度和/或spad被采样的间隔。选通窗口的使用不仅可以拒绝背景事件,还可以限制需要直方图化的时间段。这可能导致用于直方图生成的像素内资源和用于操作的结果数据速率的显着减少。此外,选通窗口还可允许在阵列区域而非整个阵列上操作时钟驱动直方图,从而节约功率。例如,在一些实施例中,可以在更宽的角度(例如,30到120度)使用和/或处理较低的距离范围,因此可以使用局部选通信号来抑制和/或减少阵列的该区域中的直方图像素,而中心区域(例如30度)中的像素继续在较长的距离范围内工作。在一些实施例中,仅在较低距离范围内进行处理可能意味着时钟驱动直方图不会在与较远距离相关联的那些持续时间(例如,自发射器发射后的持续时间)内进行操作。

82.在一些实施例中,cmm的计算可以包括完整直方图的读出。在一些实施例中,toa计算可以对感兴趣的仓执行cmm计算。例如,一些实施例可以使用2仓cmm算法。可以识别峰值仓,并且可以仅在峰值仓及其紧邻(左或右)邻居上执行cmm计算,以像素计数最高者为准。相对于其他cmm方法,此操作可能会产生非常准确的toa计算。在一些实施例中,可以仅使用峰值仓来执行进一步的背景抑制。在一些实施例中,片上dsp可以基于计算的cmm执行计算toa的全部任务并且发送最终的经过cmm计算的toa用于读出,这可以降低到外部实体的数据速率。

83.尽管本文讨论的2仓cmm算法方法使用峰值仓和一个相邻的相邻仓,但是本发明构思不限于此。在一些实施例中,在计算cmm操作时,额外的仓可以包含在峰值仓中。例如,对于某些激光脉冲,cmm操作可能会使用与峰值仓(例如,在峰值仓的两侧)紧邻的两个仓(例如,没有方形顶部轮廓的激光脉冲,或者激光脉冲宽度不是一个直方图仓宽,这样来自激光脉冲的能量将落入两个相邻的仓中)。在不背离本文描述的发明概念下,本领域的普通技术人员将理解包括附加仓的其他变化。

84.图13示意性地示出了根据本文描述的一些实施例的基于tdc的直方图和粗略直方图的使用的示例比较。图13图示了lidar系统的发射器的不同配置的结果。

85.参考图13,第一组三个模拟(左侧)示出了使用时间相关单光子计数(tcspc)的具有高时间分辨率(100ps)的基于tdc的lidar系统。模拟显示,对于192m范围内的目标,单个选通子帧从190m延伸到200m,背景(bg)水平从0到100klux不等。

86.在类似条件下提供第二组三个模拟(右侧),但根据本文描述的一些实施例,粗略直方图仓为每个10ns(选择为等于激光器的脉冲宽度)。图13所示的实验结果表明,使用基于粗略直方图的cmm方法可以提供与更细粒度模型同等的精度,同时仍然保持距离计算的可接受值。

87.根据本文描述的实施例的峰值探测算法的使用提供了额外的好处。如本文所讨论的,在一些实施例中,可以在像素中设置阈值,使得如果任何直方图仓达到该阈值(例如,达到饱和),则可以冻结像素以节约功率。本文描述的实施例提供了使用alu进位的简单饱和

探测实现。因此,实现该功能可能不需要更复杂的解码器。该饱和探测操作还可用于依赖于范围的帧速率传感器架构,其中饱和探测标志可用于驱动读出操作。

88.本文描述的实施例还提供了一种有益的spad组合电路,其不需要诸如可在常规装置中使用的or或xor树。相反,可以使用边沿探测电路和并行计数器电路来确定在直方图仓内(例如,具有时钟周期)发生的探测器(例如,spad)事件的数量。

89.在本文所述的实施例中,通过在像素中使用sram单元来进一步减小像素区域。这可能包含与采样时钟同步的精细时序。本文描述的实施例可以采用滚动的sram读

‑

修改

‑

写序列,允许在每个时钟周期从多个探测到的事件构建直方图。

90.图14以图形方式示出了根据本文描述的一些实施例的直方图辅助的质心计算。如图14所示,可以在给定的持续时间内提供一系列选通信号(例如,对应于选通窗口)。在每个选通窗口期间,一定程度的背景噪声可能会反映在像素上。在一个选通窗口(例如,选通#11)期间,探测到激光返回。如图14所示,更细粒度的常规tdc方法(由“精细直方图”表示)可以报告采样周期内的多个变化峰值。相比之下,在粗略直方图实现中(由“粗略直方图”表示),可以使用较少数量的直方图仓(例如,在10到25之间),并且激光脉冲返回可能会在直方图中的一个中产生一个峰值仓(例如,直方图仓4)。

91.在本文描述的实施例的一些示例中,可以确定峰值仓,并且也可以确定峰值直方图仓(例如,直方图仓3)的最大相邻直方图仓以用于质心计算。作为本文描述的实施例的一个例子,然后可以计算质心cm为:

[0092][0093]

其中h(bp)是峰值直方图仓中保存的计数(例如,h(4)),h(bn)是相邻直方图仓中保存的计数(例如,h(3)),np是峰值直方图仓的数量(例如,4),nn是相邻直方图仓的数量(例如,3)。

[0094]

给定质心cm,距离范围r可以计算为:

[0095][0096]

其中tintegrate是与仓同步的时钟信号的周期(例如,gclk或fastclk),c是光速,并且strobe<i>是峰值直方图仓的选通窗口的开始的持续时间。上述等式1和等式2仅仅是可以计算质心和距离范围的方式的示例,并不旨在限制本发明。在不脱离本发明的范围的情况下,本领域普通技术人员将理解计算质心和/或距离范围的其他方法。

[0097]

图15示出了根据本文描述的一些实施例的用于略微变化的激光脉冲返回的直方图仓的附加示例。如图15所示,尽管使用了粗略直方图采样,但仍然可以通过质心计算来实现精细的距离分辨率(例如,200m处的平均误差<10cm)。在一些实施例中,可以通过仅在峰值仓上计算质心来实现更大的背景抑制,从而降低光滤波器通带要求。此处描述的操作可能会导致在适度像素区域(例如,45nm cmos中的25μm)的低工作频率和功耗(例如,100mhz@0.25μw/像素)。

[0098]

在一些实施例中,背景校正可以通过由像素(或列逻辑)确定峰值仓数(npk)来完成。然后,可以确定具有最高像素计数的相邻(例如,紧邻峰值仓)峰值仓数(nbpk)。接下来,

非npk和nbpk(h

bg

)的仓的计数的总和可以计算为(假设nbpk<npk):

[0099][0100]

上面的示例假设l的直方图仓的数量为非负整数。接下来,这些直方图仓的平均值可以计算为h

av

=h

bg

/(l

‑

2)。然后,经背景校正的质心(cm)可以计算为:

[0101][0102]

以上讨论的等式3和等式4仅仅是计算质心的方式的示例,并不旨在限制本发明。在不脱离本发明的范围的情况下,本领域普通技术人员将理解计算质心和/或距离范围的其他方法。

[0103]

本文描述的实施例提供了优于传统装置的多个优点。本文描述的一些实施例使用选通窗口内的粗略直方图来减少和/或最小化电路资源和/或功率和/或抑制背景噪声。此外,一些实施例将质心的计算限制为峰值直方图仓和紧邻的直方图仓,以显着降低测量误差。本文描述的一些实施例提供直方图的直接生成,不使用tdc,而是使用粗略分级。这提供了使用全局时钟而不需要校准本地tdc的优势。本文描述的一些实施例可以受益于使用低时钟频率(例如,对于10ns激光脉冲为100mhz),这可以降低功耗并允许读

‑

增

‑

写sram操作。本文描述的一些实施例可以将sram存储器用于直方图数据,这可以节约由唯一仓地址循环驱动的区域(例如,在一些实施例中,仓地址不是tdc码)。本文描述的一些实施例可以通过使用并行加法器树而不使用传统的or/xor树或相关器电路来提供多事件的处理。本文描述的一些实施例可以通过加法器进位提供饱和探测,这可以利用不太复杂的算法。本文描述的一些实施例通过在饱和探测之后阻止像素操作(例如,冻结)来提供功率节约。本文描述的一些实施例提供了使用由本文描述的饱和探测信号驱动的范围相关帧速率架构的可能性。

[0104]

本文已经参考了示出示例实施例的附图描述了各种实施例。然而,这些实施例可以以不同的形式体现并且不应被解释为限于在此阐述的实施例。相反,提供这些实施例是为了使本公开彻底和完整,并且将本发明构思充分传达给本领域技术人员。对示例实施例的各种修改以及在此描述的一般原理和特征将是显而易见的。在附图中,层和区域的尺寸和相对尺寸未按比例示出,并且在某些情况下为了清楚可能被夸大。

[0105]

示例实施例主要是根据在特定实现中提供的特定方法和装置来描述的。然而,这些方法和装置可以在其他实现方式中有效地运行。诸如“示例实施例”、“一个实施例”和“另一实施例”之类的短语可以指相同或不同的实施例以及多个实施例。将关于具有某些组件的系统和/或装置来描述实施例。然而,系统和/或装置可以包括比所示那些更少或更多的部件,并且可以在不脱离本发明构思的范围的情况下对部件的布置和类型进行变化。还将在具有特定步骤或操作的特定方法的上下文中描述示例实施例。然而,这些方法和装置可以有效地用于具有不同和/或附加步骤/操作以及与示例性实施例不一致的不同顺序的步骤/操作的其他方法。因此,本发明构思不旨在限于所示实施例,而是符合与本文描述的原理和特征一致的最宽范围。

[0106]

本文使用的术语仅用于描述特定实施例的目的,并不旨在限制示例实施例。如本文所用的单数形式的“一个”、“一种”和“该”也旨在包括复数形式,除非上下文另有明确指

示。还应当理解的是,如本文所用的术语“包括”或“包含”是开放式的,包括一个或更多个陈述的要素、步骤和/或功能,但不排除一个或更多个未陈述的要素、步骤和/或功能。术语“和/或”包括一个或更多个相关所列项目的任何组合和所有组合。

[0107]

应当理解的是,虽然术语第一、第二等可在本文中用于描述各种元素,但这些元素不应受这些术语的限制。这些术语仅用于区分一个元素与另一个元素。因此,在不脱离本发明构思的范围的情况下,下面讨论的第一元件可以被称为第二元件。

[0108]

还应当理解的是,当一个元件被称为“连接”或“耦合”到另一个元件时,它可以直接连接或耦合到另一个元件,或者可以存在中间元件。相反,当一个元件被称为“直接连接”或“直接耦合”到另一个元件时,不存在中间元件。

[0109]

除非另有定义,本文中使用的所有术语(包括技术术语和科学术语)与本发明构思所属领域的普通技术人员通常理解的含义相同。应当进一步理解的是,术语,例如在常用词典中定义的那些,应被解释为具有与其在相关领域的上下文中的含义一致的含义并且不会以理想化或过于正式的含义被解释,除非在本文中明确定义。

[0110]

结合以上描述和附图,本文公开了许多不同的实施例。应当理解的是,逐字地描述和说明这些实施例的每个组合和子组合将是过度重复和混淆的。因此,包括附图在内的本说明书应被解释为构成本文所述实施例的所有组合和子组合、以及制造和使用它们的方式和过程的完整书面描述,并且应支持对任何此类组合的权利要求或子组合的权利要求。

[0111]

在附图和说明书中,已经公开了本公开的实施例,并且虽然使用了特定术语,但是它们仅用于一般和描述性的意义而不是为了限制的目的。提供以下权利要求是为了确保本技术满足作为所有司法管辖区的优先权申请的所有法定要求,并且不应被解释为阐述本发明的范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。