1.本发明涉及静电卡盘。

背景技术:

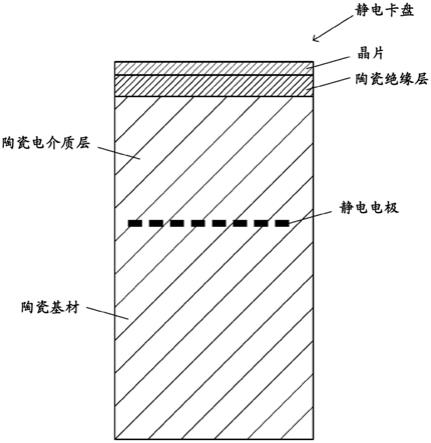

2.以往,在半导体晶片的传送、曝光、cvd等成膜工艺、清洗、蚀刻、切割等微细加工中,使用吸附保持晶片的静电卡盘。例如,专利文献1所公开的静电卡盘具有:陶瓷基材、配置在陶瓷基材上的薄的陶瓷电介质层、以及埋设在陶瓷电介质层与陶瓷基材之间的静电电极(参照图4)。陶瓷电介质层的表面为晶片载置面。在该静电卡盘中,陶瓷基材的材质和陶瓷电介质层的材质均为氧化铝烧结体。

3.现有技术文献

4.专利文献

5.专利文献1:日本特开2005

‑

343733号公报

技术实现要素:

6.发明所要解决的课题

7.但是,由于陶瓷电介质层的材质为氧化铝烧结体,因此虽然绝缘性能(体积电阻率、耐电压)高,但介电常数没有那么高。因此,有时无法充分得到将晶片吸附于晶片载置面时的静电吸附力。

8.本发明是为了解决这样的课题而完成的,其主要目的在于提供一种绝缘性能和静电吸附力都高的静电卡盘。

9.用于解决课题的方案

10.本发明的静电卡盘具备:

11.陶瓷基材;

12.陶瓷电介质层,其配置在所述陶瓷基材上并比所述陶瓷基材薄;

13.静电电极,其埋设在所述陶瓷电介质层与所述陶瓷基材之间;以及

14.陶瓷绝缘层,其配置在所述陶瓷电介质层上并比所述陶瓷电介质层薄,

15.所述陶瓷绝缘层的体积电阻率及耐电压比所述陶瓷电介质层高,

16.所述陶瓷电介质层的介电常数比所述陶瓷绝缘层高。

17.在该静电卡盘中,由于陶瓷绝缘层的体积电阻率及耐电压比陶瓷电介质层高,因此绝缘性能由于该陶瓷绝缘层而被保持得高。另一方面,由于陶瓷电介质层的介电常数比陶瓷绝缘层高,因此与介电常数成比例地变高的静电吸附力由于陶瓷电介质层而变高。这样,本发明的静电卡盘的绝缘性能和静电吸附力都高。

18.在本发明的静电卡盘中,所述陶瓷绝缘层也可以是气溶胶沉积(ad)膜或喷镀膜。特别优选陶瓷绝缘层为ad膜。ad膜在原料粒子彼此的晶界不存在绝缘性低的玻璃相,与使原料粒子烧结而成的膜为同等程度,因此体积电阻率、耐电压变高。

19.在本发明的静电卡盘中,优选所述陶瓷电介质层的材质为钛酸钡或锆钛酸铅,所

述陶瓷绝缘层的材质优选为氧化铝。

20.在本发明的静电卡盘中,所述陶瓷绝缘层可以以覆盖所述陶瓷电介质层的整个表面的方式设置,且具有支撑晶片的多个凸部。

21.在本发明的静电卡盘中,所述陶瓷电介质层可以具有支撑晶片的多个凸部,所述陶瓷绝缘层至少设置于所述凸部的顶面。在陶瓷绝缘层中,陶瓷绝缘层也可以覆盖陶瓷电介质层的整个表面而不仅仅覆盖陶瓷电介质层的凸部。

附图说明

22.图1是本实施方式的静电卡盘的纵剖视图。

23.图2是另一实施方式的静电卡盘的纵剖视图。

24.图3是另一实施方式的静电卡盘的纵剖视图。

25.图4是以往的静电卡盘的纵剖视图。

具体实施方式

26.以下,参照附图来说明本发明的优选的实施方式。图1是晶片载置台的制造工序图(纵剖视图)。

27.如图1所示,静电卡盘具备陶瓷基材、陶瓷电介质层、静电电极和陶瓷绝缘层。陶瓷电介质层配置在陶瓷基材上,且比陶瓷基材薄。在本实施方式中,陶瓷电介质层和陶瓷基材是一体烧成的陶瓷烧结体。静电电极埋设在陶瓷电介质层与陶瓷基材之间。陶瓷绝缘层配置在陶瓷电介质层上,且比陶瓷电介质层薄。陶瓷绝缘层的体积电阻率及耐电压比陶瓷电介质层高,陶瓷电介质层的介电常数比陶瓷绝缘层高。

28.陶瓷绝缘层可以是cvd膜或pvd膜,但从能够比较容易地使膜厚变厚的方面考虑,优选为ad膜或喷镀膜。特别是,ad膜在原料粒子彼此的晶界不存在绝缘性低的玻璃相,与使原料粒子烧结而成的膜为同等程度,因此体积电阻率、耐电压变高。ad膜是由ad法(包括等离子体ad法)形成的膜。ad法由于能够通过冲击固化现象使陶瓷粒子成膜,因此不需要在高温下对陶瓷粒子进行烧结。

29.陶瓷电介质层的材质优选为钛酸钡或锆钛酸铅,陶瓷绝缘层的材质优选为氧化铝。

30.在以上说明的本实施方式的静电卡盘中,由于陶瓷绝缘层的体积电阻率及耐电压比陶瓷电介质层高,因此绝缘性能由于该陶瓷绝缘层而被保持得高。另一方面,由于陶瓷电介质层的介电常数比陶瓷绝缘层高,因此与介电常数成比例地变高的静电吸附力由于陶瓷电介质层而变高。

31.需说明的是,不言而喻,本发明不受上述的实施方式的任何限制,只要属于本发明的技术范围内就可用各种方式来实施。

32.例如,在上述的实施方式中,陶瓷绝缘层也可以以覆盖陶瓷电介质层的整个表面的方式设置并具有支撑晶片的多个凸部(参照图2)。关于这样的结构,也可以例如以覆盖陶瓷电介质层的整个表面的方式形成ad膜,在将该ad膜的表面精加工成镜面(例如表面粗糙度ra为0.1μm以下的面)之后,利用ad法(包括等离子体ad法)在该镜面上形成多个凸部。这样一来,由于未形成凸部的部分保持镜面的状态,因此不会成为在半导体工艺中产生微粒

的原因。

33.在上述的实施方式中,也可以是陶瓷电介质层具有支撑晶片的多个凸部,陶瓷绝缘层仅设置在凸部的顶面(参照图3),但从提高耐电压的观点出发,优选覆盖陶瓷电介质层的整个表面而不仅仅覆盖陶瓷电介质层的凸部。

34.在上述的实施方式中,也可以在陶瓷基材中埋设rf电极和加热器电极(电阻发热体)中的至少一者。

35.本申请将2019年6月28日申请的日本专利申请第2019

‑

121488号作为优先权主张的基础,通过引用将其全部内容包含在本说明书中。

36.产业上的利用可能性

37.本发明能够用于例如半导体晶片的传送、曝光、cvd等成膜工艺、清洗、蚀刻、切割等微细加工。

技术特征:

1.一种静电卡盘,具备:陶瓷基材;陶瓷电介质层,其配置在所述陶瓷基材上并比所述陶瓷基材薄;静电电极,其埋设在所述陶瓷电介质层与所述陶瓷基材之间;以及陶瓷绝缘层,其配置在所述陶瓷电介质层上并比所述陶瓷电介质层薄,所述陶瓷绝缘层的体积电阻率及耐电压比所述陶瓷电介质层高,所述陶瓷电介质层的介电常数比所述陶瓷绝缘层高。2.根据权利要求1所述的静电卡盘,其中,所述陶瓷绝缘层为气溶胶沉积膜或喷镀膜。3.根据权利要求1或2所述的静电卡盘,其中,所述陶瓷电介质层的材质为钛酸钡或锆钛酸铅,所述陶瓷绝缘层的材质为氧化铝。4.根据权利要求1至3中任一项所述的静电卡盘,其中,所述陶瓷绝缘层以覆盖所述陶瓷电介质层的整个表面的方式设置,具有支撑晶片的多个凸部。5.根据权利要求1至3中任一项所述的静电卡盘,其中,所述陶瓷电介质层具有支撑晶片的多个凸部,所述陶瓷绝缘层至少设置在所述凸部的顶面。

技术总结

静电卡盘具备陶瓷基材、陶瓷电介质层、静电电极和陶瓷绝缘层。陶瓷电介质层配置在陶瓷基材上,比陶瓷基材薄。静电电极埋设在陶瓷电介质层与陶瓷基材之间。陶瓷绝缘层配置在陶瓷电介质层上,比陶瓷电介质层薄。陶瓷绝缘层的体积电阻率及耐电压比所述陶瓷电介质层高,陶瓷电介质层的介电常数比陶瓷绝缘层高。瓷电介质层的介电常数比陶瓷绝缘层高。瓷电介质层的介电常数比陶瓷绝缘层高。

技术研发人员:竹林央史 相川贤一郎 久野达也

受保护的技术使用者:日本碍子株式会社

技术研发日:2020.06.10

技术公布日:2021/12/3

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。