1.本技术涉及数字集成电路的测量技术领域,例如涉及一种时序单元保持时间的测量方法和测量电路。

背景技术:

2.时序单元的保持时间是影响信号数据稳定传输的重要因素之一,在进行时序单元库的设计时,时序单元保持时间的精确测量直接影响芯片的性能、生产和制造。现有技术中通常采用时钟相位精细调节法或通过多个缓冲器作为最小测量刻度等效测量保持时间。然而,这些方法存在很多不足,比如受限于时钟相位可调范围小和缓冲器存在延迟,测量的时钟路径和数据路径存在差异性,且在不同的测试电压下这种差异性的表现更明显,由此会导致时序单元保持时间的测量误差非常大。

技术实现要素:

3.有鉴于此,本技术实施例提供一种时序单元保持时间的测量方法和测量电路,以提高时序单元保持时间的测量精度,满足芯片的性能要求。

4.本技术实施例提供一种时序单元保持时间的测量电路,该测量电路包括时钟信号发生模块、第一选择模块、第二选择模块、延迟检测模块、第一时钟相位控制器、第二时钟相位控制器、数据信号传输模块、时钟信号传输模块、待测时序单元和控制模块;

5.其中,所述时钟信号发生模块分别与所述第一选择模块、所述延迟检测模块和所述控制模块电连接;所述延迟检测模块分别与所述第一选择模块、所述第二选择模块和所述控制模块电连接;所述第一选择模块分别与所述控制模块、所述第一时钟相位控制器和所述第二时钟相位控制器电连接;所述第二选择模块分别与所述控制模块、所述数据信号传输模块和所述时钟信号传输模块电连接;所述第一时钟相位控制器分别与所述控制模块和所述数据信号传输模块电连接,所述第二时钟相位控制器分别与所述控制模块和所述时钟信号传输模块电连接,所述数据信号传输模块分别与所述待测时序单元和所述控制模块电连接,所述时钟信号传输模块分别与所述待测时序单元和所述控制模块电连接,所述待测时序单元与所述控制模块电连接;

6.所述第一时钟相位控制器用于输出第一脉冲信号并为所述数据信号传输模块提供时钟信号,所述第二时钟相位控制器用于输出第二脉冲信号并为所述时钟信号传输模块提供时钟信号;

7.所述控制模块用于控制所述第一选择模块和所述第二选择模块,形成第一测试路径、第二测试路径和第三测试路径,以基于所述第一测试路径、所述第二测试路径和所述第三测试路径,确定时序单元的保持时间,其中,所述第一测试路径由所述时钟信号发生模块、所述第一时钟相位控制器、所述第二时钟相位控制器、所述数据信号传输模块、所述时钟信号传输模块、待测时序单元和控制模块组成,所述第二测试路径由所述时钟信号发生模块、所述延迟检测模块、所述第一时钟相位控制器、所述数据信号传输模块和控制模块组

成,所述第三测试路径由所述时钟信号发生模块、所述延迟检测模块、所述第二时钟相位控制器、所述时钟信号传输模块和控制模块组成。

8.本技术实施例还提供了一种时序单元保持时间的测量方法,该测量方法适用于本技术实施例所述的时序单元保持时间的测量电路,所述测量电路包括时钟信号发生模块、第一选择模块、第二选择模块、延迟检测模块、第一时钟相位控制器、第二时钟相位控制器、数据信号传输模块、时钟信号传输模块、待测时序单元和控制模块,所述控制模块控制所述第一选择模块和所述第二选择模块,形成第一测试路径、第二测试路径和第三测试路径,所述第一测试路径由所述时钟信号发生模块、所述第一时钟相位控制器、所述第二时钟相位控制器、所述数据信号传输模块、所述时钟信号传输模块、待测时序单元和控制模块组成,所述第二测试路径由所述时钟信号发生模块、所述延迟检测模块、所述第一时钟相位控制器、所述数据信号传输模块和控制模块组成,所述第三测试路径由所述时钟信号发生模块、所述延迟检测模块、所述第二时钟相位控制器、所述时钟信号传输模块和控制模块组成;

9.所述方法包括:

10.分别确定时钟信号的第一周期值、第二周期值和第三周期值,其中,所述第一周期值为在所述第一测试路径下所述待测时序单元正确接收所述时钟信号的临界周期,所述第二周期值为在所述第二测试路径下所述延迟检测模块正确接收所述时钟信号的临界周期,所述第三周期值为在所述第三测试路径下所述延迟检测模块正确接收所述时钟信号的临界周期;

11.根据所述第一周期值、所述第二周期值和所述第三周期值确定时序单元的保持时间。

12.关于本技术的以上实施例和其他方面以及其实现方式,在附图说明、具体实施方式和权利要求中提供更多说明。

附图说明

13.图1是现有技术中的一种时序单元保持时间的示意图;

14.图2是本技术实施例提供的一种时序单元保持时间的测量电路的结构示意图;

15.图3是本技术实施例提供的一种时序单元保持时间测量信号的时序图;

16.图4是本技术实施例提供的另一种时序单元保持时间的测量电路的结构示意图;

17.图5是本技术实施例提供的一种时序单元保持时间的测量方法的流程图;

18.图6是本技术实施例提供的一种时钟信号的周期值的确定方法的流程图;

19.图7是本技术实施例提供的一种时钟信号的周期值的测量示意图。

具体实施方式

20.下文中将结合附图对本技术的实施例进行说明。在不冲突的情况下,本技术中的实施例及实施例中的特征可以相互任意组合。

21.图1是现有技术中的一种时序单元保持时间的示意图。参考图1,时序单元(如触发器)的保持时间(th:hold time)是指在时序单元的时钟信号上升沿到来以后,数据信号需要保持稳定不变的时间。如果保持时间th不够,数据将不能被有效读取并转换为输出,保持时间th就是指这个最小的稳定时间。

22.在现有技术中,时序单元的保持时间是在单元库设计的时候,可由spice工具通过仿真得到,但这只是一个理论计算值,如果理论计算值相比于芯片中的实际数值偏大,则给后端时序收敛加重了不必要的困难,而如果理论计算值要偏小,则可能造成芯片生产后出现时序问题,芯片达不到实际工作频率,因此在完成时序单元库设计后,保持时间的理论与实际之间的数值保持一致性非常重要。为了确保保持时间的实际值与理论值保持一致,通常需要对保持时间进行测量验证。

23.在一种现有的技术方案中,提出一种基于时钟相位精细调节的保持时间的测量方法,例如通过对时钟相位的精细调节,将精细调节后的两个具有相位偏差的时钟分别作为时钟与数据送入待测时序单元进行hold violation(保持时间时序违例)的识别,以此判断出时序单元的保持时间,但这种本身测量精度受限于时钟相位可调的最小step,加之时钟在不同传输路径上具有差异性,且在不同测试电压下,这种差异性的表现各不相同,保持时间误差非常大。

24.在另一种现有的技术方案中,提出利用一个延迟较小的buffer(缓冲器)作为最小测量刻度,同时针对时序单元的时钟与数据路径构造不同数量差异的buffer,以此来判断出保持时间等效于多少个最小测量刻度buffer,这种方法的精度也受限于作为最小测量刻度的buffer的延迟,同样在测量的时钟与数据通路上也存在差异性,且在不同电压下,这种差异性的表现会显著加大,导致测量结果误差非常大。

25.在现有技术中,通常,时序单元保持时间的测量与时钟信号的周期或频率大小无关。

26.有鉴于此,本技术提出一种时序单元保持时间的测量电路和测量方法,通过控制模块控制第一时钟相位控制器输出第一脉冲信号并为数据信号传输模块提供时钟信号,控制第二时钟相位控制器输出第二脉冲信号并为时钟信号传输模块提供时钟信号,由此使得时序单元保持时间的测量与时钟信号的周期或频率产生关联。然后通过控制模块控制第一选择模块和第二选择模块,形成第一测试路径、第二测试路径和第三测试路径,再分别确定时钟信号在第一测试路径下待测时序单元正确接收时钟信号的临界周期(记为第一周期值)、在第二测试路径下延迟检测模块正确接收时钟信号的临界周期(记为第二周期值)、在第三测试路径下延迟检测模块正确接收时钟信号的临界周期(记为第三周期值),最后根据第一周期值、第二周期值和第三周期值确定时序单元的保持时间。由此可知,第一时钟相位控制器和第二时钟相位控制器使得第一测试路径下保持时间违例测试与时钟信号的周期或频率产生关联(即与第一周期值有关),从而使得时序单元保持时间的确定只与第一周期值、第二周期值和第三周期值有关,而不会存在受限于时钟相位调节范围和缓冲器延迟,以及不同的测试电压差异性大导致测量误差大的问题,从而提高了测量的精度。

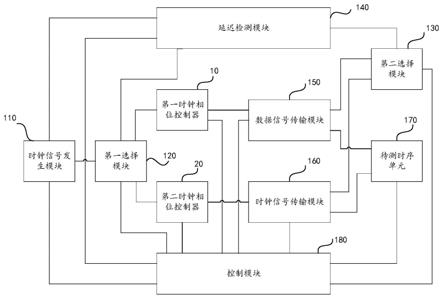

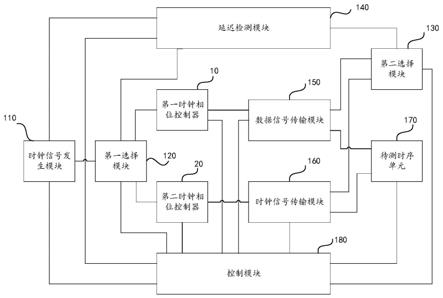

27.在一实现方式中,图2是本技术实施例提供的一种时序单元保持时间的测量电路的结构示意图,参考图2,该测试电路包括时钟信号发生模块110、第一选择模块120、第二选择模块130、延迟检测模块140、第一时钟相位控制器10、第二时钟相位控制器20、数据信号传输模块150、时钟信号传输模块160、待测时序单元170和控制模块180;

28.其中,时钟信号发生模块110分别与第一选择模块120、延迟检测模块140和控制模块180电连接;延迟检测模块140分别与第一选择模块120、第二选择模块130和控制模块180电连接;第一选择模块120分别与控制模块180、第一时钟相位控制器10和第二时钟相位控

制器20电连接;第二选择模块130分别与控制模块180、数据信号传输模块150和时钟信号传输模块160电连接;第一时钟相位控制器10分别与控制模块180和数据信号传输模块150电连接,第二时钟相位控制器20分别与控制模块180和时钟信号传输模块160电连接,数据信号传输模块150分别与待测时序单元170和控制模块180电连接,时钟信号传输模块160分别与待测时序单元170和控制模块180电连接,待测时序单元170与控制模块180电连接;

29.第一时钟相位控制器10用于输出第一脉冲信号并为数据信号传输模块150提供时钟信号,第二时钟相位控制器20用于输出第二脉冲信号并为时钟信号传输模块160提供时钟信号;

30.控制模块180用于控制第一选择模块120和第二选择模块130,形成第一测试路径、第二测试路径和第三测试路径,以基于第一测试路径、第二测试路径和第三测试路径,确定时序单元的保持时间,其中,第一测试路径由时钟信号发生模块110、第一时钟相位控制器10、第二时钟相位控制器20、数据信号传输模块150、时钟信号传输模块160、待测时序单元170和控制模块180组成,第二测试路径由时钟信号发生模块110、延迟检测模块140、第一时钟相位控制器10、数据信号传输模块150和控制模块180组成,第三测试路径由时钟信号发生模块110、延迟检测模块140、第二时钟相位控制器20、时钟信号传输模块160和控制模块180组成。

31.在一实施例中,图3是本技术实施例提供的一种时序单元保持时间测量信号的时序图,参考图3,设时钟信号发生模块110发出的时钟信号为具有两个上升沿的脉冲信号,如图3中的p1曲线,分别在t0和t2时刻具有一个上升沿,分别在t1和t3时刻具有一个下降沿,该具有两个上升沿的脉冲信号分别输入到第一时钟相位控制器10和第二时钟相位控制器20,经第一时钟相位控制器10输出为第一个上升沿被截断,只有第二个上升沿能通过的第一脉冲信号,如图3中的p2曲线,第一脉冲信号在t2时刻有一个上升沿;经第二时钟相位控制器20输出为第二个上升沿被截断,只有第一个上升沿能通过的第二脉冲信号,如图3中的p3曲线,第二脉冲信号在t0时刻有一个上升沿。在图3中,曲线p4为第二发送寄存器151输出端输出的数据信号时序图,曲线p5为待测时序单元的输出端输出的信号时序图。其中,第一脉冲信号可以为数据信号传输模块150提供时钟信号,第二脉冲信号可以为时钟信号传输模块160提供时钟信号。

32.在一实施例中,第一选择模块120用于控制时钟信号发生模块110和延迟检测模块140中的一个分别与第一时钟相位控制器10和第二时钟相位控制器20接通。第二选择模块130用于控制数据信号传输模块150和时钟信号传输模块160中的一个与延迟检测模块140接通。例如,当控制模块180控制第一选择模块120控制时钟信号发生模块110分别与第一时钟相位控制器10和第二时钟相位控制器20接通,测试电路进入待测时序单元保持时间的临界点测试模式,即形成由时钟信号发生模块110、第一时钟相位控制器10、数据信号传输模块150、时钟信号传输模块160、第二时钟相位控制器20、待测时序单元170和控制模块180组成的第一测试路径。

33.当控制模块180控制第一选择模块120控制延迟检测模块140分别与第一时钟相位控制器10和第二时钟相位控制器20接通,控制第二选择模块130控制数据信号传输模块150和时钟信号传输模块160中的一个与延迟检测模块140接通,使测试电路进入时钟信号传输路径与数据信号传输路径的延迟比较模式,其中,数据信号传输路径为由时钟信号发生模

块110、延迟检测模块140、第一时钟相位控制器10、数据信号传输模块150和控制模块180组成的第二测试路径,时钟信号传输路径为由时钟信号发生模块110、延迟检测模块140、第二时钟相位控制器20、时钟信号传输模块160和控制模块180组成的第三测试路径。

34.在一实施例中,图4是本技术实施例中提供的另一种时序单元保持时间的测量电路的结构示意图,参考图4,时钟信号发生模块110包括时钟调频单元111和时钟脉冲控制单元112,时钟调频单元111与时钟脉冲控制单元112电连接,时钟脉冲控制单元112分别与延迟检测模块140和第一选择模块120的第一输入端a1电连接,控制模块180分别与时钟调频单元111和时钟脉冲控制单元112电连接。

35.在实施例中,时钟调频单元111可以为pll(phase locked loop,锁相环),用做时钟源,其时钟频率精度和稳定度高,抖动小,且频率可精细化调整。时钟脉冲控制单元112可以为occ电路(on-chip-clock,时钟产生电路),用于输出时钟脉冲信号。

36.在一实施例中,参考图4,延迟检测模块140包括第一发送寄存器141和接收寄存器142,其中,第一发送寄存器141的第一输入端与时钟信号发生模块110电连接,第一发送寄存器141的第二输入端输入外接数据信号data1,第一发送寄存器141的输出端与第一选择模块120的第二输入端a2电连接;接收寄存器142的第一输入端与时钟信号发生模块110电连接,接收寄存器142的第二输入端与第二选择模块130的输出端电连接,接收寄存器142的输出端与控制模块180电连接。

37.在实施例中,第一发送寄存器141用于测试电路在第二测试路径和第三测试路径下数据信号传输的起点,接收寄存器142用于测试电路在第二测试路径和第三测试路径下数据信号传输的终点。例如,在第二测试路径下,控制模块180控制第一选择模块120的第二输入端a2接通,即将延迟检测模块的第一发送寄存器141的输出端分别与第一时钟相位控制器10和第二时钟相位控制器20接通,同时控制模块180还控制第二选择模块130的第二输入端b2与延迟检测模块140的接收寄存器142接通,即形成由时钟信号发生模块110、第一发送寄存器141、第一时钟相位控制器10、数据信号传输模块150、接收寄存器142和控制模块180组成的第二测试路径。在第二测试路径下测试时,第一发送寄存器141的第一输入端输入时钟信号发生模块110输出的时钟信号,第一发送寄存器141的第二输入端输入外接数据信号data1,外接数据信号data1由第一发送寄存器141输出,经数据信号传输模块150,最终输送到接收寄存器142。

38.在第三测试路径下,控制模块180控制第一选择模块120的第二输入端a2接通,即将延迟检测模块140的第一发送寄存器141的输出端分别与第一时钟相位控制器10和第二时钟相位控制器20接通,同时控制模块180还控制第二选择模块130的第一输入端b1与延迟检测模块140的接收寄存器142接通,即形成由时钟信号发生模块110、第一发送寄存器141、第二时钟相位控制器20、时钟信号传输模块160、接收寄存器142和控制模块180组成的第三测试路径。在第三测试路径下测试时,第一发送寄存器141的第一输入端输入时钟信号发生模块110输出的时钟信号,第一发送寄存器141的第二输入端输入外接数据信号data1,外接数据信号data1由第一发送寄存器141输出,经时钟信号传输模块160,最终输送到接收寄存器142。

39.在一实施例中,参考图4,数据信号传输模块150包括第二发送寄存器151,第二发送寄存器151的第一输入端与第一时钟相位控制器10电连接,第二发送寄存器151的第二输

入端输入外接数据信号data1,第二发送寄存器151的输出端分别与第二选择模块130的第二输入端和待测时序单元170的第二输入端电连接。

40.在实施例中,第二发送寄存器151的第二输入端输入外接数据信号data1用于为第一测试路径测试时提供数据信号。例如,在第一测试路径下,控制模块180控制第一选择模块120的第一输入端a1接通,即信号发生模块110的输出端分别与第一时钟相位控制器10和第二时钟相位控制器20接通,形成由时钟信号发生模块110、第一时钟相位控制器10、数据信号传输模块150、第二时钟相位控制器20、时钟信号传输模块160、待测时序单元170和控制模块180组成的第一测试路径。在第一测试路径下测试时,第二发送寄存器151的第一输入端输入第一时钟相位控制器10输出的第一脉冲信号,该第一脉冲信号为第一测试路径测试时提供时钟信号,第二发送寄存器151的第二输入端输入外接数据信号data1,外接数据信号data1由第二发送寄存器151输出,然后输送到待测时序单元170。

41.在实施例中,参考图4,第二发送寄存器151的复位端、第一发送寄存器141的复位端、接收寄存器142的复位端、待测时序单元170的复位端均与控制模块180电连接,通过控制模块180可以控制第二发送寄存器151、第一发送寄存器141、接收寄存器142和待测时序单元170的复位和清零功能。

42.在一实施例中,参考图4,时钟信号传输模块160包括至少一个第一缓冲模块b1,第一缓冲模块b1的输入端与第二时钟相位控制器20电连接,第一缓冲模块b1的输出端分别与第二选择模块130的第一输入端和待测时序单元170的第一输入端电连接。

43.在实施例中,第一缓冲模块b1形成时钟信号传输路径,第一缓冲模块b1用于调节时钟信号传输模块160的延迟时间。需要说明的是,数据信号传输模块150也可以包括第一缓冲模块b1,可以由第二发送寄存器151和第一缓冲模块b1组成数据信号传输路径,数据信号传输路径的第一缓冲模块b1的数量可以包括多个,时钟信号传输路径的第一缓冲模块b1的个数也可以包括多个,其具体的个数可以根据实际的测试需求进行设置,具体个数在此不做具体的限定。

44.在一实施例中,当控制模块180控制第一选择模块120的第一输入端a1闭合且第二输入端a2断开、第二选择模块130的第一输入端b1和第二输入端b2均断开时,形成第一测试路径;当控制模块180控制第一选择模块120的第一输入端a1断开且第二输入端a2闭合、第二选择模块130的第一输入端b1断开且第二输入端b2闭合时,形成第二测试路径;当控制模块180控制第一选择模块120的第一输入端a1断开且第二输入端a2闭合、第二选择模块130的第一输入端b1闭合且第二输入端b2断开时,形成第三测试路径。

45.在实施例中,当控制模块180控制第一选择模块120的第一输入端a1闭合且第二输入端a2断开、第二选择模块130的第一输入端b1和第二输入端b2均断开时,即使得延迟检测模块与第一时钟相位控制器10和第二时钟相位控制器20断开,使信号发生模块110的输出端分别与第一时钟相位控制器10和第二时钟相位控制器20接通,形成由时钟信号发生模块110、第一时钟相位控制器10、数据信号传输模块150(包括由第二发送寄存器151形成的数据信号传输路径)、第二时钟相位控制器20、时钟信号传输模块160(包括由第一缓冲模块b1形成的时钟信号传输路径)、待测时序单元170和控制模块180组成的第一测试路径。在第一测试路径中,数据信号传输路径具有固定延迟,延迟数值记为t_data,时钟信号传输路径也具有固定延迟,延迟数值记为t_c l k。在第一测试路径下测试时,信号发生模块110输出具

有两个上升沿的脉冲信号,该脉冲信号分别输入到第一时钟相位控制器10和第二时钟相位控制器20,经第一时钟相位控制器10输出第一脉冲信号,经第二时钟相位控制器20输出第二脉冲信号,第一脉冲信号作为第二发送寄存器151的时钟信号,第二发送寄存器151的第一输入端输入的第一脉冲信号如图3中的p2曲线,第二脉冲信号经第一缓冲模块b1输出到待测时序单元170的第一输入端(即时钟端),输入到待测时序单元的第一输入端的第二脉冲信号如图3中曲线p3,待测时序单元的输出端输出的信号时序如图3中的曲线p5。第二发送寄存器151的第一输入端输入第一脉冲信号,第二发送寄存器151的第二输入端输入外接数据信号data1(如图3中的曲线p4),通过时钟信号发生模块110可以调节时钟信号的频率,通常,当时钟信号频率比较慢时,外接数据信号data1由第二发送寄存器151输出后能够被待测时序单元170捕获到,但是当时钟信号频率达到某个阈值时,会出现hold违例,待测时序单元170将无法捕获第二发送寄存器151发出的数据信号,此时出现hold违例的时钟信号的临界周期记为period_hd,且该临界周期满足如下条件:

46.t

clk-t

data

=period_hd-th

47.其中,th为待测时序单元的保持时间。

48.当控制模块180控制第一选择模块120的第一输入端a1断开且第二输入端a2闭合、第二选择模块130的第一输入端b1断开且第二输入端b2闭合时,即使得第一发送寄存器141与第一时钟相位控制器10接通,第一时钟相位控制器10与数据信号传输模块150接通,数据信号传输模块150与接收寄存器142接通,形成由时钟信号发生模块110、第一发送寄存器141、第一时钟相位控制器10、第二发送寄存器151、接收寄存器142和控制模块180组成的第二测试路径。其中,第一时钟相位控制器10可以被控制模块180控制为直通状态,即对第一发送寄存器141输出的信号不做关断处理。在第二测试路径下测试时,第一发送寄存器141的第一输入端输入时钟信号发生模块110输出的时钟信号,第一发送寄存器141的第二输入端输入外接数据信号data1,通过时钟信号发生模块110可以调节时钟信号的频率,通常,当时钟信号频率比较慢时,外接数据信号data1由第一发送寄存器141发出经第一时钟相位控制器10和第二发送寄存器151输出后能够被接收寄存器142捕获到,当时钟信号频率比较快时能够提高数据信号的传输速率,但是当时钟信号频率太快时,接收寄存器142将无法正常接收由第一发送寄存器141发出的数据信号。则当时钟信号频率达到某个阈值时,接收寄存器142刚好能够收到数据信号时的时钟信号的周期为临界周期,该临界周期记为per iod_data。

49.当控制模块180控制第一选择模块120的第一输入端a1断开且第二输入端a2闭合、第二选择模块130的第一输入端b1闭合且第二输入端b2断开时,即使得第一发送寄存器141与第二时钟相位控制器20接通,第二时钟相位控制器20与时钟信号传输模块160接通,时钟信号传输模块160与接收寄存器142接通,形成由时钟信号发生模块110、第一发送寄存器141、第二时钟相位控制器20、第一缓冲模块b1、接收寄存器142和控制模块180组成的第三测试路径。其中,第二时钟相位控制器20可以被控制模块180控制为直通状态,即对第一发送寄存器141输出的信号不做关断处理。在第三测试路径下测试时,第一发送寄存器141的第一输入端输入时钟信号发生模块110输出的时钟信号,第一发送寄存器141的第二输入端输入外接数据信号data1,通过时钟信号发生模块110可以调节时钟信号的频率,通常,当时钟信号频率比较慢时,外接数据信号data1由第一发送寄存器141发出经第二时钟相位控制

器20和第一缓冲模块b1输出后能够被接收寄存器142捕获到,当时钟信号频率比较快时能够提高数据信号的传输速率,但是当时钟信号频率太快时,接收寄存器142将无法正常接收由第一发送寄存器141发出的数据信号。则当时钟信号频率达到某个阈值时,接收寄存器142刚好能够收到数据信号时的时钟信号的周期为临界周期,该临界周期记为period_clk。则,第二测试路径下的临界周期period_data和第三测试路径下的period_clk满足如下条件:

50.t

data-t

clk

=period_data-period_clk

51.则结合第一测试路径下出现hold违例的时钟信号的临界周期记为period_hd所满足的条件,可以得到:

52.th=period_hd-period_clk period_data

53.由此可知,时序单元保持时间th只与第一测试路径下的待测时序单元正确接收数据时的时钟信号的临界周期记为period_hd、第二测试路径下延迟检测模块能刚好正常接收到数据信号时的时钟信号的临界周期period_data和第三测试路径下延迟检测模块能刚好正常接收到数据信号时的时钟信号的临界周期period_clk有关,而与数据信号传输路径和时钟信号传输路径的差异性、缓冲器的延迟、以及测试电压无关,可以避免现有技术中存在因数据信号传输路径和时钟信号传输路径的差异性、缓冲器的延迟、测试电压不同差异性大等问题而导致的测量结果误差较大的问题,从而可以提高待测时序单元保持时间的测量精度。

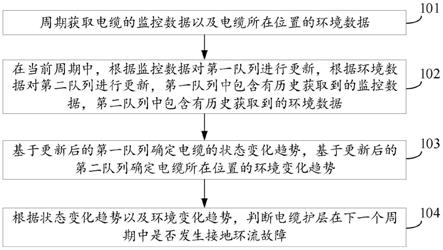

54.在一实现方式中,图5是本技术实施例提供的一种时序单元保持时间的测量方法的流程图,本技术的时序单元保持时间的测量方法适用于本技术任意实施例所述的时序单元保持时间的测量电路,该测量电路包括时钟信号发生模块、第一选择模块、第二选择模块、延迟检测模块、第一时钟相位控制器、第二时钟相位控制器、数据信号传输模块、时钟信号传输模块、待测时序单元和控制模块,控制模块控制第一选择模块和第二选择模块,形成第一测试路径、第二测试路径和第三测试路径,第一测试路径由时钟信号发生模块、第一时钟相位控制器、第二时钟相位控制器、数据信号传输模块、时钟信号传输模块、待测时序单元和控制模块组成,第二测试路径由时钟信号发生模块、延迟检测模块、第一时钟相位控制器、数据信号传输模块和控制模块组成,第三测试路径由时钟信号发生模块、延迟检测模块、第二时钟相位控制器、时钟信号传输模块和控制模块组成;

55.参考图5,该测量方法包括如下步骤:

56.s210、分别确定时钟信号的第一周期值、第二周期值和第三周期值,其中,第一周期值为在第一测试路径下待测时序单元正确接收时钟信号的临界周期,第二周期值为在第二测试路径下延迟检测模块正确接收时钟信号的临界周期,第三周期值为在第三测试路径下延迟检测模块正确接收时钟信号的临界周期;

57.s220、根据第一周期值、第二周期值和第三周期值确定时序单元的保持时间。

58.在一实施例中,时序单元的保持时间=第一周期值-第二周期值 第三周期值。

59.在实施例中,通过控制模块180可以控制时钟信号发生模块110输出的时钟信号的周期或频率,以实现在第一测试路径、第二测试路径和第三测试路径下时钟信号频率的调节。

60.在实施例中,通过第一时钟相位控制器10可以控制时钟信号发生模块110输出的

时钟信号的脉冲个数和相位,输出第一脉冲信号,通过第二时钟相位控制器20可以控制时钟信号发生模块110输出的时钟信号的脉冲个数和相位,输出第二脉冲信号,以实现第一测试路径下可以通过改变时钟信号发生模块110输出的时钟信号的周期测试待测时序单元保持时间的违例。

61.在实施例中,参考图5,分别测得:在第一测试路径下,待测时序单元出现违例时,待测时序单元刚好能捕获到由数据信号传输模块150的第二发送寄存器151发出的数据信号时,时钟信号的周期值,即第一周期值period_hd;在第二测试路径下,接收寄存器142刚好能捕获到由延迟检测模块140的第一发送寄存器141发出的经数据信号传输模块150输出的数据信号时,时钟信号的周期值,即第二周期值period_data;在第三测试路径下,接收寄存器142刚好能捕获到由延迟检测模块140的第一发送寄存器141发出的经时钟信号传输模块160输出的数据信号时,时钟信号的周期值,即第三周期值period_clk。其中,第一周期值、第二周期值、第三周期值和待测时序单元的保持时间满足如下关系:

62.th=period_hd-period_clk period_data

63.由此,可以确定待测时序单元的保持时间th。

64.在一实现方式中,图6是本技术实施例提供的一种时钟信号的周期值的确定方法的流程图,根据图6所述的方法可以确定时钟信号的周期值,其中,周期值为第一周期值、第二周期值、第三周期值中的任意一项。确定时钟信号的周期值的方法包括如下步骤:

65.s310、确定时钟信号的临界周期预估范围和周期步长。

66.在实施例中,确定时钟信号的临界周期预估范围的方法可以为:首先可由spice工具通过仿真获取时钟信号的临界周期的期望值。然后确定一个周期步长,该周期步长可以为变步长,最后根据周期步长从小到大依次进行测试,直到第一次出现时钟信号的临界周期的测试值与临界周期的期望值不一致时,以第一次出现时钟信号的临界周期的测试值与临界周期的期望值不一致时的时钟信号周期值与周期步长之差作为临界周期预估范围的左区间值,记为p_min,以第一次出现时钟信号的临界周期的测试值与临界周期的期望值不一致时的时钟信号周期值与周期步长之和作为临界周期预估范围的右区间值,记为p_max。由此可以确定时钟信号的临界周期范围f,记为<p_min,p_max>。

67.在实施例中,周期步长可以为固定周期步长s,例如周期步长s可以为1ps、5ps和10ps等。此外,周期步长越小,则调节的精度越高,降低时钟抖动影响的效果就越好。

68.s320、根据周期步长将临界周期预估范围分成n份,得到n 1个测试周期值。

69.在实施例中,例如,可以根据周期步长s将临界周期范围f分成n份,加上f的两个区间端点值,共得到n 1个测试周期值。其中,n 1个测试周期值可以为p_max、p_min (n-1)*s、p_min (n-2)*s、

…

p_min 4*s、p_min 3*s、p_min 2*s、p_min 1*s和p_min。

70.s330、对n 1个测试周期值进行测试,得到n 1个测试结果。

71.s340、从n 1个测试周期值中找出m个测试周期值,m个测试周期值的测试结果为待测时序单元或延迟检测模块能正确接收时钟信号;其中,m小于或者等于n 1。

72.s350、根据m个测试周期值,确定时钟信号的周期值。

73.在实施例中,图7是本技术实施例提供的一种时钟信号的周期值的测量示意图,参考图7,根据时序分析理论,可以估算出,在第一测试路径下,当时钟信号周期小于某一特定值(例如p_min)时,此时测试电路的待测时序单元一定能够采样到时序单元保持时间出现

违例,小于p_min的周期区域称之为预估稳定发生时序违例区域,如图7中的i区;当时钟信号周期大于某一特定值(例如p_max),此时测试电路的待测时序单元能够稳定采样到正常的输出结果,大于p_max的周期区域称之为预估稳定不发生时序违例区域,如图7中的ii区。同理,在第二测试路径和第三测试路径下,当时钟信号周期小于某一特定值(例如p_min)时,此时测试电路的延迟检测模块的接收寄存器一定能够采样到接收寄存器无法正确接收数据信号的结果,小于p_min的周期区域称之为预估稳定发生无法正确接收数据信号的区域;当时钟信号周期大于某一特定值(例如p_max),此时测试电路的延迟检测模块的接收寄存器一定能够稳定采样到正确的数据信号,大于p_max的周期区域称之为预估稳定不发生无法正确接收数据信号的区域。

74.在实施例中,以第一次测试路径测试为例,首先分别对n 1个测试周期值进行测试,得到n 1个测试结果并记录。这n 1个测试结果可以包括出现保持时间时序违例跳变、非时序违例跳变、发生违例和未发生违例,即出现图7所示的时序违例跳变点k1和k2,非时序违例跳变点k3和k4,以及预估稳定发生时序违例区域i区和预估稳定不发生时序违例区域ii区。然后从n 1个测试结果中找出其测试结果为刚好不再稳定发生时序违例的结果,并将其对应的周期值记录为period_trigger_1,如图7中的时序跳变点k1;从n 1个测试结果中找出其测试结果为刚好不再发生稳定不发生时序违例的结果,并将其对应的周期值记录为period_trigger_m,如图7中的时序跳变点k4;最后,将周期值period_trigger_1、周期值period_trigger_m以及位于周期值period_trigger_1和周期值period_trigger_m之间的测试周期值(假设有m-2个)取平均值,得到时钟信号的第一周期值,可以如下公式计算得到:

[0075][0076]

其中,period_avg为时钟信号的周期值。其中,m小于或者等于n 1。

[0077]

在实施例中,以第二测试路径测试为例,首先分别对n 1个测试周期值进行测试,得到n 1个测试结果并记录。这n 1个测试结果可以包括无法正确接收数据信号、能够正确接收数据信号、稳定发生无法正确接收数据信号的跳变和稳定不发生无法正确接收数据信号的跳变。然后从n 1个测试结果中找出其测试结果为刚好不再稳定发生无法正确接收数据信号的结果,并将其对应的周期值记录为period_trigger_1;从n 1个测试结果中找出其测试结果为刚好不再稳定不发生无法正确接收数据信号的结果,并将其对应的周期值记录为period_trigger_m;最后,将周期值period_trigger_1、周期值period_trigger_m以及位于周期值period_trigger_1和周期值period_trigger_m之间的测试周期值(假设有m-2个)取平均值,得到时钟信号的第二周期值。同理,按照这个方法还可以确定第三周期值。

[0078]

以上所述,仅为本技术的示例性实施例而已,并非用于限定本技术的保护范围。一般来说,本技术的多种实施例可以在硬件或专用电路、软件、逻辑或其任何组合中实现。例如,一些方面可以被实现在硬件中,而其它方面可以被实现在可以被控制器、微处理器或其它计算装置执行的固件或软件中,尽管本技术不限于此。

[0079]

通过示范性和非限制性的示例,上文已提供了对本技术的示范实施例的详细描述。但结合附图和权利要求来考虑,对以上实施例的多种修改和调整对本领域技术人员来

说是显而易见的,但不偏离本发明的范围。因此,本发明的恰当范围将根据权利要求确定。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。