1.本发明涉及时钟树技术领域,特别是涉及一种鱼骨状时钟树及实现方法。

背景技术:

2.时钟树,是个由许多缓冲单元(buffer/inv cell)平衡搭建的网状结构,它有一个源点,一般是时钟输入端(clock input port),也有可能是design内部某一个单元输出脚(cell output pin),由一级一级的缓冲单元搭建而成,衡量时钟树质量的关键因子包括:时钟树长度,时钟树公共路径,时钟树信号转换时间(clock transition time),时钟树漂移(clock skew),时钟树噪声,时钟占空比。

3.时钟树构建方案是芯片后端物理设计实现中的一个非常重要的步骤,时钟树的质量直接关乎芯片的电能消耗以及芯片运行速度。高算力芯片追逐极致的速度以及极致的功耗,物联网芯片追逐极致功耗。但无论哪种芯片,怎样构建一条级数少、公共路径多、噪声干扰小、时序易于收敛的时钟树是芯片后端里设计者需要耗费精力和大量时间来解决的问题。

4.传统的时钟树在搭建时从pll先引出一个缓冲单元,然后以这个缓冲单元为源头设置两个次一级的缓冲单元,次一级的缓冲单元下再设置第三级的缓冲单元,以此类推直到缓冲单元连接到芯片的子模块。由传统的时钟树的搭建方法可知,从pll开始到每个子模块的时钟树级数相同,距离pll近的子模块和距离远的子模块具有相同的级数,同时多个子模块之间存在同步的时序检查。

5.本领域人员知晓过多的时钟缓冲器会造成时钟树长度长,时钟树功耗大,容易造成通道布线拥塞,时钟树布线占用资源多,时钟树上噪声大,同时,时钟树上缓冲器单元多也会造成时钟树分叉早公共路径少,由ocv占掉的时钟周期多,最终的时序收敛困难。

6.因此需要对现有的时钟树的搭建方法进行改进,降低芯片功耗,降低时序收敛的难度。

技术实现要素:

7.本发明的目的是:提供一种新的时钟树及实现方法,降低芯片功耗,降低时序收敛的难度。

8.为了实现上述目的,本发明提供了一种鱼骨状时钟树,包括一条主时钟树和若干条子时钟树,所述主时钟树从pll引出,所述子时钟树从主时钟树引出,所述子时钟树设置有若干时钟分叉点,所述时钟分叉点作为传统时钟树的源头建立传统时钟树。

9.进一步的,所述主时钟树设置于芯片的中轴线上。

10.进一步的,所述主时钟树包括若干依次连接的第一缓存单元,所述子时钟树包括若干依次连接的第二缓冲单元,所述子时钟树从相邻两个第一缓存单元之间的连接线上引出。

11.进一步的,所述主时钟树的第一缓存单元设置于芯片的子模块之外,所述第二缓

存单元穿过芯片的子模块,被子时钟树穿过的子模块内包括若干个第二缓存单元,相邻两个第二缓存单元之间引出时钟分叉点。

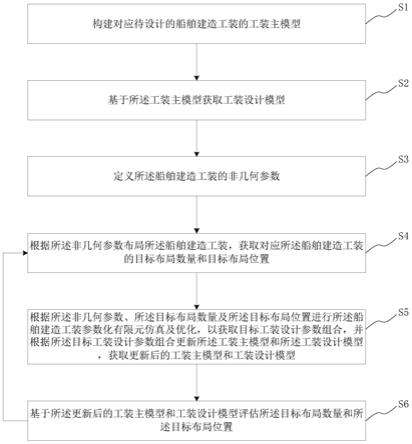

12.本发明还公开了一种鱼骨状时钟树的实现方法,包括:

13.获取芯片的子模块布局。

14.从芯片的pll引出主时钟树并根据子模块布局设置主时钟树使主时钟树位于芯片的中轴线上。

15.从主时钟树上引出若干条子时钟树,并使子时钟树均匀的分布在主时钟树两侧。

16.从子时钟树上引出时钟分叉点,并以时钟分叉点作为传统时钟树的源头建立传统时钟树。

17.进一步的,所述主时钟树包括若干依次连接的第一缓存单元,所述子时钟树包括若干依次连接的第二缓冲单元,所述子时钟树从相邻两个第一缓存单元之间的连接线上引出。

18.进一步的,所述主时钟树的第一缓存单元设置于芯片的子模块之外,所述第二缓存单元穿过芯片的子模块,被子时钟树穿过的子模块内包括若干个第二缓存单元,相邻两个第二缓存单元之间引出时钟分叉点。

19.进一步的,所述芯片的子模块布局包括单层子模块布局和双层子模块布局。

20.进一步的,当芯片为单层子模块布局时,从主时钟树引出的子时钟树将芯片分割为若干个子区域,在每个子区域通过子时钟树引出的时钟分叉点建立传统时钟树。

21.进一步的,当芯片为双层子模块布局时,所述芯片的第一层子模块上设置由多个均匀分布的第二层子模块,从芯片的pll引出主时钟树并使主时钟树设置于第二层子模块的中轴线位置,从主时钟树上引出若干子时钟树穿过第二层子模块使位于主时钟树同一层同一列的第二层子模块位于同一子时钟树上,所述第二层子模块内设置有时钟分叉点,所述时钟分叉点作为传统时钟树的源头设置传统时钟树。

22.本发明实施例一种鱼骨状时钟树及实现方法与现有技术相比,其有益效果在于:通过建立主时钟树和子时钟树建立鱼骨状的时钟树结构,减少了pll到芯片子模块间的缓冲单元,降低了芯片功耗;主时钟树和子时钟树还起到公共路径的作用,ocv占掉的时钟周期少,最终的时序收敛容易。

附图说明

23.图1是本发明背景技术中传统时钟树的结构示意图;

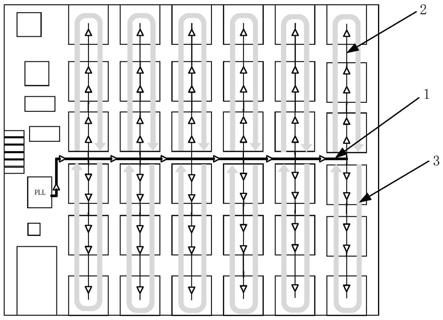

24.图2是本发明芯片为单层子模块布局时鱼骨状时钟树的设置示意图;

25.图3是本发明芯片的双层子模块布局示意图;

26.图4是本发明芯片为双层子模块布局时鱼骨状时钟树的设置示意图;

27.图5是本发明子时钟树设置时钟分叉点的结构示意图。

28.图中,1、主时钟树;2、子时钟树;3、数据流流向。

具体实施方式

29.下面结合附图和实施例,对本发明的具体实施方式作进一步详细描述。以下实施例用于说明本发明,但不用来限制本发明的范围。

30.实施例1:

31.参照附图2、附图4和附图5,本发明公开了一种鱼骨状时钟树,包括一条主时钟树和若干条子时钟树,所述主时钟树从pll引出,所述子时钟树从主时钟树引出,所述子时钟树设置有若干时钟分叉点,所述时钟分叉点作为传统时钟树的源头建立传统时钟树。

32.在本实施例中,所述主时钟树设置于芯片的中轴线上。将主时钟树设置在芯片的中轴线上或芯片多个子模块的中心位置,使芯片的子模块尽可能的均匀的分布在主时钟树的两侧,可以从物理距离上减少布线的长度和布线的数量。同时当主时钟树位于芯片的中轴线上时,子时钟树也可以方便的,均匀的将子模块连接在一起。设置子时钟树时也应当考虑芯片的实际子模块的布局,根据子模块的数量和位置设置子时钟树。

33.在本实施例中,所述主时钟树包括若干依次连接的第一缓存单元,所述子时钟树包括若干依次连接的第二缓冲单元,所述子时钟树从相邻两个第一缓存单元之间的连接线上引出。

34.在本实施例中,主时钟树上的多个第一缓存单元组成主时钟树路径,所述子时钟树上的多个第二缓存单元组成次级时钟树路径。

35.在本实施例中,所述主时钟树的第一缓存单元设置于芯片的子模块之外,所述第二缓存单元穿过芯片的子模块,被子时钟树穿过的子模块内包括若干个第二缓存单元,相邻两个第二缓存单元之间引出时钟分叉点。

36.一种可选的实施方式为:子模块内设置两个第二缓存单元,两个第二缓存单元之间的连线上引出时钟分叉点。

37.在本实施例中,通过建立主时钟树和子时钟树建立鱼骨状的时钟树结构,减少了pll到芯片子模块间的缓冲单元,降低了芯片功耗;主时钟树和子时钟树还起到公共路径的作用,ocv占掉的时钟周期少,最终的时序收敛容易。

38.实施例2:

39.本发明还公开了一种鱼骨状时钟树的实现方法,将实施例1中的鱼骨状时钟树应用到芯片中,主要包括如下步骤:

40.步骤1、获取芯片的子模块布局。

41.步骤2、从芯片的pll引出主时钟树并根据子模块布局设置主时钟树使主时钟树位于芯片的中轴线上。

42.步骤3、从主时钟树上引出若干条子时钟树,并使子时钟树均匀的分布在主时钟树两侧。

43.步骤4、从子时钟树上引出时钟分叉点,并以时钟分叉点作为传统时钟树的源头建立传统时钟树。

44.在步骤1中,由于不同的芯片在设计时有不同数量的子模块,且这些子模块的排列位置也不尽相同,因此在将鱼骨状的时钟树应用到不同芯片时应当考虑芯片的实际子模块布局。

45.在本实施例中,所述芯片的子模块布局包括单层子模块布局和双层子模块布局。附图2为单层子模块的芯片示意图,附图3为双层子模块的芯片示意图。

46.在步骤2中,将主时钟树设置在芯片的中轴线上或芯片多个子模块的中心位置,使芯片的子模块尽可能的均匀的分布在主时钟树的两侧,可以从物理距离上减少布线的长度

和布线的数量。同时当主时钟树位于芯片的中轴线上时,子时钟树也可以方便的,均匀的将子模块连接在一起。设置子时钟树时也应当考虑芯片的实际子模块的布局,根据子模块的数量和位置设置子时钟树。

47.在步骤3中,所述主时钟树包括若干依次连接的第一缓存单元,所述子时钟树包括若干依次连接的第二缓冲单元,所述子时钟树从相邻两个第一缓存单元之间的连接线上引出。

48.在步骤4中,从子时钟树上引出时钟分叉点,并以时钟分叉点作为传统时钟树的源头建立传统时钟树。参照附图5,子时钟树上引出的时钟分叉点上设置有第三缓冲单元,并以第三缓冲单元作为传统时钟树的源头构建传统时钟树。

49.在本实施例中,所述传统时钟树的结构和设置方法为,确定一个缓冲单元作为源头,并在源头的缓存单元下设置两个次一级的缓存单元,在次一级的缓存单元下设置第三级的缓存单元,即上一级的缓存单元下设置有两个次一级的缓存单元。重复建立多级缓存单元直到连接所有芯片子模块。

50.在本实施例中,所述主时钟树的第一缓存单元设置于芯片的子模块之外,所述第二缓存单元穿过芯片的子模块,被子时钟树穿过的子模块内包括若干个第二缓存单元,相邻两个第二缓存单元之间引出时钟分叉点。

51.由于实施例2是在实施例1的基础上进行撰写的,因此部分重复的技术特征不在赘述。

52.实施例3:

53.在实施例2的基础上,参照附图2,当芯片为单层子模块布局时,从主时钟树引出的子时钟树将芯片分割为若干个子区域,在每个子区域通过子时钟树引出的时钟分叉点建立传统时钟树。

54.实施例4:

55.在实施例2的基础上,当芯片为双层子模块布局时,所述芯片的第一层子模块上设置由多个均匀分布的第二层子模块,从芯片的pll引出主时钟树并使主时钟树设置于第二层子模块的中轴线位置,从主时钟树上引出若干子时钟树穿过第二层子模块使位于主时钟树同一层同一列的第二层子模块位于同一子时钟树上,所述第二层子模块内设置有时钟分叉点,所述时钟分叉点作为传统时钟树的源头设置传统时钟树。

56.参照附图3、4,所述芯片的双层子模块布局具体为:在第一层子模块即附图4的大方框上设置第二层子模块。所述第二层子模块有多个。

57.在本实施例中,当建立鱼骨状时钟树时,选取多个第二层子模块的中轴线位置设置主时钟树,然后案子第二层子模块的排列位置引出子时钟树,所述子时钟树穿过第二层子模块。附图4中的标号1是一条主时钟树,这条主时钟树直接从pll提供,在满足时钟电器性能(时钟transition time)的情况下横向分布在芯片中间,标号2是从主时钟树上送出的穿过子模块的时钟树,主时钟树和子时钟树共同构成了鱼骨状时钟树结构。

58.在本实施例中,附图4中的标号3表示数据流流向,数据由芯片主控制逻辑产生。举例说明如下:主控制产生的数据由北侧的h12子模块处理之后再流入h6进行处理,进而进入h0进行处理,h0处理2次之后反向送回h6,h6再处理一次送回给h12,h12处理之后再送回给芯片主控单元,完成一次数据处理。图4中显示了12条数据处理链路。

59.参照附图5,子模块h12中触发器的时钟树的公共路径是buffer0、buffer4,buffer4后面构建传统的clocktree(同图1的方式),对于h12内部的触发器来说时钟的非公共路径控制在h12子模块内,从pll开始直至buffer4都属于时钟公共路径;h6模块中触发器的时钟公共路径是buffer0、buffer1、buffer2、buffer5,同理,buffer5后面构建传统的时钟树,对于h6内部的触发器来说时钟的非公共路径被控制在h6子模块内部,从pll开始直至buffer5时钟路径都属于公共时钟路径。对于子模块h12和h6之间需要交互的触发器来说时钟公共路径只到buffer0,h12和h6内部的触发器时钟之间的偏差时buffer1 buffer2的delay,在逻辑设计阶段充分考虑这段接口,时序裕量充足。

60.若附图4中的芯片结构直接采用传统时钟树连接pll和子模块,则其连接方式为附图1中的连接方式。从pll开始到每个子模块的时钟树级数相同,物理上,距离pll距离近的子模块h0、h6、h12、h18、h24、h30按照物理距离不需要那么多的时钟树缓冲器单。同时h0、h6、h12、h18、h24、h30之间存在同步的时序检查。过多的时钟缓冲器会造成时钟树长度长,时钟树功耗大,容易造成通道布线拥塞,时钟树布线占用资源多,时钟树上噪声大,同时,时钟树上缓冲器单元多也会造成时钟树分叉早公共路径少,由ocv占掉的时钟周期多,最终的时序收敛困难。

61.综上,本发明实施例提供一种鱼骨状时钟树及实现方法与现有技术相比,其有益效果在于:通过建立主时钟树和子时钟树建立鱼骨状的时钟树结构,减少了pll到芯片子模块间的缓冲单元,降低了芯片功耗;主时钟树和子时钟树还起到公共路径的作用,ocv占掉的时钟周期少,最终的时序收敛容易。

62.以上所述仅是本发明的优选实施方式,应当指出,对于本技术领域的普通技术人员来说,在不脱离本发明技术原理的前提下,还可以做出若干改进和替换,这些改进和替换也应视为本发明的保护范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。