1.本发明属于数字模拟混合电路设计领域,特别涉及一种数模混合电路中数字版图布局的方法及其装置。

背景技术:

2.在所有设计到模拟信号和数字信号处理的电路中,模数、数模转换都是必不可少的组成部分,这就造就了模拟信号转数字信号(adc)、数字信号转模拟信号(dac)的地位,任何系统都离不开它,现在的系统几乎都是数字与模拟混合信号系统,而且不同的应用场景需要选用不同的adc与dac。随着市场需求越来越大,adc和dac芯片研发周期的长短,尤其是设计实现方法,大大地影响到其市场的占有率。因此,如何能够快速完成其数字版图布局(layout),减少面积,缩短研发周期尤为重要,而这其中数字部分版图的布局有着举足轻重的地位,能快速地确定数字部分版图布局,并且面积小,占用绕线资源不多,能够让整个数字模拟混合电路版图的顶层top版图工程师更好地去规划和完成芯片版图。

3.现阶段,layout版图工程师直接根据电路原理图导出相应的电子元器件,然后根据电路原理图和结合工艺生产规则去进行器件的布局和连线。但这种方法不利于多位版图工程师协同工作,对于数字模拟混合电路中一些可能会被重复用到的逻辑单元,如inv(反向器)、nand(与非门)等,版图工程师也不能很好的处理,使得这些逻辑单元不能够很好的被重复调用,这样会增加版图设计上的反复迭代,影响芯片的设计周期,从而降低芯片设计的效率。

技术实现要素:

4.本发明所要解决的技术问题在于,提供一种数字模拟混合电路中数字版图布局的方法及装置,能减少版图设计上标准单元的反复迭代,提高芯片的设计效率。

5.为了解决上述技术问题,本发明提供了一种数字模拟混合电路中数字版图布局的方法,具体为:

6.根据获取的设计网表和所用工艺的设计规则,分别确定引脚宽度值最大的逻辑单元和最小版图走线设计规则,并在所述引脚宽度值最大的逻辑单元上添加保护环,构建第一标准单元;其中,所述设计网表中记录了多个逻辑单元、每个逻辑单元的设计参数和设计规则;

7.根据所述第一标准单元的版图高度和所述最小版图走线设计规则,对所述设计网表上记录的逻辑单元添加保护环,创建标准单元库;

8.获取待布局的数字模拟混合电路,并根据所述待布局的数字模拟混合电路中的各数字模块,调用所述标准单元库,构建版图模块,继而根据构建的版图模块,对数字模拟混合电路中数字版图进行布局。

9.进一步地,所述根据获取的设计网表,确定引脚宽度值最大的逻辑单元,具体为:

10.从设计网表中提取逻辑单元类型,并分别对比各个逻辑单元中的pmos管和nmos管

的引脚宽度值,得到pmos管和nmos管的引脚宽度值最大的逻辑单元。

11.进一步地,所述在所述引脚宽度值最大的逻辑单元上添加保护环,构建第一标准单元,具体为:

12.在所述引脚宽度值最大的逻辑单元中的pmos管和nmos管上下两侧添加保护环,并基于满足所述最小版图走线设计规则,对添加保护环后的引脚宽度值最大的逻辑单元进行版图布局布线,构建所述第一标准单元。

13.进一步地,所述根据所述第一标准单元的版图高度和所述最小版图走线设计规则,对所述设计网表上记录的逻辑单元添加保护环,创建标准单元库,具体为:

14.在设计网表上记录的每个逻辑单元中的pmos管和nmos管上下两侧添加保护环,并基于第一标准单元的版图高度和最小版图走线设计规则,对添加保护环后的每个逻辑单元进行版图布局布线,分别构建各逻辑单元对应的标准单元,组成标准单元库。

15.进一步地,所述获取待布局的数字模拟混合电路,并根据所述待布局的数字模拟混合电路中的各数字模块,调用所述标准单元库,构建版图模块,具体为:

16.获取并分析数字模拟混合电路中的构建各数字模块所需的标准单元,在标准单元库中调用所述各数字模块所需的标准单元进行拼接,完成各个版图模块的构建。

17.进一步地,所述根据构建的版图模块,对数字模拟混合电路中数字版图进行布局,具体为:

18.将构建的版图模块提交至顶层版图,进行版图模块的布局和连线,从而完成对数字模拟混合电路中数字版图的布局。

19.同时,本发明还提供了一种数字模拟混合电路中数字版图布局的装置,包括:第一标准单元模块、标准单元库建立模块和数模分析布局模块;

20.其中,所述第一标准单元模块用于根据获取的设计网表和所用工艺的设计规则,分别确定引脚宽度值最大的逻辑单元和最小版图走线设计规则,并在所述引脚宽度值最大的逻辑单元上添加保护环,构建第一标准单元;

21.所述标准单元库建立模块用于根据所述第一标准单元的版图高度和所述最小版图走线设计规则,对所述设计网表上记录的逻辑单元添加保护环,创建标准单元库;

22.所述数模分析布局模块用于获取待布局的数字模拟混合电路,并根据所述待布局的数字模拟混合电路中的各数字模块,调用所述标准单元库,构建版图模块,继而根据构建的版图模块,对数字模拟混合电路中数字版图进行布局。

23.进一步地,所述根据获取的设计网表,确定引脚宽度值最大的逻辑单元和最小版图走线设计规则,并在所述引脚宽度值最大的逻辑单元上添加保护环,构建第一标准单元,具体为:

24.从设计网表中提取逻辑单元类型,并分别对比各个逻辑单元中的pmos管和nmos管的引脚宽度值,得到pmos管和nmos管的引脚宽度值最大的逻辑单元;在所述引脚宽度值最大的逻辑单元中的pmos管和nmos管上下两侧添加保护环,并基于满足所述最小版图走线设计规则,对添加保护环后的引脚宽度值最大的逻辑单元进行版图布局布线,构建所述第一标准单元。

25.进一步地,所述根据所述第一标准单元的版图高度和所述最小版图走线设计规则,对所述设计网表上记录的逻辑单元添加保护环,创建标准单元库,具体为:

26.在设计网表上记录的每个逻辑单元中的pmos管和nmos管上下两侧添加保护环,并基于第一标准单元的版图高度和最小版图走线设计规则,对添加保护环后的每个逻辑单元进行版图布局布线,分别构建各逻辑单元对应的标准单元,组成标准单元库。

27.进一步地,所述获取待布局的数字模拟混合电路,并根据所述待布局的数字模拟混合电路中的各数字模块,调用所述标准单元库,构建版图模块,继而根据构建的版图模块,对数字模拟混合电路中数字版图进行布局,具体为:

28.获取并分析数字模拟混合电路中的构建各数字模块所需的标准单元,在标准单元库中调用所述各数字模块所需的标准单元进行拼接,完成各个版图模块的构建;将构建的版图模块提交至顶层版图,进行版图模块的布局和连线,从而完成对数字模拟混合电路中数字版图的布局。

29.实施本技术实施例,具有如下的有益效果:

30.本发明能够通过根据逻辑单元以及最小版图走线设计规则,对逻辑单元添加保护环后,建立标准单元库,能够更好地重复调用数字模拟混合电路版图中涉及的标准单元,加快数字部分版图的布局,并且本发明提供的双边保护环涉及方法能更好的预防闩锁效应;创建好标准单元库能够更快更好的构建数字模块,提交到顶层top版图设计师能够更好的规划芯片布局,减少了版图涉及上的反复迭代,提高芯片设计效率,缩短了芯片流片时间。

附图说明

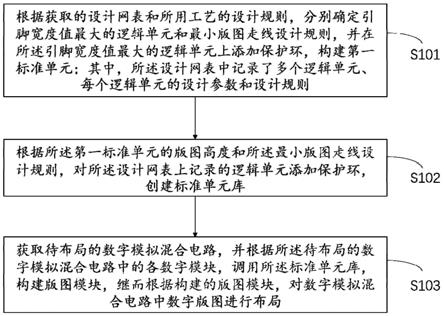

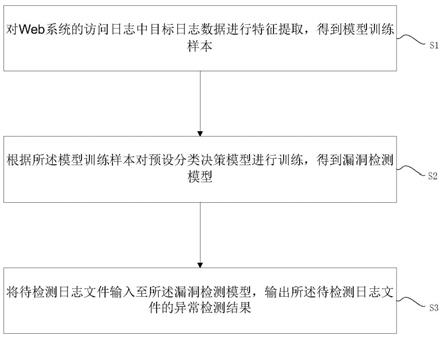

31.图1是本发明实施例中一种数模混合电路中数字版图布局的方法的步骤流程图;

32.图2是本发明实施例中各个版图图层及形状含义的示意图;

33.图3是本发明实施例中添加保护环结构的示意图;

34.图4是本发明实施例中保护环的两种类型的示意图;

35.图5是本发明实施例中标准单元以nwell为界线进行拼接的示意图;

36.图6是本发明实施例中标准单元以保护环的active层为边界进行拼接的示意图;

37.图7是本发明实施例中标准单元以连线m2金属层2之间的最小间距为边界进行拼接的示意图;

38.图8是本发明实施例中若干个标准单元构建的版图模块进行的数字版图布局的示意图;

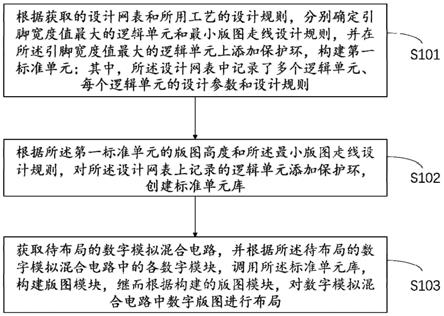

39.图9是本发明实施例中一种本发明实施例中一种数模混合电路中数字版图布局的装置的结构图。

具体实施方式

40.为了使本发明的目的、技术方案及优点更加清楚明白,以下将结合本发明中的附图,对本发明实施例中的技术方案进行进一步详细说明。显然,此所描述的实施例仅是本发明一部分实施例,而不是全部实施例,并不用于限定本发明。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所用其他实施例,都属于本发明保护的范围。

41.请参阅图1,其是本发明实施例提供的一种数模混合电路中数字版图布局的方法,具体为以下步骤:

42.s101:根据获取的设计网表和所用工艺的设计规则,分别确定引脚宽度值最大的逻辑单元和最小版图走线设计规则,并在所述引脚宽度值最大的逻辑单元上添加保护环,构建第一标准单元;其中,设计网表中记录了多个逻辑单元、每个逻辑单元的设计参数和设计规则。

43.进一步地,步骤s101中根据获取的设计网表,确定引脚宽度值最大的逻辑单元,具体为:从设计网表中提取逻辑单元类型,并分别对比各个逻辑单元中的pmos管和nmos管的引脚宽度值,得到pmos管和nmos管的引脚宽度值最大的逻辑单元。

44.在本实施例中,使用以逻辑单元的名称为关键词从设计网表中提取逻辑单元类型,其中逻辑单元类型包括但不限于inv(反相器)、nand2(二输入与门)、or3(三输入或门)和tgate(t门逻辑)。逻辑单元的各个版图图层及形状的含义如图2示。

45.在本实施例中,请参阅图2,nw为nwell衬底层,od为active层,po为ploy氧化层,pp为pplus扩散层,np为nplus扩散层,co为active层和metal1之间的通孔或ploy层和metal1之间的通孔,m1为metal1金属层1,via1为m1和m2之间的通孔,m2为metal2金属层2。

46.在本实施例中,逻辑单元的设计参数包括但不限于:管脚宽度值、输入端、栅长度、水平垂直pin脚格点间距和最小单元间距;设计规则包括但不限于:走线设计规则、安全间距规则、通孔设计规则和文字设计规则。最小版图走线设计规则属于按最小走线和最小安全间距进行版图设计的规则。

47.在本实施例中,对比逻辑单元中pmos管和nmos管的引脚宽度值,所有逻辑单元pmos管的引脚宽度值是一致的,nmos管属tgate的引脚宽度值最大。

48.进一步地,在步骤s101中引脚宽度值最大的逻辑单元上添加保护环,构建第一标准单元,具体为:在所述引脚宽度值最大的逻辑单元中的pmos管和nmos管上下两侧添加保护环,并基于满足所述最小版图走线设计规则,对添加保护环后的引脚宽度值最大的逻辑单元进行版图布局布线,构建所述第一标准单元。

49.优选地,在本实施例中,参考图3,对tgate逻辑单元中的pmos管和nmos管上下两侧添加保护环,基于各个掩膜层满足最小版图走线设计规则的情况下,完成tgate逻辑单元版图布局布线,建立tgate所属的第一标准单元。

50.其中,保护环有两种类型,请参阅图4,一种是能够为pmos管实现收集空穴的保护环301,由nwell衬底、active层、ploy氧化层、nplus扩散孔、contact通孔和metal金属层形成;二是能够为nmos管实现收集电子的保护环302,由active层、ploy氧化层、pplus扩散层、contact通孔和metal金属层形成。

51.s102:根据所述第一标准单元的版图高度和所述最小版图走线设计规则,对所述设计网表上记录的逻辑单元添加保护环,创建标准单元库。

52.进一步地,在步骤s102中根据所述第一标准单元的版图高度和所述最小版图走线设计规则,对设计网表上记录的逻辑单元添加保护环,创建标准单元库,具体为:在设计网表上记录的每个逻辑单元中的pmos管和nmos管上下两侧添加保护环,并基于第一标准单元的版图高度和最小版图走线设计规则,对添加保护环后的每个逻辑单元进行版图布局布线,分别构建各逻辑单元对应的标准单元,组成标准单元库。

53.优选地,在本实施例中,基于第一标准单元的版图高度和最小版图走线设计规则,对设计网表中记录的inv、nand2、or3等逻辑单元进行版图布局布线,这里要求inv、nand2、

or3等逻辑单元进行布局布线后对应其所属的inv、nand2、or3等标准单元的版图高度和本实施例第一标准单元(即tgate标准单元)版图高度完全一致,且都要按照最小版图走线设计规则进行布局布线,构建出inv、nand2、or3等逻辑单元对应的inv、nand2、or3等标准单元,并把构建的标准单元存储于标准单元库中。

54.s103:获取待布局的数字模拟混合电路,并根据所述待布局的数字模拟混合电路中的各数字模块,调用所述标准单元库,构建版图模块,继而根据构建的版图模块,对数字模拟混合电路中数字版图进行布局。

55.进一步地,所述获取待布局的数字模拟混合电路,并根据所述待布局的数字模拟混合电路中的各数字模块,调用所述标准单元库,构建版图模块,具体为:获取并分析数字模拟混合电路中的构建各数字模块所需的标准单元,在标准单元库中调用各数字模块所需的标准单元进行拼接,完成各个版图模块的构建。

56.优选地,在本实施例中,根据待布局的数字模拟混合电路,分析待布局的数字模拟混合电路中的各数字模块,并根据此数字模块调用标准单元库中将要应用到的inv标准单元和tgate标准单元,以同一版图高度的inv标准单元和tgate标准单元进行拼接,构建版图模块。其中,一共有三种标准单元拼接方式。

57.第一种拼接方式,请参阅图5(左为inv,右为tgate),根据标准单元之间的nwell为界线,对标准单元进行拼接,随后补齐图层m1层、active层,构建版图模块。其中,该种方法应用于待布局的数字模拟混合电路中的各数字模块纵向连线资源紧张的情况。

58.第二种拼接方式,请参阅图6(左为inv,右为tgate),根据标准单元保护环的active层为边界,对标准单元进行拼接,构建版图模块。其中,该种方法应用于待布局的数字模拟混合电路中的各数字模块连线资源不紧张且避免拼接后引起不必要的版图走线设计规则错误的情况,能够避免保护环中各个图层出现版图走线设计规则错误,特别是contact通孔错位而引起的各种版图走线设计规则错误。

59.第三种拼接方式,请参阅图7(左为inv,右为tgate),根据标准单元以连线m2金属层2之间的最小间距为边界进行拼接,即以两个标准单元用到的两处不同点或者信号的金属层之间最小的间距进行拼接,构建版图模块。其中,该种方法应用于待布局的数字模拟混合电路中的各数字模块连线资源不紧张且整个数字模拟混合电路芯片设计要求的面积尽可能小的情况。

60.在另外一实施例中,多个标准单元进行版图模块拼接布局。当版图模块摆成m

×

1(m代表列数,1代表1行标准单元以进行布局拼接)的情况时,电源网络(vdd/vss)就会直接规划好2条vss和2条vdd;当版图模块摆成m

×

n(m代表列数,n代表行数)的情况时,将vdd或vss进行翻转拼接,降低版图高度,形成的电源网络请参考图8,这样的布局形成的电源网络会比常规标准单元拼接布局后的版图模块的电源网络更强,最终根据数字模拟混合电路原理图完成连线,完成物理验证。

61.进一步地,所述根据构建的版图模块,对数字模拟混合电路中数字版图进行布局,具体为:将构建的版图模块提交至顶层版图,进行版图模块的布局和连线,从而完成对数字模拟混合电路中数字版图的布局。

62.在本实施例中,数字模拟混合电路中数字版图的布局和连线通过提交版图模块数据到top顶层版图,进行版图模块的布局和连线,并且根据top顶层版图进行微调版图模块,

例如一些pin引脚的位置,从而实现数字模拟混合电路中数字版图的布局和连线。

63.进一步地,本发明还提供了一种数字模拟混合电路中数字版图布局的装置,请参考图9,包括:第一标准单元模块901、标准单元库建立模块902和数模分析布局模块903。

64.第一标准单元模块901用于从设计网表中提取逻辑单元类型,并分别对比各个逻辑单元中的pmos管和nmos管的引脚宽度值,得到pmos管和nmos管的引脚宽度值最大的逻辑单元;在所述引脚宽度值最大的逻辑单元中的pmos管和nmos管上下两侧添加保护环,并基于满足最小版图走线设计规则,对添加保护环后的引脚宽度值最大的逻辑单元进行版图布局布线,构建第一标准单元。

65.在本实施例中,使用以逻辑单元的名称为关键词从设计网表中提取逻辑单元类型inv(反相器)、nand2(二输入与非门)、or3(三输入或门)和tgate(t门逻辑),并分别对比各个逻辑单元中的pmos管和nmos管的引脚宽度值,得到pmos管和nmos管的引脚宽度值最大的逻辑单元tgate,在逻辑单元tgate中的pmos管和nmos管上下两侧添加保护环,并基于满足最小版图走线设计规则,构建tgate标准单元,即第一标准单元。

66.标准单元建立模块902用于在设计网表上记录的每个逻辑单元中的pmos管和nmos管上下两侧添加保护环,并基于第一标准单元的版图高度和最小版图走线设计规则,对添加保护环后的每个逻辑单元进行版图布局布线,分别构建各逻辑单元对应的标准单元,组成标准单元库。

67.在本实施例中,从设计网表上记录的inv、nand2和or3逻辑单元中的pmos管和nmos管上下两侧添加保护环,并基于tgate标准单元的版图高度和最小版图走线设计规则,对inv、nand2和or3逻辑单元进行版图布局布线,构建inv、nand2和or3标准单元,组成标准单元库。

68.数模分析布局模块903用于获取并分析数字模拟混合电路中的构建各数字模块所需的标准单元,在标准单元库中调用各数字模块所需的标准单元进行拼接,完成各个版图模块的构建;将构建的版图模块提交至顶层版图,进行版图模块的布局和连线,从而完成对数字模拟混合电路中数字版图的布局。

69.在本实施例中,获取并分析数字模拟混合电路中的一个数字模块所需的标准单元,标准单元库中调用tgate标准单元和inv标准单元,并对tgate标准单元和inv标准单元进行拼接,完成该数字模块对应的版图模块构建。将构建好的各个版图模块提交至顶层版图,进行版图模块的布局和连线,从而完成对数字模拟混合电路中数字版图的布局。

70.实施本发明实施例,具有如下效果:

71.本发明实施例能够更好地将数字模拟混合电路的版图布局进行区分,使得不同的top顶层版图工程师能够更好地协同工作,由一个版图工程师统一设计管理整个数字模拟混合芯片中的标准单元库,其他有需要用到这些标准单元的版图工程师可以灵活调用标准单元库,同时还提出了一种标准单元双边保护环的版图布局设计方法,能够更好地重复调用数字模拟混合电路版图中涉及的标准单元所拼接的版图模块,加快数字版图布局,此外这样实现的版图模块版图布局有着更强的电源网络,进而有着更强地供电能力,并且能够较好地预防闩锁效应。相比于现有技术,本发明实施例的数字版图布局方法能让顶层版图工程师更好地规划芯片布局,减少版图设计上标准单元的反复迭代设计,提高芯片的设计效率,缩短芯片流片时间。

72.以上是本发明的优选实施方式,应当指出,对于本技术领域的普通技术人员来说,在不脱离本发明原理的前提下,还可以做出若干改进和润饰,这些改进和润饰也视为本发明的保护范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。