1.本发明构思涉及包括线识别部的半导体器件。

背景技术:

2.具有高集成度的半导体器件可以在衬底上包括处于同一高度的彼此平行的多个布线。布线数量的增加使得难以检查选自所述多个布线之中的一个布线的位置。例如,难以准确地识别选自彼此平行的多个位线之中的一个位线的位置。

技术实现要素:

3.本发明构思的示例性实施方式提供了半导体器件,该半导体器件提供了彼此平行的多个布线之中的每个布线的位置的相对容易的识别。

4.根据本发明构思的示例性实施方式的一种半导体器件可以包括设置在衬底上的堆叠结构。该堆叠结构包括多个绝缘层和多个电极层。多个沟道结构延伸穿过堆叠结构。第一布线组包括设置在堆叠结构上的多个第一水平布线。所述多个第一水平布线在第一方向上排列并在与第一方向交叉的第二方向上延伸。所述多个第一水平布线中的每个连接到所述多个沟道结构中的对应一个。第二布线组包括设置在堆叠结构上的多个第二水平布线。所述多个第二水平布线在第一方向上排列并在第二方向上延伸。所述多个第二水平布线中的每个连接到所述多个沟道结构中的对应一个。第一线识别部设置在第一布线组与第二布线组之间。所述多个绝缘层和所述多个电极层在与第一方向和第二方向交叉的第三方向上交替地堆叠。所述多个沟道结构中的每个在第三方向上延伸。

5.根据本发明构思的示例性实施方式的一种半导体器件可以包括第一布线组,该第一布线组包括设置在衬底上的多个第一水平布线。所述多个第一水平布线在第一方向上排列并在与第一方向交叉的第二方向上延伸。第二布线组包括设置在衬底上的多个第二水平布线。所述多个第二水平布线在第一方向上排列并在第二方向上延伸。线识别部设置在第一布线组与第二布线组之间。线识别部位于重叠区域中,该重叠区域设置在所述多个第一水平布线之中最靠近该线识别部的一个第一水平布线与所述多个第二水平布线之中最靠近该线识别部的一个第二水平布线之间。

6.根据本发明构思的示例性实施方式的一种半导体器件可以包括设置在衬底上的源极线。包括多个绝缘层和多个电极层的堆叠结构设置在源极线上。多个沟道结构穿过堆叠结构并接触源极线。第一布线组包括设置在堆叠结构上的多个第一水平布线。所述多个第一水平布线在第一方向上排列并在与第一方向交叉的第二方向上延伸。所述多个第一水平布线中的每个连接到所述多个沟道结构中的对应一个。第二布线组包括设置在堆叠结构上的多个第二水平布线。所述多个第二水平布线在第一方向上排列并在第二方向上延伸。所述多个第二水平布线中的每个连接到所述多个沟道结构中的对应一个。第一线识别部设置在第一布线组与第二布线组之间。第三布线组包括设置在衬底上的多个第三水平布线。所述多个第三水平布线在第二方向上排列并在第一方向上延伸。所述多个第三水平布线中

的每个连接到所述多个电极层中的对应一个。第四布线组包括设置在衬底上的多个第四水平布线。所述多个第四水平布线在第二方向上排列并在第一方向上延伸。所述多个第四水平布线中的每个连接到所述多个电极层中的对应一个。所述多个绝缘层和所述多个电极层在与第一方向和第二方向交叉的第三方向上交替地堆叠。所述多个沟道结构中的每个在第三方向上延伸。

附图说明

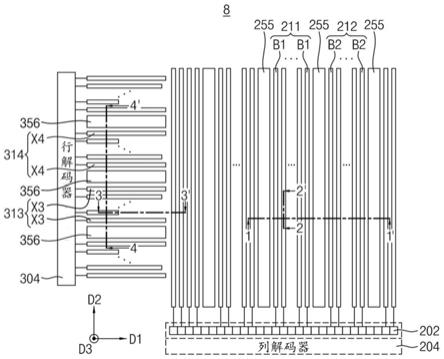

7.图1是根据本发明构思的示例性实施方式的半导体器件的示意图,示出了图2的部分8。

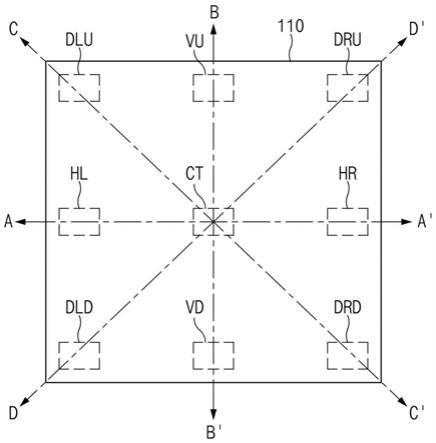

8.图2是根据本发明构思的示例性实施方式的半导体器件的示意图。

9.图3至图8是示出根据本发明构思的示例性实施方式的图1的一些元件的俯视图。

10.图9是根据本发明构思的示例性实施方式的半导体器件的沿着图1的线1

‑

1'截取的剖视图。

11.图10是根据本发明构思的示例性实施方式的半导体器件的沿着图1的线2

‑

2'截取的剖视图。

12.图11至图13是示出根据本发明构思的示例性实施方式的图9的半导体器件的一些元件的局部视图。

13.图14至图16是分别示出根据本发明构思的示例性实施方式的图9的半导体器件的部分36至部分38的放大图。

14.图17和图18是根据本发明构思的示例性实施方式的半导体器件的剖视图。

15.图19和图20是根据本发明构思的示例性实施方式的半导体器件的示意图。

具体实施方式

16.图1和图2是用于描述根据本发明构思的示例性实施方式的半导体器件的示意图。图1可以是详细示出图2的部分8的放大图。图3至图8是示出图1的一些元件的俯视图。图9是用于描述根据本发明构思的示例性实施方式的半导体器件的沿着图1的线1

‑

1'截取的剖视图,图10是沿着图1的线2

‑

2'截取的剖视图。图11至图13是示出图9的一些元件的局部视图。图14至图16是分别示出图9的部分36至部分38的放大图。图17是用于描述根据本发明构思的示例性实施方式的半导体器件的沿着图1的线3

‑

3'截取的剖视图,图18是沿着图1的线4

‑

4'截取的剖视图。根据本发明构思的示例性实施方式的半导体器件可以包括三维(3d)闪存,诸如垂直nand(vnand)闪存。

17.参照图1,根据本发明构思的示例性实施方式的半导体器件可以包括页缓冲器202、列解码器204、行解码器304、包括多个第一水平布线b1的第一布线组211、包括多个第二水平布线b2的第二布线组212、多个第一线识别部255、包括多个第三水平布线x3的第三布线组313、包括多个第四水平布线x4的第四布线组314以及多个第二线识别部356。在示例性实施方式中,多个第一线识别部255和多个第二线识别部356中的每个可以对应于计数图案或辨别物。多个第一水平布线b1和多个第二水平布线b2中的每个可以对应于位线。例如,在示例性实施方式中,多个第一线识别部255中的每个可以是位线计数图案。

18.多个第一水平布线b1和多个第二水平布线b2可以彼此平行地设置。多个第一水平

布线b1和多个第二水平布线b2可以在第一方向d1上排列(例如,间隔开),并且可以均在与第一方向d1交叉的第二方向d2上延伸。如图1的示例性实施方式所示,第二方向d2可以垂直于第一方向d1。然而,本发明构思的示例性实施方式不限于此,第二方向d2可以以各种不同的角度与第一方向d1交叉。

19.在示例性实施方式中,多个第一水平布线bl和多个第二水平布线b2中的每个可以具有基本相同的宽度(例如,在第一方向d1上的长度)。在示例性实施方式中,第一布线组211可以包括在约2至约10,000的范围内的数量的第一水平布线b1。例如,第一布线组211可以包括约2,000个第一水平布线b1。第二布线组212可以包括在约2至约10,000的范围内的数量的第二水平布线b2。例如,第二布线组212可以包括约2,000个第二水平布线b2。

20.选自多个第一线识别部255之中的一个第一线识别部255可以(例如,在第一方向d1上)设置在第一布线组211与第二布线组212之间。例如,选自多个第一线识别部255之中的一个第一线识别部255可以(例如,在第一方向d1上)设置在多个第一水平布线b1与多个第二水平布线b2之间。选自多个第一线识别部255之中的一个第一线识别部255可以设置在第一重叠区域中,该第一重叠区域设置在多个第一水平布线b1之中最靠近所述一个第一线识别部255的一个第一水平布线b1与多个第二水平布线b2之中最靠近所述一个第一线识别部255的一个第二水平布线b2之间。在示例性实施方式中,选自多个第一线识别部255之中的一个第一线识别部255可以仅位于第一重叠区域中,并且可以不突出到第一重叠区域之外。

21.第一布线组211和第二布线组212可以在第二方向d2上与页缓冲器202相邻设置。页缓冲器202可以在第二方向d2上与列解码器204相邻设置。多个第一水平布线b1和多个第二水平布线b2中的每个可以连接到页缓冲器202。如图1的示例性实施方式所示,多个第一线识别部255可以不连接到页缓冲器202。

22.第一布线组211和第二布线组212可以在第一方向d1上与第三布线组313和第四布线组314相邻设置。多个第三水平布线x3和多个第四水平布线x4可以彼此平行地设置。多个第三水平布线x3和多个第四水平布线x4可以在第二方向d2上排列(例如,间隔开)。多个第三水平布线x3和多个第四水平布线x4中的每个可以在第一方向d1上延伸。在示例性实施方式中,多个第三水平布线x3和多个第四水平布线x4中的每个可以具有基本相同的宽度(例如,在第二方向d2上的长度)。

23.选自多个第二线识别部356之中的一个第二线识别部356可以(例如,在第二方向d2上)设置在第三布线组313与第四布线组314之间。例如,选自多个第二线识别部356之中的一个第二线识别部356可以(例如,在第二方向d2上)设置在多个第三水平布线x3与多个第四水平布线x4之间。选自多个第二线识别部356之中的一个第二线识别部356可以设置在第二重叠区域中,该第二重叠区域在多个第三水平布线x3之中最靠近所述一个第二线识别部356的一个第三水平布线x3与多个第四水平布线x4之中最靠近所述一个第二线识别部356的一个第四水平布线x4之间。在示例性实施方式中,选自多个第二线识别部356之中的一个第二线识别部356可以仅位于第二重叠区域中,并且可以不突出到第二重叠区域之外。

24.第三布线组313和第四布线组314可以在第一方向d1上与行解码器304相邻设置。多个第三水平布线x3和多个第四水平布线x4中的每个可以连接到行解码器304。多个第二线识别部356可以不连接到行解码器304。

25.参照图2,根据本发明构思的示例性实施方式的半导体器件可以包括存储单元阵列100、页缓冲器202、列解码器204和行解码器304。如图1的示例性实施方式所示,第一布线组211、第二布线组212、第三布线组313和第四布线组314可以设置在存储单元阵列100中。

26.如图1

‑

2的示例性实施方式所示,存储单元阵列100可以在第一方向dl上与行解码器304相邻设置。存储单元阵列100可以在第二方向d2上与列解码器204相邻设置。页缓冲器202可以(例如,在第二方向d2上)设置在存储单元阵列100与列解码器204之间。在示例性实施方式中,列解码器204可以对应于y解码器。页缓冲器202可以包括多个感测放大器。行解码器304可以对应于x解码器或字线解码器。

27.参照图3至图8的示例性实施方式,多个第一线识别部255和多个第二线识别部356中的每个可以具有如图3所示的条形状、如图4所示的包括多个块的形状、如图5所示的包括条形状和多个空的空间的组合的形状、如图6和图7所示的包括在其间具有用于连接的连接部分的多个块的形状、如图8所示的链形状、或诸如其组合的各种大小和形状。

28.参照图9,根据本发明构思的示例性实施方式的半导体器件可以包括衬底51、下水平布线71、连接电极层73、支撑部75、堆叠结构85、多个沟道结构99、第一上绝缘层103、第二上绝缘层105、第三上绝缘层106、多个位插塞(bit plug)107、多个第一水平布线b1、多个第二水平布线b2和多个第一线识别部255。堆叠结构85可以包括交替且重复地堆叠的多个电极层81和多个绝缘层83。

29.多个电极层81和多个绝缘层83可以在与第一方向d1和第二方向d2交叉的第三方向d3上交替地堆叠。例如,如图9的示例性实施方式所示,第三方向d3可以垂直于第一方向d1和第二方向d2,并且可以是衬底51的厚度方向。多个沟道结构99中的每个可以在第三方向d3上延伸。多个第一水平布线b1和多个第二水平布线b2中的每个可以经由多个位插塞107连接到多个沟道结构99中的对应沟道结构的至少一个。多个第一线识别部255可以不电连接到多个沟道结构99。例如,如图9的示例性实施方式所示,半导体器件不包括(例如,在第三方向d3上)设置在多个第一线识别部255与多个沟道结构99之间的任何位插塞107。多个第一线识别部255可以与多个沟道结构99绝缘。第一上绝缘层103和第二上绝缘层105可以(例如,在第三方向d3上)设置在多个第一线识别部255与多个沟道结构99之间。

30.在示例性实施方式中,多个第一水平布线b1可以具有第一节距pl。多个第一水平布线b1中的每个可以具有基本相同的第一水平宽度w1(例如,在第一方向d1上的长度)。多个第一水平布线b1之间的间隔(例如,相邻的第一水平布线b1在第一方向d1上彼此间隔开的长度)可以是第一间隔d11。第一节距p1可以等于第一水平宽度w1和第一间隔d11之和。多个第二水平布线b2可以具有第二节距p2。多个第二水平布线b2中的每个可以具有基本相同的第二水平宽度w2(例如,在第一方向d1上的长度)。多个第二水平布线b2之间的间隔(例如,相邻的第二水平布线b2在第一方向d1上彼此间隔开的长度)可以是第二间隔d22。第二节距p2可以等于第二水平宽度w2和第二间隔d22之和。在示例性实施方式中,第二水平宽度w2可以与第一水平宽度w1基本相同。第二节距p2可以与第一节距p1基本相同。然而,本发明构思的示例性实施方式不限于此。

31.多个第一线识别部255可以设置在与多个第一水平布线b1和多个第二水平布线b2基本相同的高度(例如,在第三方向d3上距衬底51的上表面的距离)处。在示例性实施方式中,多个第一线识别部255、多个第一水平布线b1和多个第二水平布线b2可以包括相同材

料,并且可以基本上同时形成。多个第一线识别部255、多个第一水平布线b1和多个第二水平布线b2中的每个可以具有基本相同的厚度(例如,在第三方向d3上的长度)。在示例性实施方式中,多个第一线识别部255、多个第一水平布线b1和多个第二水平布线b2可以包括金属、金属氮化物、金属氧化物、金属硅化物、导电碳、多晶硅、或诸如其组合的导电层。多个第一线识别部255、多个第一水平布线b1和多个第二水平布线b2的顶表面可以(例如,在第三方向d3上)基本上彼此共面。多个第一线识别部255、多个第一水平布线b1和多个第二水平布线b2的底表面可以(例如,在第三方向d3上)基本上彼此共面。

32.在示例性实施方式中,多个第一线识别部255可以包括与多个第一水平布线bl和多个第二水平布线b2的材料不同的材料。在示例性实施方式中,多个第一线识别部255可以包括空的空间。在示例性实施方式中,多个第一线识别部255和第三上绝缘层106可以包括相同的材料,并且可以同时形成。多个第一线识别部255可以包括绝缘层。

33.多个第一线识别部255中的每个可以具有第三水平宽度w3(例如,在第一方向d1上的长度)。如图9的示例性实施方式所示,第三水平宽度w3可以大于第一水平宽度w1和第二水平宽度w2中的每个。在示例性实施方式中,第三水平宽度w3可以在第一水平宽度w1和第二水平宽度w2中的每个的大小的约2至约20倍的范围内。例如,第三水平宽度w3可以为约300nm。在示例性实施方式中,第一水平宽度w1和第二水平宽度w2中的每个可以在约15nm至约150nm的范围内。选自多个第一线识别部255之中的一个第一线识别部255的侧边缘与多个第一水平布线b1之中最靠近所述一个第一线识别部255的一个第一水平布线b1的相邻侧边缘之间的间隔可以是第三间隔d31。在示例性实施方式中,第三间隔d31可以与第一间隔d11基本相同。选自多个第一线识别部255之中的一个第一线识别部255的侧边缘与多个第二水平布线b2之中最靠近所述一个第一线识别部255的一个第二水平布线b2的相邻侧边缘之间的间隔可以是第四间隔d32。在示例性实施方式中,第四间隔d32可以与第二间隔d22基本相同。在示例性实施方式中,第一间隔d11、第二间隔d22、第三间隔d31和第四间隔d32可以基本相同。

34.在示例性实施方式中,下水平布线71可以对应于源极线或公共源极线(csl)。多个电极层81中邻近堆叠结构85的最下端的至少一个和多个电极层81中邻近堆叠结构85的最上端的至少一个可以均对应于栅极诱导漏极泄漏(gidl)控制线。多个电极层81中的一些可以均对应于字线或虚设字线。多个电极层81中邻近堆叠结构85的最下端并(例如,在第三方向d3上)设置在gidl控制线与字线之间的至少一个可以对应于地选择线(gsl)。多个电极层81中邻近堆叠结构85的最上端并(例如,在第三方向d3上)设置在gidl控制线与字线之间的至少一个可以对应于串选择线(ssl)。

35.下水平布线71可以设置在衬底51上。例如,如图9的示例性实施方式所示,下水平布线71的下表面可以直接接触衬底51的上表面。在示例性实施方式中,衬底51可以包括诸如硅晶片的半导体衬底。下水平布线71可以包括单层或多层。在示例性实施方式中,下水平布线71可以包括金属、金属氮化物、金属硅化物、金属氧化物、导电碳、多晶硅或其组合。例如,下水平布线71可以包括掺杂的多晶硅层。在示例性实施方式中,下水平布线71可以通过将n型或p型杂质注入到衬底51中而形成。连接电极层73和支撑部75可以设置在下水平布线71上。连接电极层73可以设置在下水平布线71与支撑部75之间。例如,如图9的示例性实施方式所示,下水平布线71的上表面可以直接接触连接电极层73的下表面,支撑部75的下表

面可以直接接触连接电极层73的上表面。

36.堆叠结构85可以设置在支撑部75上。例如,堆叠结构85的下表面可以直接接触支撑部75的上表面。在示例性实施方式中,多个电极层81可以包括金属、金属氮化物、金属硅化物、金属氧化物、导电碳、多晶硅或其组合。在示例性实施方式中,多个绝缘层83可以包括硅氧化物、硅氮化物、硅氮氧化物、硅硼氮化物(sibn)、硅碳氮化物(sicn)、低k电介质、高k电介质或其组合。例如,多个绝缘层83可以包括硅氧化物。多个沟道结构99中的每个可以穿过堆叠结构85、支撑部75和连接电极层73,并且可以延伸到下水平布线71的内部。多个沟道结构99可以接触下水平布线71。例如,如图9的示例性实施方式所示,多个沟道结构99的下表面可以处于(例如,在第三方向d3上)低于下水平布线71的上表面的高度。

37.第一上绝缘层103可以设置在堆叠结构85上。例如,如图9的示例性实施方式所示,第一上绝缘层103的下表面可以直接接触堆叠结构85的上表面。第二上绝缘层105可以设置在第一上绝缘层103上。例如,如图9的示例性实施方式所示,第二上绝缘层105的下表面可以直接接触第一上绝缘层103的上表面。多个位插塞107形成为穿过第二上绝缘层105和第一上绝缘层103以直接接触第一水平布线b1和第二水平布线b2的下表面并直接接触多个沟道结构99的上表面。多个第一水平布线b1、多个第二水平布线b2和多个第一线识别部255可以设置在第二上绝缘层105上。例如,如图9的示例性实施方式所示,多个第一水平布线b1、多个第二水平布线b2和多个第一线识别部255的下表面可以直接接触第二上绝缘层105的上表面。覆盖多个第一水平布线b1、多个第二水平布线b2和多个第一线识别部255的第三上绝缘层106可以设置在第二上绝缘层105上。例如,如图9的示例性实施方式所示,第三上绝缘层106的下表面可以直接接触多个第一水平布线b1、多个第二水平布线b2和多个第一线识别部255的上表面和侧表面以及第二上绝缘层105的上表面。

38.在示例性实施方式中,多个位插塞107可以包括金属、金属氮化物、金属硅化物、金属氧化物、导电碳、多晶硅或其组合。在示例性实施方式中,第一上绝缘层103、第二上绝缘层105和第三上绝缘层106可以包括硅氧化物、硅氮化物、硅氮氧化物、sibn、sicn、低k电介质、高k电介质或其组合。

39.参照图10,根据本发明构思的示例性实施方式的半导体器件可以包括衬底51、下水平布线71、连接电极层73、支撑部75、堆叠结构85、多个隔离图案89、多个沟道结构99、第一上绝缘层103、第二上绝缘层105、第三上绝缘层106、多个位插塞107和多个第一水平布线b1。

40.多个隔离图案89中的每个可以在第三方向d3上延伸,并且可以在第二方向d2上排列。多个隔离图案89中的每个可以穿过第一上绝缘层103、堆叠结构85、支撑部75和连接电极层73,并且可以延伸到下水平布线71的内部。例如,如图10的示例性实施方式所示,多个隔离图案89的下表面可以处于(例如,在第三方向d3上)低于下水平布线71的上表面的高度。在示例性实施方式中,多个隔离图案89可以包括硅氧化物、硅氮化物、硅氮氧化物、sibn、sicn、低k电介质、高k电介质或其组合。

41.参照图11的示例性实施方式,多个沟道结构99可以穿过堆叠结构85。第一上绝缘层103可以覆盖堆叠结构85和多个沟道结构99。第二上绝缘层105可以设置在第一上绝缘层103上。第一线识别部255可以设置在第二上绝缘层105上。第一线识别部255可以不电连接到多个沟道结构99。第一线识别部255可以与多个沟道结构99绝缘。第一上绝缘层103和第

二上绝缘层105可以设置在第一线识别部255与多个沟道结构99之间。

42.参照图12的示例性实施方式,第一上绝缘层103可以设置在堆叠结构85上。第二上绝缘层105可以设置在第一上绝缘层103上。第一线识别部255可以设置在第二上绝缘层105上。如图12的示例性实施方式所示,与包括多个沟道结构99的图1的示例性实施方式相比,在示出的局部区域中,半导体器件可以不包括(例如,在第三方向d3上)在衬底51与第一线识别部255之间的多个沟道结构99。第一线识别部255可以不电连接到堆叠结构85的多个电极层81。第一线识别部255可以与多个电极层81绝缘。

43.参照图13的示例性实施方式,半导体器件包括第一虚设接触插塞287,该第一虚设接触插塞287穿过第一上绝缘层103、堆叠结构85、支撑部75和连接电极层73并延伸到下水平布线71的内部。例如,如图13的示例性实施方式所示,第一虚设接触插塞287的下表面可以处于低于下水平布线71的上表面的高度。第一虚设接触插塞287可以直接接触下水平布线71。接触间隔物286可以围绕第一虚设接触插塞287的侧表面。接触间隔物286可以设置在第一虚设接触插塞287与堆叠结构85的多个电极层81和多个绝缘层83之间。接触间隔物286可以提供多个电极层81与第一虚设接触插塞287之间的绝缘结构。

44.第二虚设接触插塞288穿过第二上绝缘层105并接触第一虚设接触插塞287。例如,第二虚设接触插塞288的下表面可以直接接触第一虚设接触插塞287的上表面。接触第二虚设接触插塞288的第一线识别部255可以设置在第二上绝缘层105上。例如,如在图13的示例性实施方式所示,第一线识别部255的下表面可以直接接触第二虚设接触插塞288的上表面。第一线识别部255可以经由第二虚设接触插塞288和第一虚设接触插塞287电连接到下水平布线71。然而,虚设接触插塞的数量在其它示例性实施方式中可以变化,并且至少一个虚设接触插塞可以配置为将第一线识别部255连接到下水平布线71。

45.在示例性实施方式中,接触间隔物286可以包括硅氧化物、硅氮化物、硅氮氧化物、sibn、sicn、低k电介质、高k电介质或其组合。在示例性实施方式中,第一虚设接触插塞287和第二虚设接触插塞288中的每个可以包括金属、金属氮化物、金属硅化物、金属氧化物、导电碳、多晶硅或其组合。

46.参照图14的示例性实施方式,沟道结构99可以包括芯图案97、围绕芯图案97的外部的沟道层96、围绕沟道层96的外部的信息存储图案95和设置在沟道层96上的位垫(bit pad)98。如图14的示例性实施方式所示,信息存储图案95可以包括围绕并直接接触沟道层96的外部的隧道绝缘层91、围绕并直接接触隧道绝缘层91的外部的电荷存储层92以及围绕并直接接触电荷存储层92的外部的阻挡层93。在部分36中,沟道结构99可以穿过电极层81和多个绝缘层83。位插塞107可以穿过第一上绝缘层103,并且可以接触沟道结构99的位垫98。例如,如图14的示例性实施方式所示,位插塞107的下表面可以直接接触位垫98的上表面。

47.在示例性实施方式中,隧道绝缘层91可以包括诸如硅氧化物的绝缘层。电荷存储层92可以包括诸如硅氮化物的绝缘层。阻挡层93可以包括硅氧化物、硅氮化物、硅氮氧化物、sibn、sicn、低k电介质、高k电介质或其组合。沟道层96可以包括多晶硅、非晶硅、单晶硅、或诸如其组合的半导体层。芯图案97可以包括硅氧化物、硅氮化物、硅氮氧化物、sibn、sicn、低k电介质、高k电介质或其组合。位垫98可以包括金属、金属氮化物、金属氧化物、金属硅化物、导电碳、多晶硅、或诸如其组合的导电层。

48.参照图15的示例性实施方式,多个电极层81和多个绝缘层83可以重复且交替地堆叠。沟道结构99可以穿过多个电极层81和多个绝缘层83。沟道结构99可以包括芯图案97、沟道层96和信息存储图案95。信息存储图案95可以包括隧道绝缘层91、电荷存储层92和阻挡层93。

49.参照图16的示例性实施方式,连接电极层73可以设置在下水平布线71与支撑部75之间。例如,如图16的示例性实施方式所示,连接电极层73的下表面可以直接接触下水平布线71的上表面,连接电极层73的上表面可以直接接触支撑部75的下表面。绝缘层83可以设置在支撑部75上。沟道结构99可以穿过绝缘层83和支撑部75,并且可以延伸到下水平布线71的内部。例如,如图16的示例性实施方式所示,沟道结构99的下表面可以处于低于下水平布线71的上表面的高度。连接电极层73可以穿过信息存储图案95的侧表面,并且可以直接接触沟道层96的侧表面。沟道结构99的最下端可以设置在高于下水平布线71的底表面的高度处。沟道层96可以经由连接电极层73电连接到下水平布线71。

50.参照图17,根据本发明构思的示例性实施方式的半导体器件可以包括衬底51、下水平布线71、连接电极层73、连接模制层73m、支撑部75、第一下绝缘层76、第二下绝缘层77、掩埋绝缘图案78、堆叠结构85、至少一个层间绝缘层86、多个沟道结构99、第一上绝缘层103、第二上绝缘层105、第三上绝缘层106、多个位插塞107、第一接触插塞307、第二接触插塞308、第三接触插塞309、多个第一水平布线b1、多个第二水平布线b2和第三水平布线x3。连接电极层73和连接模制层73m可以形成连接布线层。

51.下水平布线71和第一下绝缘层76可以设置在衬底51上。例如,如图17的示例性实施方式所示,下水平布线71和第一下绝缘层76的下表面可以直接接触衬底51的上表面,并且可以相对于彼此在第一方向d1上排列。下水平布线71和第一下绝缘层76的顶表面可以(例如,在第三方向d3上)基本上彼此共面。连接模制层73m、连接电极层73、支撑部75、第二下绝缘层77和掩埋绝缘图案78可以设置在下水平布线71和第一下绝缘层76上。

52.在示例性实施方式中,连接模制层73m可以包括相对于下水平布线71和支撑部75具有蚀刻选择性的材料。连接模制层73m可以包括下模制层73l、设置在下模制层73l上的上模制层73u以及(例如,在第三方向d3上)设置在下模制层73l与上模制层73u之间的中间模制层73c。中间模制层73c可以包括相对于下模制层73l和上模制层73u具有蚀刻选择性的材料。例如,在示例性实施方式中,下模制层73l和上模制层73u中的每个可以包括硅氧化物。中间模制层73c可以包括硅氮化物。

53.支撑部75可以覆盖连接模制层73m和连接电极层73。支撑部75可以包括穿过连接模制层73m和连接电极层73的部分,并且可以直接接触下水平布线71的顶表面。如图17的示例性实施方式所示,支撑部75可以直接接触连接模制层73m的顶表面和侧表面以及连接电极层73的顶表面和侧端。第二下绝缘层77的侧端可以接触支撑部75的侧端和连接模制层73m的侧端。掩埋绝缘图案78可以设置在支撑部75上。

54.支撑部75、第二下绝缘层77和掩埋绝缘图案78的顶表面可以(例如,在第三方向d3上)基本上彼此共面。在示例性实施方式中,第一下绝缘层76、第二下绝缘层77和掩埋绝缘图案78中的每个可以包括硅氧化物、硅氮化物、硅氮氧化物、sibn、sicn、低k电介质、高k电介质或其组合。在示例性实施方式中,支撑部75可以包括多晶硅层。连接电极层73可以包括金属、金属氮化物、金属氧化物、金属硅化物、导电碳、多晶硅、或诸如其组合的导电层。

55.堆叠结构85和层间绝缘层86可以(例如,在第三方向d3上)设置在支撑部75、第二下绝缘层77和掩埋绝缘图案78上。层间绝缘层86可以设置在堆叠结构85的侧表面上。在示例性实施方式中,层间绝缘层86可以包括硅氧化物、硅氮化物、硅氮氧化物、sibn、sicn、低k电介质、高k电介质或其组合。

56.第一上绝缘层103、第二上绝缘层105和第三上绝缘层106可以(例如,在第三方向d3上)依次堆叠在堆叠结构85和层间绝缘层86上。第一接触插塞307可以基本上在第三方向d3上延伸并穿过第一上绝缘层103和层间绝缘层86,并且可以接触多个电极层81中的对应电极层。第二接触插塞308可以基本上在第三方向d3上延伸并穿过第二上绝缘层105,并且可以接触第一接触插塞307。例如,如图17的示例性实施方式所示,第二接触插塞308的下表面可以直接接触第一接触插塞307的上表面。第三接触插塞309可以基本上在第三方向d3上延伸并穿过第三上绝缘层106,并且可以接触第二接触插塞308。例如,如图17的示例性实施方式所示,第三接触插塞309的下表面可以直接接触第二接触插塞308的上表面。第三水平布线x3可以设置在第三上绝缘层106上,并且可以接触第三接触插塞309。例如,如图17的示例性实施方式所示,第三水平布线x3的下表面可以直接接触第三接触插塞309的上表面。然而,本发明构思的示例性实施方式不限于此。第三水平布线x3可以经由第三接触插塞309、第二接触插塞308和第一接触插塞307连接到多个电极层81中的对应电极层。在示例性实施方式中,第一接触插塞307、第二接触插塞308、第三接触插塞309和第三水平布线x3中的每个可以包括金属、金属氮化物、金属氧化物、金属硅化物、导电碳、多晶硅、或诸如其组合的导电层。

57.第三水平布线x3可以设置在与多个第一水平布线b1和多个第二水平布线b2不同的高度处。例如,如图17的示例性实施方式所示,第三水平布线x3可以形成在高于多个第一水平布线b1和多个第二水平布线b2的高度处。在示例性实施方式中,第三水平布线x3可以设置在第三上绝缘层106上。例如,如图17的示例性实施方式所示,第三水平布线x3的下表面可以直接接触第三上绝缘层106的上表面。多个第一水平布线b1和多个第二水平布线b2可以形成在第三上绝缘层106中。例如,第三上绝缘层106可以直接接触多个第一水平布线b1和多个第二水平布线b2的上表面和侧表面。

58.参照图18,根据本发明构思的示例性实施方式的半导体器件可以包括衬底51、第一下绝缘层76、第二下绝缘层77、至少一个层间绝缘层86、第一上绝缘层103、第二上绝缘层105、第三上绝缘层106、包括多个第三水平布线x3的第三布线组313、包括多个第四水平布线x4的第四布线组314、以及多个第二线识别部356。

59.多个第三水平布线x3、多个第四水平布线x4和多个第二线识别部356可以设置在第三上绝缘层106上。例如,如图18的示例性实施方式所示,多个第三水平布线x3、多个第四水平布线x4和多个第二线识别部356的下表面可以直接接触第三上绝缘层106的上表面。多个第三水平布线x3中的每个可以具有基本相同的水平宽度(例如,在第二方向d2上的长度)。多个第三水平布线x3中的每个可以在对应的第三水平布线x3与相邻的第三水平布线x3之间具有基本相同的间隔(例如,每个第三水平布线x3与相邻的第三水平布线x3间隔开的在第二方向d2上的长度)。多个第四水平布线x4中的每个可以具有基本相同的水平宽度(例如,在第二方向d2上的长度)。多个第四水平布线x4中的每个可以在对应的第四水平布线x4与相邻的第四水平布线x4之间具有基本相同的间隔(例如,每个第四水平布线x4与相

邻的第四水平布线x4间隔开的在第二方向d2上的长度)。在示例性实施方式中,多个第三水平布线x3可以具有与多个第四水平布线x4基本相同的节距。

60.多个第二线识别部356可以设置在与多个第三水平布线x3和多个第四水平布线x4基本相同的高度处。在示例性实施方式中,多个第二线识别部356、多个第三水平布线x3和多个第四水平布线x4可以包括基本上同时形成的相同材料。多个第二线识别部356、多个第三水平布线x3和多个第四水平布线x4中的每个可以具有基本相同的厚度(例如,在第三方向d3上的长度)。在示例性实施方式中,多个第二线识别部356、多个第三水平布线x3和多个第四水平布线x4可以包括金属、金属氮化物、金属氧化物、金属硅化物、导电碳、多晶硅、或诸如其组合的导电层。多个第二线识别部356、多个第三水平布线x3和多个第四水平布线x4的顶表面可以(例如,在第三方向d3上)基本上彼此共面。多个第二线识别部356、多个第三水平布线x3和多个第四水平布线x4的底表面可以(例如,在第三方向d3上)基本上彼此共面。

61.在示例性实施方式中,多个第二线识别部356可以包括与多个第三水平布线x3和多个第四水平布线x4的材料不同的材料。在示例性实施方式中,多个第二线识别部356可以包括空的空间。多个第二线识别部356可以包括绝缘层。

62.多个第二线识别部356中的每个可以具有比多个第三水平布线x3和多个第四水平布线x4中的每个的水平宽度(例如,在第二方向d2上的长度)大的水平宽度。在示例性实施方式中,多个第二线识别部356中的每个的水平宽度可以在多个第三水平布线x3和多个第四水平布线x4中的每个的水平宽度的约2至约20倍的范围内。例如,多个第二线识别部356中的每个的水平宽度可以为约300nm。在示例性实施方式中,多个第三水平布线x3和多个第四水平布线x4中的每个的水平宽度可以在约15nm至约150nm的范围内。选自多个第二线识别部356之中的一个第二线识别部356与多个第三水平布线x3之中(例如,在第二方向d2上)紧邻所述一个第二线识别部356的一个第三水平布线x3之间的间隔可以与多个第三水平布线x3中的彼此相邻的第三水平布线x3之间的间隔基本相同。选自多个第二线识别部356之中的一个第二线识别部356与多个第四水平布线x4之中(例如,在第二方向d2上)紧邻所述一个第二线识别部356的一个第四水平布线x4之间的间隔可以与多个第四水平布线x4中的彼此相邻的第四水平布线x4之间的间隔基本相同。

63.连同图18再次参照图1和图17,多个第三水平布线x3和多个第四水平布线x4中的每个可以经由第三接触插塞309、第二接触插塞308和第一接触插塞307连接到多个电极层81中的对应一个。多个第二线识别部356可以不电连接到多个电极层81。多个第三水平布线x3、多个第四水平布线x4和多个第二线识别部356可以形成在与多个第一水平布线b1、多个第二水平布线b2和多个第一线识别部255不同的高度处。在示例性实施方式中,多个第三水平布线x3、多个第四水平布线x4和多个第二线识别部356可以设置在第三上绝缘层106上。例如,如图18的示例性实施方式所示,多个第三水平布线x3、多个第四水平布线x4和多个第二线识别部356的下表面可以直接接触第三上绝缘层106的上表面。多个第一水平布线b1、多个第二水平布线b2和多个第一线识别部255可以形成在第三上绝缘层106中并设置在第三上绝缘层106的上表面下方。

64.图19和图20是用于描述根据本发明构思的示例性实施方式的半导体器件的示意图。

65.参照图19,根据本发明构思的示例性实施方式的半导体器件可以包括页缓冲器202、列解码器204、行解码器304、包括多个第一水平布线b1的第一布线组211、包括多个第二水平布线b2的第二布线组212、多个第一线识别部255、包括多个第三水平布线x3的第三布线组313以及包括多个第四水平布线x4的第四布线组314。

66.多个第一水平布线b1和多个第二水平布线b2可以在第一方向d1上排列。多个第一水平布线b1和多个第二水平布线b2中的每个可以在第二方向d2上延伸。选自多个第一线识别部255之中的一个第一线识别部255可以(例如,在第一方向d1上)设置在第一布线组211与第二布线组212之间。

67.第一布线组211和第二布线组212可以在第一方向d1上与第三布线组313和第四布线组314相邻设置。多个第三水平布线x3和多个第四水平布线x4可以在第二方向d2上排列。多个第三水平布线x3和多个第四水平布线x4中的每个可以在第一方向d1上延伸。在示例性实施方式中,多个第三水平布线x3和多个第四水平布线x4中的每个可以具有基本相同的宽度(例如,在第二方向d2上的长度)。

68.第三布线组313和第四布线组314可以在第一方向d1上与行解码器304相邻设置。多个第三水平布线x3和多个第四水平布线x4中的每个可以连接到行解码器304。

69.参照图20,根据本发明构思的示例性实施方式的半导体器件可以包括页缓冲器202、列解码器204、包括多个第一水平布线b1的第一布线组211、包括多个第二水平布线b2的第二布线组212以及多个第一线识别部255。

70.多个第一水平布线b1和多个第二水平布线b2可以在第一方向d1上排列。多个第一水平布线b1和多个第二水平布线b2中的每个可以在第二方向d2上延伸。选自多个第一线识别部255之中的一个第一线识别部255可以(例如,在第一方向d1上)设置在第一布线组211与第二布线组212之间。

71.根据本发明构思的示例性实施方式,线识别部可以提供在多个水平布线之间。可以实现用于使彼此平行的多个布线中的每个的位置能够被容易地识别的半导体器件。

72.在上文中,已经参照附图描述了本发明构思的示例性实施方式,但是可以理解,本领域技术人员可以在不改变本发明构思或实质特征的情况下以另外的详细形式来实现示例性实施方式。应理解,上述示例性实施方式在所有方面只是示例并且本发明构思不受其限制。

73.本技术要求享有2020年5月25日在韩国知识产权局提交的韩国专利申请第10

‑

2020

‑

0062192号的优先权,该韩国专利申请的公开内容通过引用全文合并于此。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。