1.本发明涉及一种时钟数据恢复电路,特别涉及一种可提升信号抖动忍受力的时钟数据恢复电路。

背景技术:

2.在数据信号传输动作中,常使时钟信号配合数据信号来进行调整。然而在传输过程中,常因信号抖动现象而使数据信号与对应的时钟信号间产生偏移,造成数据信号无法正确传递的问题。

3.已知技术中,常通过时钟数据恢复电路来克服上述的问题。然已知的时钟数据恢复电路常需要复杂的电路或演算方式来执行数据信号与时钟信号间的调校动作,在设计难度以及电路成本上,都造成一定的负担。

技术实现要素:

4.本发明是针对一种时钟数据恢复电路,可提升信号的抖动忍受力。

5.根据本发明的实施例,时钟数据恢复电路包括相位混合器、相位检测器、数据采样位置检测器以及数据选择器。相位混合器依据第一时钟信号以及第二时钟信号以产生第三时钟信号以及第四时钟信号。相位检测器依据第一时钟信号以及第二时钟信号以对数据信号采样,藉以产生第一采样数据、第二采样数据以及相位状态信号。数据采样位置检测器依据第三时钟信号以及第四时钟信号以对数据信号采样,藉以产生第三采样数据、第四采样数据以及控制信号。数据选择器依据控制信号以及相位状态信号以选择第一采样数据、第二采样数据、第三采样数据以及第四采样数据的其中之一以产生输出数据。其中第一时钟信号、第二时钟信号、第三时钟信号以及第四时钟信号的相位不相同。

6.基于上述,本发明通过多个相位不同的时钟信号以进行数据采样动作,并依据数据信号的超前或落后状态,来对应选择出正确的采样数据,藉由简单的架构,可提升输出数据的正确性。

附图说明

7.包含附图以便进一步理解本发明,且附图并入本说明书中并构成本说明书的一部分。附图说明本发明的实施例,并与描述一起用于解释本发明的原理。

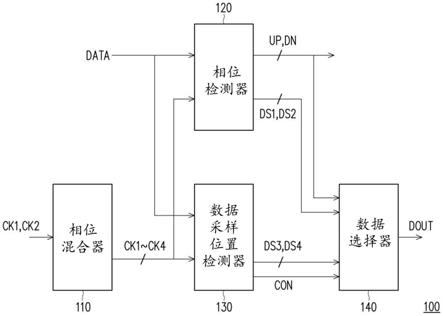

8.图1为本发明一实施例的时钟数据恢复电路的示意图

9.图2为本发明一实施例的时钟数据恢复电路的数据采样动作的示意图;

10.图3及图4示出本发明实施例的数据采样动作的多个实施方式的示意图;

11.图5示出本发明实施例的相位检测器的示意图;

12.图6示出本发明实施例的数据采样位置检测器的示意图;

13.图7a至图7d示出本发明实施例的时钟数据恢复电路的动作波形图;

14.图8示出本发明实施例的时钟数据恢复电路中的数据选择器的实施方式的示意

图;

15.图9示出本发明实施例的选择信号产生器的状态机流程图;

16.图10示出本发明另一实施例的时钟数据恢复电路的示意图。

17.附图标号说明

18.100、1000:时钟数据恢复电路;

19.1050:电荷泵电路;

20.1060:振荡器;

21.110、1010:相位混合器;

22.120、1020:相位检测器;

23.130、1030:数据采样位置检测器;

24.140、800、1040:数据选择器;

25.500:相位检测器;

26.511~515、611~614、822、832:双沿触发触发器;

27.521、522、621:异或门;

28.600:数据采样位置检测器;

29.810:选择信号产生器;

30.820:领先数据产生器;

31.821、831:多任务器;

32.830:落后数据产生器;

33.840:选择器;

34.c1~c4:状态;

35.ck1~ck4:时钟信号;

36.cmp1~cmp6:比较器;

37.con、conx:控制信号;

38.d_e、d_l:选中数据;

39.d0~d2:数据;

40.data:数据信号;

41.ds1~ds4、di1、di2:采样数据;

42.dout:输出数据;

43.es1、es2、ls1、ls2:子状态;

44.r1:基准信号;

45.s1:领先状态;

46.s2:落后状态;

47.sel1~sel3:选择信号;

48.t1n~t4n、t1n’~t4n’、t1n”~t4n”:下降沿;

49.t1p~t4p、t1p’~t4p’、t1p”~t4p”:上升沿;

50.ui:单位区间;

51.up、dn、upx:相位状态子信号;

52.vp:泵升电压。

具体实施方式

53.现将详细地参考本发明的示范性实施例,示范性实施例的实例说明于附图中。只要有可能,相同元件符号在图式和描述中用来表示相同或相似部分。

54.请参照图1,图1为本发明一实施例的时钟数据恢复电路的示意图。时钟数据恢复电路100包括相位混合器110、相位检测器120、数据采样位置检测器130以及数据选择器140。相位混合器110接收相位不相同的第一时钟信号ck1以及第二时钟信号ck2,并依据第一时钟信号ck1以及第二时钟信号ck2以分别产生第三时钟信号ck3以及第四时钟信号ck4。在本实施例中,第一时钟信号ck1以及第二时钟信号ck2、第三时钟信号ck3以及第四时钟信号ck4的相位均不相同,其中,第一时钟信号ck1与第三时钟信号ck3具有一默认相位差,第三时钟信号ck3与第二时钟信号ck2具有上述的预设相位差,第二时钟信号ck2与第四时钟信号ck4则具有上述的预设相位差。

55.在本实施例中,相位混合器110可通过延迟第一时钟信号ck1以产生第三时钟信号ck3,并通过延迟第二时钟信号ck2以产生第四时钟信号ck4。在细节上,相位混合器110针对第一时钟信号ck1以及第二时钟信号ck2进行延迟的延迟量可以是相同的。第一时钟信号ck1、第二时钟信号ck2、第三时钟信号ck3以及第四时钟信号ck4可以依序具有45度的相位差。

56.此外,相位检测器120耦接至相位混合器110。相位检测器120接收第一时钟信号ck1以及第二时钟信号ck2,并接收数据信号data。相位检测器120依据第一时钟信号ck1以及第二时钟信号ck2以对数据信号data采样,藉以产生第一采样数据ds1、第二采样数据ds2以及相位状态信号。在本实施例中,相位状态信号包括第一相位状态子信号dn以及第二相位状态子信号up。

57.在本实施例中,相位检测器120可以是一种二元式相位检测器(bang bang phase detector,bbpd),所产生的第一相位状态子信号dn以及第二相位状态子信号up可分别表示数据信号data对应第一时钟信号ck1以及第二时钟信号ck2是为相位领先或落后的状态。

58.数据采样位置检测器130耦接至相位混合器110以及相位检测器120。数据采样位置检测器130接收第三时钟信号ck3以及第四时钟信号ck4,并依据第三时钟信号ck3以及第四时钟信号ck4以对数据信号data采样,藉以产生第三采样数据ds3、第四采样数据ds4以及控制信号con。数据选择器140则耦接至相位检测器120以及数据采样位置检测器130。数据选择器140接收第一采样数据ds1、第二采样数据ds2、第三采样数据ds3、第四采样数据ds4、控制信号con、第一相位状态子信号dn以及第二相位状态子信号up。数据选择器140并依据控制信号con、第一相位状态子信号dn以及第二相位状态子信号up以选择第一采样数据ds1、第二采样数据ds2、第三采样数据ds3以及第四采样数据ds4的其中之一以产生输出数据dout。在本发明实施例中,第一采样数据ds1、第二采样数据ds2、第三采样数据ds3以及第四采样数据ds4可以是串行格式,数据选择器140则可输出同样为串行格式的输出数据dout,或通过串行转并行的传换动作,以产生为并行格式的输出数据dout。

59.以下请参照图2,其中图2为本发明一实施例的时钟数据恢复电路的数据采样动作的示意图。在本实施例中,所有的数据信号的采样动作都是通过时钟信号的双转态缘(上升沿以及下降沿)来进行的。在图2中,数据信号data可依序通过第一时钟信号的上升沿t1p、第三时钟信号的上升沿t3p、第二时钟信号的上升沿t2p、第四时钟信号的上升沿t4p、第一

时钟信号的下降沿t1n、第三时钟信号的下降沿t3n、第二时钟信号的下降沿t2n、第四时钟信号的下降沿t4n来进行采样。再通过比较器cmp1~cmp6以执行采样数据的比较动作。细节上,比较器cmp1比较对应第一时钟信号与第二时钟的上升沿t1p、t2p的采样数据;比较器cmp2比较对应第三时钟信号与第四时钟的上升沿t3p、t4p的采样数据;比较器cmp3比较对应第二时钟信号的上升沿t2p与第一时钟的下降沿t1n的采样数据;比较器cmp4比较对应第四时钟信号的上升沿t4p与第三时钟的下降沿t3n的采样数据;比较器cmp5比较对应第一时钟信号的下降沿t1n与第二时钟的下降沿t2n的采样数据;比较器cmp6则比较对应第三时钟信号的下降沿t3n与第四时钟的下降沿t4n的采样数据。通过比较器cmp1~cmp6的比较结果,来判断出数据信号data的超前或落后状态。

60.以下请参照图3以及图4,图3、4为本发明实施例的数据采样动作的多个实施方式的示意图。图3以基准信号r1为基础。其中基准信号r1的一个周期可以视为2单位区间(unit interval,ui)。在理想状态下数据信号data可依据第一时钟信号的上升、下降沿t1p、t1n;第二时钟信号的上升、下降沿t2p、t2n;第三时钟信号的上升、下降t3p、t3n;第四时钟信号的上升、下降t4p、t4n来进行采样。

61.当数据信号data与时钟信号间产生偏移现象(时钟信号超前于数据信号data)时,如状态c1及c2。

62.在状态c1中,数据信号data与时钟信号间产生0~1/4单位区间ui的偏移。此时数据信号data依据偏移后的第一时钟信号的上升、下降沿t1p’、t1n’;偏移后的第二时钟信号的上升、下降沿t2p’、t2n’;偏移后的第三时钟信号的上升、下降沿t3p’、t3n’;偏移后的第四时钟信号的上升、下降沿t4p’、t4n’来进行采样。并且,可依据比较对应第四时钟信号的上升沿t4p’以及第三时钟信号的上升沿t3p’所获得的采样数据(均等于数据d1),来产生控制信号(例如等于逻辑电平1)。基于控制信号等于逻辑电平1,可选择偏移后的第四时钟信号的上升沿t4p’所获得的采样数据来作为输出数据。

63.在状态c2中,数据信号data与时钟信号间产生1/4~1/2单位区间ui的偏移。此时数据信号data依据偏移后的第一时钟信号的上升、下降沿t1p”、t1n”;偏移后的第二时钟信号的上升、下降沿t2p”、t2n”;偏移后的第三时钟信号的上升、下降沿t3p”、t3n”;偏移后的第四时钟信号的上升、下降沿t4p”、t4n”来进行采样。并且,可依据比较对应第四时钟信号的上升沿t4p”以及第三时钟信号的上升沿t3p”所获得的采样数据(分别等于数据d1、d0),来产生控制信号(例如等于逻辑电平0)。基于控制信号等于逻辑电平0,可选择偏移后的第一时钟信号的下降沿t1n”所获得的采样数据来做为输出数据。

64.在图4中,当数据信号data与时钟信号间产生偏移现象(时钟信号落后于数据信号data)时,如状态c3及c4。

65.在状态c3中,数据信号data与时钟信号间产生0~1/4单位区间ui的偏移。此时数据信号data依据偏移后的第一时钟信号的上升、下降t1p’、t1n’;偏移后的第二时钟信号的上升、下降t2p’、t2n’;偏移后的第三时钟信号的上升、下降t3p’、t3n’;偏移后的第四时钟信号的上升、下降t4p’、t4n’来进行采样。并且,可依据比较对应第四时钟信号的上升沿t4p’以及第三时钟信号的上升沿t3p’所获得的采样数据(均等于数据d1),来产生控制信号(例如等于逻辑电平1)。基于控制信号等于逻辑电平1,可选择偏移后的第二时钟信号的上升沿t2p’所获得的采样数据来作为输出数据。

66.在状态c4中,数据信号data与时钟信号间产生1/4~1/2单位区间ui的偏移。此时数据信号data依据偏移后的第一时钟信号的上升、下降沿t1p”、t1n”;偏移后的第二时钟信号的上升、下降沿t2p”、t2n”;偏移后的第三时钟信号的上升、下降沿t3p”、t3n”;偏移后的第四时钟信号的上升、下降沿t4p”、t4n”来进行采样。并且,可依据比较对应第四时钟信号的上升沿t4p”以及第三时钟信号的上升沿t3p”所获得的采样数据(分别等于数据d1、d0),来产生控制信号(例如等于逻辑电平0)。基于控制信号等于逻辑电平0,可选择偏移后的第三时钟信号的上升沿t3p”所获得的采样数据来做为输出数据。

67.以下请参照图5,图5为本发明实施例的相位检测器的示意图。相位检测器500包括双沿触发触发器511~515以及由异或门521、522构成的比较电路。双沿触发触发器511依据第一时钟信号ck1的上升沿及下降沿对数据信号data采样,藉以产生第一采样数据ds1。双沿触发触发器512耦接至双沿触发触发器511的输出端,依据第二时钟信号ck2的上升沿及下降沿对第一采样数据ds1采样,并藉以产生第五采样数据di1。

68.在另一方面,双沿触发触发器513依据第二时钟信号ck2的上升沿及下降沿对数据信号data采样,藉以产生第二采样数据ds2。双沿触发触发器514耦接至双沿触发触发器513的输出端。双沿触发触发器514并依据第一时钟信号ck1的上升沿及下降沿对第二采样数据采样ds2,藉以产生第六采样数据di2。

69.异或门521接收第二采样数据ds2以及第五采样数据di1,并针对第二采样数据ds2以及第五采样数据di1进行比较,以产生第一相位状态子信号dn。异或门522则接收第一采样数据ds1以及第六采样数据di2,并针对第一采样数据ds1以及第六采样数据di2进行比较,以产生第二相位状态子信号up。

70.附带一提,双沿触发触发器515接收第二相位状态子信号up,并依据第三时钟信号ck3对第二相位状态子信号up进行采样,以产生同步后的第二相位状态子信号upx。第二相位状态子信号upx可以同步于第三时钟信号ck3,有利于后续电路的处理动作。

71.在本实施例中,第一时钟信号ck1至第三时钟信号ck3间的关系与图1的实施例相同,在此不多赘述。

72.以下则请参照图6,图6为本发明实施例的数据采样位置检测器的示意图。数据采样位置检测器600包括双沿触发触发器611~614以及由异或门621建构的比较器。双沿触发触发器611依据第三时钟信号ck3的上升沿以及下降沿来对数据信号data采样,藉以产生第三采样数据ds3。双沿触发触发器612依据第四时钟信号ck4的上升沿以及下降沿来对数据信号data采样,藉以产生元数据di4。此外,双沿触发触发器613依据第三时钟信号ck3的上升沿以及下降沿来对中继信号di4采样,藉以产生第四采样数据ds4。其中,通过双沿触发触发器613,第四采样数据ds4与第三采样数据ds3可以接同步于第三时钟信号ck3。

73.异或门621接收第四采样数据ds4与第三采样数据ds3,并通过比较第四采样数据ds4与第三采样数据ds3来产生控制信号con。附带一提的,双沿触发触发器614可接收控制信号con,并依据第二时钟信号ck2来采样控制信号con,并产生同步后控制信号conx。

74.关于本发明实施例的时钟数据恢复电路的动作细节,可参照图5、6以及图7a至图7d,其中图7a至图7d为本发明实施例的时钟数据恢复电路的动作波形图。

75.在图7a中,数据信号data与时钟信号(ck1~ck4)间产生0~1/4单位区间ui的偏移(时钟信号超前于数据信号data)。数据信号data原始为数据d0,在第三时钟信号ck3的上升

沿t3p发生前变更为数据d1,在第三时钟信号ck3的下降沿t3n发生前变更为数据d2。

76.此外,双沿触发触发器612可依据第四时钟信号ck4的下降沿t4n’来采样数据信号data以获得为数据d0的中继信号di4。而通过双沿触发触发器511依据第一时钟信号ck1的上升沿t1p对数据信号data的采样动作,则可获得为数据d0的第一采样数据ds1。接着,依据第三时钟信号ck3的上升沿t3p,双沿触发触发器611可以产生为数据d1第三采样数据ds3,双沿触发触发器613则可以产生为数据d0第四采样数据ds4。并且,在此同时,异或门621可以针对数据ds3以及ds4执行异或运算以产生控制信号con。在第二时钟信号ck2的上升沿t2p发生时,同步后控制信号conx的数据为数据d0以及d1的异或运算的结果。

77.双沿触发触发器512以及513则同步依据第二时钟信号ck2的上升沿t2p以分别针对第一采样数据ds1以及数据信号data进行采样,并分别产生第五采样数据di1以及第二采样数据ds2。在本实施例中,第五采样数据di1以及第二采样数据ds2分别为数据d0以及d1。相对应的,异或门521针对数据d0以及d1进行异或运算,并产生第一相位状态子信号dn。

78.在第一时钟信号ck1的下降沿t1n发生时,第一采样数据ds1变更为数据d1。在第三时钟信号ck3的下降沿t3n发生时,第三采样数据ds3以及第四采样数据ds4分别变更为数据d2以及d1,控制信号con对应变更为数据d2以及d1的异或运算的结果。在第二时钟信号ck2的下降沿t2n发生时,同步后控制信号conx的数据为数据d2以及d1的异或运算的结果。

79.在另一方面,在第二时钟信号ck2的下降沿t2n发生时,第五采样数据di1以及的第二采样数据ds2分别变更为数据d1以及d2。第一相位状态子信号dn则变更为数据d1以及d2的异或运算结果。

80.在图7b中,数据信号data与时钟信号(ck1~ck4)间产生1/4~1/2单位区间ui的偏移(时钟信号超前于数据信号data)。数据信号data原始为数据d0,在第二时钟信号ck2的上升沿t2p发生前变更为数据d1,在第二时钟信号ck2的下降沿t2n发生前变更为数据d2。

81.与图7a实施例不相同的,在第三时钟信号ck3的上升沿t3p发生时,第三采样数据ds3以及第四采样数据ds4同步为数据d0,并且在第三时钟信号ck3的下降沿t3n发生时,第三采样数据ds3以及第四采样数据ds4同步变更为数据d1。也就是说,本实施例中的第三采样数据ds3以及第四采样数据ds4持续维持为相同的数据。相对应的,控制信号con以及同步后控制信号conx则维持等于逻辑电平0。

82.在图7c中,数据信号data与时钟信号(ck1~ck4)间产生0~1/4单位区间ui的偏移(时钟信号落后于数据信号data)。数据信号data原始为数据d0,在第一时钟信号ck1的上升沿t1p发生前变更为数据d1,在第一时钟信号ck1的下降沿t1n发生前变更为数据d2。在动作方面,在第二时钟信号ck2的下降沿t2n’发生时,第二采样数据ds2变更为数据d0,而在第四时钟信号ck4的下降沿t4n’发生时,元数据di4也变更为数据d0。接着,在第一时钟信号ck1的上升沿t1p发生时,第一采样信号ds1以及第五采样信号di1同步分别变更为数据d1、d0。相对应的,第二相位状态子信号up的数据等于数据d1、d0的异或运算结果。

83.在第三时钟信号ck3的上升沿t3p发生时,第四采样数据ds4、第三采样数据ds3分别变更为数据d0、d1。相对应的,控制信号con的数据等于数据d1、d0的异或运算结果。在第二时钟信号ck2的上升沿t2p发生时,第二采样数据ds2变更为数据d1。

84.接着,在第四时钟信号ck4的上升沿t4p发生时,中继信号di4变更为数据d1,而在后续的第一时钟信号ck1的下降沿t1n发生时,第五采样数据di1以及第一采样数据ds1分别

变更为数据d1以及d2,第二相位状态子信号up的数据等于数据d1、d2的异或运算结果。并且,在接续的第三时钟信号ck3的下降沿t3n发生时,同步后的第二相位状态子信号upx变更为数据d1、d2的异或运算结果。

85.此外,在第三时钟信号ck3的下降沿t3n发生时,第四采样数据ds4以及第三采样数据ds3分别变更为数据d1以及d2,控制信号con则变更为数据d1、d2的异或运算结果。而在第二时钟信号ck2的下降沿t2n发生时,第二采样数据ds2变更为数据d2。

86.在图7d中,数据信号data与时钟信号(ck1~ck4)间产生1/4~1/2单位区间ui的偏移(时钟信号落后于数据信号data)。数据信号data原始为数据d0,在第四时钟信号ck4的下降沿t4n发生前变更为数据d1,在第四时钟信号ck4的上升沿t4p发生前变更为数据d2。在动作方面,在第三时钟信号ck3的下降沿t3n’发生时,第三采样数据ds3以及第四采样数据ds4均变更为数据d0。在第二时钟信号ck2的下降沿t2n’发生时,第二采样数据ds2则变更为数据d1。接着,在第四时钟信号ck4的下降沿t4n’发生时,元数据di4也变更为数据d0。

87.并且,在第一时钟信号ck1的上升沿t1p发生时,第一采样信号ds1以及第五采样信号di1同步分别变更为数据d1、d0。相对应的,第二相位状态子信号dp的数据等于数据d1、d0的异或运算结果。

88.在第三时钟信号ck3的上升沿t3p发生时,第四采样数据ds4、第三采样数据ds3均变更为数据d1。相对应的,控制信号con等于逻辑电平0。在第二时钟信号ck2的上升沿t2p发生时,第二采样数据ds2变更为数据d1。

89.接着,在第四时钟信号ck4的上升沿t4p发生时,中继信号di4变更为数据d2,而在后续的第一时钟信号ck1的下降沿t1n发生时,第五采样数据di1以及第一采样数据ds1分别变更为数据d1以及d2,第二相位状态子信号up的数据等于数据d1、d2的异或运算结果。并且,在接续的第三时钟信号ck3的下降沿t3n发生时,同步后的第二相位状态子信号upx变更为数据d1、d2的异或运算结果。

90.此外,在第三时钟信号ck3的下降沿t3n发生时,第四采样数据ds4以及第三采样数据ds3均变更为数据d2,控制信号con维持等于逻辑电平0。而在第二时钟信号ck2的下降沿t2n发生时,第二采样数据ds2变更为数据d2。

91.值得一提的,上述实施方式中的异或运算可用以比较两个数据是否相同。在本实施例中,当执行异或运算的二数据相同时,对应产生的异或运算结果为逻辑电平0,相反的,当执行异或运算的二数据不相同时,对应产生的异或运算结果为逻辑电平1。

92.以下请参照图8,图8为本发明实施例的时钟数据恢复电路中的数据选择器的实施方式的示意图。数据选择器包括800选择信号产生器810、领先数据产生器820、落后数据产生器830以及选择器840。选择信号产生器810依据控制信号con、第一相位状态子信号dn以及第二相位状态子信号up来产生选择信号sel1~sel3。领先数据产生器820耦接至选择信号产生器810。领先数据产生器820依据选择信号sel1以选择第四采样数据ds4及第一采样数据ds1的其中之一以产生选中数据d_e。落后数据产生器830耦接至选择信号产生器810。落后数据产生器830依据选择信号sel2以选择第三采样数据ds3及第二采样数据ds2的其中之一以产生选中数据d_l。选择器840耦接至领先数据产生器820、落后数据产生器830以及选择信号产生器810。选择器840依据选择信号sel3以选择选中数据d_e以及选中数据d_l的其中之一以产生输出数据dout。

93.在本实施方式中,领先数据产生器820包括多任务器821以及双沿触发触发器822。多任务器821接收第四采样数据ds4、第一采样数据ds1以及选择信号sel1。多任务器821依据选择信号sel1以选择第四采样数据ds4以及第一采样数据ds1的其中之一以做为输出。双沿触发触发器822则依据第一时钟信号ck1的上升沿以及下降沿来采样多任务器821的输出,并藉以产生选中数据d_e。

94.落后数据产生器830则包括多任务器831以及双沿触发触发器832。多任务器831接收第二采样数据ds2、第三采样数据ds3以及选择信号sel2。多任务器831依据选择信号sel2以选择第二采样数据ds2以及第三采样数据ds3的其中之一做为输出。双沿触发触发器832则依据第一时钟信号ck1的上升沿以及下降沿来采样多任务器831的输出,并藉以产生选中数据d_l。

95.在本实施例中,选择信号产生器810可以为一状态机(state machine)电路。而关于选择信号sel1~sel3的产生方式,则可参照图9示出的本发明实施例的选择信号产生器的状态机流程图。其中,选择信号产生器810在领先状态s1的第一子状态下es1,在当控制信号con为第一逻辑电平(例如逻辑电平0)且第一相位状态子信号dn为第二逻辑电平(例如逻辑电平1)时,进入领先状态s1的第二子状态es2。在领先状态s1的第一子状态下es1,在当控制信号con与第二相位状态子信号up皆为第二逻辑电平时,则进入落后状态s2的第一子状态ls1。另外,选择信号产生器810在领先状态s1的第二子状态es2下,当控制信号con与第一相位状态子信号dn皆为第二逻辑电平时,则进入领先状态s1的第一子状态es1。

96.另外,选择信号产生器810在落后状态s2的第一子状态ls2下,当控制信号con与第一相位状态子信号dn皆为第二逻辑电平,进入领先状态s1的第二子状态es2。选择信号产生器810在落后状态s2的第一子状态ls1下,当控制信号con为第一逻辑电平,且第二相位状态子信号up为第二逻辑电平时,进入落后状态s2的第二子状态ls2。选择信号产生器810在落后状态s2的第二子状态ls2下,当控制信号con与第二相位状态子信号up皆为第二逻辑电平时,进入落后状态s2的第一子状态ls1。

97.在另一方面,选择信号产生器810在领先状态s1的第一子状态es1下,产生为第二逻辑电平的选择信号sel1;在领先状态s1的第二子状态es2下,产生为第一逻辑电平的选择信号sel1;在落后状态s2的第一子状态ls1下,产生为第二逻辑电平的选择信号sel2;在落后状态s2的第二子状态ls2下,产生为第一逻辑电平的选择信号sel2;在领先状态s1下,产生为第二逻辑电平的选择信号sel3;并且,在落后状态下s2,产生为第一逻辑电平的选择信号sel3。

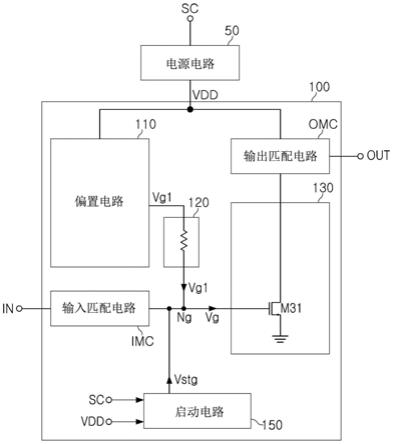

98.以下请参照图10,图10为本发明另一实施例的时钟数据恢复电路的示意图。时钟数据恢复电路1000包括相位混合器1010、相位检测器1020、数据采样位置检测器1030、数据选择器1040、电荷泵电路1050以及振荡器1060。与图1的实施例不相同的,电荷泵电路1050用以接收第一子相位状态信号dn以及第二子相位状态信号up,并依据第一子相位状态信号dn以及第二子相位状态信号up调整泵升电压vp的电压值。振荡器1060耦接至电荷泵电路1050,并依据泵升电压vp的电压值来调整第一时钟信号ck1(以及第二时钟信号ck2)的频率。在本实施中,振荡器1060可以为一电压控制振荡器(voltage controlled oscillator)。

99.综上所述,本发明通过产生多个时钟信号,并依据多个时钟信号的上升沿以及下

降沿针对数据信号进行采样,以判断出时钟信号与数据信号间的偏移状态,并据以选出正确的输出数据。如此一来,时钟数据恢复电路可具有相对大的信号抖动的忍受能力,维持数据的正确性。

100.最后应说明的是:以上各实施例仅用以说明本发明的技术方案,而非对其限制;尽管参照前述各实施例对本发明进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分或者全部技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本发明各实施例技术方案的范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。