1.本公开总体上涉及存储器装置。

背景技术:

2.诸如动态随机存取存储器(dram)的高速存储器装置已经在诸如移动电话的许多电 子装置中变得无处不在。然而,由于dram的成本和与改变dram配置相关联的不灵 活性,对更多存储器空间的日益增长的需求不能总是得到满足。在移动电话的典型场景 中,用户可同时打开许多应用程序而没有意识到这一点。这可能导致dram达到其全 部容量,并因此降低移动电话的性能。用户可能需要手动停止未使用的应用程序以释放 更多的存储器空间。

技术实现要素:

3.在一个方面,本公开涉及一种设备,其包括:多个存储器块;耦合到多个存储器块 的第一数据总线和第二数据总线;以及非易失性存储(nvs)数据传输电路,其耦合到多 个存储器块并且经配置以当经由第一数据总线同时存取多个存储器块中不同于第一存 储器块的第二存储器块时,响应于数据传输命令经由第二数据总线将多个存储器块中的 第一存储器块中的数据传输到nvs。

4.在另一方面,本公开涉及一种方法,其包括:在存储器装置处,响应于来自控制器 的存储器读取或写入命令,经由存储器装置中的第一数据总线在存储器装置中的多个存 储器块处执行存储器操作;从控制器接收数据传输命令;响应于数据传输命令,将多个 存储器块的第一存储器块中的数据经由存储器装置中的第二数据总线传输到非易失性 存储(nvs)装置。

5.在另一方面,本公开涉及一种设备,其包括:多个存储器块;耦合到多个存储器块 的第一数据总线;耦合到多个存储器块且经配置以按通电顺序从熔丝阵列传输熔丝数据 的第二数据总线;经配置以经由第一数据总线对多个存储器块执行存储器读取和写入操 作的控制器;以及经配置以经由第二数据总线将多个存储器块中的第一存储器块中的数 据传输到非易失性存储器(nvs)装置的nvs数据传输电路。

附图说明

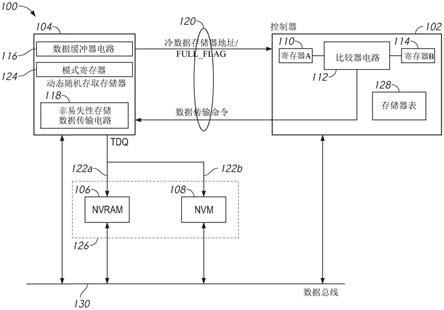

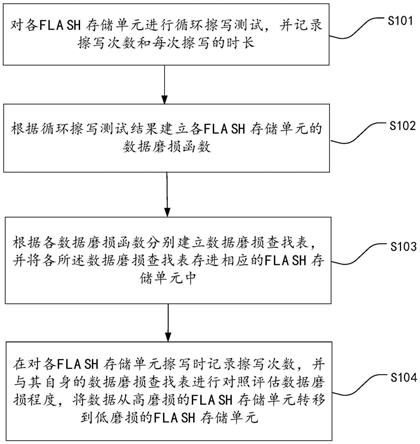

6.图1a是根据本公开的一些实例的实例存储器系统的图。

7.图1b是根据本公开的一些实例的实例存储器映射表的图。

8.图2是根据本公开的一些实例的实例存储器装置的一部分的图。

9.图3a是根据本公开的一些实例的实例存储器装置的一部分的图。

10.图3b是根据本公开的一些实例的实例非易失性存储(nvs)数据传输电路的图。

11.图3c是根据本公开的一些实例的实例选择器电路的图。

12.图4是根据本公开的一些实例的可在存储器装置中实现的实例方法的图。

13.图5是根据本公开的一些实例的可在控制器装置中实现的实例方法的图。

具体实施方式

14.下文将参考附图详细解释本公开的各种实施例。以下详细描述参考附图,附图以图 解的方式示出了本公开的特定方面和实施例。该详细描述包含足以使本领域技术人员能 够实践本公开的实施例的细节。可利用其它实施例,并且可在不脱离本公开的范围的情 况下进行结构、逻辑和电气改变。本文公开的各种实施例不必相互排斥,因为一些公开 的实施例可与一或多个其它公开的实施例组合以形成新的实施例。

15.存储器装置中的冷数据的实例可包含可能最少存取的数据或可能不太可能存取的 数据。存取范围可以指在过去或可预见的将来的时间段内的存储器活动,并且由存取频 率、应用程序使用、功耗或其它标准来度量。存储器活动可包含读取或写入,或读取和 写入操作的组合。在整个本公开进一步描述冷数据的各种实例。

16.图1a是根据本文中所描述的一些实例的实例存储器系统的图。存储器系统100可 在半导体装置中实现。存储器系统100还可在由一或多个半导体装置和/或各种电子组件 组成的电路板中实现。在一些实例中,存储器系统100可包含控制器102、存储器装置 104(例如,dram)和nvs 126,其可包含各种类型的nvs装置,诸如nvram 106或 nvm 108。在一些实例中,系统100可安装在诸如移动电话的电子装置中。系统100中 的任何装置可耦合到数据总线130以从/向数据总线130读取/写入数据。例如,系统100 可安装在移动装置中,其中控制器102可包含能够运行多个应用程序的一或多个中央处 理单元(cpu)。这些应用程序中的数据处理可能需要对dram 104进行存储器存取。在 一些场景中,随着在移动装置中打开更多的应用程序,存储在dram 104中的数据可能 导致dram 104变满。随着dram变满,dram中的一些冷数据可被传输到nvs,例 如nvram 106和nvm 108,以释放dram中的更多存储器空间。进一步解释dram 中的数据管理。

17.进一步参考图1a,系统100中的控制器可经由数据总线130耦合到dram 104且 经配置以从/向存储器读取/写入数据。nvs(例如,106、108)还可耦合到数据总线130, 以经由数据总线130向/从控制器102或其它装置提供数据/接收数据。另外,dram 104 可经由传输总线122a、122b耦合到nvs装置,例如,106、108。例如,传输总线122a、 122b可以是dram与nvs装置之间的总线。在非限制性实例中,传输总线122a、122b 可耦合到dram的测试端口tdq。经由传输总线122a、122b的数据传输可避免干扰系 统100的数据总线130上的正常数据存取。

18.替代地,和/或另外地,系统100可包含例如耦合在dram 104与控制器102之间 的冷数据传输控制总线120。在一些实例中,冷数据传输控制总线120包含用于在dram 104和控制器102之间传输信息的信号线。在一些实施例中,第一存储器块中的数据可 在冷数据传输控制总线120中同时传输,而第二存储器块中的数据在正常存储器存取操 作中在数据总线130中存取,其中第一存储器块和第二存储器块不同。例如,第一存储 器块可含有冷数据或冷数据存储器地址,且第二存储器块可含有用于正常存储器存取操 作的数据。冷数据传输控制总线120可以是单向或双向的,且可包含一或多个位。例如, 控制器102可从dram接收指示dram正在变满的存储器满标志,例如,有效 full_flag(处于逻辑高)。另外,控制器102还可从dram 104接收冷数据存储器地 址。响应于有效full_flag,控制器102可经由

冷数据传输控制总线120向dram 104 提供数据传输命令。

19.在一些实例中,冷数据可包含可以以各种方式确定的不经常使用或最不经常使用的 数据块。例如,dram 104可在一个时间段内从dram中的存储器单元的多次先前存 取中确定哪个数据块存取最少。在一些实例中,写入数据块可能比读取数据块花费更长 的时间。冷数据可被确定为在一个时间段内具有最少量的存储器写入操作的数据块。应 当理解,确定冷数据的其它方式也是可能的。

20.在一些实例中,dram可检测存储器满警报,并且随后将full_flag设置为高电 平有效。例如,如果确定dram已经达到90%满,则full_flag可变为有效并被设 置为高逻辑电平。在其它实例中,当dram已经达到95%、85%、80%、75%或任何其 它合适的水平时,full_flag被设置为高。在其它时间,full_flag可能是无效的 并被设置为低逻辑电平。

21.如上所述,dram 104可经由冷数据传输控制总线120将dram中的冷数据的存 储器地址传输到控制器102。存储器地址可表示可在dram 104与nvs之间传输的冷 数据的最小数据块。例如,存储器阵列可包含多个存储器组,其各自包含多个存储器段。 对各种存储器组和段的存取可由段掩码表来管理。在一些实例中,可以配置段掩码表, 使得每个存储器组有一个段掩码(多个位),其中可以动态地分配段以匹配存储器块大小。 在非限制性实例中,冷数据的最小数据块可以是给定存储器组内的存储器段。然后,冷 数据的存储器地址可包含组号和段号。进一步解释存储器控制器102与dram 104之间 的通信。

22.在一些实例中,控制器102可包含第一寄存器,例如,reg a(110),其经配置以存 储从dram 104接收的冷数据的存储器地址。在一些实例中,冷数据传输控制总线120 可包含串行连接以串行方式传输信息。在此情况下,dram 104可包含数据缓冲器电路, 诸如先进先出(fifo)缓冲器116,其经配置以将存储器地址以串行方式传输到控制器 102。替代地,冷数据传输控制总线120可包含多个位以并行方式传输存储器地址。例 如,dram 104中的每个存储器组可包含128个段。在这种情况下,冷数据传输控制总 线120可包含至少7位以传输段号。冷数据传输控制总线120还可经配置以包含较高数 目的位以传输冷数据的组号(例如,10位以容纳总共1024个组)。在一些实例中,控制 器102可包含第二寄存器,例如,reg b(114)和比较器电路112。控制器102还可经配 置以经由冷数据传输控制总线120将数据传输命令发送到dram 104。

23.在操作中,响应于接收到有效full_flag(例如,处于逻辑高)和冷数据存储器地 址,控制器102可经配置以确定dram是否应将冷数据传输到nvs(例如,106、108)。 在确定dram是否应当传输冷数据时,控制器102可确定冷数据的此传输是否会干扰 任何正在进行的存储器存取操作。例如,reg b可存储在未决存储器存取操作期间正在 传输的数据的当前存储器地址。比较器电路112可经配置以比较reg a 110中的冷数据 的存储器地址与reg b 114中的未决存储器操作中的当前存储器地址。如果在reg a 110和reg b 114中的存储器地址之间存在匹配,则控制器102可确定暂停冷数据的传 输,因为此种传输可能干扰对当前存储器地址的正常存储器操作。如果在reg a 110和 reg b 114中的存储器地址之间不存在匹配,则控制器102可确定dram中的冷数据可 传输到nvs(例如,106、108)而不干扰对当前存储器地址的存储器操作,因为冷数据存 储器地址和被存取的当前存储器地址对应于不同的存储器块。在此情况下,控制器102 可经由冷数据传输控制总线120向dram 104发送数据传输命令。

24.在一些实例中,dram 104可包含模式寄存器124。从控制器102到dram 104的 数据传输命令可以是模式寄存器命令。例如,dram可包含冷数据模式,其通过对模式 寄存器中的设置进行编程来启用,诸如通过模式寄存器写入操作。在此情况下,从控制 器向dram发送数据传输命令可包含控制器在dram中设置冷数据模式,其中冷数据 模式指示冷数据传输的开始。响应于从控制器102接收到数据传输命令(例如,设置冷数 据模式),dram可经配置以开始将冷数据传输到nvs装置(例如,106、108)。

25.进一步参考图1a,dram 104可包含经配置以控制冷数据传输的nvs数据传输电 路118。在一些实例中,dram 104可包含用于正常存储器存取操作的内部数据总线。 dram 104还可包含另一数据总线,例如,熔丝总线。熔丝总线可用于在存储器装置通 电时将熔丝阵列中的数据集推送到存储器行和列解码器中的熔丝锁存电路。在通电之 后,dram 104可使用熔丝总线来传输冷数据,从而消除对第一数据总线上的存储器存 取的任何干扰。

26.在一些实例中,dram可经由dram中的第二数据总线和到nvs装置的传输总线 122a、122b将dram中的冷数据从dram传输到nvs装置。在传输冷数据时,冷数 据的存储器地址(例如,存储器组和段号)可预先在dram中确定并存储在dram中(例 如,在寄存器中)。nvs装置中的冷数据传输的目的地地址可由控制器102确定,控制 器102还向目的地nvs装置(例如,106、108)提供目的地地址。在该配置中,控制器 102控制冷数据从dram到nvs装置的传输。例如,控制器可确定nvs装置的类型和 冷数据应被传输到的地址。

27.在非限制性实例中,存储器块中的每一个(例如,给定存储器组中的存储器段)可具 有相关联的读取/写入标签,其指示与该存储器块相关联的存储器操作的类型。如果存储 器块被存取以进行数据读取,则读取/写入标签可以是“读取”;如果存储器块被存取以 进行数据写入,则读取/写入标签可以是“写入”。存储器块的存取速度对于读取和写入 操作可能不同,例如,写入操作可能需要比读取操作更长的存取时间。在一些实例中, 控制器102可确定什么类型的存储器操作与冷数据相关联,并且基于与冷数据相关联的 存储器操作的类型来确定nvs装置的类型。例如,nvram可具有比nvm更快的存取 速度。如果与冷数据相关联的读取/写入标签是“写入”,则控制器102可将目的地nvs 装置指定为“较快”装置,例如,nvram。相反,如果与冷数据相关联的读取/写入标 签是“读取”,则控制器可将目的地nvs装置指定为“较慢”装置,例如,nvm。应当 理解,根据选择何种类型的nvs装置的其它配置也是可能的。

28.在一些实例中,控制器102还可包含存储器表128,其跟踪数据的物理位置的地址。 一旦到nvs装置的冷数据传输完成,dram 104就可通过更新full_flag(例如将full_flag从有效高逻辑状态改变为无效低逻辑状态)来通知控制器102。在接收到更 新的无效full_flag时,控制器102可更新存储器表128。这在图1b中进一步解释。

29.图1b是根据本公开的一些实例的实例存储器映射表的图。在一些实例中,存储器 映射表180(诸如视觉存储器的页面)可包含在控制器102(图1a)中且用于控制各种存储 器操作。存储器映射表180可含有每个存储器页面或存储器块的多个存储器地址。在图 1b所示的实例中,每个存储器块含有4k字节的数据。其它存储器块大小也是可能的。 在一些实例中,视觉存储器页面182中的每个值可包含对应于dram 184中的物理存储 器位置的地址或对应于nvs装置186中的物理存储器位置的地址。nvs装置可以是 nvram、nvm或任何其它合适的非易失性存储装置。在图1b的实例中,一旦冷数据 被移动到nvs装置,就可更新控制

收外部时钟信号和互补的外部时钟信号。外部时钟信号(包含互补的外部时钟信号)可被 提供到时钟输入电路212。时钟输入电路212可接收外部时钟信号且生成内部时钟信号 iclk。时钟输入电路212可向内部时钟生成器214提供内部时钟信号iclk。内部时钟 生成器214可基于从命令/地址输入电路202接收的内部时钟信号iclk和时钟使能信号 cke生成相位控制的内部时钟信号lclk。尽管不限于此,但是dll电路可用作内部 时钟生成器214。内部时钟生成器214可向io电路222提供相位控制的内部时钟信号 lclk。io电路222可使用相位控制器内部时钟信号lclk作为用于确定读取数据的输 出定时的定时信号。

36.电源端子可接收电源电压vdd和vss。这些电源电压vdd和vss可提供到电压 生成器电路224。电压生成器电路224可基于电源电压vdd和vss生成各种内部电压 vpp、vod、vary、vperi等。内部电压vpp主要用于行解码器208中,内部电压 vod和vary主要用于存储器单元阵列218中包含的读出放大器samp中,并且内部 电压vperi用于许多其它电路块中。io电路222可接收电源电压vdd和vssq。例如, 电源电压vddq和vssq可分别是与电源电压vdd和vss相同的电压。然而,专用电 源电压vddq和vssq可用于io电路222。

37.在一些实例中,半导体装置200可在通电和操作期间使用各种配置参数或设置,诸 如启动参数和设置、冗余设置、选项设置、标识(id)设置或其任何组合。半导体装置200 可使用配置参数来指定操作特性,诸如电压电平、时序配置、i/o和其它总线配置等。 一些配置参数或设置可与冗余配置相关联,诸如标识哪些存储器地址将从有缺陷的存储 器单元行或列重定向到冗余的存储器单元行或列。

38.半导体装置200可包含熔丝阵列225,其包含经配置以存储用于配置参数和设置的 熔丝数据的多个可编程存储元件(例如,熔丝、反熔丝等)。例如,存储元件可存储存储 器单元阵列的有缺陷存储器的地址、启动参数和设置、冗余设置、选项设置、标识(id) 设置或其任何组合。在启动(例如,通电)时,可将存储在熔丝阵列225中的一些信息(例 如,熔丝数据)提供到半导体装置200的电路,诸如命令解码器206、行解码器208、列 解码器210、时钟输入电路212、内部时钟生成器214、电压生成器电路224、io电路 222等。

39.行解码器208可包含熔丝锁存器219,其存储熔丝数据,诸如对应于有缺陷存储器 单元的冗余存储器单元的存储器地址。列解码器210还可包含熔丝锁存器217且以与行 解码器208类似的方式操作。在一些实例中,熔丝数据可用于配置半导体装置200的操 作,例如,在通电序列的早期熔丝读取操作中。在非限制性实例中,存储在熔丝阵列225 中的熔丝数据可被划分成位子集(例如,数据子集),这些比特子集在通电序列期间从熔 丝阵列225串行广播到熔丝总线232。熔丝逻辑226可锁存熔丝数据的位的每一相应子 集且可将位的相应子集提供到行解码器208和/或列解码器210中的熔丝锁存器。

40.在一些实例中,行解码器208和/或列解码器210可随后使用熔丝数据来确定应将哪 些存储器地址引导到存储器单元的冗余行或列。例如,xadd可对应于有缺陷的存储器 单元。在行解码器208中,当在行解码器208处接收到xadd时,将xadd与熔丝锁 存器219中的值进行比较且将其引导到存储器组bank0

‑

n中的冗余物理存储器位置的 地址。列解码器210可以以与行解码器208类似的方式操作。

41.进一步参考图2,nvs数据传输电路228可耦合到rwamp 220和熔丝总线。nvs 数据传输电路228还可耦合到外部端子,例如,测试端口tdq。在一些实例中,端子 tdq可连接到nvs装置,诸如nvram或nvm(图1a中的106、108)。nvs数据传输 电路228还可耦合到内部数据

总线230,并且经配置以将数据重定向到存储器单元阵列/ 从存储器单元阵列重定向数据以用于正常存储器操作。例如,nvs数据传输电路228可 经配置以将数据从存储器单元阵列重定向到内部数据总线230(经由rwamp 220)或将数 据从内部数据总线重定向到存储器单元阵列(经由rwamp 220)。

42.nvs数据传输信号nvs_transferf可从命令解码器206提供到nvs数据传输电路 228。在一些实例中,响应于从控制器(例如,图1a中的102)接收到数据传输命令, nvs_transferf变为有效。例如,半导体装置200可包含经配置以存储来自控制器102(图 1a)的数据传输命令集的模式寄存器229。模式寄存器229可包含在模式寄存器124中(在 图1a中)。数据传输命令可对应于被设置的冷数据模式。这可导致命令解码器206提供 有效的冷数据传输命令,例如,低电平有效nvs_transferf信号。在冷数据传输中,响 应于有效nvs_transferf信号,nvs数据传输电路228可将从存储器单元阵列提供的数 据引导到熔丝总线(经由rwamp 220),以进一步传输到nvs装置。这在本公开中详细 解释。

43.图3a是根据本公开的一些实例的实例存储器装置的一部分的图。实例存储器装置 300中的各种组件可在dram 104(图1a)和存储器装置200(图2)中实现。例如,存储器 阵列302可包含在dram 104(图1a)或存储器组218(图2)的存储器阵列中。熔丝总线 304可包含在存储器装置200(图2)中。如图3a中所示,存储器组(例如,e、f、g、h、 i、j、k和l)可耦合到熔丝总线304。包含在存储器阵列302中的其它数目的存储器组 也是可能的。

44.存储器装置300还可包含多个选择器电路306。例如,选择器电路可耦合到熔丝总 线并且还耦合到相应的存储器组。选择器电路可经配置以将数据从相应的存储器组引导 到熔丝总线。在图3a所示的实例中,存储器组的读取操作(rd)可将数据从存储器组引 导到相应的选择器电路306,其可将数据引导到熔丝总线304。在图3c中将进一步详细 解释选择器电路。

45.上述装置300可经配置以执行从dram到nvs装置的冷数据传输,诸如从dram 104到图1a中的nvs装置(106、108)。由于冷数据传输经由熔丝总线与dram中的正 常存储器存取独立地且同时地执行,因此对其它数据块的正常存储器存取不被中断。在 一些实例中,冷数据传输可响应于数据传输命令而执行,而正常存储器存取可响应于存 储器存取命令而执行。由于冷数据传输和正常存储器存取操作经由不同的数据总线同时 执行,因此冷数据传输的速度要求不是特别重要。例如,来自存储器组的多位冷数据可 经由并串电路308转换为串行输出。

46.现在,进一步参考图3a,存储器装置300可包含并串电路308。并串电路308可耦 合到熔丝总线且还耦合到dram装置的tdq端口。在一些实例中,并串电路308可经 配置以将熔丝总线中的并行数据转换为串行数据以通过tdq端口传输到nvs装置314, 例如,nvram或nvm。并串电路308还可包含输出缓冲器310,其经配置以向nvs 装置314输出串行数据。在一些实例中,并串电路308可包含多个d型触发器以在熔丝 总线中串行输出多个数据位。应当理解,包含其它并串电路也是可能的。输出缓冲器310 可包含cmos晶体管。

47.图3b是根据本公开的一些实例的实例nvs数据传输电路的图。nvs数据传输电路 350可在dram 104(图1a)、存储器装置200(图2)或存储器装置300(图3a)的一部分中 实现。nvs数据传输电路350可耦合到存储器组320。在图3b中,为了说明,仅示出 了一个nvs数据传输电路。然而,在其它实例中,nvs数据传输电路350可包含多个 电路,其各自耦合到相应

的存储器组。

48.在一些实例中,nvs数据传输电路350可包含经配置以将冷数据信息传输到控制器 的数据缓冲器电路334。冷数据信息可包含冷数据的存储器地址(例如,存储器组和段号)。 冷数据信息还可包含存储器满标志,例如,full_flag。有效(例如,逻辑高)full_flag 可指示dram中的存储器正在变满(例如,95%、90%、85%、80%或任何其它合适的阈 值)。在一些实例中,数据缓冲器电路334可包含fifo电路,其经配置以将多个位中的 冷数据的存储器地址转换为用于串行输出到控制器的一系列位。nvs数据传输电路350 还可包含数据传输逻辑330。在一些实例中,一旦模式寄存器(例如,图1a中的124、 图2中的229)中的冷数据模式被设置(例如,设置为逻辑高值),命令解码器(例如,图2 的命令解码器206)可触发数据传输逻辑330开始将冷数据传输到目标nvs装置,例如, nvram或nvm,或其它非易失性存储装置。

49.在一些实例中,nvs数据传输电路350可包含耦合到dram中的存储器组320并 且还耦合到数据总线342和熔丝总线344的选择器电路324。例如,数据总线342可包 含内部数据总线230(在图2中)。熔丝总线344可包含熔丝总线232(图2中)或熔丝总线 304(图3a中)。在一些实例中,选择器电路324可包含多个选择器电路,其各自与相应 的存储器组相关联。这允许经由熔丝总线344对冷数据的并行数据传输和经由数据总线 342对不同存储器组的存储器存取。例如,如图3a所示,可在nvs数据传输电路350 中实现与存储器阵列302中的相应存储器组相关联的选择器电路306。选择器电路324 可耦合到各种控制线。例如,选择器电路324可耦合到相应组的组读取/写入信号,例如, bk_write、bk_read。选择器电路324还可耦合到nvs_transferf线。在非限制性实例 中,如图2所示,响应于来自控制器(例如,图1a中的102)的冷数据传输命令,可从命 令解码器206提供有效nvs_transferf信号。

50.在一些实例中,nvs数据传输电路350还可包含耦合到数据传输逻辑330的计数器 电路328。计数器电路328可经配置以确定冷数据传输何时完成。响应于冷数据传输完 成的确定,数据传输逻辑330可经配置以向控制器发送标志以指示数据传输完成,使得 控制器可更新存储器映射表。在非限制性实例中,在冷数据传输完成时,数据传输逻辑 330可向控制器102(图1a)发送无效(例如,逻辑低)full_flag标志。

51.在操作中,在模式寄存器(例如,图1中的124、图2中的229)中设置冷数据模式时, 数据传输逻辑330可开始将冷数据从dram传输到由控制器选择的目标nvs装置。在 实例中,冷数据的地址可存储在dram中。目标nvs装置的地址可由控制器(例如,图 1a中的102)在目标nvs装置中设置。如图1a中的实施例所述,目标nvs装置可由控 制器基于与冷数据相关联的“读取/写入”标志来确定。在传输冷数据时,将冷数据中的 每个数据块从多个存储器组320中的相应存储器组提供到nvs数据传输电路350的对 应选择器电路324。如果nvs_transferf为有效(例如,处于逻辑低)并且与nvs数据传 输电路350相关联的存储器组没有执行任何正常的读取/写入操作(例如,bk_write和 bk_read信号均为无效,例如,处于逻辑低),则选择器电路324可将数据从存储器组引 导到熔丝总线。在正常存储器操作中,选择器电路324不将数据从存储器组重定向到熔 丝总线,而是将数据从数据总线重定向到存储器组或从存储器组重定向到数据总线。

52.进一步参考图3b,nvs数据传输电路350可包含并串电路336。一旦冷数据被引导 到熔丝总线,dram中的并串电路336可经配置以将多位冷数据转换为一系列位,并将 串行

位提供到tdq端口的输出缓冲器340,以传输到nvs装置。如前所述,在308(图 3a)中提供了并串电路的实例。并串电路的其它实施方案是可能的。例如,一或多个电 路可经配置以将16位并行数据转换为串行数据,其各自以时钟周期提供。时钟可以是 dram装置的内部时钟或相位控制的内部时钟,诸如iclk或lclk(图1a)。在此实例 中,在iclk或lclk的每一时钟周期,提供16位数据的位中的一者。换句话说,在 此类实例中,输出16位数据将花费16个时钟周期。替代地,输出冷数据的时钟周期数 可以变化。例如,冷数据的每一位可在时钟的上升沿和下降沿被计时,因此,需要8个 时钟周期来输出16位的冷数据。

53.在一些实例中,可在nvs_transferf信号变为低电平有效时激活计数器电路328。 在其它实例中,计数器使能信号可响应于有效nvs_transferf信号而变为有效,并且有 效计数器使能信号触发计数器电路328开始计数。随后,当计数的数目已过去时,计数 器电路328可向数据传输逻辑330提供结束控制信号,以使数据传输逻辑330向控制器(例如,图1a中的102)提供无效full_flag标志(例如,处于逻辑低)。在一些实例中, 冷数据中的每个数据(例如,16位)花费16个时钟周期以提供到nvs装置。在此类实例 中,如果存储器组中的存储器段具有1024行和128列,则计数器电路328可经配置以 在计数器使能信号变为有效之后以1024x128x16个时钟周期将结束控制信号提供到数 据传输逻辑330。随后,数据传输逻辑330将无效full_flag标志发送到控制器(例如, 图1a中的102)。

54.替代地,和/或另外,计数器电路328可经配置以基于与字线选择信号相关联的异步 复位信号来提供结束控制信号。例如,如在上述实例中,组中的存储器段可具有1024 行。在此情况下,计数器电路可在字线wl<0>、wl<1>、wl<2>

……

中的每一者变为 有效时递增,直到wl<1024>为止,此时计数器电路提供结束控制信号。在该配置中, 仅计数字线,但不需要计数时钟周期。

55.图3c是根据本公开的一些实例的实例选择器电路的图。在一些实例中,选择器电 路354可以是选择器电路324(图3b)的实例实施方案。选择器电路354可包含具有互补 控制输入的受控缓冲器360。例如,非反相控制输入可耦合到经配置以提供select信 号的选择控制电路364。反相控制输入可耦合到反相器362,其耦合到选择控制电路364。 换句话说,非反相控制输入和反相控制输入处的信号可以是互补信号。响应于有效 select信号(例如,逻辑高),受控缓冲器360经配置以将数据从存储器阵列352提供 到熔丝总线。响应于无效select信号(例如,逻辑低),受控缓冲器360的输出可以是 浮动的。

56.进一步参考图3c,选择控制电路364可包含逻辑门,例如nor门,该逻辑门由 bk_write、bk_read和nvs_transferf信号控制。在操作中,当与包含选择器电路354 的nvs数据传输电路相关联的相应存储器组不执行任何存储器存取操作时,bk_write 和bk_read均为无效。当nvs_transferf信号变为有效(例如,处于逻辑低)时,select 信号变为高电平有效,以控制缓冲器360将数据从存储器阵列352提供到熔丝总线。

57.选择器电路354还可包含在相反方向上彼此并行耦合的受控输入缓冲器358和受控 输出缓冲器356。缓冲器358和356可分别由bk_write(或/bk_write)和bk_read(或 /bk_read)信号控制。在上述实例中,当用于相应存储器组的bk_write和bk_read信号 均为低电平,且nvs_transferf为低电平有效时,select信号为有效。作为响应,输 入和输出缓冲器358、356均停用。当存储器阵列352处于正常存取操作(例如,处于读 取操作)时,bk_read为有效,从而导致输出缓冲器356将数据从存储器组提供到数据总 线。当存储器阵列352处于

写入操作时,bk_write为有效,从而导致输入缓冲器358将 数据从数据总线提供到存储器。在读取或写入操作中,bk_read和bk_write中的一者有 效(例如,处于逻辑高),导致选择控制电路364的输出处的select信号无效,从而禁 用缓冲器360。因此,来自存储器的数据将不会提供到熔丝总线。

58.参考图1至3描述的各种实施例可在一或多个方法中实现。图4是根据本公开的一 些实例的可在存储器装置中实现的实例方法的图。方法400可在诸如104(图1a)、200(图 2)、300(图3a)或nvs数据传输电路350(图3b)的dram中实现。例如,方法400可包 含在操作402处检测存储器满警报。方法400还可包含在操作404处将冷数据存储器地 址传送到例如控制器,以及在操作406处将存储器满标志传送到例如控制器。控制器可 在诸如102(图1a)和314(图3a)的各种实施例中实现。在一些实例中,方法400可经由 冷数据传输控制总线120(图1a)将冷数据存储器地址和存储器满标志传输到控制器。类 似于图1a中的实施例,冷数据存储器地址可包含存储器组号和含有冷数据的给定存储 器组中的段号。操作404可经由诸如fifo电路(例如,图1a中的116)的数据缓冲器电 路和冷数据传输控制总线(例如,120(图1a))以串行方式传输存储器组和段号。存储器满 标志可包含full_flag。例如,在检测到存储器满警报的标准时,例如,在存储器满 至少95%、90%、85%或80%时,或在已满足其它标准时,方法400可传输有效 full_flag(例如,逻辑高)。

59.方法400还可在操作408处经由冷数据传输控制总线120(图1a)接收nvs数据传输 命令。类似于图1a和3b的实施例中描述的方式,nvs数据传输命令可以是模式寄存 器(mr)命令,例如,在dram中设置冷数据模式的mr写入命令。响应于在dram中 设置冷数据模式,方法400可在操作410处开始将冷数据传输到nvs。如图1a和3a 至3c所述,冷数据传输可由dram装置使用数据总线(诸如熔丝总线)自主地执行。因 此,冷数据传输可与正常存储器存取操作同时执行。在传输冷数据时,方法400可控制 选择器电路(例如,图3b中的324、图3c中的354)以向熔丝总线提供冷数据。方法400 还可使用并串电路(例如,图3a中的308、图3b中的336)以串行方式将熔丝总线上的 冷数据提供到nvs装置。待传输的冷数据的存储器地址可存储在dram中的寄存器中。 目标nvs装置和目标nvs装置中的目标地址可由控制器确定,该控制器设置目标nvs 装置中的目的地地址。如图1a、2、3a和3b所示,方法400可经由dram的tdq端 口和传输总线122a或122b(图1a)将冷数据从熔丝总线提供到目标nvs装置(例如,图 1a中的106、108)中的目的地地址。

60.进一步参考图4,方法400还可在操作414处确定冷数据传输是否完成。例如,可 在例如328(图3b)的计数器电路中执行该确定。如在图3b的实施例中类似地描述的, 该方法可在操作412处使用计数器电路进行计数,直到经过数个计数为止。在一些实例 中,计数可基于传输给定存储器组的存储器段中的所有数据块所需的时钟数目。在其它 实例中,计数可基于存储器段中的字线的数目。计数的使用是任选的。在其它实例中, 冷数据传输的完成可以以其它方式确定。本公开不限于通过使用计数和/或计数器来确定 冷数据传输的完成。

61.当传输已经完成时,方法结束操作414并进行到在操作416处向控制器发送完成标 志。在发送完成标志时,方法400可发送无效full_flag(例如,逻辑低)。

62.图5是根据本公开的一些实例的可在控制器装置中实现的实例方法的图。方法500 可在诸如102(图1a)或312(图3a)的控制器装置中实现。例如,方法500可包含在502 处接收

冷数据的存储器地址,以及在操作504处接收存储器满标志。如图1a中的实施 例所述,方法500可经由冷数据传输控制总线120(图1a)从dram接收冷数据存储器地 址和存储器满标志。冷数据存储器地址可包含存储器组号和与冷数据相关联的存储器组 中的段号。存储器满标志可以是指示dram已经变满或正在变满的有效full_flag(例 如,高逻辑电平)。

63.响应于从dram接收到的有效full_flag,方法500可确定是否应当开始冷数据 传输。例如,方法500可在操作506处将冷数据存储器地址与正在dram中存取的当 前存储器地址进行比较,并且在操作508处确定冷数据存储器地址是否与正在存取的当 前存储器地址匹配。例如,方法500可使用比较器电路(例如,图1a中的112)来比较冷 数据存储器地址与正在存取的当前存储器地址,每一地址存储在相应的寄存器中。该比 较可确定冷数据存储器地址是否与正在存取的当前存储器地址匹配。在一些实例中,比 较存储器地址中的组号和段号两者。

64.一旦在操作508处确定冷数据存储器地址与正在存取的当前组地址匹配,则该方法 可在操作510处向存储器装置发送nvs数据传输命令。如果在操作508处冷数据存储 器地址与正在存取的当前组地址不匹配,则方法500可在操作506处继续检查,直到冷 数据存储器地址与正在存取的当前组地址匹配。如图1a中的实施例所述,在发送nvs 数据传输命令之前,方法500可在507处确定目的地nvs装置。在一些实例中,可基 于与冷数据相关联的存储器存取类型来确定目的地nvs装置。例如,如果冷数据用于

ꢀ“

写入”操作,则方法500可将更快的nvs装置(诸如nvram)确定为目的地nvs装置。 相反,如果冷数据用于“读取”操作,则方法500可将较慢的nvs装置(诸如nvm)确 定为目的地nvs装置。在操作509处,方法500还可在目的地nvs装置处设置目标位 置以进行冷数据传输。

65.在一些实例中,类似于图1a中描述的实施例,nvs数据传输命令可以是在dram 中的模式寄存器中设置冷数据模式的mr命令,从而导致存储器装置开始从dram到 nvs装置的冷数据传输。如图1a、1b、3a、3b和3c中的各种实施例所述,冷数据传 输可在dram中独立于使用数据总线(诸如熔丝总线和tdq端口)的正常存储器操作而 执行。在此配置中,冷数据传输可与dram的正常存储器操作同时发生。一旦在510 处发送冷数据传输命令,方法500可通过在512处检查full_flag标志来检查冷数据 传输是否完成。如本公开中所描述的,一旦完成冷数据传输,dram可经由冷数据传输 控制总线120(图1a)提供无效full_flag(例如,逻辑低)。方法500可在操作514处进 行以更新控制器中的存储器表(例如,图1a中的存储器表128)。

66.图1至5中的各种实施例提供优于现有系统的优点。例如,可在dram变满之前 检测冷数据并将其从dram传输到具有较慢存储器速度的nvs装置。这可提高存储器 装置的利用率,并且提高整体系统性能和用户体验。例如,在实现本公开中描述的系统 的电子移动装置中,用户可同时打开多个应用程序。可将用于不经常使用的应用程序的 数据从dram移动到nvs装置,以便为活动的应用程序释放更多的存储器空间,完全 在后台并且与正常存储器存取操作同时进行。这样,用户完全不知道冷数据传输。

67.此外,可在诸如熔丝总线的替代数据总线中执行从dram到nvs装置的冷数据传 输,使得可在不同的数据总线上执行dram中的正常存储器存取。在本公开中描述的 各种实施例中,可以以串行方式执行冷数据传输和/或与冷数据传输相关联的数据传输 (例如,从dram到控制器的冷数据存储器地址的传输),从而降低所需的硬件成本和带 宽。

68.虽然具体实施方式描述了某些优选的实施例和实例,但是本领域技术人员将理解, 本公开的范围超出了具体公开的实施例,延伸至其它替代实施例和/或实施例的使用及其 明显的修改和等同物。另外,在本公开范围内的其它修改对于本领域技术人员将显而易 见。还预期到,可以对实施例的特定特征和方面进行各种组合或子组合,并且仍属于本 公开的范围内。应当理解,公开的实施例的各种特征和方面可以彼此组合或替代以形成 公开的实施例的变化模式。因此,目的是本公开的至少一些的范围不应由以上描述的特 定公开的实施例限制。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。