1.本发明涉及集成电路设计领域,尤其涉及一种任意整数分频器及其分频方法。

背景技术:

2.分频器在数字电路系统中应用广泛,主要用来对输入时钟信号按照某一分频数分频,得到我们想要的某一时钟频率的时钟信号。这里,分频数定义为输入信号频率与输出信号频率之间的比值。

3.现在很多器件或者电路系统只能在一定范围的频率信号下才能正常工作,而高速分频器的输入时钟频率很高,对数字电路的时序要求非常苛刻。基于计数器的整数分频器的输出信号占空比不能保证是50%,但目前很多系统对输出信号的占空比要求是50%。

4.如图1所示,当分频比是偶数2的时候,输出信号占空比是50%;当分频比是奇数3的时候,输出信号占空比不是50%。对于输出信号占空比为50%且延迟可粗调的分频器,设计要求复杂的数字逻辑,给高速电路自动布局布线带来困难,电路工作的最高频率受到限制。

5.因此,设计一款结构简单、占空比50%的任意整数分频器是亟待解决的问题。

技术实现要素:

6.本发明提供了一种任意整数分频器,包括:第一任意整数分频器、第二任意整数分频器、逻辑处理模块、多路选择器及d触发器;输入信号包括:时钟信号clk-in、分频比div#及复位信号rst;所述第一任意整数分频器的输出信号为ck10、ck11......ck1n;所述第二任意整数分频器的输出信号为ck20、ck21......ck2n;其中,所述分频比div#的范围为整数1~n;所述d触发器的输入信号为所述分频比div#及所述时钟信号clk-in,输出信号为选择信号sel;当所述分频比div#为偶数时,所述逻辑处理模块及所述多路选择器根据所述选择信号sel,选择所述第一任意整数分频器的输出信号ck10、ck11......ck1n为输出信号clk-out;当所述分频比div#为奇数时,根据所述选择信号sel,所述逻辑处理模块对所述信号ck10、ck11......ck1n与所述信号ck20、ck21......ck2n进行或运算,并经过多路选择器进行选择,形成所述输出信号clk-out。

7.可选的,所述第一任意整数分频器为上升沿触发器。

8.可选的,所述第二任意整数分频器为下降沿触发器。

9.可选的,所述第一任意整数分频器及所述第二任意整数分频器的触发时钟信号均为所述时钟信号clk-in。

10.可选的,还包括同步模块,所述同步模块的输入信号为延迟信号dly,所述延迟信号dly经过所述同步模块后形成同步信号dly-sync,所述同步信号dly-sync作为所述多路选择器的选择信号。

11.可选的,所述逻辑处理模块包括:或运算单元及选择器单元,所述选择信号sel作为所述选择器单元的选择信号。

12.本发明还提供通过上述任一项所述的任意整数分频器进行分频处理的方法,包括:将带分频处理时钟信号clk-in输入所述第一任意整数分频器、所述第二任意整数分频器及所述d触发器;所述第一任意整数分频器及所述第二任意整数分频器根据自身分频配置,将所述时钟信号clk-in进行分频处理之后,依次输出至所述逻辑处理模块及所述多路选择器;所述逻辑处理模块及所述多路选择器将所述第一任意整数分频器及所述第二任意整数分频器输出的时钟信号进行逻辑处理后得到输出时钟信号进行输出。

13.与现有技术相比,本发明的技术方案具有以下的优点:

14.本发明通过两个分频器对时钟信号进行分频处理,处理后的输出信号经过逻辑处理模块及多路选择器进行逻辑处理和选择,使得当分频比为奇数时,得到的时钟信号的占空比为50%。电路结构简单,提高了器件性能,扩大了电路工作的频率范围。

附图说明

15.图1是当分频比为2和3时的信号波形图;

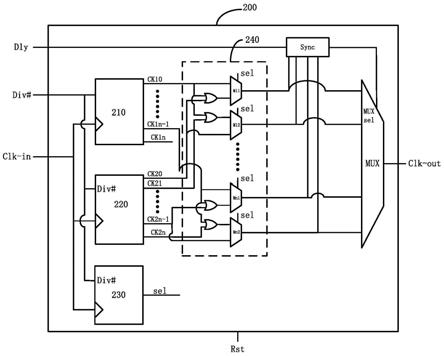

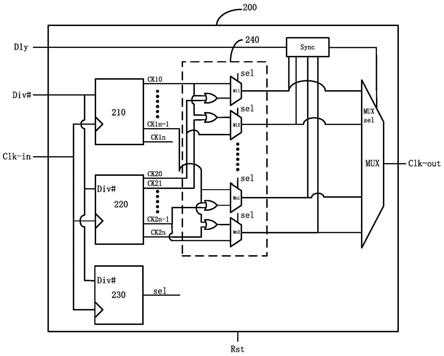

16.图2是本发明实施例中的一种任意整数分频器的结构示意图;

17.图3是当分频比是2和3时的信号波形图。

具体实施方式

18.为使本发明的上述目的、特征和优点能够更为明显易懂,下面结合附图对本发明的具体实施例做详细的说明。

19.图2是本发明实施例中的一种任意整数分频器的结构示意图。其中:

20.所示任意整数分频器200包括:第一任意整数分频器210、第二任意整数分频器220、逻辑处理模块240、多路选择器mux及d触发器230;输入信号包括:时钟信号clk-in、分频比div#及复位信号rst;所述第一任意整数分频器210的输出信号为ck10、ck11......ckln;所述第二任意整数分频器220的输出信号为ck20、ck21......ck2n;其中,所述分频比div#的范围为整数1~n;所述d触发器230的输入信号为所述分频比div#及所述时钟信号clk-in,输出信号为选择信号sel。

21.当所述分频比div#为偶数时,所述逻辑处理模块240及所述多路选择器mux根据所述选择信号sel,选择所述第一任意整数分频器210的输出信号ck10、ck11......ck1n为输出信号clk-out。

22.当所述分频比div#为奇数时,根据所述选择信号sel,所述逻辑处理模块240对所述信号ck10、ck11......ckln与所述信号ck20、ck21......ck2n进行或运算,并经过多路选择器mux进行选择,形成所述输出信号clk-out。

23.具体的,所述第一任意整数分频器210为上升沿触发器;所述第二任意整数分频器220为下降沿触发器。所述第一任意整数分频器210及所述第二任意整数分频器220的触发时钟信号均为所述时钟信号clk-in。

24.需要说明的是,本发明实施例中,所述选择信号sel均与图2中sel所示的接头连接。

25.在本发明实施例中,所述任意整数分频器200还包括同步模块sync,所述同步模块sync的输入信号为延迟信号dly,所述延迟信号dly经过所述同步模块sync后形成同步信号

dly-sync,所述同步信号dly-sync作为所述多路选择器mux的选择信号mux sel。

26.在本发明实施例中,所述逻辑处理模块240还包括:或运算单元及选择器单元,所述选择信号sel作为所述选择器单元的选择信号。

27.本实施例以下面情况为例进行说明。

28.当div#[0]=1,分频比为奇数时,所述第一任意整数分频器210及第二任意整数分频器220相关输出经过或运算后被选择;当div#[0]=0,分频比为偶数,所述第一任意整数分频器210及第二任意整数分频器220的相关输出直接输出被选择。

[0029]

其中,选择信号sel来自于div#[0]的同步信号,也就是所述d触发器230的输出信号。所述d触发器230的输入时钟是clk-in,输入信号是div#[0]。

[0030]

具体的,所述延迟控制信号dly来控制输出信号的延迟。假设输入时钟clk-in的周期为t,则输出延迟为dly*t/2。所述延迟信号dly通过所述同步模块sync得到同步信号dly-sync,用来作为所述多路选择器mux的选择信号mux sel,延迟信号dly经过同步后的dly-sync时序是确定的,用来做多路选择器mux的选择信号时可以避开多路输入信号的跳变,确保最终输出时钟信号无毛刺。

[0031]

参考图3,图3是当分频比是2和3时的信号波形图。参考图2及图3,当分频比为2时,所述第一任意整数分频器210的输出信号直接被选择,因此,输出信号占空比为50%。而当分频比为3时,所述逻辑处理模块240与所述多路选择器mux对所述所述第一任意整数分频器210的输出信号与所述第二任意整数分频器220的输出信号进行或运算并选择,如图所示,所述任意整数分频器200的输出信号为占空比为50%的输出信号。

[0032]

本发明还提供通过上述所述的任意整数分频器进行分频处理的方法,包括:将带分频处理时钟信号clk-in输入所述第一任意整数分频器、所述第二任意整数分频器及所述d触发器;所述第一任意整数分频器及所述第二任意整数分频器根据自身分频配置,将所述时钟信号clk-in进行分频处理之后,依次输出至所述逻辑处理模块及所述多路选择器;所述逻辑处理模块及所述多路选择器将所述第一任意整数分频器及所述第二任意整数分频器输出的时钟信号进行逻辑处理后得到输出时钟信号进行输出。

[0033]

综上所述,本发明提供的技术方案中,两个分频器对时钟信号进行分频处理,处理后的输出信号经过逻辑处理模块及多路选择器进行逻辑处理和选择,使得当分频比为奇数时,得到的时钟信号的占空比为50%。电路结构简单,提高了器件性能,扩大了电路工作的频率范围。

[0034]

虽然本发明披露如上,但本发明并非限定于此。任何本领域技术人员,在不脱离本发明的精神和范围内,均可作各种更动与修改,因此本发明的保护范围应当以权利要求所限定的范围为准。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。