1.本发明属于电子和光电子领域;具体涉及一种插入二维半导体硒化铟纳米片改善二维过渡金属硫族化合物电接触的方法。

背景技术:

2.二维过渡金属硫族化合物(tmds)由于其特殊的物理性质在电子和光电子领域具有光明的应用前景,但是其性能严重地受限于tmds和电极材料之间较大的接触势垒。为了提高二维tmds功能器件(如,场效应晶体管,光电晶体管等)的性能,有效地降低tmds和金属电极之间的接触势垒具有非常重要的意义。

3.迄今为止,文献报道了许多方法来改善tmds电接触行为,包括选择具有合适功函数的金属作为电极、对tmds进行化学掺杂(chemical doping)、一维边缘接触(edge-contact)、直接化学气相沉积制备石墨烯-tmds或者2d金属-tmds异质结构、相工程(phase engineering)、在金属电极与tmds材料之间插入超薄金属氧化层或者六方氮化硼。尽管上述方法在一定程度上起到了改善电接触行为的作用,但同时也存在着诸多挑战。例如,由于金属和tmds之间强烈的费米能级钉扎效应,schottky-mott极限不能有效地指导选取不同功函数的金属作为电极以有效地降低其与tmds之间的接触势垒;利用化学方法对tmds进行简并掺杂可以减少势垒宽度,并且提高电子注入效率,但是其稳定性和耐久性有待提高;相工程和直接生长2d金属-tmds平面结可以使器件中出现具有相对较小势垒的连续的异质或同质结,但是当2d金属的费米能级深度介于tmds材料的价带和导带之间时,其效用可能并不明显,除此之外,其制备工艺依然存在挑战。

4.除了上述方式,在金属电极和tmds沟道材料之间插入一个隧穿层,如宽带隙的al2o3、ta2o5、tio2、h-bn等,可以有效地减轻异质结界面处的费米能级钉扎,以及通过减少金属诱导的带隙态和界面偶极子来降低接触势垒。这种方式同样存在其局限性。首先,该方式通过权衡肖特基势垒和隧穿势垒来降低接触势垒,因此插入的金属氧化物或者h-bn的厚度被严格地限制在1-3nm。由于tmds地疏水特性,通过原子层沉积或者其他气相沉积方式在其表面精确、均匀地生长理想厚度的金属氧化物极具挑战,在此过程中tmds薄膜还可能在高温下损坏其原有的结构。同样地,h-bn纳米片的厚度也仅限于单、双层,无论剥离还是生长都极具挑战。其次,金属氧化物和h-bn相对较高的导带和较低的价带可能会增加n-型或p-型tmds晶体管的隧穿电阻。

技术实现要素:

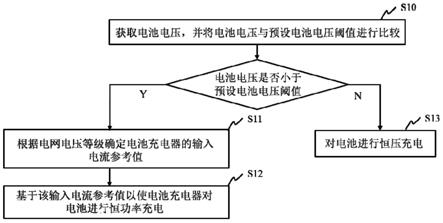

5.本发明是要解决现有改善tmds电接触方法改善效果不明显,以及绝缘插入层厚度严格受限的技术问题,而提供了一种插入二维半导体硒化铟(inse)纳米片改善二维过渡金属硫族化合物(tmds)电接触的方法。

6.本发明的一种插入二维半导体硒化铟纳米片改善二维过渡金属硫族化合物电接

触的方法按以下步骤进行:

7.一、通过机械剥离方法制备tmds层,通过干法转移将tmds层转移到清洗干净的sio2/si衬底上的sio2一侧,然后进行退火处理,退火后自然冷却至室温,备用;

8.二、通过机械剥离方法制备inse纳米片层,然后通过光学显微镜和原子力显微镜选择所需厚度的inse纳米片层,并通过干法转移将inse纳米片层转移至步骤一后的tmds层上,然后进行退火处理,退火后自然冷却至室温,得到inse与tmds的异质结,完成二维过渡金属硫族化合物电接触的改善。

9.进一步限定,步骤一中所述tmds为n-mos2或p-wse2。

10.进一步限定,步骤一中所述机械剥离方法具体过程为:用胶带粘贴n-mos2或p-wse2并按压使其减薄,然后将其粘在贴有pdms薄膜的载玻片上,得到pdms薄膜上的tmds层。

11.进一步限定,步骤一中所述tmds层的厚度为14nm~16nm,长为20μm~100μm,宽为20μm~100μm。

12.进一步限定,步骤一中所述tmds层的厚度为15nm。

13.进一步限定,步骤二中所述机械剥离方法具体过程为:用胶带粘贴inse块体并按压使其减薄,然后将其粘在贴有pdms薄膜的载玻片上,得到pdms薄膜上的inse纳米片层。

14.进一步限定,步骤二中所述inse纳米片层的厚度为4nm~12nm。

15.进一步限定,步骤一中所述胶带为蓝膜胶带。

16.进一步限定,步骤二中所述胶带为蓝膜胶带。

17.进一步限定,步骤一中所述退火处理的具体条件为:氩气氛围,气体流量15sccm~25sccm,升温速率4℃/min~6℃/min,升温至温度为300~330℃,时间为1.5h~2.5h。

18.进一步限定,步骤一中所述退火处理的具体条件为:氩气氛围,气体流量20sccm,升温速率5℃/min,升温至温度为310~320℃,时间为2h。

19.进一步限定,步骤二中所述退火处理的具体条件为:氩气氛围,气体流量15sccm~25sccm,升温速率4℃/min~6℃/min,升温至温度为300~330℃,时间为1.5h~2.5h。

20.进一步限定,步骤二中所述退火处理的具体条件为:氩气氛围,气体流量20sccm,升温速率5℃/min,升温至温度为310~320℃,时间为2h。

21.本发明与现有技术相比具有的显著效果,具体如下:

22.(1)本发明采用机械剥离和干法转移的方式,将硒化铟覆盖在tmds片层材料上,该方法简单,对tmds电接触改善效果明显。

23.(2)本发明采用的inse插入层不被严格的限制在1-3nm的超薄厚度,4-12nm的绝缘inse插入层均可以降低tmds晶体管的接触势垒。随着cvd生长大面积富缺陷态inse-tmds异质结构技术的成熟,该方式在大规模制备具有低接触势垒的异质结器件具有光明的应用前景。

附图说明

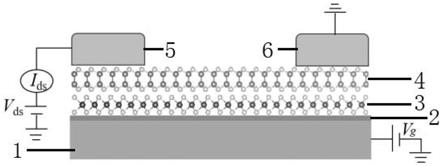

24.图1为用具体实施方式一的inse与n-mos2的异质结制备的器件结构示意图;其中1-si,2-sio2,3-tmds层,4-inse纳米片层,5-源极电极,6-漏极电极;

25.图2为验证试验中的验证器件的光学照片,其中区域a为n-mos2层,区域b为inse纳米片层;

26.图3为图2对应的有效肖特基势垒高度随栅压的变化曲线图;

27.图4为具体实施方式一至五中插入inse绝缘层的厚度与器件的有效肖特基势垒之间的关系图;

28.图5为验证试验中的验证器件的光学照片,其中区域a为p-wse2层,区域b为inse纳米片层;

29.图6为图5对应的有效肖特基势垒高度随栅压的变化曲线图。

具体实施方式

30.具体实施方式一:本实施方式的一种插入二维半导体硒化铟纳米片改善二维过渡金属硫族化合物电接触的方法按以下步骤进行:

31.一、通过机械剥离方法制备tmds层,所述机械剥离方法具体过程为:用胶带粘贴n-mos2并按压,按压后对折,重复对折按压3次,使其减薄,然后将其粘在贴有pdms薄膜的载玻片上,得到pdms薄膜上厚度为15nm、长

×

宽为90μm

×

10μm的n-mos2层,通过干法转移将pdms薄膜上的n-mos2层转移到清洗干净的sio2/si衬底上的sio2一侧,然后进行退火处理,具体条件为:氩气氛围,气体流量20sccm,升温速率5℃/min,升温至温度为310℃,时间为2h。退火后自然冷却至室温,备用;

32.二、通过机械剥离方法制备inse纳米片层,所述机械剥离方法具体过程为:用胶带粘贴inse块体并按压,按压后对折,重复对折按压3次,使其减薄,然后将其粘在贴有pdms薄膜的载玻片上,得到pdms薄膜上的inse纳米片层,通过光学显微镜选择厚度为4.2nm的inse纳米片层,并通过干法转移将pdms薄膜上的inse纳米片层转移至步骤一后的n-mos2层上,然后进行退火处理,具体条件为:氩气氛围,气体流量20sccm,升温速率5℃/min,升温至温度为310℃,时间为2h。退火后自然冷却至室温,得到inse与n-mos2的异质结,完成二维过渡金属硫族化合物电接触的改善。

33.为了验证本实施方式的效果,将本实施方式得到的inse与n-mos2的异质结制备成器件,具体过程如下:

34.利用电子束曝光(ebl)的方式在具体实施方式一得到的inse与n-mos2的异质结样品表面沉积cr/au电极,得到器件结构如图1所示,为了排除器件制备工艺引入的影响因素,单一地确定inse插入层对mos2电接触的影响,我们制备了如图2所示的验证器件(标尺为10μm),其中既包含单独的mos2与电极,又包含在mos2与电极之间插入inse的部分,另外,为了证明所用inse的绝缘性,该器件也包含了单独的inse部分。

35.对用具体实施方式一的inse与n-mos2的异质结制备的器件进行电学性能分析,得到如图3所示的有效肖特基势垒曲线图,从图中可以看出,单独mos2器件的有效肖特基势垒高度为156mev,而在mos2与电极之间插入4.2nm厚的绝缘inse后,其有效肖特基势垒高度很明显地减小到44mev,同时,也测量了单独inse,测试结果证明了其绝缘性。

36.具体实施方式二:本实施方式与具体实施方式一不同的是:步骤二中所述inse纳米片层的厚度为5.5nm。其他步骤及参数与具体实施方式一相同。

37.具体实施方式三:本实施方式与具体实施方式一不同的是:步骤二中所述inse纳米片层的厚度为7nm。其他步骤及参数与具体实施方式一相同。

38.具体实施方式四:本实施方式与具体实施方式一不同的是:步骤二中所述inse纳

米片层的厚度为9nm。其他步骤及参数与具体实施方式一相同。

39.具体实施方式五:本实施方式与具体实施方式一不同的是:步骤二中所述inse纳米片层的厚度为12nm。其他步骤及参数与具体实施方式一相同。

40.检测:对具体实施方式一至五中插入inse绝缘层的厚度与器件的有效肖特基势垒之间的关系进行检测,得到如图4所示的关系图,从图中可以看出,在mos2层与电极之间插入4.2nm厚的绝缘inse纳米片层后,其有效肖特基势垒高度很明显地减小到44mev。在mos2层与电极之间插入5.5nm厚的绝缘inse纳米片层后,其有效肖特基势垒高度很明显地减小到38mev。在mos2层与电极之间插入7nm厚的绝缘inse纳米片层后,其有效肖特基势垒高度很明显地减小到36mev。在mos2层与电极之间插入9nm厚的绝缘inse纳米片层后,其有效肖特基势垒高度很明显地减小到50mev。在mos2层与电极之间插入12nm厚的绝缘inse纳米片层后,其有效肖特基势垒高度很明显地减小到55mev。

41.具体实施方式六:本实施方式的一种插入二维半导体硒化铟纳米片改善二维过渡金属硫族化合物电接触的方法按以下步骤进行:

42.三、通过机械剥离方法制备tmds层,所述机械剥离方法具体过程为:用胶带粘贴p-wse2并按压,按压后对折,重复对折按压3次,使其减薄,然后将其粘在贴有pdms薄膜的载玻片上,得到pdms薄膜上厚度为15nm、长

×

宽为70μm

×

20μm的p-wse2层,通过干法转移将pdms薄膜上的p-wse2层转移到清洗干净的sio2/si衬底上的sio2一侧,然后进行退火处理,具体条件为:氩气氛围,气体流量20sccm,升温速率5℃/min,升温至温度为310℃,时间为2h。退火后自然冷却至室温,备用;

43.四、通过机械剥离方法制备inse纳米片层,所述机械剥离方法具体过程为:将用胶带粘贴inse块体并按压,按压后对折,重复对折按压3次,使其减薄,然后将其粘在贴有pdms薄膜的载玻片上,得到pdms薄膜上的inse纳米片层,通过光学显微镜选择厚度为12nm的inse纳米片层,并通过干法转移将pdms薄膜上的inse纳米片层转移至步骤一后的p-wse2层上,然后进行退火处理,具体条件为:氩气氛围,气体流量20sccm,升温速率5℃/min,升温至温度为310℃,时间为2h。退火后自然冷却至室温,得到inse与p-wse2的异质结,完成二维过渡金属硫族化合物电接触的改善。

44.为了验证本实施方式的效果,将本实施方式得到的inse与p-wse2的异质结制备成器件,具体过程如下:

45.利用电子束曝光(ebl)的方式在具体实施方式六得到的inse与p-wse2的异质结样品表面沉积cr/au电极,为了排除器件制备工艺引入的影响因素,单一地确定inse插入层对wse2电接触的影响,我们制备了如图5所示的验证器件(标尺为10μm),其中既包含单独的wse2与电极,又包含在wse2与电极之间插入inse的部分,另外,为了证明所用inse的绝缘性,该器件也包含了单独的inse部分。

46.对用具体实施方式六的inse与wse2的异质结制备的器件进行电学性能分析,得到如图6所示的有效肖特基势垒曲线图,从图中可以看出,单独wse2器件的有效肖特基势垒高度为95mev,而在wse2与电极之间插入12nm厚的绝缘inse后,其有效肖特基势垒高度很明显地减小到了16mev,同时,也测量了单独inse,测试结果证明了其绝缘性。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。