超结mosfet器件

技术领域

1.本技术涉及功率半导体器件领域,具体涉及一种超结mosfet器件。

背景技术:

2.超结金属

‑

氧化物半导体场效应晶体管(metal

‑

oxide

‑

semiconductor field

‑

effect transistor,mosfet)器件的体二极管特性相比于常规mosfet更差,其原因是超结mosfet器件内部具有交替的pn柱结构,使得体二极管正向导通时存储在耐压层中的非平衡载流子浓度更高,而在体二极管反向恢复过程中非平衡载流子被抽取的速度很快。在反向恢复过程中极易出现电流和电压的过冲,造成超结mosfet器件损坏,导致反向恢复特性较差。

技术实现要素:

3.鉴于此,本技术提供一种超结mosfet器件,以解决现有的超结mosfet器件反向恢复特性较差的问题。

4.本技术提供的一种超结mosfet器件,包括n型外延层以及位于所述n型外延层上的元胞区和终端区,所述元胞区与所述终端区相接触;其中,

5.所述元胞区包括第一超结结构,所述第一超结结构两侧的上表面各设有第一p型基区,所述第一超结结构中间的上端面上设有第一多晶硅栅极,所述第一多晶硅栅极的下表面以及两侧面均设有第一氧化层,所述第一氧化层的外围设有源极金属,所述源极金属两端的宽度小于同侧的所述第一p型基区的宽度;

6.所述终端区包括第二超结结构,所述第二超结结构的上表面设有第二p型基区,所述第二p型基区的上表面设有第二氧化层,所述第二氧化层上设有第二多晶硅栅极,所述第二多晶硅栅极的上表面设有栅极pad(焊垫);

7.根据所述第一多晶硅栅极以及所述第二多晶硅栅极的状态,在所述第一p型基区的表面形成供电流通过的导电沟道。

8.其中,所述第一多晶硅栅极包括第一n型多晶硅以及位于所述第一n型多晶硅的上表面的第一p型多晶硅,所述第一p型多晶硅与所述源极金属形成欧姆接触,所述第一n型多晶硅通过栅走线与所述栅极pad连接。

9.其中,每侧的所述第一p型基区中设有相接触的n 源区和p 体区,其中一侧的所述n 源区的部分上表面和p 体区的部分上表面与所述源极金属的一端连接,另一侧的所述n 源区的部分上表面和p 体区的部分上表面与所述源极金属的另一端连接。

10.其中,所述第二p型基区的宽度大于所述第一p型基区的宽度。

11.其中,所述第一超结结构包括第一n柱以及位于所述第一n柱两侧的第一p柱,所述第一n柱为所述n型外延层的部分区域,每侧的所述第一p柱的上表面与位于同一侧的所述第一p型基区接触,所述第一n柱的上表面与所述第一氧化层接触。

12.其中,所述第一n型多晶硅为掺杂硼的n型多晶硅,所述第一p型多晶硅为掺杂磷的

p型多晶硅。

13.其中,所述第二多晶硅栅极包括第二n型多晶硅以及位于所述第二n型多晶硅上表面的第二p型多晶硅,所述第二p型多晶硅与所述栅极pad上的栅极金属形成欧姆接触。

14.其中,所述第二n型多晶硅包括相接触的第一n型多晶硅区域和第二n型多晶硅区域,所述第二n型多晶硅区域位于所述超结mosfet器件的中心位置或靠近所述超结mosfet器件的中心位置。

15.其中,所述第一n型多晶硅区域连接栅走线,所述第一n型多晶硅区域的宽度等于所述第二p型多晶硅的宽度,所述第二n型多晶硅区域沿着栅叉指延伸至与所述第一n型多晶硅相接触。

16.其中,所述第二超结结构包括交替分布的第二n柱和第二p柱,所述第二n柱为所述n型外延层的部分区域,所述第二n柱的上表面和所述第二p柱的上表面均与所述第二p型基区相接触。

17.本技术上述超结mosfet器件,通过设置n型外延层以及位于n型外延层上的元胞区和终端区;其中,元胞区包括第一超结结构,第一超结结构两侧的上表面各设有第一p型基区,第一超结结构中间的上端面上设有第一多晶硅栅极,第一多晶硅栅极的下表面以及两侧面均设有第一氧化层,第一氧化层的外围设有源极金属,源极金属两端的宽度小于同侧的第一p型基区的宽度;终端区包括第二超结结构,第二超结结构的上表面设有第二p型基区,第二p型基区与第一p型基区接触,第二p型基区的上表面设有第二氧化层,第二氧化层上设有第二多晶硅栅极。基于此,可以根据第一多晶硅栅极以及第二多晶硅栅极的状态,第一p型基区的表面形成供电流通过的导电沟道。从而,使得电流通过mos沟道路径而不通过体二极管路径流动,减少了非平衡少子的注入。因此,本技术可以提高反向恢复特性。

附图说明

18.为了更清楚地说明本技术实施例中的技术方案,下面将对实施例描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本技术的一些实施例,对于本领域技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

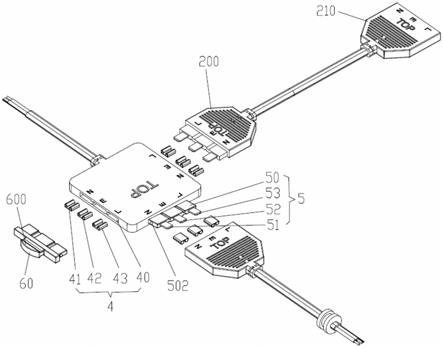

19.图1是本技术实施例提供的超结mosfet器件的俯视结构示意图;

20.图2是本技术实施例提供的图1中aa'bb'段的横截面示意图;

21.图3是本技术实施例提供的图1中cc'd段的横截面示意图;

22.图4是本技术实施例提供的芯片的结构示意图。

具体实施方式

23.超结mosfet器件的体二极管特性相比于常规mosfet更差,其原因是超结mosfet器件内部具有交替的pn柱结构,使得体二极管正向导通时存储在耐压层中的非平衡载流子浓度更高,而在体二极管反向恢复过程中非平衡载流子被抽取的速度很快。在反向恢复过程中极易出现电流和电压的过冲,造成超结mosfet器件损坏,导致反向恢复特性较差。为了解决这个问题,本技术提出一种超结mosfet器件,可以提高反向恢复特性。

24.下面结合附图,对本技术实施例中的技术方案进行清楚、完整地描述,显然,所描

述的实施例仅是本技术一部分实施例,而非全部实施例。基于本技术中的实施例,本领域技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本技术保护的范围。在不冲突的情况下,下述各个实施例及其技术特征可以相互组合。

25.请参阅图1至图3,图1是本技术实施例提供的超结mosfet器件的结构示意图;图2是本技术实施例提供的图1中aa'bb'段的横截面示意图;图3是本技术实施例提供的图1中cc'd段的横截面示意图。该超结mosfet器件包括n型外延层10、元胞区20和终端区30,其中,元胞区20和终端区30位于n型外延层10上,且元胞区20和终端区30相接触。

26.需要说明的是,bb'段对应的是超结mosfet器件的元胞区20,本技术实施例示例性的给出了一个元胞区20,在实际应用中,元胞区20的数量根据具体需求还可以是多个,本技术实施例对元胞区20的数量不做特别限制。

27.本技术实施例中,元胞区20即为超结mosfet器件的元胞结构,元胞区20包括第一超结结构201,第一超结结构201两侧的上表面各设有第一p型基区202,第一超结结构201中间的上端面上设有第一多晶硅栅极203,该第一多晶硅栅极203的下表面以及两侧面均设有第一氧化层204,第一氧化层204的外围设有源极金属205,该第一氧化层204可以用于将第一多晶硅栅极203与源极金属205进行隔离,以避免发生短路现象。

28.需要说明的是,在一种实施方式中,第一氧化层204的材质可以是二氧化硅(sio2)。在另一种实施方式中,第一氧化层204的材质可以是二氧化硅和氮化硅的复合材料。

29.本技术实施例中,源极金属205两端的宽度小于同侧的第一p型基区202的宽度。以便于在第一p型基区202限制的宽度范围内,可以形成源极金属205的两端,以节省空间。

30.本技术实施例中,终端区30包括第二超结结构301,第二超结结构301的上表面设有第二p型基区302,第二p型基区302与第一p型基区202相接触。第二p型基区302的上表面设有第二氧化层303,第二氧化层303上设有第二多晶硅栅极304,第二氧化层303可以用于将第二多晶硅栅极304与源极金属205进行隔离,以避免发生短路现象。

31.需要说明的是,在一种实施方式中,第二氧化层303的材质可以是二氧化硅(sio2)。在另一种实施方式中,第二氧化层303的材质可以是二氧化硅和氮化硅的复合材料。

32.本技术实施例中,第二多晶硅栅极304的上表面设有栅极pad305。

33.本技术实施例中,可以通过控制第一多晶硅栅极203以及第二多晶硅栅极304的状态,以控制在第一p型基区202的表面形成可供电流通通过的导电沟道。比如,通过控制元胞区20的第一多晶硅栅极203正偏,以及栅极pad305下方的第二多晶硅栅极304反偏,可以使第一p型基区202的表面反型形成可供电流通过的导电沟道,这样可以使电流通过mos沟道路径而不通过超结mosfet器件的体二极管路径流动,减少了非平衡少子的注入。

34.可以理解的是,本技术实施例中,通过设置n型外延层10以及位于n型外延层10上的元胞区20和终端区30。其中,元胞区20包括第一超结结构201,第一超结结构201两侧的上表面各设有第一p型基区202,第一超结结构201位于中间位置的上端面上设有第一多晶硅栅极203,第一多晶硅栅极203的下表面以及两侧面均设有第一氧化层204,第一氧化层204的外围设有源极金属205。终端区30包括第二超结结构301,第二超结结构301的上表面设有第二p型基区302,第二p型基区302与第一p型基区202相接触,第二p型基区302的上表面设

有第二氧化层303,第二氧化层303上设有第二多晶硅栅极304。基于此,可以根据第一多晶硅栅极203以及第二多晶硅栅极304的状态,在第一p型基区202的表面形成供电流通过的导电沟道。从而,使得电流通过mos沟道路径而不通过体二极管路径流动,减少了非平衡少子的注入。因此,本技术可以提高反向恢复特性。

35.比如,在一种实施方式中,第一多晶硅栅极203可以包括第一n型多晶硅231和第一p型多晶硅232,其中,第一p型多晶硅232可以位于第一n型多晶硅231的上表面,第一p型多晶硅232与源极金属205形成欧姆接触,第一n型多晶硅231通过栅走线与栅极pad305连接,以保证第一n型多晶硅231与栅极pad305是连通的。

36.需要说明的是,第一n型多晶硅231是一个高浓度掺杂区,比如,在一种实施方式中,第一n型多晶硅231可以为掺杂硼的n型多晶硅。第一p型多晶硅232是一个高浓度掺杂区,比如,在一种实施方式中,第一p型多晶硅232可以为掺杂磷的p型多晶硅,该掺杂的磷可以是注入了砷和磷的复合材料,也可以是单纯的磷。

37.本技术实施例中,元胞区20中包含两个第一p型基区202,该两个第一p型基区202相对于第一超结结构201的中心线对称分布。

38.比如,在一种实施方式中,每侧的第一p型基区202中可以设有相接触的n 源区221和p 体区222,其中一侧的n 源区221的部分上表面和p 体区222的部分上表面与源极金属205的一端连接,另一侧的n 源区221的部分上表面和p 体区222的部分上表面与源极金属205的另一端连接。

39.本技术实施例中,n 源区221可以靠近第一超结结构201顶端的中心位置。两侧的n 源区221相对于第一超结结构201的顶端可以是对称分布的,两侧的p 体区222相对于第一超结结构201可以是对称分布的,这样可以保证第一氧化层204对源极金属205两侧的绝缘性能是一致的。

40.比如,在一种实施方式中,第一多晶硅栅极203的两侧面的第一氧化层204的厚度可以大于第一多晶硅栅极203的下表面的第一氧化层204的厚度,这样可以提升对第一多晶硅栅极203和源极金属205的隔离效果,以进一步避免发生短路现象。

41.当然,在其它实施方式中,第一多晶硅栅极203的两侧面的第一氧化层204的厚度可以等于第一多晶硅栅极203的下表面的第一氧化层204的厚度,或者第一多晶硅栅极203的两侧面的第一氧化层204的厚度可以小于第一多晶硅栅极203的下表面的第一氧化层204的厚度,此时对第一多晶硅栅极203和源极金属205的隔离效果将会变差。

42.比如,在一种实施方式中,第一超结结构201可以包括第一n柱211以及位于第一n柱211两侧的第一p柱212,即第一超结结构201中包含两个第一p柱212。第一n柱211与第一p柱212是交替分布的,第一n柱211与第一p柱212可以构成体二极管。

43.需要说明的是,第一n柱211可以为n型外延层的部分区域,每侧的第一p柱212的上表面与位于同一侧的第一p型基区202接触,第一n柱211的上表面与第一氧化层204接触。

44.图2中示例性地画出了第一超结结构201包括一个第一n柱211和两个第一p柱212。实际应用中,第一超结结构可以包括多个第一n柱以及多个第一p柱,第一n柱与第一p柱交替分布,相邻第一n柱与第一p柱可以构成一个体二极管,在第一超结结构包括多个第一n柱以及多个第一p柱的情况下,可以构成多个体二极管。

45.比如,第一p柱的数量为两个,第一n柱的数量为两个,第一p柱与第一n柱交替分

布,例如从左至右按照第一p柱、第一n柱、第一p柱、第一n柱的顺序交替分布。

46.再比如,第一p柱的数量为三个,第一n柱的数量为两个,第一p柱与第一n柱交替分布,例如从左至右按照第一p柱、第一n柱、第一p柱、第一n柱、第一p柱的顺序交替排列。

47.又如,第一p柱的数量为四个,第一n柱的数量为三个,第一p柱与第一n柱交替分布,例如从左至右按照第一p柱、第一n柱、第一p柱、第一n柱、第一p柱、第一n柱、第一p柱的顺序交替排列。在实际应用中,可以根据具体需求设置超结结构中包含的第一n柱和第一p柱的数量,本技术实施例对第一超结结构201包含的第一n柱211以及第一p柱212的数量不做特别限制。

48.需要说明的是,超结mosfet器件的全部或部分元胞区20可以作为沟道二极管实用,避免元胞区20中的体二极管(如第一n柱211与第一p柱212构成的体二极管、第一n型多晶硅231和第一p型多晶硅232构成的体二极管等)导通。该沟道二极管几乎没有非平衡载流子存储效应,因此反向恢复时间更短,反向恢复特性更佳。

49.比如,在一种实施方式中,第一p型基区202可以设置在第一p柱212的上表面以及第一n柱211的部分侧面,并与第一p柱212的上表面以及第一n柱211的部分侧面相接触。

50.比如,在一种实施方式中,第二多晶硅栅极304可以包括第二n型多晶硅以及位于第二n型多晶硅上表面的第二p型多晶硅341,第二p型多晶硅341与栅极pad305上的栅极金属形成欧姆接触,以保证第二p型多晶硅341与栅极pad305上的栅极金属是连通的。从aa'段和cc'段可以看出,位于栅极pad305下方的第二n型多晶硅以及第二p型多晶硅341形成第二多晶硅二极管。

51.需要说明的是,第二n型多晶硅是一个高浓度掺杂区,比如,在一种实施方式中,第二n型多晶硅可以为掺杂硼的n型多晶硅。第二p型多晶硅341是一个高浓度掺杂区,比如,在一种实施方式中,第二p型多晶硅341可以为掺杂磷的p型多晶硅,该掺杂的磷可以是注入了砷和磷的复合材料,也可以是单纯的磷。

52.比如,在一种实施方式中,根据图中的aa'段以及cc'段可以看出,第二n型多晶硅包括相接触的第一n型多晶硅区域342和第二n型多晶硅区域343。这样,第一n型多晶硅区域342和第二n型多晶硅区域343可以分别与第二p型多晶硅341构成不同性能的第二多晶硅二极管。其中,第二n型多晶硅区域343可以位于超结mosfet器件的中心位置或靠近超结mosfet器件的中心位置。

53.比如,在一种实施方式中,第一n型多晶硅区域342连接栅走线,请参阅aa'段,第一n型多晶硅区域342的宽度可以等于第二p型多晶硅341的宽度。请参阅cc'段,第二n型多晶硅区域343可以沿着栅叉指cd方向延伸至与第一n型多晶硅231,实现与元胞区20的第一n型多晶硅231相接触,同时还实现了第一多晶硅二极管与第二多晶硅二极管的接触,以方便同时对第一多晶硅二极管与第二多晶硅二极管的状态进行控制。

54.需要说明的是,为了保证第二n型多晶硅区域343可以沿着栅叉指cd方向延伸,比如,在一种实施方式中,第二p型基区302的宽度可以大于第一p型基区202的宽度。当第二p型基区302的宽度可以大于第一p型基区202的宽度时,可以在第二p型基区302的上表面提供足够的空间用于布局第二氧化层303,相应的,第二氧化层303就可以提供足够的空间供第二n型多晶硅区域343沿着栅叉指cd方向延伸。

55.比如,在一种实施方式中,第二超结结构301包括交替分布的第二n柱311和第二p

等指示的方位或位置关系为基于附图所示的方位或位置关系,仅是为了便于描述本技术和简化描述,而不是指示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本技术的限制。另外,对于特性相同或相似的结构元件,本技术可采用相同或者不相同的标号进行标识。此外,术语“第一”、“第二”仅用于描述目的,而不能理解为指示或暗示相对重要性或者隐含指明所指示的技术特征的数量。由此,限定有“第一”、“第二”的特征可以明示或者隐含地包括一个或者更多个特征。在本技术的描述中,“多个”的含义是两个或两个以上,除非另有明确具体的限定。

65.在本技术中,“示例性”一词是用来表示“用作例子、例证或说明”。本技术中被描述为“示例性”的任何一个实施例不一定被解释为比其它实施例更加优选或更加具优势。为了使本领域任何技术人员能够实现和使用本技术,本技术给出了以上描述。在以上描述中,为了解释的目的而列出了各个细节。应当明白的是,本领域普通技术人员可以认识到,在不使用这些特定细节的情况下也可以实现本技术。在其它实施例中,不会对公知的结构和过程进行详细阐述,以避免不必要的细节使本技术的描述变得晦涩。因此,本技术并非旨在限于所示的实施例,而是与符合本技术所公开的原理和特征的最广范围相一致。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。