1.本发明涉及一种多工位并发测试的memory烧写时间系统及其烧写方法,属于芯片检测技术领域。

背景技术:

2.在烧写时间的测试过程中,需要通过查询读写标志位或寄存器来判别是否写入,从而计算得到烧写的时间,进而判别芯片是否达到设计的写入速度规定的指标。

3.现有的测试采用不断查询的方式,通过查询次数及查询周期来得到写入完成时间。一般memory 测试的测试覆盖率要求高,进而测试时间长。为了减少测试成本和提高测试效率,往往采用多工位测试。而烧写时间的测试要求在多工位并行测试时对ate的架构要求很高,需要给每个被测器件分配独立的处理单元才能进行并行测试和并行处理。这种架构成本较高,并没有被广泛采用,因而无法实现低成本的高效并行测试,而不得不在牺牲测试效率的情况对各个工位串行测试,且测试时间很长。

技术实现要素:

4.本发明要解决的技术问题是,针对现有技术不足,提出一种多工位并发测试的memory烧写时间系统及其烧写方法,可以在低成本下实现多工位并行测试。

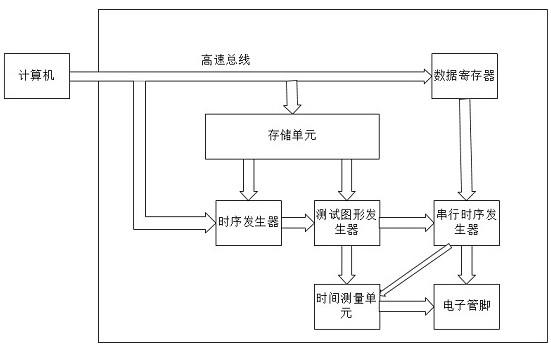

5.为了实现上述目的,本方面采用的技术方案为:一种多工位并发测试的memory烧写时间系统,所述系统通过高速总线连接计算机,其特征在于:所述系统包括存储单元、时序发生器、数据寄存器、测试图形发生器、串行时序发生器、时间测量单元和电子管脚;所述存储单元、时序发生器和数据寄存器通过高速总线连接所述计算机,所述时序发生器、测试图形发生器和串行时序发生器依次相连,所述存储单元连接所述时序发生器和测试图形发生器,所述数据寄存器连接所述串行时序发生器,所述时间测量单元与所述电子管脚相连,所述串行时序发生器连接所述时间测量单元和电子管脚,所述测试图形发生器连接所述时间测量单元。

6.上述技术方案的进一步改进是:所述计算机实现生成pattern文件的功能;所述存储单元实现存储pattern文件的功能。

7.上述技术方案的进一步改进是:所述时序发生器实现按照pattern文件指定的时序要求,产生每个测试周期的精准时序信号的功能。

8.上述技术方案的进一步改进是:所述数据寄存器包括发送寄存器和上传寄存器,所述发送寄存器实现存储待发送数据的功能,所述上传寄存器实现存储读取数据并上传至计算机的功能。

9.上述技术方案的进一步改进是:所述测试图形发生器实现按照pattern文件指定的时序要求,产生图形测试所需的控制时序的功能。

10.上述技术方案的进一步改进是:所述串行时序发生器实现根据pattern文件的指令对所述数据寄存器进行装载和赋值的操作,所述串行时序发生器为per

‑

pin结构的串行

时序发生器。

11.上述技术方案的进一步改进是:所述时间测量单元实现通过所述串行时序发生器和测试图形发生器的触发产生测量时间和频率的功能,所述时间测量单元为per

‑

pin结构的时间测量单元。

12.上述技术方案的进一步改进是:所述电子管脚实现将pattern文件按时序输出电平驱动和接收被测器件的反馈的功能,所述电子管脚为per

‑

pin结构的电子管脚。

13.上述技术方案的进一步改进是:所述高速总线实现所述存储单元、时序发生器和数据寄存器与计算机之间的数据交换的功能。

14.一种应用于权利要求1-6任一项所述的多工位并发测试的memory烧写时间系统的多工位并发测试的memory烧写方法,所述方法用于测试被测器件的烧写时间,包括以下步骤:s1:测试开始前,将被测器件连接至电子管脚,确定待使用的所述测试子系统对应的被测器件的测试需求,所述计算机根据测试需求生成pattern文件;s2:所述计算机通过总线控制器将pattern文件传输至存储单元中;s3:烧写开始时,运行时间测量单元并产生烧写所需要的测量时间和频率,时序发生器按照pattern文件指定的时序要求产生每个测试周期的精准时序信号,测试图形发生器产生测试所需的控制时序;s4:串行时序发生器经过电子管脚的反馈,根据pattern文件的指令不断接收被测器件的输出和读写状态,直到串行时序发生器匹配到pattern文件的读写位,串行时序发生器得到被测器件的烧写时间;s5:时间测量单元停止计时,串行时序发生器将烧写时间赋值给数据寄存器,数据寄存器将烧写时间上传至计算机;s6:完成并得到被测器件的烧写时间。

15.本发明带来的有益效果是:本发明不需要为每个被测器件提供独立的处理器,降低了测试成本;本发明可以多工位完成烧写时间的测试;本发明通过pattern文件控制,编程简便。

附图说明

16.下面结合附图对本发明作进一步的说明。

17.图1是本发明实施例的结构示意图。

18.图2是本发明实施例的被测器件连接的结构示意图。

具体实施方式

19.下面对照附图,通过对实施例的描述,对本发明的具体实施方式如所涉及的各部分之间的相互位置及连接关系、各部分的作用及工作原理、操作使用方法等,作进一步详细的说明,以帮助本领域技术人员对本发明的构思、技术方案有更完整、准确和深入的理解。

实施例

20.如图1所示,一种多工位并发测试的memory烧写时间系统,系统通过高速总线连接

计算机,系统包括存储单元、时序发生器、数据寄存器、测试图形发生器、串行时序发生器、时间测量单元和电子管脚;存储单元、时序发生器和数据寄存器通过高速总线连接计算机,时序发生器、测试图形发生器和串行时序发生器依次相连,存储单元连接时序发生器和测试图形发生器,数据寄存器连接串行时序发生器,时间测量单元与电子管脚相连,串行时序发生器连接时间测量单元和电子管脚,测试图形发生器连接时间测量单元。

21.计算机实现生成pattern文件的功能;存储单元实现存储pattern文件的功能。时序发生器实现按照pattern文件指定的时序要求,产生每个测试周期的精准时序信号的功能。数据寄存器包括发送寄存器和上传寄存器,发送寄存器实现存储待发送数据的功能,上传寄存器实现存储读取数据并上传至计算机的功能。测试图形发生器实现按照pattern文件指定的时序要求,产生图形测试所需的控制时序的功能。串行时序发生器实现根据pattern文件的指令对数据寄存器进行装载和赋值的操作,串行时序发生器为per

‑

pin结构的串行时序发生器。时间测量单元实现通过串行时序发生器和测试图形发生器的触发产生测量时间和频率的功能,时间测量单元为per

‑

pin结构的时间测量单元。电子管脚实现将pattern文件按时序输出电平驱动和接收被测器件的反馈的功能,电子管脚为per

‑

pin结构的电子管脚。高速总线实现存储单元、时序发生器和数据寄存器与计算机之间的数据交换的功能。

22.如图2所示,多个被测器件均可以分配独立的串行时序发生器(缩写为sdg)和时间测量单元(缩写为tmu),如第一被测器件、第二被测器件和第三被测器件,分别连接到第一电子管脚、第二电子管脚和第三电子管脚,并且分别分配第一串行时序发生器和第一时间测量单元、第二串行时序发生器和第二时间测量单元、第三串行时序发生器和第三时间测量单元。然后统一通过测试图形发生器来控制,实现多工位的烧写时间的测试。

23.下面的表1是pattern文件的一个示例:表1中,(1)为pattern head命令,用于定义pattern文件所引用的外部文件信息。(2)为pattern文件的指令名称,用于控制测试图形发生器的执行的执行顺序。(3)是pattern文件的时序代号,每个时序代号可以定义了一组信息,包括周期、时沿、波形等。(4)是pattern文件的通道数据,每列代表一个通道,每个符号代表通道电平,其中1为高电平,0

为低电平,用于被测器件的输入;h为高电平,l为低电平,用于和被测器件的输出进行比较;x为不关心。

24.一种应用于多工位并发测试的memory烧写时间系统的多工位并发测试的memory烧写方法,方法用于测试被测器件的烧写时间,包括以下步骤:s1:测试开始前,将被测器件连接至电子管脚,确定待使用的测试子系统对应的被测器件的测试需求,计算机根据测试需求生成pattern文件;s2:计算机通过总线控制器将pattern文件传输至存储单元中;s3:烧写开始时,运行时间测量单元并产生烧写所需要的测量时间和频率,时序发生器按照pattern文件指定的时序要求产生每个测试周期的精准时序信号,测试图形发生器产生测试所需的控制时序;s4:串行时序发生器经过电子管脚的反馈,根据pattern文件的指令不断接收被测器件的输出和读写状态,直到串行时序发生器匹配到pattern文件的读写位,串行时序发生器得到被测器件的烧写时间;s5:时间测量单元停止计时,串行时序发生器将烧写时间赋值给数据寄存器,数据寄存器将烧写时间上传至计算机;s6:完成并得到被测器件的烧写时间。

25.本发明不局限于上述实施例,凡采用等同替换形成的技术方案,均落在本发明要求的保护范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。