一种同步时钟产生电路及可堆叠dcdc变换系统

技术领域

1.本实用新型涉及时钟电路技术领域,尤其是指一种同步时钟产生电路及可堆叠dcdc变换系统。

背景技术:

2.现有技术中,在需要产生同步时钟是往往直接通过环形振荡器产生一个n倍于开关频率的主时钟(n为堆叠的相位数)。例如,堆叠的相位总数为4,单相开关频率为1mhz,则环形振荡器需要产生的同步时钟频率为4mhz。该技术的主要问题是需要增加额外的逻辑电路来区分master clk和slaver clk,另外,当单相开关频率较高和堆叠的相位数较多时,同步时钟频率较高,此时采用环形振荡器会有较大的误差。其它一些厂商也会通过环形振荡器得到频率与单相开关频率相同的clk,再通过pll产生n倍于开关频率的主时钟(n为堆叠的相位数)。但该技术的问题是pll需要稳定时间且电路实现比较复杂。此外,该技术方案若在工作过程中总相位数发生变化,由于pll是闭环控制回路,因此其频率在切换后的一段时间内可能会与目标值偏差较大。

技术实现要素:

3.本实用新型针对现有技术的问题提供一种同步时钟产生电路,该同步时钟产生电路在动态相数变化的时候也能保持开关周期的稳定并提供均衡的开关相移。

4.本实用新型采用如下技术方案:一种同步时钟产生电路,包括基准电压源、第一电阻、第一比较器、第一脉冲产生器、斜坡产生器、或门单元以及依次连接的至少两个时钟同步单元,第一比较器的第一输入端与斜坡产生器的输出端连接,所述基准电压源的输出端以及第一电阻的一端与第一比较器的第二输入端连接,所述第一比较器的输出端与第一脉冲产生器的输入端连接,或门单元的输入端以及斜坡产生器的控制端均与第一脉冲产生器的输出端连接;所述同步时钟产生单元包括开关管、第二电阻、第二比较器、第二脉冲产生器以及相位控制端口,第二电阻设有第一连接端和第二连接端,第一个时钟同步单元中第二电阻的第一连接端与第一电阻连接,其余时钟同步单元中第二电阻的第一连接端均与上一时钟同步单元中第二电阻的第二连接端连接,最后一个时钟同步单元中第二电阻的第二连接端接地,在每个同步时钟产生单元中,第二比较器的第一输入端与斜坡产生器连接,第二比较器的第二输入端以及开关管的第一开关端与第二电阻的第一连接端连接,开关管的控制端与相位控制端口连接,开关管的第二开关端接地,第二比较器的输出端与第二脉冲产生器的输入端连接,第二脉冲产生器的输出端与或门单元的输入端连接;第一脉冲产生器输出的脉冲的脉冲宽度与第二脉冲产生器输出的脉冲的脉冲宽度不同。

5.作为优选,所述基准电压源为电压跟随器。

6.作为优选,同步时钟产生单元的数量为八个。

7.作为优选,所有同步时钟产生单元中的第二电阻的阻值相同。

8.作为优选,第一脉冲产生器输出的脉冲的脉冲宽度为10ns,第二脉冲产生器输出

的脉冲的脉冲宽度为30ns。

9.作为优选,斜坡产生器包括下拉开关管m9以及电容c0,电容c0的一端与外部电源连接,电容c0的另一端接地,下拉开关管m9的第一开关端以及斜坡产生器的输出端均与电容c0的所述一端连接,下拉开关管m9的第二开关端接地,下拉开关管m9的控制端与第一脉冲产生器的输出端连接。

10.作为优选,所述或门单元包括第一或门、第二或门以及第三或门,部分同步时钟产生单元中的第一脉冲产生器的输出端与第一或门的输入端连接,其余同步时钟产生单元中的第一脉冲产生器的输出端与第二或门的输入端连接,第一或门的输出端以及第二或门的输出端分别与第三或门的输入端连接。

11.本实用新型还提供一种可堆叠dc/dc变换系统,包括变换输入端vin、变换输出端vout、主芯片和若干个从芯片,所述主芯片包括第一逻辑控制电路、第一半桥电路以及上述同步时钟产生电路,所述从芯片包括第二逻辑控制电路以及第二半桥电路,第一半桥电路的输入端以及第二半桥电路的输入端分别与变换输入端vin连接,第一半桥电路的输出端以及第二半桥电路的输出端分别与变换输出端vout连接,所述同步时钟产生电路分别向第一逻辑控制电路以及第二逻辑控制电路输出时钟信号,第一逻辑控制电路与第一半桥电路的控制端连接,第二逻辑控制电路与第二半桥电路的控制端连接。

12.本实用新型的有益效果:同步时钟的循环周期与相位总数无关,因此即使堆叠的相位总数发生实时变化的情况,同步时钟信号也可以保持稳定的循环周期和相位差,有利于dc/dc变换器的稳定工作。

附图说明

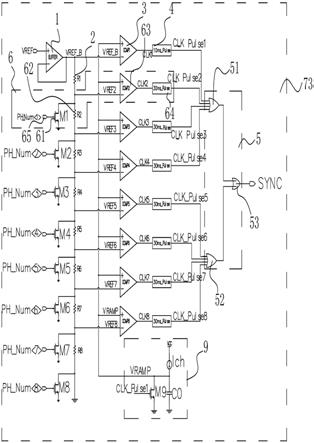

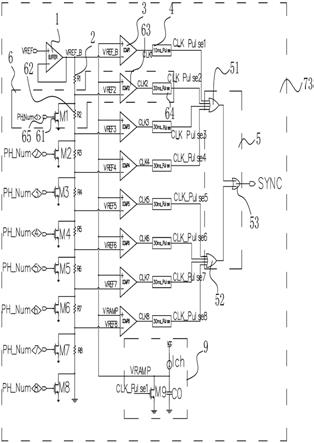

13.图1为本实用新型的同步时钟产生电路的电路图。

14.图2为本实用新型的可堆叠dcdc变换系统的结构示意图。

15.图3为本实用新型的同步时钟信号的产生时序图。

16.附图标记为:1、基准电压源;2、第一电阻;3、第一比较器;4、第一脉冲产生器;5、或门单元;51、第一或门;52、第二或门;53、第三或门;6、时钟同步单元;61、开关管;62、第二电阻;63、第二比较器;64、第二脉冲产生器;65、相位控制端口;7、主芯片;71、第一逻辑控制电路;72、第一半桥电路;73、同步时钟产生电路;8、从芯片;81、第二逻辑控制电路;82、第二半桥电路;9、斜坡产生器。

具体实施方式

17.为了便于本领域技术人员的理解,下面结合实施例与附图对本实用新型作进一步的说明,实施方式提及的内容并非对本实用新型的限定。以下结合附图对本实用新型进行详细的描述。

18.实施例一

19.如图1所示,一种同步时钟产生电路73,包括基准电压源1、第一电阻2、第一比较器3、第一脉冲产生器4、斜坡产生器9、或门单元5以及依次连接的至少两个时钟同步单元6,第一比较器3的第一输入端与斜坡产生器9的输出端连接,所述基准电压源1的输出端以及第一电阻2的一端与第一比较器3的第二输入端连接,所述第一比较器3的输出端与第一脉冲

产生器4的输入端连接,或门单元5的输入端以及斜坡产生器9的控制端均与第一脉冲产生器4的输出端连接;所述同步时钟产生单元包括开关管61、第二电阻62、第二比较器63、第二脉冲产生器64以及相位控制端口65,第二电阻62设有第一连接端和第二连接端,第一个时钟同步单元6中第二电阻62的第一连接端与第一电阻2连接,其余时钟同步单元6中第二电阻62的第一连接端均与上一时钟同步单元6中第二电阻62的第二连接端连接,最后一个时钟同步单元6中第二电阻62的第二连接端接地,在每个同步时钟产生单元中,第二比较器63的第一输入端与斜坡产生器9连接,第二比较器63的第二输入端以及开关管61的第一开关端与第二电阻62的第一连接端连接,开关管61的控制端与相位控制端口65连接,开关管61的第二开关端接地,第二比较器63的输出端与第二脉冲产生器64的输入端连接,第二脉冲产生器64的输出端与或门单元5的输入端连接;第一脉冲产生器4输出的脉冲的脉冲宽度与第二脉冲产生器64输出的脉冲的脉冲宽度不同。

20.斜坡产生器9用于产生斜坡信号vramp。基准电压源1用于产生基准电压vref_b。在上述实施例中,可以通过控制开关管61(m1

‑

m8)的开关来控制vref2

‑

vref8的电压值,进而控制一个开关周期内同步时钟的脉冲个数。第二比较器63(comp1

‑

comp8),用于比较vramp和基准电压vref_b的大小,当vramp大于对应的基准电压vref_b时,其输出产生一个上升沿。第一脉冲产生器4和第二脉冲产生器64将clk1

‑

clk8的上升沿转换成脉冲信号,且第一脉冲产生器4输出脉宽与第二脉冲产生器64输出的脉宽不同,从而区分clk1与clk2

‑

clk8。clk1用于表示一个新开关周期的起点。

21.当周期开始时,斜坡产生器9产生的斜坡信号vramp由0v开始上升,当vramp的值上升到等于基准电压vref_b的值时,第一比较器3输出由低电平翻转为高电平,产生clk_pulse1。通过m9,clk_pulse1将vramp下拉至0v,开始新的vramp周期。clk_pulse1也可称为同步时钟循环周期。

22.具体地,所述基准电压源1为电压跟随器。

23.dc/dc变换系统的相位大多为1至8位,因此优选地,同步时钟产生单元的数量为八个,以便适用不同相位的dc/dc变换系统。为方便描述,本实施例选取的相位总数为4相。vref=2v,r1

‑

r8=50k,ich=2ua,c0=1pf,则单相的时钟频率为:fsw=1/t=ich/(vref*c0)=1mhz。开关管61(m1

‑

m8)的通断与相位总数有关,相位总数与图1中ph_num<8:1>的对应表如下:

24.[0025][0026]

可知当相位总数为4相时,ph_num<8:1>对应的值为:11111000。如图所示,由于p_num<8:4>都是高电平,因此m8/m7/m6/m5/m4都处于开启状态,vref<8>=vref<7>=vref<6>=vref<5>=0v,vref2=1.5v,vref3=1v,vref4=0.5v。

[0027]

如图3所示,0

‑

t0:电流ich对电容c0持续进行充电,使得vramp电压保持ich/c0=2v/us的速度上升,当vramp上升到2v时,第一比较器3的输出clk1产生上升沿(clk1电压由低电平变为高电平),该上升沿被第一脉冲产生器4转换成脉宽为10ns的脉冲信号clk_pulse1。clk_pulse1通过或逻辑,使得同步时钟信号sync在t0时刻也输出一个脉冲宽度为10ns的脉冲信号。另一方面,clk_pulse1变为高电平后,m9开启并将vramp下拉至0v,comp1/comp2/comp3/comp4都输出为低电平。

[0028]

t0

‑

t1:clk_pulse1的10ns正脉冲结束后,下拉开关管m9断开,电容c0重新开始充电,vramp电压以ich/c0=2v/us的速度上升。当vramp上升到0.5v时,第二比较器63comp2的输出clk2产生上升沿,该上升沿被第二脉冲产生器64转换成脉宽为30ns的脉冲信号clk_pulse2。clk_pulse2通过或逻辑,使得同步时钟信号sync在t1时刻输出一个脉冲宽度为30ns的脉冲信号。同样的原理,在t2和t3时刻,vramp分别跨过1v和1.5v时,使得同步时钟信号sync在t2和t3时刻都产生一个脉冲宽度为30ns的脉冲信号。

[0029]

t3

‑

t4:vramp从1.5v继续上升到2v,第一比较器3comp1的输出clk1产生上升沿,电路的状态重新回到t0时刻的状态。因此,t0

‑

t4为同步时钟同步时钟信号sync的循环周期,一个循环周期内同步时钟信号sync有四个脉冲信号,每个脉冲信号的相位差为90度。

[0030]

具体地,所有同步时钟产生单元中的第二电阻62的阻值相同,保证各个第二电阻62稳定分压。

[0031]

具体地,第一脉冲产生器4输出的脉冲的脉冲宽度为10ns,第二脉冲产生器64输出的脉冲的脉冲宽度为30ns。

[0032]

如图1所示,斜坡产生器9包括下拉开关管m9以及电容c0,电容c0的一端与外部电源连接,电容c0的另一端接地,下拉开关管m9的第一开关端以及斜坡产生器9的输出端均与电容c0的所述一端连接,下拉开关管m9的第二开关端接地,下拉开关管m9的控制端与第一脉冲产生器4的输出端连接。斜坡产生器9用于产生斜坡信号vramp。当周期开始时,电容c0通过ich进行充电,vramp由0v开始上升,当vramp上升到基准电压vref_b时,第一比较器3输出由低电平翻转为高电平,产生clk_pulse1。通过下拉开关管m9,clk_pulse1将vramp下拉至0v,开始新的vramp周期。clk_pulse1也可称为同步时钟循环周期,且同步时钟循环周期t为:t=vref*c0/ich。同步时钟循环周期与dc/dc变换系统开关周期的大小相同。

[0033]

或门芯片大多两个或四个输入端,输入端为其他数量的芯片需要定制,成本较高。

因此在一些实施例中,如图1所示,所述或门单元5包括第一或门51、第二或门52以及第三或门53,部分同步时钟产生单元中的第一脉冲产生器4的输出端与第一或门51的输入端连接,其余同步时钟产生单元中的第一脉冲产生器4的输出端与第二或门52的输入端连接,第一或门51的输出端以及第二或门52的输出端分别与第三或门53的输入端连接,使得电路中可采用两个或四个输入端而无需定制。

[0034]

实施例二

[0035]

如图2所示,本实施例提供一种可堆叠dc/dc变换系统,包括变换输入端vin、变换输出端vout、主芯片7和若干个从芯片8,所述主芯片7包括第一逻辑控制电路71、第一半桥电路72以及实施例一所述的同步时钟产生电路73,所述从芯片8包括第二逻辑控制电路81以及第二半桥电路82,第一半桥电路72的输入端以及第二半桥电路82的输入端分别与变换输入端vin连接,第一半桥电路72的输出端以及第二半桥电路82的输出端分别与变换输出端vout连接,所述同步时钟产生电路73分别向第一逻辑控制电路71以及第二逻辑控制电路81输出时钟信号,第一逻辑控制电路71与第一半桥电路72的控制端连接,第二逻辑控制电路81与第二半桥电路82的控制端连接。

[0036]

上述实施例中,同步时钟产生电路通过脉冲宽度来区分主芯片7时钟和从芯片8时钟,使得由主芯片7和从芯片8能够实现管脚功能复用,减少了主芯片7和从芯片8的输出端数量,使得可堆叠dc/dc变换系统走线更为简洁。

[0037]

对于主芯片7,其只接收脉冲宽度为10ns的同步时钟信号sync脉冲信号;对于从芯片8其通过自身编号来确定接收哪个同步时钟信号sync脉冲信号。如图3所示,第三个从芯片中,3就为其编号,表示该从从芯片接收的同步时钟信号sync脉冲信号为循环周期的第三个脉冲信号(10ns的同步时钟信号sync脉冲信号为计数的起点,并且10ns的同步时钟信号sync脉冲信号不计算在内)。不论是主芯片还是从芯片,接收到与其编号对应的同步时钟信号sync脉冲信号后,会向第一半桥电路72/第二半桥82发送pwm信号,控制一半桥电路72/第二半桥82的上下管开关。pwm信号的宽度由芯片的控制环路确定,以使得输出电压稳定在目标电压上。

[0038]

以上所述,仅是本实用新型较佳实施例而已,并非对本实用新型作任何形式上的限制,虽然本实用新型以较佳实施例公开如上,然而并非用以限定本实用新型,任何熟悉本专业的技术人员,在不脱离本实用新型技术方案范围内,当利用上述揭示的技术内容作出些许变更或修饰为等同变化的等效实施例,但凡是未脱离本实用新型技术方案内容,依据本实用新型技术是指对以上实施例所作的任何简单修改、等同变化与修饰,均属于本实用新型技术方案的范围内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。