基于fpga的三点压电驱动快摆镜迟滞补偿控制系统

技术领域:

1.本专利涉及一种压电驱动快摆镜,具体涉及一种基于fpga的三点压电驱动快摆镜迟滞补偿控制系统。

背景技术:

2.空间天文望远镜在轨工作环境非常复杂,探测器的探测精度会受多种复杂因素的影响,为了保证望远镜的探测器高质量成像和长时间的稳定,在采用飞行器高精度姿态控制与振动抑制等技术手段的基础上,需要借助精密稳像技术以消除各种扰动源对空间天文望远镜的影响。大口径快摆镜(large

‑

aperture fsm,lafsm)是空间天文望远镜精密稳像系统的关键组成部分,其对精细导星仪(fine guidance sensor,fgs)检测并反馈的视轴偏移量进行像移补偿,可有效抑制指向跟踪系统残余的视轴误差,实现高精度稳像。

3.随着纳米级定位技术的迅速发展,纳米量级压电精密驱动技术已逐渐成为现代精密定位与测量领域的关键技术。压电陶瓷执行器具有响应频率高,负载大及位移分辨率高等优点,其相比于音圈电机(voice coil actuators,vca)具有更高的谐振频率和位移分辨率,是稳像系统中快摆镜执行机构常用的驱动设备。然而,压电陶瓷执行器固有的迟滞非线性会对快摆镜像移补偿精度造成不利影响从而降低稳像系统的性能。

4.现场可编程门阵列(field programmable gate array,fpga)属于专用集成电路(application specific integrated circuit,asic)中集成度最高的一种,内部由大量的基本逻辑单元组成。fpga的i/o资源丰富并能够灵活配置,使其与外围器件连接非常方便。用户可对fpga内部的逻辑资源和i/o资源等重新配置,以定制用户所需的功能,极大地提高了系统设计的灵活性,缩短了产品的设计周期。不同于dsp和arm等顺序执行指令的技术原理,fpga可以实现真正的并行运算。目前先进的fpga中都包含了具有数字信号处理功能的硬件核心,这些经过优化处理的硬件dsp模块可以提高数据运算过程的时钟频率,使高速复杂的迟滞补偿运算能够稳定执行。因此,采用fpga完成基于多stop算子并联的pi逆模型在fpga的部署,实现三点驱动快摆镜中多压电陶瓷执行器的并行迟滞补偿与控制。

技术实现要素:

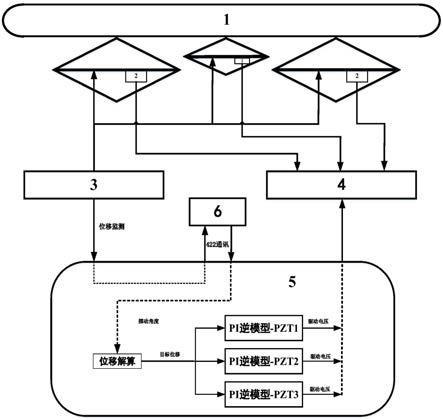

5.针对上述应用背景,本专利提出了一种基于fpga的高精度、快速响应的三点压电驱动快摆镜迟滞补偿控制系统,所述系统包括三点压电驱动快摆镜1,sgs微位移传感器(resistance strain gauge sensor)2、sgs信号调理与采集电路3、压电陶瓷驱动电路4、fpga迟滞补偿控制模块5和上位机6。上位机6通过422通讯接口将快摆镜的目标摆动角度信号发送给fpga迟滞补偿控制模块5,其中的位移解算将摆动角度解算为三点压电陶瓷执行器的目标位移,通过迟滞补偿算法将目标位移进行反解求得各个压电陶瓷执行器的驱动电压,经压电陶瓷驱动电路4对三点压电驱动快摆镜1转角的控制,从而实现了对压电陶瓷迟滞非线性的补偿;sgs微位移传感器2负责实时检测压电陶瓷执行器的位移,经sgs信号调理与采集电路3将位移信号输入进fpga迟滞补偿控制模块,并通过422通讯接口传输给上位机

6,完成压电陶瓷执行器位移的实时监测。

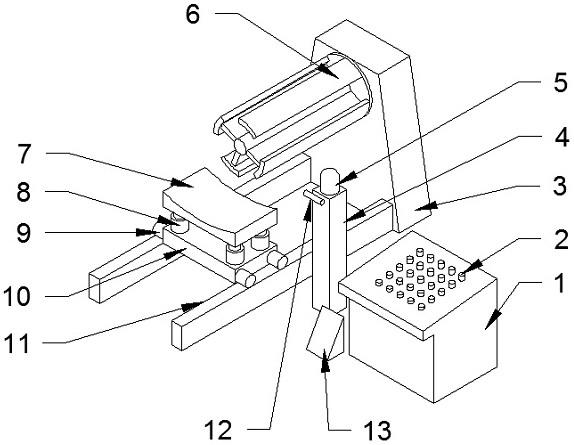

6.优选的,所述三点压电驱动快摆镜1以压电陶瓷执行器作为促动器,通过柔性支撑微位移放大机构对镜面进行驱动,镜面二维偏转采用三点并联驱动方式,三个压电陶瓷执行器围绕镜面中心呈等边三角形分布,每两个执行器和中心连线的夹角为120

°

。

7.优选的,所述压电陶瓷驱动电路4与fpga迟滞补偿控制模块5连接,由相互独立的三个驱动通道组成,用于对三点压电陶瓷执行器的并行驱动。所述电路还包括压电陶瓷驱动电源和16bits dac,所述压电陶瓷驱动电源与所述16bits dac相连,采用复合二级放大器对dac的输出电压进行放大,从而实现压电驱动快摆镜的驱动。

8.优选的,所述sgs信号调理与采集电路3与fpga迟滞补偿控制模块5连接,由相互独立的三个检测和采集通道组成,用于对三点压电陶瓷执行器实际位移的并行检测。所述电路还包括信号调理模块和18bits adc,所述信号调理模块用于将sgs位移传感器输出的差分电压信号转换为单端输出,并通过窄带巴特沃斯低通滤波器对检测的微弱位移信号进行去噪和放大;所述18bits adc为差分输入型,在模数转换前需要将单端电压转换为差分电压输入,用于将sgs检测的位移模拟信号转变为数字信号接入fpga迟滞补偿控制模块。

9.优选的,所述fpga迟滞补偿控制模块5利用fpga实现了多压电陶瓷执行器的并行迟滞补偿与控制算法,采用vhdl语言完成了基于多stop算子并联的pi(prandtl

–

ishlinskii)逆模型在fpga的部署,pi逆模型的系数需要事先采用智能优化算法根据已经采集好的输入电压

‑

输出位移数据进行标定。所述基于多stop算子并联的pi逆迟滞模型表达式中曲线上升段和下降段多项式阶次和系数可以由智能优化算法进行自适应调整来增强对于不同迟滞特性曲线的普适性,从而提高算法迟滞非线性补偿精度。

10.本专利充分利用了fpga的并行计算优势,降低了系统计算延时,提高了系统响应速度,实现高精度、实时和同步多压电补偿与控制。

附图说明:

11.图1是三点压电驱动快摆镜迟滞补偿控制系统结构图。

12.图2是压电迟滞补偿方式框图。

13.图3是改进stop算子的pi的逆模型结构图。

14.图4是fpga迟滞补偿控制模块软件架构图。

具体实施方式:

15.本专利采用逆模型迟滞补偿的方式来消除压电陶瓷迟滞非线性,利用pi迟滞逆模型来对位移解算模块得到的压电陶瓷执行器目标位移进行反解获得驱动电压并通过16bits d/a采集电路输出,经过压电陶瓷驱动电源驱动压电陶瓷执行器,从而实现目标输出与实际输出的线性化,如图2所示。

16.常规迟滞模型的输入为驱动电压,输出为位移,而逆迟滞模型的输入为位移,输出为驱动电压。针对压电迟滞逆模型的建立问题,为了避免复杂的求逆过程及对约束条件的制约,采用基于多stop算子并联的pi逆模型对压电迟滞逆模型直接建模。stop算子基于连续介质力学中的弹塑性行为,其离散数学形式如式(1)所示:

17.er(0)=min{r

i

,max{

‑

r

i

,y(k) er0}}

18.er(k)=min{r

i

,max{

‑

r

i

,y(k)

‑

y(k

‑

1) er(k

‑

t)}}

ꢀꢀꢀꢀ

(1)

19.其中,r

i

是算子阈值,n是算子数量,1≤i≤n,er0是算子初值,y(k)是输出位移。因压电执行器的输入电压是正值,故使用stop算子的单边形式为:

20.er(0)=min{r

i

,max{0,y(k) er0}}

21.er(k)=min{r

i

,max{0,y(k)

‑

y(k

‑

1) er(k

‑

t)}}

ꢀꢀꢀꢀꢀ

(2)

22.式(2)中的stop算子不能够有效拟合出非对称逆迟滞环,故对基本stop算子进行改进,如式(3)所示:

23.er(k)=min{r

i

,max{0,f(k)

‑

f(k

‑

1) er(k

‑

t)}}

[0024][0025]

f

l

(y(k))=a1[y(k)]3 a2[y(k)]2 a3y(k) a4[0026]

f

r

(y(k))=b1[y(k)]3 b2[y(k)]2 b3y(k) b4ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

(3)

[0027]

式中,f

r

(y(k))为逆迟滞曲线下降段的输出位移表示,f

l

(y(k))为逆迟滞曲线上升段的输出位移表示,a1~a4,b1~b4为多项式系数且都是正值。

[0028]

将式(3)的改进stop算子进行加权叠加可以建立改进pi逆模型:

[0029][0030][0031]

r

i

=ci

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

(4)

[0032]

其中,q是初载曲线权重,y(k)是输出位移,ω

i

是算子权重,n表示算子数量,τ,ρ,c为系数且都是正常数,基于改进stop算子的pi的逆模型结构如图3所示。

[0033]

对于不同工艺的压电陶瓷执行器,迟滞特性曲线也各有差别,反映在模型表达式上就是迟滞曲线上升段和下降段的多项式阶次和系数会有差异。利用事先采集好的压电陶瓷执行器的输入电压

‑

输出位移曲线,借助智能优化算法对模型中a1~a4,b1~b4,q,τ,ρ,c的值进行辨识,实现压电迟滞曲线的自适应拟合,并将辨识好的参数导入到建立好的fpga迟滞逆模型模块中,完成基于fpga平台的算法模型部署,软件架构如图4所示。

[0034]

sgs微位移传感器负责实时检测压电陶瓷执行器的伸缩量,经sgs信号调理与采集电路将位移信号输入进fpga,并通过422通讯接口传输给上位机,完成压电陶瓷执行器位移的实时监测。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。