1.本发明属于分布式存储技术领域,具体涉及一种实现分布式存储的加速芯片纠删码插件的优化方法及装置。

背景技术:

2.分布式存储系统通常采用纠删码来实现数据的冗余,如果因磁盘故障等问题导致数据的丢失,可以通过纠删码实现数据的恢复。分布式存储系统根据不同的开源代码实现了不同的纠删码插件。分布式系统通过加载插件来调用插件的编解码函数。随着加速芯片的出现,在分布式系统的架构上扩展了基于加速芯片纠删码插件,此种插件会直接调用芯片的驱动api来实现编解码功能,降低了系统cpu的利用率,提高了分布式系统的性能。常见的加速芯片实现了jerasure库和isa库的编解码矩阵,编解码矩阵有范德蒙和柯西等。加速芯片和cpu用同一个矩阵进行编码生成的数据是一样的。因此如果加速芯片有问题后,cpu可以临时代替加速芯片进行编解码,保证了分布式系统的可用性和可靠性。

3.然而分布式存储系统的纠删存储池创建的时候已经绑定了插件名和矩阵类型,如果使用加速芯片进行编解码的时候出了故障,纠删存储池就不可以使用。此时存储池如果想用cpu编解码,就要修改分布式存储系统纠删码插件调度模块的逻辑,这种方式更改了系统的架构,使代码逻辑复杂化,降低了系统的性能。

4.此为现有技术的不足,因此,针对现有技术中的上述缺陷,提供一种实现分布式存储的加速芯片纠删码插件的优化方法及装置,是非常有必要的。

技术实现要素:

5.针对现有技术的上述采用加速芯片纠删码插件直接调用芯片的驱动api来实现编解码功能时,若加速芯片进行编解码的时候出了故障,需要修改纠删码插件调度模块的逻辑来使用cpu编码,但使得代码逻辑复杂化,降低系统性能的缺陷,本发明提供一种实现分布式存储的加速芯片纠删码插件的优化方法及装置,以解决上述技术问题。

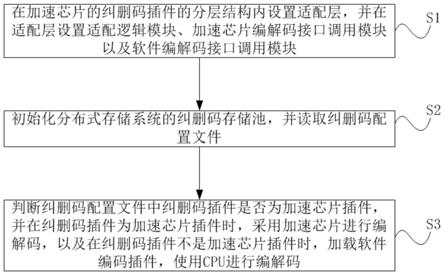

6.第一方面,本发明提供一种实现分布式存储的加速芯片纠删码插件的优化方法,包括如下步骤:

7.s1.在加速芯片的纠删码插件的分层结构内设置适配层,并在适配层设置适配逻辑模块、加速芯片编解码接口调用模块以及软件编解码接口调用模块;

8.s2.初始化分布式存储系统的纠删码存储池,并读取纠删码配置文件;

9.s3.判断纠删码配置文件中纠删码插件是否为加速芯片插件,并在纠删码插件为加速芯片插件时,采用加速芯片进行编解码,以及在纠删码插件不是加速芯片插件时,加载软件编码插件,使用cpu进行编解码。

10.进一步地,步骤s1具体步骤如下:

11.s11.在加速芯片的纠删码插件的分层结构内增设适配层;

12.s12.在适配层内设置适配逻辑模块、加速芯片编解码接口调用模块以及软件编解

码接口调用模块;

13.s13.设置加速芯片编解码接口调用模块连接驱动层的加速芯片编解码接口和接口层的编解码接口;

14.s14.设置软件编解码接口调用模块连接驱动层的加速芯片编解码接口和接口层的编解码接口;

15.s15.设置适配逻辑模块进行接口调用逻辑判断,并进行异常处理,选择连接加速芯片编解码接口调用模块或软件编解码接口调用模块。在原有加速芯片的纠删码插件的结构中增设适配层,增设纠删码插件选择调用的接口逻辑,并处理异常。

16.进一步地,驱动层的加速芯片编解码接口基于加速芯片物理层。加速芯片编解码接口包括编码接口和解码接口,编码接口和解码接口均基于加速芯片物理层实现编解码功能。

17.进一步地,步骤s2具体步骤如下:

18.s21.初始化分布式存储系统的纠删码存储池,将当前纠删码插件作为配置纠删码插件,写入纠删码配置文件;

19.s22.读取纠删码配置文件,获取配置纠删码插件。纠删码存储池初始化时会对纠删码插件采用加速芯片插件还是软件编码插件件选择。

20.进一步地,步骤s21具体步骤如下:

21.s211.判断加速芯片插件是否可用;

22.若是,进入步骤s212;

23.若否,进入步骤s213;

24.s212.设置加速芯片插件为当前纠删码插件,并将加速芯片插件作为配置纠删码插件写入纠删码配置文件,进入步骤s22;

25.s213.设置软件编码插件为当前纠删码插件,并将软件编码插件作为配置纠删码插件写入纠删码配置文件中,进入步骤s22。加速芯片插件作为物理插件,基于加速芯片物理层进行编解码,软件编码插件基于cpu基于编解码。

26.进一步地,步骤s3具体步骤如下:

27.s31.判断纠删码配置文件中配置纠删码插件是否为加速芯片插件;

28.若是,进入步骤s32;

29.若否,进入步骤s34;

30.s32.加载加速芯片插件,并通过加速芯片插件进行编解码;

31.s33.判断加速芯片插件编解码过程是否有异常;

32.若否,返回编解码数据,结束;

33.若是,进入步骤s35;

34.s34.加载软件编码插件;

35.s35.通过cpu进行编解码,并返回编解码数据。根据配置文件中加载的纠删码插件是否为加速芯片插件选择加载的插件以及编解码的载体,并且当加载加速芯片插件,但加速芯片插件编解码异常时,仍可以采用cpu解码,提高了分布式存储系统稳定性,并简化了原有编解码逻辑。

36.进一步地,软件编码插件包括jerasure插件或isa插件。jerasure插件或isa插件

支撑与加速芯片同样的编解码矩阵。

37.第二方面,本发明提供一种实现分布式存储的加速芯片纠删码插件的优化装置,包括:

38.适配层设置单元,用于在加速芯片的纠删码插件的分层结构内设置适配层,并在适配层设置适配逻辑模块、加速芯片编解码接口调用模块以及软件编解码接口调用模块;

39.纠删码存储池初始化单元,用于初始化分布式存储系统的纠删码存储池,并读取纠删码配置文件;

40.纠删码插件判断及编解码单元,用于判断纠删码配置文件中纠删码插件是否为加速芯片插件,并在纠删码插件为加速芯片插件时,采用加速芯片进行编解码,以及在纠删码插件不是加速芯片插件时,加载软件编码插件,使用cpu进行编解码。

41.进一步地,适配层设置单元包括:

42.适配层设置子单元,用于在加速芯片的纠删码插件的分层结构内增设适配层;

43.适配层内模块设置子单元,用于在适配层内设置适配逻辑模块、加速芯片编解码接口调用模块以及软件编解码接口调用模块;

44.加速芯片编解码接口连接设置子单元,用于设置加速芯片编解码接口调用模块连接驱动层的加速芯片编解码接口和接口层的编解码接口;

45.软件编解码接口连接设置子单元,用于设置软件编解码接口调用模块连接驱动层的加速芯片编解码接口和接口层的编解码接口;

46.接口调用逻辑设置子单元,用于设置适配逻辑模块进行接口调用逻辑判断,并进行异常处理,选择连接加速芯片编解码接口调用模块或软件编解码接口调用模块;

47.纠删码存储池初始化单元包括:

48.纠删码存储池初始化子单元,用于初始化分布式存储系统的纠删码存储池,将当前纠删码插件作为配置纠删码插件,写入纠删码配置文件;

49.配置纠删码插件获取子单元,用于读取纠删码配置文件,获取配置纠删码插件;

50.纠删码插件判断及编解码单元包括:

51.纠删码插件判断子单元,用于判断纠删码配置文件中配置纠删码插件是否为加速芯片插件;

52.加速芯片插件加载子单元,用于纠删码插件为加速芯片插件时,加载加速芯片插件,并通过加速芯片插件进行编解码;

53.编解码异常判断子单元,用于判断加速芯片插件编解码过程是否有异常;

54.编解码数据返回子单元,用于加速芯片插件编解码过程无异常时,返回编解码数据;

55.软件编码插件加载子单元,用于纠删码插件不是加速芯片插件时,加载软件编码插件;

56.cpu编解码子单元,用于加速芯片插件编解码异常或者加载软件编码插件后,通过cpu进行编解码,并返回编解码数据。

57.进一步地,纠删码存储池初始化子单元包括:

58.加速芯片插件可用判断组件,用于判断加速芯片插件是否可用;

59.加速芯片插件写入组件,用于加速芯片插件可用时,设置加速芯片插件为当前纠

删码插件,并将加速芯片插件作为配置纠删码插件写入纠删码配置文件;

60.软件编码插件写入组件,用于加速芯片插件不可用时,设置软件编码插件为当前纠删码插件,并将软件编码插件作为配置纠删码插件写入纠删码配置文件中。

61.本发明的有益效果在于,

62.本发明提供的实现分布式存储的加速芯片纠删码插件的优化方法及装置,通过在加速芯片原有的分层结构添加适配层,优化了纠删码插件适配及编解码的逻辑,提高了分布式存储系统的可靠性和稳定性。

63.此外,本发明设计原理可靠,结构简单,具有非常广泛的应用前景。

64.由此可见,本发明与现有技术相比,具有突出的实质性特点和显著的进步,其实施的有益效果也是显而易见的。

附图说明

65.为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,对于本领域普通技术人员而言,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

66.图1是本发明实现分布式存储的加速芯片纠删码插件的优化方法的流程示意图一。

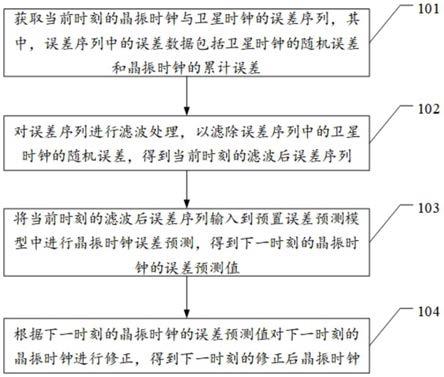

67.图2是本发明实现分布式存储的加速芯片纠删码插件的优化方法的流程示意图二。

68.图3为本发明实现分布式存储的加速芯片纠删码插件的优化装置示意图。

69.图中,1

‑

适配层设置单元;1.1

‑

适配层设置子单元;1.2

‑

适配层内模块设置子单元;1.3

‑

加速芯片编解码接口连接设置子单元;1.4

‑

软件编解码接口连接设置子单元;1.5

‑

接口调用逻辑设置子单元;2

‑

纠删码存储池初始化单元;2.1

‑

纠删码存储池初始化子单元;2.2

‑

配置纠删码插件获取子单元;3

‑

纠删码插件判断及编解码单元;3.1

‑

纠删码插件判断子单元;3.2

‑

加速芯片插件加载子单元;3.3

‑

编解码异常判断子单元;3.4

‑

编解码数据返回子单元;3.5

‑

软件编码插件加载子单元;3.6

‑

cpu编解码子单元。

具体实施方式

70.为了使本技术领域的人员更好地理解本发明中的技术方案,下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都应当属于本发明保护的范围。

71.下面对本发明中出现的关键术语进行解释。

72.加速芯片:一种用于计算的芯片,和cpu一样。

73.纠删码:纠删码(erasure coding,ec)是一种数据保护方法,它将数据分割成片段,把冗余数据块扩展、编码,并将其存储在不同的位置,比如磁盘、存储节点或者其它地理位置。

74.纠删码存储池:存储池的一种实现方式,它通过纠删码实现了数据的冗余。

75.纠删码插件:不同的纠删码以插件的形式实现,分布式存储系统的存储池初始化的时候通过配置来决定和加载纠删码插件。常见的有jerasure插件和isa插件。

76.编解码矩阵:常见有范德蒙矩阵和柯西矩阵,jerasure和isa都实现了这两种矩阵,但同一种矩阵的实现的又不相同,cpu和加速芯片可以通过矩阵来计算解码数据。

77.实施例1:

78.如图1所示,本发明提供一种实现分布式存储的加速芯片纠删码插件的优化方法,包括如下步骤:

79.s1.在加速芯片的纠删码插件的分层结构内设置适配层,并在适配层设置适配逻辑模块、加速芯片编解码接口调用模块以及软件编解码接口调用模块;

80.s2.初始化分布式存储系统的纠删码存储池,并读取纠删码配置文件;

81.s3.判断纠删码配置文件中纠删码插件是否为加速芯片插件,并在纠删码插件为加速芯片插件时,采用加速芯片进行编解码,以及在纠删码插件不是加速芯片插件时,加载软件编码插件,使用cpu进行编解码。

82.实施例2:

83.如图2所示,本发明提供一种实现分布式存储的加速芯片纠删码插件的优化方法,包括如下步骤:

84.s1.在加速芯片的纠删码插件的分层结构内设置适配层,并在适配层设置适配逻辑模块、加速芯片编解码接口调用模块以及软件编解码接口调用模块;具体步骤如下:

85.s11.在加速芯片的纠删码插件的分层结构内增设适配层;

86.s12.在适配层内设置适配逻辑模块、加速芯片编解码接口调用模块以及软件编解码接口调用模块;

87.s13.设置加速芯片编解码接口调用模块连接驱动层的加速芯片编解码接口和接口层的编解码接口;

88.s14.设置软件编解码接口调用模块连接驱动层的加速芯片编解码接口和接口层的编解码接口;

89.s15.设置适配逻辑模块进行接口调用逻辑判断,并进行异常处理,选择连接加速芯片编解码接口调用模块或软件编解码接口调用模块;

90.s2.初始化分布式存储系统的纠删码存储池,并读取纠删码配置文件;具体步骤如下:

91.s21.初始化分布式存储系统的纠删码存储池,将当前纠删码插件作为配置纠删码插件,写入纠删码配置文件;

92.s22.读取纠删码配置文件,获取配置纠删码插件;

93.s3.判断纠删码配置文件中纠删码插件是否为加速芯片插件,并在纠删码插件为加速芯片插件时,采用加速芯片进行编解码,以及在纠删码插件不是加速芯片插件时,加载软件编码插件,使用cpu进行编解码;具体步骤如下:

94.s31.判断纠删码配置文件中配置纠删码插件是否为加速芯片插件;

95.若是,进入步骤s32;

96.若否,进入步骤s34;

97.s32.加载加速芯片插件,并通过加速芯片插件进行编解码;

98.s33.判断加速芯片插件编解码过程是否有异常;

99.若否,返回编解码数据,结束;

100.若是,进入步骤s35;

101.s34.加载软件编码插件;

102.s35.通过cpu进行编解码,并返回编解码数据。

103.实施例3:

104.如图2所示,本发明提供一种实现分布式存储的加速芯片纠删码插件的优化方法,包括如下步骤:

105.s1.在加速芯片的纠删码插件的分层结构内设置适配层,并在适配层设置适配逻辑模块、加速芯片编解码接口调用模块以及软件编解码接口调用模块;具体步骤如下:

106.s11.在加速芯片的纠删码插件的分层结构内增设适配层;

107.s12.在适配层内设置适配逻辑模块、加速芯片编解码接口调用模块以及软件编解码接口调用模块;

108.s13.设置加速芯片编解码接口调用模块连接驱动层的加速芯片编解码接口和接口层的编解码接口;驱动层的加速芯片编解码接口基于加速芯片物理层;

109.s14.设置软件编解码接口调用模块连接驱动层的加速芯片编解码接口和接口层的编解码接口;

110.s15.设置适配逻辑模块进行接口调用逻辑判断,并进行异常处理,选择连接加速芯片编解码接口调用模块或软件编解码接口调用模块;

111.s2.初始化分布式存储系统的纠删码存储池,并读取纠删码配置文件;具体步骤如下:

112.s21.初始化分布式存储系统的纠删码存储池,将当前纠删码插件作为配置纠删码插件,写入纠删码配置文件;具体步骤如下:

113.s211.判断加速芯片插件是否可用;

114.若是,进入步骤s212;

115.若否,进入步骤s213;

116.s212.设置加速芯片插件为当前纠删码插件,并将加速芯片插件作为配置纠删码插件写入纠删码配置文件,进入步骤s22;

117.s213.设置软件编码插件为当前纠删码插件,并将软件编码插件作为配置纠删码插件写入纠删码配置文件中,进入步骤s22;软件编码插件包括jerasure插件或isa插件;

118.s22.读取纠删码配置文件,获取配置纠删码插件;

119.s3.判断纠删码配置文件中纠删码插件是否为加速芯片插件,并在纠删码插件为加速芯片插件时,采用加速芯片进行编解码,以及在纠删码插件不是加速芯片插件时,加载软件编码插件,使用cpu进行编解码;具体步骤如下:

120.s31.判断纠删码配置文件中配置纠删码插件是否为加速芯片插件;

121.若是,进入步骤s32;

122.若否,进入步骤s34;

123.s32.加载加速芯片插件,并通过加速芯片插件进行编解码;

124.s33.判断加速芯片插件编解码过程是否有异常;

125.若否,返回编解码数据,结束;

126.若是,进入步骤s35;

127.s34.加载软件编码插件;

128.s35.通过cpu进行编解码,并返回编解码数据。

129.实施例4:

130.如图3所示,本发明提供一种实现分布式存储的加速芯片纠删码插件的优化装置,包括:

131.适配层设置单元1,用于在加速芯片的纠删码插件的分层结构内设置适配层,并在适配层设置适配逻辑模块、加速芯片编解码接口调用模块以及软件编解码接口调用模块;

132.纠删码存储池初始化单元2,用于初始化分布式存储系统的纠删码存储池,并读取纠删码配置文件;

133.纠删码插件判断及编解码单元3,用于判断纠删码配置文件中纠删码插件是否为加速芯片插件,并在纠删码插件为加速芯片插件时,采用加速芯片进行编解码,以及在纠删码插件不是加速芯片插件时,加载软件编码插件,使用cpu进行编解码。

134.实施例5:

135.如图3所示,本发明提供一种实现分布式存储的加速芯片纠删码插件的优化装置,包括:

136.适配层设置单元1,用于在加速芯片的纠删码插件的分层结构内设置适配层,并在适配层设置适配逻辑模块、加速芯片编解码接口调用模块以及软件编解码接口调用模块;适配层设置单元1包括:

137.适配层设置子单元1.1,用于在加速芯片的纠删码插件的分层结构内增设适配层;

138.适配层内模块设置子单元1.2,用于在适配层内设置适配逻辑模块、加速芯片编解码接口调用模块以及软件编解码接口调用模块;

139.加速芯片编解码接口连接设置子单元1.3,用于设置加速芯片编解码接口调用模块连接驱动层的加速芯片编解码接口和接口层的编解码接口;

140.软件编解码接口连接设置子单元1.4,用于设置软件编解码接口调用模块连接驱动层的加速芯片编解码接口和接口层的编解码接口;

141.接口调用逻辑设置子单元1.5,用于设置适配逻辑模块进行接口调用逻辑判断,并进行异常处理,选择连接加速芯片编解码接口调用模块或软件编解码接口调用模块;

142.纠删码存储池初始化单元2,用于初始化分布式存储系统的纠删码存储池,并读取纠删码配置文件;纠删码存储池初始化单元2包括:

143.纠删码存储池初始化子单元2.1,用于初始化分布式存储系统的纠删码存储池,将当前纠删码插件作为配置纠删码插件,写入纠删码配置文件;

144.配置纠删码插件获取子单元2.2,用于读取纠删码配置文件,获取配置纠删码插件;

145.纠删码插件判断及编解码单元3,用于判断纠删码配置文件中纠删码插件是否为加速芯片插件,并在纠删码插件为加速芯片插件时,采用加速芯片进行编解码,以及在纠删码插件不是加速芯片插件时,加载软件编码插件,使用cpu进行编解码;纠删码插件判断及编解码单元3包括:

146.纠删码插件判断子单元3.1,用于判断纠删码配置文件中配置纠删码插件是否为加速芯片插件;

147.加速芯片插件加载子单元3.2,用于纠删码插件为加速芯片插件时,加载加速芯片插件,并通过加速芯片插件进行编解码;

148.编解码异常判断子单元3.3,用于判断加速芯片插件编解码过程是否有异常;

149.编解码数据返回子单元3.4,用于加速芯片插件编解码过程无异常时,返回编解码数据;

150.软件编码插件加载子单元3.5,用于纠删码插件不是加速芯片插件时,加载软件编码插件;

151.cpu编解码子单元3.6,用于加速芯片插件编解码异常或者加载软件编码插件后,通过cpu进行编解码,并返回编解码数据。

152.实施例6:

153.如图3所示,本发明提供一种实现分布式存储的加速芯片纠删码插件的优化装置,包括:

154.适配层设置单元1,用于在加速芯片的纠删码插件的分层结构内设置适配层,并在适配层设置适配逻辑模块、加速芯片编解码接口调用模块以及软件编解码接口调用模块;适配层设置单元1包括:

155.适配层设置子单元1.1,用于在加速芯片的纠删码插件的分层结构内增设适配层;

156.适配层内模块设置子单元1.2,用于在适配层内设置适配逻辑模块、加速芯片编解码接口调用模块以及软件编解码接口调用模块;

157.加速芯片编解码接口连接设置子单元1.3,用于设置加速芯片编解码接口调用模块连接驱动层的加速芯片编解码接口和接口层的编解码接口;

158.软件编解码接口连接设置子单元1.4,用于设置软件编解码接口调用模块连接驱动层的加速芯片编解码接口和接口层的编解码接口;

159.接口调用逻辑设置子单元1.5,用于设置适配逻辑模块进行接口调用逻辑判断,并进行异常处理,选择连接加速芯片编解码接口调用模块或软件编解码接口调用模块;

160.纠删码存储池初始化单元2,用于初始化分布式存储系统的纠删码存储池,并读取纠删码配置文件;纠删码存储池初始化单元2包括:

161.纠删码存储池初始化子单元2.1,用于初始化分布式存储系统的纠删码存储池,将当前纠删码插件作为配置纠删码插件,写入纠删码配置文件;纠删码存储池初始化子单元2.1包括:

162.加速芯片插件可用判断组件,用于判断加速芯片插件是否可用;

163.加速芯片插件写入组件,用于加速芯片插件可用时,设置加速芯片插件为当前纠删码插件,并将加速芯片插件作为配置纠删码插件写入纠删码配置文件;

164.软件编码插件写入组件,用于加速芯片插件不可用时,设置软件编码插件为当前纠删码插件,并将软件编码插件作为配置纠删码插件写入纠删码配置文件中;

165.配置纠删码插件获取子单元2.2,用于读取纠删码配置文件,获取配置纠删码插件;

166.纠删码插件判断及编解码单元3,用于判断纠删码配置文件中纠删码插件是否为

加速芯片插件,并在纠删码插件为加速芯片插件时,采用加速芯片进行编解码,以及在纠删码插件不是加速芯片插件时,加载软件编码插件,使用cpu进行编解码;纠删码插件判断及编解码单元3包括:

167.纠删码插件判断子单元3.1,用于判断纠删码配置文件中配置纠删码插件是否为加速芯片插件;

168.加速芯片插件加载子单元3.2,用于纠删码插件为加速芯片插件时,加载加速芯片插件,并通过加速芯片插件进行编解码;

169.编解码异常判断子单元3.3,用于判断加速芯片插件编解码过程是否有异常;

170.编解码数据返回子单元3.4,用于加速芯片插件编解码过程无异常时,返回编解码数据;

171.软件编码插件加载子单元3.5,用于纠删码插件不是加速芯片插件时,加载软件编码插件;

172.cpu编解码子单元3.6,用于加速芯片插件编解码异常或者加载软件编码插件后,通过cpu进行编解码,并返回编解码数据。

173.尽管通过参考附图并结合优选实施例的方式对本发明进行了详细描述,但本发明并不限于此。在不脱离本发明的精神和实质的前提下,本领域普通技术人员可以对本发明的实施例进行各种等效的修改或替换,而这些修改或替换都应在本发明的涵盖范围内/任何熟悉本技术领域的技术人员在本发明揭露的技术范围内,可轻易想到变化或替换,都应涵盖在本发明的保护范围之内。因此,本发明的保护范围应所述以权利要求的保护范围为准。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。