1.本发明涉及一种用于直接存储器访问(direct memory access,dma)的系统和方法。具体地,本发明涉及一种具有增强的应对攻击的安全性的用于dma的系统和方法。

背景技术:

2.直接存储器访问(direct memory access,dma)允许数据在不消耗处理器负载进行数据访问的情况下从存储器读出数据或者向存储器写入数据。图1所示的是一种dma控制器与存储器运行的模型系统。该系统100包括处理器核心102、dma控制器104、以及存储器106。处理器核心102确定进入dma模式,以及初始化dma控制器104。作为响应,dma控制器104请求访问总线108,以及在被授权后开始在指定的地址上从存储器106读出数据或者向存储器106写入数据。对于存储器106的访问不需要处理器核心102的参与。

3.在dma控制器的块移动模式下,数据的读和/或写是在数据块内以步进递增的地址顺序而运行的。外部攻击能够从块移动操作的时序和功耗特征中搜集信息。存在着对于安全dma系统和方法的需求。

技术实现要素:

4.本发明内容被提供以介绍以下具体实施方式部分详述的概念中经选择的简化部分。本发明内容并不意欲确定权利要求中内容的关键或必要特征,亦不意欲使其限制权利要求的范围。

5.根据一种实施方式,一种用于直接存储器访问的方法包括:

6.接收直接存储器访问请求,所述直接存储器访问请求指定存储器中待访问的数据块中的地址;

7.将访问数据块的地址的顺序随机化;以及

8.以经随机化的地址顺序访问存储器。

9.在一个或多个实施方式中,将地址的顺序随机化包括:

10.响应于所接收的直接存储器访问请求而选择模式;以及

11.使用所选择的模式,变换存储器中待访问的各地址的位的位置。

12.在一个或多个实施方式中,所述模式选自多个模式,多个模式的每一个配置为变换存储器中待访问的地址的位的位置。

13.在一个或多个实施方式中,变换各地址的位的位置包括:变换存储器中待访问的地址的最低有效位的位置。

14.在一个或多个实施方式中,将地址的顺序随机化包括:向存储器中待访问的各地址分配对应的随机访问顺序。

15.在一个或多个实施方式中,将地址的顺序随机化包括:在存储器中待访问的指定地址之间插入冗余地址。

16.在一个或多个实施方式中,以经随机化的地址顺序访问存储器包括从存储器读取

数据和向存储器写入数据中的一个或多个。

17.在一个或多个实施方式中,以经随机化的地址顺序访问存储器包括以下一个或多个:从第一存储器向第二存储器复制数据、从存储器的第一部分向存储器的第二部分复制数据。

18.根据一种实施方式,一种用于直接存储器访问的方法包括:

19.接收直接存储器访问请求,所述直接存储器访问请求指定以第一顺序访问存储器中的地址;

20.以不同于第一顺序的第二顺序访问存储器中的地址。

21.在一个或多个实施方式中,地址的第一顺序是地址的步进递增顺序。

22.在一个或多个实施方式中,使用选自多个切换模式中的一个切换模式,提供地址的第二顺序。

23.在一个或多个实施方式中,使用切换模式提供第二顺序包括:变换直接存储器访问请求指定的地址的位的位置。

24.在一个或多个实施方式中,变换地址的位的位置包括:变换地址的最低有效位的位置。

25.在一个或多个实施方式中,所述方法进一步包括:为各地址分配随机顺序。

26.在一个或多个实施方式中,所述方法进一步包括:通过响应于直接存储器访问请求指定从存储器读取数据而向指定地址插入冗余地址,来扩展待访问的地址。

27.根据一种实施方式,一种用于直接存储器访问的系统包括:

28.dma控制器,配置为接收直接存储器访问请求,其中直接存储器访问请求指定存储器的待访问的地址;以及

29.乱序单元,配置为随机化指定的地址的顺序;

30.其中dma控制器进一步配置为用经乱序单元随机化的顺序访问存储器的地址。

31.在一个或多个实施方式中,乱序单元配置为通过为各指定的地址分配随机访问顺序而随机化指定的地址的顺序。

32.在一个或多个实施方式中,乱序单元配置为响应于直接存储器访问请求指定从存储器读取数据而向指定的地址加入至少一个冗余地址。

33.在一个或多个实施方式中,乱序单元配置为向指定的地址应用切换模式,以变换各指定的地址中的位的位置。

34.在一个或多个实施方式中,乱序单元配置为变换指定的地址的最低有效位的位置。

附图说明

35.为使本发明前述内容可以更具体的方式得以理解,本发明的进一步详细的描述可以参考实施方式而得到,其中部分由所附的图例而展示。所附图例仅展示本发明的典型实施方式,且因本发明可以具有其他相同地有效实施方式,所附图例不应理解为限制本发明的范围。附图是为便于理解而非测量本发明而绘制。对于本领域的技术人员而言,在阅读了本描述并结合所附图例,所要求的发明主题的益处将易于理解。在附图中,相似的标记数字被用来指示相似的元件,以及:

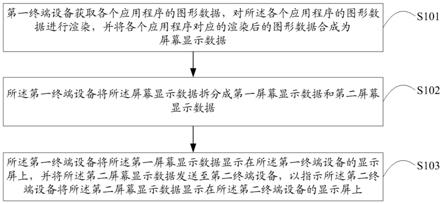

36.图1是dma控制器与存储器交互的系统的模型;

37.图2是根据一种实施方式的用于直接存储器访问的系统;

38.图3是将访问顺序与重排序的地址相映射的示例的表;

39.图4是将访问顺序与重排序的地址相映射的另一示例的表;

40.图5是根据一种实施方式的将切换模式与地址中的位的位置变动相对应的切换表;

41.图6是展示根据图5中的一种切换模式的重排序的地址的示例的表;以及

42.图7是根据一种实施方式的用于直接存储器访问的方法的流程图。

具体实施方式

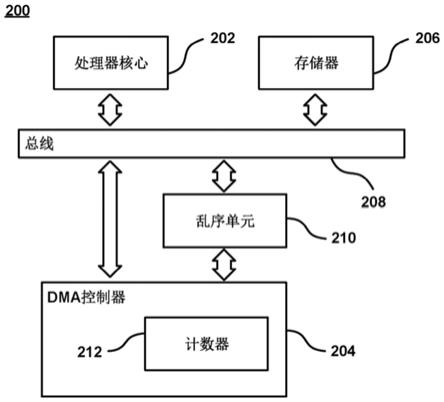

43.图2是根据本发明一种实施方式的用于直接存储器访问的系统。该系统200包括处理器核心202、dma控制器204、以及存储器206,其与图1中所示的相似。dma控制器204由处理器核心202接收dma请求命令。来自处理器核心202的请求命令发起经dma中继的数据传输,以及配置dma控制器204来用于进行数据访问操作,例如从存储器206中读出至少一个数据块,或者将数据写入存储器206。dma控制器204可以以数据字为单位来执行数据访问操作。数据块包括多个数据字,每个字与存储器206中的一个地址相关联。在本实施方式中,dma控制器204通过总线208进行通信。总线208可以实施为高级微处理器总线架构(advanced microcontroller bus architecture,)、ahb(advanced high-performance bus,高级高性能总线)、apb(advanced peripheral bus,高级外围总线),或者任何其他适于加载相应通信协议的可适用的连接。

44.响应于来自处理器核心202的dma请求命令,dma控制器204指定数据将被读取或写入的地址,其中数据的每个字与存储器206中的一个地址相关联,在本例中亦即数据的每个字被从存储器206中的一个地址读出或向存储器206中的一个地址写入。dma控制器204可以包括dma寄存器,分别用来设置指定对于特定的dma通道的存储器206中将访问的地址的值、以及设置将要传输的数据单元(即数据字)的数量的计数值。系统200还包括乱序单元210,乱序单元210连接到dma控制器204,以及与总线208耦接。在其他实施方式中,乱序单元210被集成在dma控制器204中。乱序单元210将存储器206中的读出或写入的地址的顺序进行随机化。与图1中的系统100以步进递增的地址顺序执行包括多个字的数据块的读出或写入、从而易受攻击所不同的是,图2的实施方式中的系统200包括该乱序单元210来将数据块中的字的读出或写入到地址的顺序打乱。

45.根据一种实施方式,乱序单元210包括查找表,查找表将访问存储器206的顺序和乱序的地址相映射。乱序单元210使用由dma控制器204指定的地址来根据查找表而产生乱序的地址。图3示出了作为简化的示例的查找表,其将访问顺序与存储器206中的用于四个字大小的数据块的乱序的地址相映射,并与步进递增地址相比较。由图3的示例可见,存储器206中的将被访问的第一顺序的字的地址是“110000010”,在顺次地递增的访问顺序中其是第三顺序。存储器206中的将被第二顺序访问的字的地址是“110000000”,在顺次递增的访问顺序中其是第一个被访问的。地址“110000011”是第三顺序被访问,在顺次递增的访问顺序中其是第四顺序。地址“110000001”最后在第四顺序被访问,而在顺序递增的访问中其是第二个被访问。然而,在其他实施方式中,或者对于即使是对存储器206中的同一数据块

的另一次数据访问请求,不同的、动态的乱序访问地址顺序均可适用。乱序单元210提供了对于存储器206的乱序的访问,从而对于外部攻击而言展现出了不同时序和功耗,故此增强了安全性。

46.图3所示的示例可以实施为对于将访问的地址指定一个随机的顺序,或者对于每个访问顺序指定一个从将访问的地址中随机选择的地址。应注意的是,指定地址或指定顺序应保证每个目标地址被访问至少一次,故此可能有重复的地址被指定了不同的访问顺序。图3中的示例的实施方式还可理解为对于地址的最低有效位(least significant bits,lsbs)执行了随机化。根据其他实施方式,可以随机化地址中的更多或更少的lsb,以产生dma控制器204访问存储器206的乱序的地址。系统200可以提供对于地址的不同访问顺序,即使对于存储器206中的相同数据块,从而访问相同的数据块亦能具有不同的时序和功率使用特征,进一步地通过展现不同的时序和功耗模型而增强安全性。

47.在另一实施方式中,优选地在读操作中,乱序单元210加入将访问的冗余地址,来进一步地增强鲁棒性。如图4,其示出了用于访问存储器中的4个字的数据块的此种示例。除了将欲访问的地址的顺序随机化之外,在第二、第三、第五、第七顺序上加入了“冗余”地址。在该实施方式中,对于存储器206中的4个字的数据块的访问被扩展为看起来是对于8个字的数据块的访问,而其中所访问的(读出的或写入的)一半的字为冗余数据。由该实施方式可见,所访问的地址的数目加倍,视为数据块的大小被加倍。此外,在其他实施方式中,数据块的大小的缩放可以是不同的,唯得保证存储器206中的被访问的地址不连续地增加。图4中的示例实施方式还可理解为将地址的3个lsb进行随机化,将有效地址与“冗余”地址相混。在各实施方式中,dma控制器204还可配置为复制访问行为。例如,当特定的地址位由“0”转为“1”时,dma控制器204在存储器206中的与适才访问的地址相同的地址上复制其访问行为。可以理解的是,由于最低有效位(lsb,亦称为较低有效位,lower significant bits)相比于较高有效位而言翻转的次数更多,对于lsb或者msb(middle significant bits,中等有效位)的翻转的前述特定的地址位的选择,将导致不同数目的访问行为的复制。

48.在各实施方式中,dma控制器包括计数器212。计数器212可以实施为计数寄存器,它的值可以由处理器核心202通过dma请求命令来设置。计数器值指定了由存储器206所读出或向存储器206写入的数据字的数目。随后,在一个有效的字被读出或写入存储器206时,计数器212倒数计数。计数器212倒数至零时,表明dma控制器204对于存储器206的访问完成。应当说明的是,对于“冗余”地址的访问或者复制的访问行为不被计数器212计数,这是因为所访问的数据非“有效”。尽管图4的实施方式中的“冗余”地址配置为与所访问的有效地址不同,例如将访问行为指向了不同的数据块或者不相关的地址,但是在其他实施方式中,在被访问的数据块中的有效地址亦可被重复访问。此外,dma控制器204配置为进一步地通过在特定时间将计数器212的值设置为预设值从而重复访问至少部分地址来使其访问随机化。例如,对于由存储器206中读出4个字的数据块的读操作,在读取了3个有效字后,dma控制器将计数器212的值设为“2”,指示为仅有2个字被读取。dma控制器204随后重新执行第三个字的读取操作。

49.根据另一实施方式,乱序单元210可以实施为开关。图5示出了根据一种实施方式的切换表。对于给定的访问回合,实施为开关的该乱序单元210的实施方式通过在选定的切换模式下变换指定的地址的lsb的位置,来将地址的lsb随机化。切换模式是响应于来自dma

控制器202的数据访问请求而选择的。如图5所示,对于3位lsb地址的随机化(对应于8个字的数据块访问),存在3!-1即5种可能的乱序切换模式,其中切换模式0提供的是相同的地址顺序。对于向存储器206的一次访问,在选择了切换模式后,乱序单元210将对于存储器206的访问指向基于顺次递增地址但不同于顺次递增地址而排序的地址。顺次递增地址被提供为乱序单元210的输入。乱序单元210通过使用选定的切换模式来变换所输入的地址的lsb而提供重排序的地址。在所有的3位lsb地址均处理、以及对于8个字的数据块的访问基于经处理的地址顺序而完成后,对于另一次数据访问操作可以选择不同的切换模式。对于切换模式的选择随着将访问的数据块而变化,并且即使相同的数据块亦可应用不同的切换模式。

50.图6示出了根据图5的切换表而选择切换模式4时乱序单元210的重排序的地址。存储器206中被访问的第一顺序的地址是“110000000”,其与连续递增地址中相同。被访问的第二顺序的地址是“110000010”,其通过将第二顺序的步进递增地址“110000001”使用切换模式4来对3个lsb的位置进行变换而产生,其中将地址的3个lsb“001”转换为“010”。根据图5中的切换模式4,输入地址中的最右位in[0]被置于3个lsb的中间位置作为out[1],输入地址的3个lsb中的中间位in[1]被变换为最左位作为out[2],而输入地址的3个lsb中的最左位in[2]则成为重排序的地址中的最右位而作为out[0]。根据该实施方式,存储器206中的地址被访问的顺序不同于步进递增顺序。对于存储器206的访问通过展现不同的时间和功耗特征而具有鲁棒性。

[0051]

回到图3所示的例子,地址的2个lsb被变换了位置。在其他实施方式中,图3所示的例子还可以实施为使用图6所示的切换模式选择示例,并且更多的lsb可适用于变换其位置。尽管数据块中的地址被通过图5和图6中的实施方式的“预定”的顺序进行访问,考虑到潜在可选择的模式的选项数量,访问的地址的顺序显著地不同于顺次递增的顺序,该实施方式仍可认为是使地址顺序得到随机化。

[0052]

图7所示的是根据一种实施方式的用于直接存储器访问的方法的流程图。该方法在此参考图2中所示的系统200而描述。步骤702,dma控制器204从处理器核心202接收dma请求,例如经由总线208接收。如前所述地,来自处理器核心202的dma请求可以指定存储器206中将被访问的目标地址,以及所访问的数据的大小。步骤704,作为对于来自处理器核心202的dma请求的响应,dma控制器204启动dma操作,请求对于总线208的访问、对计数器212设置一个由dma请求所指定的数据大小的值、以及用由dma请求所指定的目标地址来启动乱序单元210。步骤706,乱序单元210对将访问的存储器206的地址进行重排序。乱序单元210可以通过以上所述的各示例的途径来对地址进行重排序,例如通过如图3所示的重排序地址的lsb、通过如图4所示的插入不相关的“冗余”地址、通过如图5和图6所示的选择切换模式和变换地址位等。

[0053]

在该方法的步骤708,dma控制器204以来自乱序单元210的重排序的地址来访问存储器206。步骤708所述的对存储器206的访问可以用逐字的方式执行。故此,步骤706的对地址重排序和步骤708的以重排序地址访问存储器206可以通过一次性地重排序所有字的地址而连续地进行,也可以通过重排序一个地址并访问该重排序的地址而交替地进行。

[0054]

前述“访问”可以实施为读取操作而从存储器的访问地址上读取数据,或者实施为写入操作而向存储器的访问地址上写入数据,或者实施为复制操作而从一个存储器的访问

地址上读出数据并向另一存储器的访问地址上写入所读出的数据、或者实施为存储器内的复制操作而从第一部分读出数据并将所读出的数据写入第二部分。各实施方式的dma系统和方法以随机化的顺序访问存储器的地址,而非以步进递增的顺序。在每个访问存储器的回合中,该系统和方法将对存储器的访问指向经随机化的地址顺序。故此,即使对于访问相同的数据块而言,时间特征和功耗特征存在变化。由于对于攻击呈现鲁棒性,数据的访问是安全的。

[0055]

在此参考了特定的所示的例子对于各种示例的实施方式进行了描述。所述示例的例子被选择为辅助本领域的技术人员来形成对于各实施方式的清晰理解并得实施。然而,可以构建为包括一个或多个实施方式的系统、结构和器件的范围,以及根据一个或多个实施方式实施的方法的范围,并不为所展示的示例性例子所限制。相反地,所属技术领域的技术人员基于本说明书可以理解:可以根据各实施方式来实施出很多其他的配置、结构和方法。

[0056]

应当理解的是,就于本发明在前描述中所使用的各种位置指示来说,例如顶、底、上、下,彼等指示仅是参考了相应的附图而给出,并且当器件的朝向在制造或工作中发生变化时,可以代替地具有其他位置关系。如上所述,那些位置关系只是为清楚起见而描述,并非限制。

[0057]

本说明的前述描述是参考特定的实施方式和特定的附图,但本发明不应当限制于此,而应当由权利要求书所给出。所描述的各附图都是示例性的而非限制性的。在附图中,为示例的目的,各元件的尺寸可能被放大,且可能没有绘制为特定的比例尺。本说明也应当包括各元件、工作方式在容限和属性上的不连续的变换。还应当包括本发明的各种弱化实施。

[0058]

本说明及权利要求书中所使用的词汇“包括”并不排除其他元件或步骤。除非特别指出,在使用单数形式如“一”、“一个”指代确定或不确定的元件时,应当包括该元件的复数。从而,词汇“包括”不应当被理解为限于在其后所列出的条目,不应当理解为不包括其他元件或步骤;描述“器件包括项目a和b”的范围不应当限制为只包括元件a和b的器件。该描述表示,就于本说明而言,只有器件的元件a和b是相关的。尽管耦合通常包括电感性的连接、连接通常意为通过例如电线的连接,然而此处所述“连接”、“耦接”、“耦合”均表示在相耦接或相连接的元件之间存在电学的联系,且不意味着其间没有中间元件。在描述晶体管及其连接时,词语栅、漏、和源与栅极、漏极、源极以及栅极端、漏极端、源极端是可互换的。

[0059]

对于所属领域的技术人员而言,在不背离本发明的权利要求的范畴内可以作出多种具体变化。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。