1.本技术涉及半导体技术领域,特别涉及一种发光二极管芯片、改善其正面发光的方法及显示装置。

背景技术:

2.发光二极管(light-emitting-diode,led)是一种能将电转化为光的半导体电子元件。

3.在无finger电极设计的矩形u-led结构中,位于电极正下方的发光层部分的电流密度大(即电子或空穴的密度大),从而该部分发光强,而其余的发光层部分的电流密度会较小,从而该部分发光弱,因此导致整个u-led出光面的发光强度不均匀。

4.因而,现有技术还有待改进和提高。

技术实现要素:

5.鉴于上述现有技术的不足,本技术的目的在于提供一种发光二极管芯片,能够使得u-led整个出光面的发光强度变得均匀。

6.为实现上述目的,本技术的一个实施例提供一种发光二极管芯片,包括:衬底层,所述衬底层的表面依次设置有第一半导体层、发光层、第二半导体层及电极,其特征在于,所述衬底层上表面包括粗化区域,所述粗化区域位于所述电极在所述衬底上的投影对应的区域之外的区域。

7.可选地,所述的发光二极管芯片,其中,所述粗化区域内设置有若干无规则排列的几何图形。

8.可选地,所述的发光二极管芯片,其中,所述几何图形为圆形和/或多边形。

9.可选地,所述的发光二极管芯片,其中,任一所述几何图形的深度均小于所述衬底层厚度。

10.可选地,所述的发光二极管芯片,其中,若干所述几何图形的深度各不相等。

11.可选地,所述的发光二极管芯片,其中,所述电极包括第一电极和第二电极,所述粗化区域位于所述第一电极和所述第二电极在所述衬底上的投影对应的区域的中间对应的区域。

12.一种改善如权利要求1所述的发光二极管芯片正面发光的方法,其中,包括:

13.提供一发光二极管芯片,包括衬底层,所述衬底层的表面依次设置有第一半导体层、发光层、第二半导体层及电极;

14.在所述衬底层的上表面蚀刻出一粗化区域,所述粗化区域位于所述电极在所述衬底上的投影对应的区域之外的区域。

15.可选地,所述的改善发光二极管芯片正面发光的方法,其中,所述在所述衬底层的上表面蚀刻出一粗化区域,其中,蚀刻包括:激光蚀刻,等离子体蚀刻。

16.可选地,所述的改善发光二极管芯片正面发光的方法,其中,所述电极包括第一电

极和第二电极,所述粗化区域位于所述第一电极和所述第二电极在所述衬底上的投影对应的区域的中间对应的区域。

17.一种显示装置,其中,包括如上所述的发光二极管芯片。

18.有益效果:本技术所提供的发光二极管芯片,通过对衬底(sapphire)层特定区域进行粗化处理,粗化处理后,使原本会发生全反射的光线会因在粗化界面的入射角发生改变而被提取出到界面外,即可以使原本出不来的光线出来,从而提升了光提取效率,使发光二极管芯片的发光亮度均匀。

附图说明

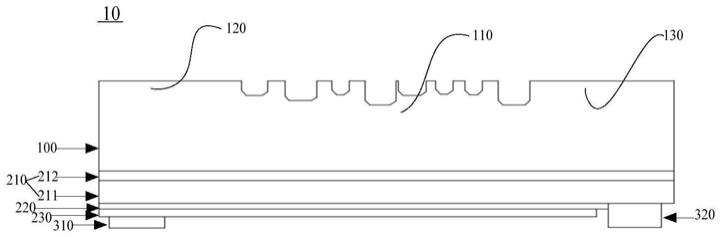

19.图1为本技术提供的发光二极管芯片剖面结构示意图。

20.图2为本技术提供的发光二极管芯片的俯视图。

21.图3为本技术提供的另一发光二极管芯片剖面结构示意图。

22.图4为现有技术中的发光二极管芯片剖面结构示意图。

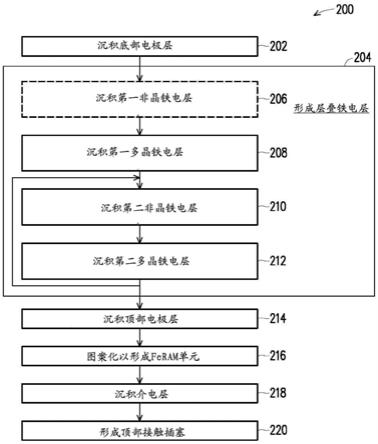

23.图5为本技术提供的一种改善发光二极管芯片正面发光的方法的流程图。

24.图6为图4所示结构的发光二极管芯片的发光强度测试结果图。

25.图7为图1所示结构的发光二极管芯片的发光强度测试结果图。

具体实施方式

26.本技术提供一种发光二极管芯片,为使本技术的目的、技术方案及效果更加清楚、明确,以下参照附图并举实施方式对本技术作进一步说明。应当理解,此处所描述的具体实施方式仅用以解释本技术,并不用于限定本技术。

27.本文中为部件所编序号本身,例如“第一”、“第二”等,仅用于区分所描述的对象,不具有任何顺序或技术含义。而本技术所说“连接”、“联接”,如无特别说明,均包括直接和间接连接(联接)。在本技术的描述中,需要理解的是,术语“上”、“下”、“前”、“后”、“左”、右”、“竖直”、“水平”、“顶”、“底”、“内”、“外”、“顺时针”、“逆时针”等指示的方位或位置关系为基于附图所示的方位或位置关系,仅是为了便于描述本技术和简化描述,而不是指示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本技术的限制。

28.在本技术中,除非另有明确的规定和限定,第一特征在第二特征“上”或“下”可以是第一和第二特征直接接触,或第一和第二特征通过中间媒介间接接触。而且,第一特征在第二特征“之上”、“上方”和“上面”可是第一特征在第二特征正上方或斜上方,或仅仅表示第一特征水平高度高于第二特征。第一特征在第二特征“之下”、“下方”和“下面”可以是第一特征在第二特征正下方或斜下方,或仅仅表示第一特征水平高度小于第二特征。

29.需要说明的是下文中,所述的粗化区域是相对于没有做粗化处理的平整的区域而言的,容易理解的,非粗化区域就是没有做粗糙化处理的区域。

30.请参考图1,本技术的一个实施例所提供的发光二极管芯片10包括,衬底层100,衬底层100的表面依次设置有第一半导体层210、发光层220、第二半导体层230、第一电极310及第二电极320。所述衬底层100上表面包括粗化区域110、第一电极在所述衬底层上的投影对应区域120及第二电极在所述衬底层上的投影对应区域130,所述粗化区域110位于所述

第一电极在所述衬底层上的投影对应区域120与第二电极在所述衬底层上的投影对应区域130之间。其中,第一半导体层为n型半导体层210,包括n-gan(n型氮化镓)211,u-gan(无掺杂氮化镓)212。衬底层100为蓝宝石衬底,发光层220为mqw(多量子阱),第二半导体层为p型半导体层230(p型氮化镓)。

31.在本实施例中,所述n型半导体层210设置在衬底层100的表面,所述n型半导体层211包括第一侧面及第二侧面。在第一侧面上形成有一台面,该台面的深度小于n型半导体层211的厚度。第二电极为n电极320设置在台面上。在所述n型半导体层211的第二侧面上设置有发光层220。所述p型半导体层230设置在发光层220表面上,第一电极为p电极310设置在p型半导体层230的表面上。

32.在本实施例中,所述粗化区域110是指通过激光、等离子体等方式在led芯片的蓝宝石衬底层出光侧的特定区域(发光亮度不均匀的区域)内蚀刻形成的表面粗化区域。粗化处理后,使原本会发生全反射的光线会因在粗化界面的入射角发生改变而被提取出到界面外,即可以使原本出不来的光线出来,从而提升了光提取效率。

33.需要说明的是,各层的生长方式及将所述衬底层表面蚀刻形成表面粗化区域均为本领域常用技术,具体操作步骤在此不做赘述。

34.在本实施例的一种实施方式中,如图2所示,在所述粗化区域110内无规则的排列着若干几何图形111,所述几何图形111的形状可以是三角形、圆形、多边形、无规则形状中的一个或多个。当所述几何图形为圆形和/或多边形时,一方面可以方便进行蚀刻操作,另一方面也容易将光提取出来(原本因全反射无法发射出来的那部分光)。

35.在本实施例的一种实施方式中,如图3所示,粗化区域110中的几何图形111具有一定的深度,容易理解的,所述几何图形的深度要小于所述衬底层100的厚度。可选地,所述几何图形的深度为所述衬底层100厚度的1/10至1/5,例如所述衬底层100的厚度为500nm,所述几何图形的深度可以是50nm至60nm,60nm至70nm,70nm至80nm,80nm至90nm,90nm至100nm等等。

36.在本实施例的一种实施方式中,粗化区域内的几何图形的深度可以是随机的,比如说一些几何图形的深度可以是5nm至10nm范围内的,而另外一部分几何图形的深度可以是20nm至45nm等等。容易理解的,这些几何图形的深度均是在小于衬底厚的前提下进行讨论的。

37.进一步地,处于同一个深度范围内(如20nm至45nm),一部分几何图形的深度可以相同的如都为25nm,而另一部分几何图形的深度为30nm。通过将几何图形的深度设置为非均匀的,可以将在衬底层内部更多的发生全反射的光取出,提升发光效率和出光的均匀性。

38.在本实施例的一个实施方式中,还可以将几何图形的深度沿粗化区域的从中部位向外延伸的方向上逐级递减的方式进行排列。作为举例,位于粗化区域110中部的几何图形为圆形,其深度为80nm,则以该圆形为中心从内向外几何图形的深度设置为75nm、70nm、65nm、60nm、55nm等等。容易理解的,几何图形的深度从内到外也可以是其他的排列方式。

39.在本实施例一个实施方式中,所述几何图形的宽度要小于所述衬底层的宽度。位于粗化区域内的几何图形的宽度可以相同,也可以不同。比如说,其中一个圆形的直径为20nm,那么其他圆形的直径可以是20nm,也可是5nm、8nm、11nm、40nm、45等等。

40.在本实施一个实施方式中,往往一个几何图形的宽度越宽,则相应的其深度也会

是几何图形中深度较深的。

41.在本实施例一个实施方式中,所述粗化区域110所占整个衬底层100的比例大于所述第一电极在所述衬底层上的投影对应区域120和所述第二电极在所述衬底层上的投影对应区域130所占比例。换句话说,所述第一电极在所述衬底层上的投影对应区域120的面积和所述第二电极在所述衬底层上的投影对应区域130的面积均小于所述粗化区域110的面积。由于发光二极管芯片电极区域相对较小,意味着高电流区域的面积占比小。因此将位于低电流区域内衬底层做粗化处理,有利于时原本在内部发生全反射的那部分光线发射出来,提升整个发光二极管芯片出光面的出光均匀性。需要说明的是,通常粗化区域与所述非粗化区域的分界,是以粗化区域最外边的一个几何图形(临近所述非粗化区域)的外边缘为界。

42.在本实施例的一个实施方式中,可以将各区域的面积设置为所述粗化区域的面积等于所述第一电极在所述衬底层上的投影对应区域的面积与所述第二电极在所述衬底层上的投影对应区域面积的和。其中,所述第一电极在所述衬底层上的投影对应区域的面积等于所述第二电极在所述衬底层上的投影对应区域的面积,容易理解的,所述粗化区域的面积占所述衬底层上表面的整个面积的1/2。

43.基于上述发光二极管芯片,本技术还提供一种改善发光二极管芯片正面发光的方法,如图5所示,所述方法包括步骤:

44.s10、提供一发光二极管芯片,包括衬底层,所述衬底层的表面依次设置有第一半导体层、发光层、第二半导体层及电极;

45.s20、在所述衬底层的上表面蚀刻出一粗化区域,所述粗化区域位于所述电极在所述衬底上的投影对应的区域之外的区域。

46.具体来说,先提供一个发光二极管芯片,该发光二极管芯片的结构如图4所示,采用激光蚀刻工艺对所述衬底层100的中间区域进行蚀刻,在蚀刻区域内形成表面粗化的区域,所述粗化区域内的图形(top view)可以是任何图形,如可以是圆形,多边形等。

47.基于上述发光二极管芯片,本技术还提供一种显示装置,所述显示装置包括了如上所述发光二极管芯片(即显示装置中的发光二极管芯片的衬底层的出光面上设置有粗化区域),使得所述显示装置的出光更加均匀。

48.下面通过一个具体的实施例,对本技术所提供的发光二极管芯片做进一步的解释说明。

49.选择一个现有技术中的一个发光二极管芯片,如图4所示,采用激光蚀刻的方式,在衬底层的表面的中间区域形成表面粗化,粗化的区域大约占衬底层整个上表面的1/2,衬底层的厚度为600nm,几何图形为椭圆形,椭圆形的深度范围是5-100nm,椭圆形的长轴长度范围为10-50nm。测定该发光二极管芯片的发光亮度结果如图7所示,图6为现有技术(表面未做粗化处理的)发光二极管芯片的发光亮度测试结果。

50.经过对比可以看出,本技术所提供的发光二极管芯片出光面发光强度更均匀。

51.综上所述,本技术所提供的一种发光二极管芯片、改善其正面发光的方法及显示装置,通过对衬底(sapphire)层特定区域进行粗化处理,粗化处理后,使原本会发生全反射的光线会因在粗化界面的入射角发生改变而被提取出到界面外,即可以使原本出不来的光线出来,从而提升了光提取效率,使发光二极管芯片的发光亮度均匀。

52.应当理解的是,本技术的应用不限于上述的举例,对本领域普通技术人员来说,可以根据上述说明加以改进或变换,所有这些改进和变换都应属于本本技术所附权利要求的保护范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。