1.本发明为一种串叠连接的电力电子器件的封装方法及其封装结构,尤指一种以异质多晶的晶圆级封装的串叠连接的电力电子器件的封装方法及其封装结构。

背景技术:

2.安森美半导体(onsemiconductor)看好氮化镓(gan)可为电源应用且提供优于硅基组件的性能优势,因而开发并推广基于氮化镓的产品及电源系统方案,并推出600v gan级联结构(cascode)晶体管ntp8g202n及ntp8g206n,瞄准工业、计算机、通讯、led照明及网络领域的各种高压应用。ntp8g202n及ntp8g206n两款组件的导通电阻分别为290mω及150mω,闸极电荷均为6.2nc,输出电容分别为36pf及56pf,反向恢复电荷分别为0.029μc及0.054μc,采用优化的to-220封装,易于根据客户现有的制板能力而整合。

3.基于同一导通电阻等级,第一代600v硅基gan(gan-on-si)组件已比高压硅mosfet提供优质4倍以上的闸极电荷、更好的输出电荷、差不多的输出电容及优质20倍以上的反向恢复电荷,并将有待继续改进,未来gan的优势会越来越明显。

技术实现要素:

4.本发明的目的在于提供一种串叠连接的电力电子器件的封装方法及其封装结构,藉此可降低连接导线的电感、电阻及热阻,缩小封装体的尺寸,提升电力密度及切换频率。

5.为达上述目的,本发明所采用的技术方案是:一种串叠连接的电力电子器件的封装方法,该方法包括如下步骤:取一基板,于其上设置一感压胶层;于该感压胶层上设置一个以上的氮化镓半导体晶粒、一个以上的二极管及一个以上的金属氧化物半导体晶体管;于该感压胶层上涂覆第一光显影层,该第一光显影层覆盖该氮化镓半导体晶粒、该二极管及该金属氧化物半导体晶体管;对该氮化镓半导体晶粒、该二极管及该金属氧化物半导体晶体管上的第一光显影层的第一面进行曝光显影,并对曝光显影区进行镀铜,形成镀铜层;于第一光显影层上设置一第一塑料层,该第一塑料层覆盖第一光显影层上的未曝光显影区及镀铜层,再于该第一塑料层上设置一散热板;剥离该基板及该感压胶层;于第一光显影层的第二面上涂覆一第二光显影层,该第二光显影层覆盖该氮化镓半导体晶粒、该二极管及该金属氧化物半导体晶体管;对第二光显影层进行曝光显影,以显露出该氮化镓半导体晶粒的闸极与汲极、该金属氧化物半导体晶体管的闸极与源极及该二极管;将该氮化镓半导体晶粒的闸极与汲极、该金属氧化物半导体晶体管的闸极与源极及该二极管形成一重分布层(rdl, redistribution layer);

将该重分布层镀上一保护层;将胶带黏贴于该陶瓷散热板上,切割该氮化镓半导体晶粒、该二极管、该金属氧化物半导体晶体管、该第一塑料层及该陶瓷散热板,以形成数个封装模块,并使得该些封装模块仅通过该胶带而彼此连接,拉伸该胶带,使得该些封装模块之间的间隙增加,并移除胶带,得到数个封装模块,将该些封装模块串叠连接以形成该电力电子器件。

6.于前述本发明的串叠连接的电力电子器件的封装方法中, 该氮化镓半导体晶粒为横向导通垂直结构或水平结构,且具有一正面及与该正面相对的一背面,藉由一导通孔将该氮化镓半导体晶粒的源极连通到该背面。

7.于前述本发明的串叠连接的电力电子器件的封装方法中,藉由一金氧半导体制程将该金属氧化物半导体晶体管与该二极管连接在一起。

8.于前述本发明的串叠连接的电力电子器件的封装方法中,在形成该镀铜层之后并在剥离该基板及该感压胶层之前,将该第一光显影层分隔出复数间隔槽,在该些间隔槽上设置一第二塑料层,并在该第二塑料层上设置一档板。

9.本发明同时提供藉由前述方法制得的串叠连接的电力电子器件的封装结构,包括复数数组串叠连接的封装模块,每一封装模块包括:氮化镓半导体晶粒、二极管、金属氧化物半导体晶体管、第一感光显影基材、镀铜层、第一塑料层、散热板、第二感光显影基材、重分布层以及保护层;其中,氮化镓半导体晶粒为横向导通垂直结构或水平结构,该二极管及金属氧化物半导体晶体管连接在一起,该该氮化镓半导体晶粒与该二极管及金属氧化物半导体晶体管之间具有一设定距离,该第一感光显影基材覆盖于氮化镓半导体晶粒、二极管及金属氧化物半导体晶体管上,并通过曝光显影显露有第一开口,该镀铜层设置于该第一开口处而将氮化镓半导体晶粒与该二极管及金属氧化物半导体晶体管连接,该第一塑料层设置于镀铜层及第一感光显影基材的第一表面上。此外,散热板设置于第一塑料层上;该第二感光显影基材覆盖于第一感光显影基材的第二表面上,并通过曝光显影显露有第二开口,该重分布层设置于第二开口处,而该保护层环绕重分布层而设置。

10.于前述本发明的串叠连接的电力电子器件的封装结构中,该散热板为陶瓷散热板或金属板。

11.于前述本发明的串叠连接的电力电子器件的封装结构中,该保护层为镍金属层、铜金属层或镍铜合金层。

12.其次,本发明还提供一种串叠连接的电力电子器件的封装方法,该方法包括如下步骤:取一基板,于其上设置一感压胶层;于该感压胶层上设置一个以上的氮化镓半导体晶粒、一个以上的二极管、一个以上的金属氧化物半导体晶体管及一个以上的金属块;于该感压胶层上涂覆第一光显影层,该第一光显影层覆盖该氮化镓半导体晶粒、该二极管、该金属氧化物半导体晶体管及该金属块;对该氮化镓半导体晶粒、该金属氧化物半导体晶体管、该二极管及该金属块上的第一光显影层的第一面进行曝光显影,并对曝光显影区进行镀铜,形成镀铜层;于第一光显影层设置一第一塑料层,该第一塑料层覆盖第一光显影层上的未曝光显影区及镀铜层,再于该第一塑料层上设置一陶瓷散热板;

剥离该基板及该感压胶层;于第一光显影层的第二面上涂覆一第二光显影层,该第二光显影层覆盖该氮化镓半导体晶粒、该二极管、该金属氧化物半导体晶体管及该金属块;对第二光显影层进行曝光显影,以显露出该氮化镓半导体晶粒的汲极、该金属氧化物半导体晶体管的闸极与源极、该二极管及该金属块;并将显露区镀上金属,形成一金属层;将该金属层镀上一保护层;将胶带黏贴于该陶瓷散热板上,切割该氮化镓半导体晶粒、该二极管、该金属氧化物半导体晶体管、该金属块、该第一塑料层及该陶瓷散热板,以形成数个封装模块,并使得该些封装模块仅通过该胶带而彼此连接,拉伸该胶带,使得该些封装模块之间的间隙增加,并移除胶带,得到数个封装模块,将该些封装模块串叠连接而形成该电力电子器件。

13.于前述本发明之串迭连接的电力电子器件封装方法中,该氮化镓半导体晶粒为横向导通垂直结构或水平结构,且具有一正面及与该正面相对的一背面,藉由一导通孔将该氮化镓半导体晶粒的汲极连通到该背面。

14.于前述本发明的串叠连接的电力电子器件封装方法中,藉由一金氧半导体制程将该金属氧化物半导体晶体管与该二极管连接在一起。本发明还提供前述方法制得的串叠连接的电力电子器件的封装结构,包括复数数组串叠连接的封装模块,每一封装模块包括:氮化镓半导体晶粒、二极管、金属氧化物半导体晶体管、金属块、第一感光显影基材、镀铜层、第一塑料层、散热板、第二感光显影基材、重分布层及保护层;其中,该氮化镓半导体晶粒为横向导通垂直结构或水平结构,且二极管与该金属氧化物半导体晶体管连接在一起,该氮化镓半导体晶粒与二极管和金属氧化物半导体晶体管之间以及氮化镓半导体晶粒与金属块之间皆具有一设定距离,该第一感光显影基材覆盖于氮化镓半导体晶粒、二极管、金属氧化物半导体晶体管及金属块上,且该第一感光显影基材上通过曝光显影显露有第一开口,该镀铜层设置于第一开口处以连接氮化镓半导体晶粒与金属块以及氮化镓半导体晶粒与二极管和该金属氧化物半导体晶体管,该第一塑料层设置于该镀铜层及该第一感光显影基材的该第一表面上,散热板则设置于第一塑料层上,第二感光显影基材覆盖于第一感光显影基材的该第二表面上,且该第二感光显影基材通过曝光显影显露有第二开口,该重分布层设置于该些第二开口上处,该保护层环绕该些重分布层而设置。

15.根据上述诸多优点,并为对本发明能进一步地了解,故揭露较佳的实施方式如下,配合图式、图号,将本发明的构成内容及其所达成的功效详细说明如后。

附图说明

16.图1a至图1j为本发明实施例1电力电子器件的封装步骤结构图;图2a为本发明实施例1的氮化镓半导体晶粒的俯视示意图;图2b为本发明实施例1的氮化镓半导体晶粒的侧面示意图;图3a为本发明实施例1的金属氧化物半导体晶体管及二极管的立体示意图;图3b为本发明实施例1的金属氧化物半导体晶体管及二极管的侧面示意图;图4为本发明实施例1电力电子器件的结构示意图;图5a为本发明实施例2的金属氧化物半导体晶体管及二极管的立体示意图;图5b为本发明实施例2的金属氧化物半导体晶体管及二极管的侧面示意图;

图6为本发明实施例2电力电子器件的结构示意图;图7a至图7j为本发明实施例3电力电子器件的封装步骤结构图;图8a为本发明实施例3中氮化镓半导体晶粒的俯视图;图8b为本发明实施例3中氮化镓半导体晶粒的侧面示意图;图9为本发明实施例3电力电子器件的结构示意图;图10为本发明实施例4电力电子器件的结构示意图;图11a为本发明实施例5的金属氧化物半导体晶体管及二极管的侧面示意图;图11b为本发明实施例5之金属氧化物半导体晶体管及二极管之俯视示意图;图11c为本发明实施例5之氮化镓半导体晶粒、金属氧化物半导体晶体管及二极管之俯视示意图;图12为本发明实施例6之氮化镓半导体晶粒、金属氧化物半导体晶体管及二极管之俯视示意图;图13a至图13l为本发明实施例7电力电子器件的封装步骤结构图;图14为本发明实施例8电力电子器件的结构示意图。

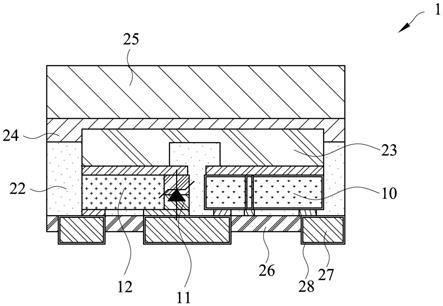

17.标号说明:1电力电子器件

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ1’ꢀ

封装模块10氮化镓半导体晶粒

ꢀꢀꢀꢀꢀ

101闸极102汲极

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

103源极11二极管

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

12金属氧化物半导体晶体管121闸极

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

122汲极123源极

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

20基板21感压胶层

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

22第一感光显影基材221第一表面

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

222第二表面223第一开口

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

224间隔槽23镀铜层

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

225第二塑料层226档板

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

24第一塑料层25散热板

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

26第二感光显影基材261第二开口

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

27重分布层27

’ꢀ

金属层

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

28保护层29胶带。

具体实施方式

18.以下藉由具体实施例说明本发明的实施方式,本领域普通技术人员可由本说明书所揭示的内容轻易地了解本发明的其他优点与功效。此外,本发明亦可藉由其他不同具体实施例加以施行或应用,在不悖离本发明的精神下进行各种修饰与变更。

19.请参阅图1a至图1j,图1a至图1j为本发明实施例1电力电子器件的封装步骤结构图。

20.如图1a至图1j所示,本发明提供一种串叠连接的电力电子器件的封装方法,该方法包括如下步骤:

取一基板20,于其上设置一感压胶层21,于该感压胶层21上设置一个以上的横向导通垂直结构的氮化镓半导体晶粒10、一个以上的二极管11及一个以上的金属氧化物半导体晶体管12,如图1a所示;于该感压胶层21上涂覆第一光显影层22,该第一光显影层22覆盖该些横向导通垂直结构的氮化镓半导体晶粒10、该二极管11及该金属氧化物半导体晶体管12,如图1b所示;对该横向导通垂直结构的氮化镓半导体晶粒10、该二极管11及该金属氧化物半导体晶体管12上的第一光显影层22的一第一面221进行曝光显影(见图1c),并对曝光显影区进行镀铜,形成一镀铜层23,如图1d所示;于第一光显影层22上设置一第一塑料层24,该第一塑料层24覆盖第一光显影层22上的未曝光显影区及镀铜层23,再于该第一塑料层24上设置一散热板25,其中,该散热板25为陶瓷散热板或金属板,如图1e所示;剥离该基板20及该感压胶层21,如图1f所示;于第一光显影层22的一第二面222上涂覆一第二光显影层26,该第二光显影层26覆盖该横向导通垂直结构的氮化镓半导体晶粒10、该二极管11及该金属氧化物半导体晶体管12;对第二光显影层26进行曝光显影,以显露出该横向导通垂直结构的氮化镓半导体晶粒10的闸极101与汲极102、该金属氧化物半导体晶体管12的闸极121与源极123及该二极管11,如图1g所示;将该横向导通垂直结构的氮化镓半导体晶粒10的闸极101与汲极102、该金属氧化物半导体晶体管12的闸极121与源极123及该二极管11形成一重分布层27(rdl, redistribution layer),如图1h所示;将该重分布层27镀上一保护层28,其中,该保护层28为镍金属层、铜金属层或镍铜合金层,如图1i所示;将胶带29黏贴于该陶瓷散热板25上,切割该横向导通垂直结构的氮化镓半导体晶粒10、该金属氧化物半导体晶体管12、该二极管11、该第一塑料层24及该陶瓷散热板25,以形成数个封装模块1’,并使得该些封装模块1’仅通过该胶带29而彼此连接,拉伸该胶带29,使得该些封装模块1’之间的间隙增加,并移除胶带29以得到数个封装模块1’,将该些封装模块1’进行串叠连接而形成电力电子器件(结合参见图4),如图1j所示。

21.请参阅图2a至图3b,图2a为本发明实施例1的氮化镓半导体晶粒的俯视示意图;图2b为本发明实施例1的氮化镓半导体晶粒的侧面示意图;图3a为本发明实施例1的金属氧化物半导体晶体管及二极管的立体示意图;图3b为本发明实施例1的金属氧化物半导体晶体管及二极管的侧面示意图。

22.如图2a至图2b所示,本发明实施例1的横向导通垂直结构的该氮化镓半导体晶粒10具有闸极101、汲极102、源极103及一导通孔104,且该横向导通垂直结构的氮化镓半导体晶粒10具有一正面105及与该正面105相对的一背面106,藉由该导通孔104将该横向导通垂直结构的氮化镓半导体晶粒10的源极103连通到该背面106。如图3a至图3b所示,藉由一金氧半导体制程将该二极管11与该金属氧化物半导体晶体管12连接在一起,形成闸极101’、汲极102’及源极103’。

23.请参阅图4,图4为本发明实施例1电力电子器件的结构示意图。

24.如图4所示,本发明提供一种串叠连接的电力电子器件的封装结构,包括复数数组

串叠连接的封装模块1’,每一封装模块1’包括:横向导通垂直结构的氮化镓半导体晶粒10、二极管11、金属氧化物半导体晶体管12、第一感光显影基材22、镀铜层23、第一塑料层24、散热板25、第二感光显影基材26、重分布层27以及保护层28;其中,该二极管11及金属氧化物半导体晶体管12连接在一起,该横向导通垂直结构的该氮化镓半导体晶粒10与该二极管11及金属氧化物半导体晶体管12之间具有一设定距离,。该第一感光显影基材22覆盖于横向导通垂直结构的氮化镓半导体晶粒10、二极管11及金属氧化物半导体晶体管12上,并通过曝光显影显露有第一开口223(结合参见图1c),该镀铜层23设置于该第一开口223处而将氮化镓半导体晶粒10与该二极管11及金属氧化物半导体晶体管12连接,该第一塑料层24设置于镀铜层23及第一感光显影基材22的第一表面221上。此外,散热板25设置于第一塑料层24上;该第二感光显影基材26覆盖于第一感光显影基材22的第二表面222上,并通过曝光显影显露有第二开口261(结合参见如图1g)。该重分布层27设置于第二开口261处,而该保护层28环绕重分布层27而设置。

25.请参阅图5a至图6,图5a为本发明实施例2的金属氧化物半导体晶体管及二极管的立体示意图;图5b为本发明实施例2的金属氧化物半导体晶体管及二极管的侧面示意图;以及图6为本发明实施例2电力电子器件的结构示意图。

26.如图5a至图5b所示,在实施例2中,不同于实施例1藉由一金氧半导体制程将该二极管11与该金属氧化物半导体晶体管12连接在一起,在该实施例2中,该二极管11与该金属氧化物半导体晶体管12为彼此分离。如图6所示,该二极管11与该金属氧化物半导体晶体管12为彼此分离,并藉由该金属层23将横向导通垂直结构的该氮化镓半导体晶粒10、该二极管11及该金属氧化物半导体晶体管12彼此连接在一起。

27.参阅图7a至图7j,图7a至图7j为本发明实施例3电力电子器件的封装步骤结构图。

28.如图7a至图7j所示,本发明另提供一种串叠连接的电力电子器件的封装方法,该方法包括如下步骤:取一基板20,于其上设置一感压胶层21;于该感压胶层21上设置一个以上的横向导通垂直结构的氮化镓半导体晶粒10、一个以上的二极管11、一个以上的金属氧化物半导体晶体管12及一个以上的金属块13,如图7a所示;于该感压胶层21上涂覆第一光显影层22,该第一光显影层22覆盖该横向导通垂直结构的氮化镓半导体晶粒10、该二极11体、该金属氧化物半导体电晶12体及该金属块13,如图7b所示;对该横向导通垂直结构的氮化镓半导体晶粒10、该二极管11、该金属氧化物半导体晶体管12及该金属块13上的第一光显影层22的第一面221进行曝光显影(见图7c),并对曝光显影区进行镀铜,形成一镀铜层23,如图7d所示;于第一光显影层22设置一第一塑料层24,该第一塑料层24覆盖第一光显影层22上的未曝光显影区及镀铜层23,再于该第一塑料层24上设置一陶瓷散热板25,如图7e所示;剥离该基板20及该感压胶层21,如图7f所示;于第一光显影层22的第二面222上涂覆一第二光显影层26,该第二光显影层26覆盖该横向导通垂直结构的氮化镓半导体晶粒10、该二极管11、该金属氧化物半导体晶体管12及该金属块13;对第二光显影层26进行第二次曝光显影,以显露出该横向导通垂直结构的氮

化镓半导体晶粒10的汲极102、该金属氧化物半导体晶体管12的闸极121与源极123、该二极管11及该金属块13,如图7g所示;将该横向导通垂直结构的氮化镓半导体晶粒10的汲极102与该金属氧化物半导体晶体管12的闸极121与源极123、该二极管11及该金属块13镀上金属,形成一金属层27’,如图7h所示;将该金属层27’镀上一保护层28,如图7i所示;如图7j所示,将胶带29黏贴于该陶瓷散热板25上,切割该横向导通垂直结构的氮化镓半导体晶粒10、该二极管11、该金属氧化物半导体晶体管12、该金属块13、该第一塑料层24及该陶瓷散热板25,以形成数个封装模块1’,并使得该些封装模块1’仅通过该胶带29而彼此连接,拉伸该胶带29,使得该些封装模块1’之间的间隙增加,并移除胶带29得到数个封装模块1’,将该些封装模块1’串叠连接形成该电力电子器件(见图9)。

29.请参阅图8a至图9,图8a为本发明实施例3中氮化镓半导体晶粒之俯视图;图8b为本发明实施例3中氮化镓半导体晶粒之侧面示意图;图9为本发明实施例3电力电子器件的结构示意图。

30.如图8a至图8b所示,在本发明的实施例3中,除了该横向导通垂直结构的氮化镓半导体晶粒10的结构不同之外,其余结构皆与实施例1相同。该横向导通垂直结构的氮化镓半导体晶粒10具有一正面105及与该正面105相对的一背面106,藉由一导通孔104将该横向导通垂直结构的氮化镓半导体晶粒10的汲极102连通到该背面106。

31.如图9所示,在本发明的实施例3中,串叠连接的电力电子器件1的封装结构,包括复数数组串叠连接的封装模块1’,每一封装模块1’包括:横向导通垂直结构的氮化镓半导体晶粒10、二极管11、金属氧化物半导体晶体管12、金属块13、第一感光显影基材22、镀铜层23、第一塑料层24、散热板25、第二感光显影基材26、重分布层27及保护层28;其中,该二极管11与该金属氧化物半导体晶体管12连接在一起,该横向导通垂直结构的氮化镓半导体晶粒10与二极管11和金属氧化物半导体晶体管12之间以及氮化镓半导体晶粒10与金属块13之间皆具有一设定距离。该第一感光显影基材22覆盖于横向导通垂直结构的氮化镓半导体晶粒10、二极管11、金属氧化物半导体晶体管12及金属块13上,且该第一感光显影基材22上通过曝光显影显露有第一开口223(结合参见图7c),该镀铜层23设置于第一开口223处以连接氮化镓半导体晶粒10与金属块13以及氮化镓半导体晶粒10与二极管11和该金属氧化物半导体晶体管12,该第一塑料层24设置于该镀铜层23及该第一感光显影基材22的该第一表面221上,散热板25则设置于第一塑料层24上,第二感光显影基材26覆盖于第一感光显影基材22的该第二表面222上,且该第二感光显影基材26通过曝光显影显露有第二开口261(结合参见图7g)。此外,该重分布层27设置于该些第二开口上261处,保护层28环绕该些重分布层27而设置。

32.请参阅图10,图10为本发明实施例4电力电子器件的结构示意图。

33.如图10所示,不同于实施例3藉由一金氧半导体制程将该金属氧化物半导体晶体管12与该二极管11连接在一起,在实施例4中,二极管11与金属氧化物半导体晶体管12为彼此分离。如图10所示,该二极管11与该金属氧化物半导体晶体管12为彼此分离,并藉由该金属层23将横向导通垂直结构的该氮化镓半导体晶粒10、该二极管11、该金属氧化物半导体晶体管12及该金块13彼此连接在一起。

34.请参阅图11a至图11c,图11a为本发明实施例5的金属氧化物半导体晶体管及二极管的侧面示意图;图11b为本发明实施例5的金属氧化物半导体晶体管及二极管的俯视示意图;以及图11c为本发明实施例5的氮化镓半导体晶粒、金属氧化物半导体晶体管及二极管的俯视示意图。

35.如图11a至图11c所示,实施例5除了包括了2个横向导通垂直结构的氮化镓半导体晶粒10、2个二极管11及2个金属氧化物半导体晶体管12之外,其余皆与实施例1相同。实施例5中,该二极管11及该金属氧化物半导体晶体管12具有第一闸极g1及第二闸极g2、第一汲极d1及第二汲极d2与第一源极s1及第二源极s2。由11c图可知,2个横向导通垂直结构的氮化镓半导体晶粒10与该2个二极管11及2个金属氧化物半导体晶体管12平行设置,因此在11a图中看不到2个横向导通垂直结构的氮化镓半导体晶粒10。

36.请参阅图12,图12为本发明实施例6的氮化镓半导体晶粒、金属氧化物半导体晶体管及二极管的俯视示意图。

37.如图12所示,实施例6除了包括了4个横向导通垂直结构的氮化镓半导体晶粒10、4个二极管11及4个金属氧化物半导体晶体管12之外,其余皆与实施例1相同。

38.请参阅图13a至图13l,图13a至图13l为本发明实施例7电力电子器件的封装步骤结构图。

39.如图13a至图13l所示,本发明提供另一串叠连接的电力电子器件的封装方法,该方法包括如下步骤:取一基板20,于其上设置一感压胶层21;于该感压胶层21上设置一个以上的横向导通垂直结构的氮化镓半导体晶粒10、一个以上的二极管11及一个以上的金属氧化物半导体晶体管12,如图13a所示;于该感压胶层21上涂覆第一光显影层22,该第一光显影层22覆盖该横向导通垂直结构的氮化镓半导体晶粒10、该二极管11及该金属氧化物半导体晶体管12,如图13b所示;对该横向导通垂直结构的氮化镓半导体晶粒10、该二极管11及该金属氧化物半导体晶体管12上的第一光显影层22的第一面221进行曝光显影(见图13c),并对曝光显影区进行镀铜,形成镀铜层23,如图13d所示;将该第一光显影层22分隔出复数间隔槽224,如图13e所示;在该些间隔槽224上设置一第二塑料层225,并在该第二塑料层225上设置一档板226,如图13f所示;剥离该基板20及该感压胶层21,如图13g所示;于第一光显影层22的第二面222上涂覆一第二光显影层26,该第二光显影层26覆盖该横向导通垂直结构的氮化镓半导体晶粒10、该二极管11及该金属氧化物半导体晶体管12,如图13h所示;对第二光显影层26的进行曝光显影,以显露出该横向导通垂直结构的氮化镓半导体晶粒10的闸极101与汲极102、该金属氧化物半导体晶体管12的闸极121及该二极管11,如图13i所示;将该横向导通垂直结构的氮化镓半导体晶粒10的闸极101与汲极102、该金属氧化物半导体晶体管12的闸极121及该二极管11形成一重分布层27,如图13j所示;将该重分布层27镀上一保护层28,如图13k所示;

将胶带29黏贴于该档板226上,切割该横向导通垂直结构的氮化镓半导体晶粒10、该二极管11、该金属氧化物半导体晶体管12及该第二塑料层225,以形成数个封装模块1’,并使得该些封装模块1’仅通过该胶带29而彼此连接,拉伸该胶带29,使得该些封装模块1’之间的间隙增加,并移除胶带29而得到数个封装模块1’(见图13l),将该些封装模块1’串叠连接而形成电力电子器件1。

40.请参阅图14,图14为本发明实施例8电力电子器件的结构示意图。

41.如图14所示,实施例8电力电子器件1的封装结构包括复数串叠连接的封装模块1’,每一封装模块1’包括:一水平结构的氮化镓半导体晶粒10’、二极管11、金属氧化物半导体晶体管12、第一感光显影基材22、镀铜层23、第二感光显影基材26、重分布层27、保护层28以及一分隔物30;其中,该二极管11及金属氧化物半导体晶体管12连接在一起,该水平结构的氮化镓半导体晶粒10’与金属氧化物半导体晶体管12藉由一焊锡膏105设置于一引线框架201上,且该分隔物30设置于该水平结构的氮化镓半导体晶粒10’及金属氧化物半导体晶体管12的两侧。该第一感光显影基材22覆盖于水平结构的氮化镓半导体晶粒10’、二极管11、金属氧化物半导体晶体管12及该分隔物30上,并通过曝光显影显露有第一开口223。该镀铜层23设置于该第一开口223处而将水平结构的氮化镓半导体晶粒10’与金属氧化物半导体晶体管12及该分隔物30连接。该第二感光显影基材26覆盖于该第一感光显影基材22及该镀铜层23上,并通过曝光显影显露有第二开口261。该重分布层27设置于第二开口261上,以及保护层28环绕重分布层27而设置。

42.上述实施例仅是为了方便说明而举例而已,本发明所主张之权利范围自应以申请专利范围所述为准,而非仅限于上述实施例。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。