1.本公开总体上涉及电子系统,并且在特定实施例中涉及电压转换器。

背景技术:

2.在开关式转换器中,转换器的电源电压通过切换开关来进行斩波,以在电感元件中实现能量累积阶段并且实现该电感元件中所累积的能量的恢复阶段,从而恢复在转换器的输出处连接的电荷。

3.在pfm(脉冲频率调制)类型的开关式转换器中,转换器的每个操作周期包括在电感元件中的能量积累阶段,随后是连接到转换器的电荷的能量恢复阶段。在能量积累阶段期间,流过电感元件的电流增加。在能量恢复阶段期间,流过电感元件的电流减小。对于每个操作周期,期望在能量累积阶段的开始和能量恢复阶段的结束时流过电感元件的电流为零。

4.已知的开关式转换器,特别是pfm类型的开关式转换器,具有各种缺点。

技术实现要素:

5.为了至少部分地解决已知的开关式转换器中的各种缺点,本公开提出了一种电压转换器和电子电路。

6.在第一方面,提供了一种电压转换器,该电压转换器包括:第一晶体管,被耦合在第一节点和电压转换器的内部节点之间,第一节点被配置为接收电源电压;第二晶体管,被耦合在内部节点和第二节点之间,第二节点被配置为接收基准电压;电感,被耦合在电压转换器的输出节点和内部节点之间;第一电路,被配置为控制第一晶体管和第二晶体管;以及第二电路,被配置为当第一晶体管和第二晶体管关断时检测内部节点的内部节点电压何时等于输出节点的输出电压,其中第一电路被配置为在第二电路检测到内部节点电压等于输出电压时,将第一晶体管导通。

7.根据一个实施例,第二电路被配置为提供第一信号,其中第一信号被配置为:当第一晶体管和第二晶体管关断并且内部节点电压大于电源电压或小于基准电压时,从第一信号的第一状态切换到第一信号的第二状态;以及当第一晶体管和第二晶体管关断并且内部节点电压等于输出电压时,从第一信号的第二状态切换到第一信号的第一状态。

8.根据一个实施例,第一电路被配置为基于第一信号来导通第一晶体管。

9.根据一个实施例,第二电路包括第三晶体管和第四晶体管,第三晶体管和第四晶体管串联耦合在第一节点和第二节点之间,第二电路被配置为使得内部节点电压确定第三晶体管和第四晶体管中的每个晶体管的关断或导通状态。

10.根据一个实施例,第二电路还被配置为使得当内部节点电压等于输出电压时,第三晶体管和第四晶体管处于相同的导通或关断状态。

11.根据一个实施例,第三晶体管和第四晶体管是金属氧化物半导体晶体管,并且其中第一信号基于第三晶体管和第四晶体管的漏极电压来确定。

12.根据一个实施例,第二电路包括组合电路,组合电路具有:与第三晶体管的第一电流路径端子耦合的第一输入、与第四晶体管的第一电流路径端子耦合的第二输入以及被配置为提供第一信号的输出。

13.根据一个实施例,组合电路包括and门,and门具有:与第三晶体管的第一电流路径端子耦合的第一输入、经由反相器闸而与第四晶体管的第一电流路径端子耦合的第二输入以及与组合电路的输出耦合的输出。

14.根据一个实施例,第三晶体管和第四晶体管是金属氧化物半导体晶体管,并且其中第三晶体管和第四晶体管的源极端子被配置为接收内部节点电压。

15.根据一个实施例,第三晶体管和第四晶体管的栅极端子被配置为接收输出电压,其中第三晶体管的漏极端子被耦合至第一节点,并且其中第四晶体管的漏极被耦合到第二节点。

16.根据一个实施例,第一晶体管和第四晶体管是p型晶体管,并且其中第二晶体管和第三晶体管是n型晶体管。

17.根据一个实施例,第三晶体管和第四晶体管的控制端子被配置为接收内部节点电压。

18.根据一个实施例,第三晶体管的第一电流路径端子被耦合至第一节点,第四晶体管的第一电流路径端子被耦合至第二节点,并且第三晶体管的第二电流路径端子经由电阻被耦合到第四晶体管的第二电流路径端子。

19.根据一个实施例,第一晶体管和第三晶体管是p型晶体管,并且其中第二晶体管和第四晶体管是n型晶体管。

20.根据一个实施例,第一晶体管、第二晶体管、第三晶体管和第四晶体管是金属氧化物半导体晶体管。

21.根据一个实施例,电压转换器还包括第三电路,第三电路被配置为基于第一信号来提供第二信号,第二信号被配置为在第二信号的第一状态与第二信号的第二状态之间切换,其中第三电路被配置为:在第二晶体管关断之后的第一预定持续时间期间,将第二信号保持在第二信号的第二状态;在第一持续时间之后,在第一信号切换到第一信号的第一状态之后,将第二信号切换到第二信号的第一状态;以及在第二信号切换到第二信号的第一状态之后的第二预定持续时间期间,将第二信号保持在第二信号的第一状态。

22.在第二方面,提供了一种电子电路,该电子电路包括:第一电路,具有:被配置为与第一晶体管的控制端子耦合的第一输出、被配置为与第二晶体管的控制端子耦合的第二输出、以及被配置为经由电感而与第一晶体管和第二晶体管耦合的第一输入;以及第二电路,具有:被配置为经由电感而与第一电路的第一输入耦合的第一输入、与第一电路的第一输入耦合的第二输入、以及与第一电路的第二输入耦合的输出,第二电路被配置为:当第一晶体管和第二晶体管关断并且第二电路的第一输入处的第一电压等于第二电路的第二输入处的第二电压时,在第二电路的输出处断言输出信号,并且其中第一电路被配置为:当第二电路的输出信号被断言时,将第一晶体管导通。

23.根据一个实施例,第二电路包括:第三晶体管,具有:被耦合在第一节点和第二节点之间的电流路径,第一节点被配置为接收电源电压,第二节点被配置为接收基准电压;以及第四晶体管,具有:被耦合在第一晶体管的电流路径和第二节点之间的电流路径,其中第

一内部节点被耦合到第二电路的第一输入,第一内部节点被耦合在第三晶体管的电流路径和第四晶体管的电流路径之间,并且其中第三晶体管和第四晶体管的控制端子被耦合到第二电路的第二输入。

24.根据一个实施例,第二电路还包括:第一电阻器,第一电阻器被耦合在第三晶体管的电流路径与第一节点之间;以及第二电阻器,第二电阻器被耦合在第四晶体管的电流路径与第二节点之间。

25.根据一个实施例,第二电路还包括逻辑电路,逻辑电路具有:与第二内部节点耦合的第一输入、与第三内部节点耦合的第二输入、以及与第二电路的输出耦合的输出,第二内部节点被耦合在第三晶体管的电流路径与第一节点之间,第三内部节点被耦合在第四晶体管的电流路径和第二节点之间。

26.根据一个实施例,第一电路包括:第一比较器,具有与第一电路的第一输入耦合的输入;以及有限状态机,具有:与第一电路的第一输出耦合的第一输出、与第一电路的第二输出耦合的第二输出、与第一比较器的输出耦合的第一输入、以及与第一电路的第二输入耦合的第二输入。

27.通过本公开的实施例,使得能够进行滤波以考虑在电感中的电流il不具有零值和稳定值时信号sig到其第一状态的任何第一切换,并且进行滤波以考虑当电流il被抵消时信号sig的任何振荡。

附图说明

28.在以下通过例示而非限制的方式给出的对特定实施例的描述中,将参考附图来对上述特征和优点以及其他特征和优点进行详细描述,其中:

29.图1非常示意性地示出了dc/dc电压转换器的一个示例性实施例;

30.图2示出了图示图1的转换器的示例性操作的时序图;

31.图3a和图3b分别示出了图示图1的转换器的期望或理论操作以及事实或实际操作的其他时序图;

32.图4非常示意性地示出了dc/dc电压转换器的一个实施例;

33.图5以电路形式示出了图4的转换器的一部分的一个实施例;

34.图6以电路形式示出了图4的转换器的一部分的一个实施例变型;

35.图7示出了图示图4的转换器的操作的时序图;

36.图8示出了图4的转换器的更详细的实施例;以及

37.图9示出了图4和图8的转换器的一个实施例。

具体实施方式

38.一些实施例解决了已知的开关式转换器、特别是pfm类型的开关式转换器的所有或一些缺点。

39.一些实施例涉及开关模式电源类型的dc/dc电压转换器,dc/dc电压转换器将直流(dc)电源电压转换为直流(dc)输出电压。一些实施例涉及降压型的dc/dc电压转换器,其中dc输出电压的值低于dc电源电压的值。

40.一个实施例提供了电压转换器,包括:

41.第一mos晶体管,被连接在转换器的内部节点与被配置为接收电源电位的第一节点之间;

42.第二mos晶体管,被连接在转换器的内部节点与被配置为接收基准电位的第二节点之间;电感,被连接在转换器的内部节点和输出节点之间;第一电路,被配置为控制第一mos晶体管和第二mos晶体管;以及第二电路,被配置为当第一晶体管和第二晶体管处于关断状态时检测内部节点的电位何时大于电源电位、内部节点的电位何时小于基准电位、以及内部节点的电位何时等于输出节点的电位,检测到内部节点的电位等于输出节点的电位使得由第一电路调节到第一晶体管的导通状态的切换控制。

43.根据一个实施例,第二电路被配置为在第一信号的第一状态和第一信号的第二状态之间提供第一信号切换,当第一晶体管和第二晶体管处于关断状态并且内部节点的电位等于输出节点的电位时处于第一信号的第一状态,当第一晶体管和第二晶体管处于关断状态并且内部节点的电位大于电源电位或小于基准电位时处于第一信号的第二状态。

44.根据一个实施例,第一电路被配置为基于第一信号而调节到第一晶体管的导通状态的控制。

45.根据一个实施例,第二电路包括串联耦合在第一节点和第二节点之间的第三mos晶体管和第四mos晶体管,第二电路被配置为使得内部节点的电位确定第三晶体管和第四晶体管中的每个晶体管的关断或导通状态。

46.根据一个实施例,第二电路还被配置为使得当内部节点的电位等于输出节点的电位时,第三晶体管和第四晶体管处于相同的导通或关断状态。

47.根据一个实施例,第一信号基于第三晶体管和第四晶体管的漏极的电位来确定。

48.根据一个实施例,第二电路包括组合电路,组合电路的一个输入被耦合到第三晶体管的漏极,并且其另一输入被耦合到第四晶体管的漏极,组合电路包括被配置为提供第一信号的输出。

49.根据一个实施例,组合电路包括and门,and门的一个输入被耦合到第三晶体管的漏极,其另一输入通过反相器闸被耦合到第四晶体管的漏极,并且其另一输出被耦合到组合电路的输出。

50.根据一个实施例,第三晶体管和第四晶体管的源极被配置为接收内部节点的电位,或者第三晶体管和第四晶体管的栅极被配置为接收内部节点的电位。

51.根据一个实施例:第三晶体管和第四晶体管的源极被配置为接收内部节点的电位;第三晶体管和第四晶体管的栅极被配置为接收输出节点的电位;第三晶体管的漏极被耦合到第一节点;并且第四晶体管的漏极被耦合到第二节点。

52.根据一个实施例,第一晶体管和第四晶体管是pmos晶体管,第二晶体管和第三晶体管是nmos晶体管。

53.根据一个实施例:第三晶体管和第四晶体管的栅极被配置为接收内部节点的电位;第三晶体管的源极被耦合到第一节点;第四晶体管的源极被耦合到第二节点;并且第三晶体管的漏极通过至少一个电阻被耦合到第四晶体管的漏极。

54.根据一个实施例,第一晶体管和第三晶体管是pmos晶体管,第二晶体管和第四晶体管是nmos晶体管。

55.根据一个实施例,转换器还包括第三电路,第三电路被配置为基于第一信号,在第

二信号的第一状态和第二信号的第二状态之间提供第二信号切换,第三电路被配置为:在控制第二晶体管切换到关断状态之后的第一预定持续时间期间,将第二信号保持在第二信号的第二状态;在第一持续时间之后,在将第一信号切换到第一信号的第一状态之后,将第二信号切换到第二信号的第一状态;以及在将第二信号切换到第二信号的第一状态之后的第二预定持续时间期间,将第二信号保持在第二信号的第一状态。

56.另一实施例提供了包括所公开的转换器的电子电路。

57.在各个附图中,相同的特征已由相同的附图标记表示。具体地,在各个实施例之间共有的结构和/或功能特征可以具有相同的附图标记并且可以设置相同的结构、尺寸和材料性质。

58.为了清楚起见,仅详细图示和描述了对理解本文所述实施例有用的操作和元件。具体地,没有详细描述可以提供dc/dc转换器的典型应用,所公开的实施例与这些典型应用兼容。

59.除非另有说明,否则当提及连接在一起的两个元件时,表示没有除导体以外的任何中间元件的直接连接;当提及耦合在一起的两个元件时,表示这两个元件可以连接或者它们可以经由一个或多个其他元件耦合。

60.在以下公开中,除非另有说明,否则当提及绝对位置限定词(例如,术语“前”、“后”、“上”、“下”、“左”、“右”等)或相对位置限定词(例如,术语“上方”、“下方”、“较高”、“较低”等)或取向限定词(例如,“水平”、“竖直”等)时,参考图中所示的定向。

61.除非另有说明,否则表述“约”、“大约”、“基本上”和“在

…

的量级”表示在10%以内,优选在5%以内。

62.在随后的描述中,当引用节点的电压时,除非另有说明,否则认为这涉及节点和基准电位之间的电压,基准电位通常为接地。此外,当提及节点的电位时,认为除非另外指出,否则该电位相对于基准电位为基准。给定节点的电压和电位将进一步由相同的附图标记指定。

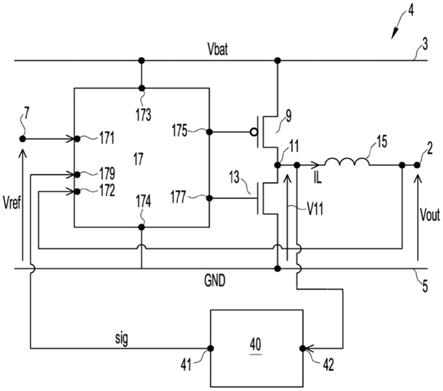

63.图1非常示意性地示出了所公开的实施例适用的类型的电压转换器1的一个示例。在该示例中,转换器1是开关模式电源类型的dc/dc转换器,其将直流(dc)电源电压转换为直流(dc)输出电压。

64.转换器1被配置为提供相对于基准电位(通常为接地gnd)为基准的直流输出电位vout。转换器包括输出节点2,电位vout在输出节点2上可用。

65.转换器1由相对于基准电位gnd(通常为接地)为基准的直流电位vbat供电。转换器1然后被连接在置于电位vbat处的第一导电轨或节点3与置于基准电位gnd处的第二导电轨或节点5之间。

66.转换器1被配置为以等于设定点值的值来提供电位vout。为此,转换器1在输入节点7上接收相对于电位gnd为基准的设定点直流电位vref,设定点直流电位vref的值表示电位vout的设定点值,优选地等于电位vout的设定点值。

67.在该示例中,电位vout、vbat和vref为正。

68.在该示例中,转换器1是降压(step

‑

down/buck)型的,即,电位vout的设定点值小于电位vbat的值。换言之,电位vout的值小于电位vbat的值。

69.转换器1包括第一mos(金属氧化物半导体)晶体管9,优选地是pmos晶体管(p沟道

mos晶体管)。mos晶体管9被连接在轨3和内部节点11之间。换言之,晶体管9的第一导电端子(例如,其源极)被连接到轨3,晶体管9的第二导电端子(例如,其漏极)被连接到节点11。

70.转换器1还包括第二mos晶体管13,优选地是nmos晶体管(n沟道mos晶体管)。晶体管13被连接在节点11和轨5之间。换言之,晶体管13的第一导电端子(例如,其源极)被连接到轨5,晶体管9的第二导电端子(例如,其漏极)被连接到节点11。

71.因此,晶体管9和13被串联连接在轨3和5之间,并且在内部节点11处彼此连接。

72.转换器1包括电感元件或电感15。电感15被连接在节点11和节点2之间。

73.转换器1包括控制电路17。电路17被配置为实现或控制转换器1的操作周期,以将电位vout调节为使得其值等于设定点值vref。

74.为此,电路17包括:

75.端子171,被耦合(优选地被连接)至节点7;

76.端子172,被耦合(优选地被连接)至节点2;

77.端子173,被耦合(优选地被连接)至轨3;

78.端子174,被耦合(优选地被连接)至轨5;

79.端子175,被耦合(优选地被连接)至晶体管9的控制端子或栅极;以及

80.端子177,被耦合(优选地被连接)至晶体管13的控制端子或栅极。

81.转换器1包括连接在节点2和轨5之间的输出电容(未示出)。作为示例,该电容为2.2μf至20μf的量级,或者甚至更大。该输出电容用作滤波器。换言之,转换器的该输出电容使得可以将在节点2上存在的电流平滑化,并存储由转换器提供给节点2的能量。

82.尽管此处未示出,但是在操作期间,充电器(charge)被连接在节点2和轨5之间,从而由电位vout供电。该充电器包括节点2和轨5之间的输入电容。优选地,持续时间ton取决于电位vbat,并且对于电位vbat的给定值,持续时间ton是恒定的。

83.在该示例中,转换器1被配置为以脉冲频率调制(不连续导电模式)操作。电路17然后被配置为当电位vout的值低于设定点值vref并且两个晶体管9和13处于关断状态时,开始转换器1的操作周期。更具体地,在每个操作周期的开始处,电路17被配置为控制将晶体管9置于导通状态,晶体管13处于关断状态。然后在第一持续时间ton期间,能量在电感15中积累,第一持续时间ton例如对于每个操作周期恒定,在每个操作周期中,晶体管9被电路17保持在导通状态,电流il然后在电感15中循环。在持续时间ton结束时,电路17被配置为控制将晶体管9置于关断状态并且将晶体管13置于导通状态。然后在第二持续时间toff期间,能量被电感15恢复到在转换器的输出处连接的电荷,第二持续时间toff例如对于每个操作周期恒定,在每个操作周期中,晶体管13被电路17保持在导通状态,然后在电感中循环的电流il减小。在持续时间toff结束时,电路17被配置为控制将晶体管13置于关断状态。

84.持续时间toff被确定为使得:电路17控制将晶体管13置于关断状态的时刻对应于循环流过电感的电流il被抵消的时刻。然而,实际上,如将在说明书的其余部分中更详细地公开的,情况并非总是如此,这是有问题的。

85.图2示出了图示图1的转换器1的期望示例性操作的时序图。

86.图2顶部的时序图图示了电位vout(以伏特v为单位)随时间t的演变,图2底部的时序图图示了流过电感15的电流il随时间t的对应演变。

87.在时刻t0,晶体管9和13处于关断状态,电流il为零,并且电位vout的值大于其设

定点值,设定点值在该示例中为电位vref的值。

88.在时刻t0和随后的时刻t2之间,例如由于连接到转换器1的电荷消耗电流这一事实,电位vout减小。

89.在时刻t0和t2之间的时刻t1处,电位vout变得低于其设定点值vref。这由转换器1的电路17来检测,电路17然后控制将晶体管9置于导通状态。在时刻t2处,晶体管9导通。

90.因此,从时刻t2起,电感15的一个端子被连接到节点2,而一个端子经由晶体管9被耦合到轨3。循环流过电感15的电流il增大。

91.结果,从时刻t2起,电流il被提供给节点2,并且节点2与轨5之间的电容(图1中未示出)被充电。电位vout增加并且再次高于其设定点值vref。

92.在随后的时刻t3处,t3等于t2 ton,电路17控制将晶体管13置于导通状态并且将晶体管9置于关断状态。在时刻t3处,电感中的电流具有最大值ilp。

93.因此,从时刻t3起,电感15的一个端子被连接到节点2,并且一个端子经由晶体管13被连接到轨5。循环流过电感15的电流il减小。

94.尽管电流il从时刻t3开始减小,只要它不为零,则节点2和轨5之间的电容继续被充电,并且如果由电荷汲取的电流小于提供给节点2的电流il,则电位vout继续增加。

95.在随后的时刻t4处,t4等于t3 toff,电路17控制将晶体管13置于关断状态。此处认为转换器1按其应有的方式操作,并且电流il然后在时刻t4处为零。但是,实际上并非总是如此。

96.从时刻t4开始,电流il为零,并且电位vout减小,类似于时刻t0发生的情况。

97.尽管此处未示出,但是当电位vout的值在时刻t4之后的时刻返回到其设定点值vref以下时,电路17实现如关于连续时刻t2、t3和t4所描述的新的操作周期。

98.图3a和图3b示出了图示图1的转换器1的操作的其他时序图。更具体地,图3a示出了电流il的演变的理想或理论示例。图3b示出了电流il的实际演变的示例。图3a和图3b的这两个时序图图示了示例性操作,其中对于若干连续的操作周期,电压vout小于转换器1的每个操作周期结束时的电压vref。

99.在时刻t30处,尽管在图3a中未图示,但是电压vout小于电压vref。操作周期从切换到晶体管9的导通状态开始。结果,电流il增大,直到随后的时刻t31,t31等于t30 ton。

100.在时刻t31处,电流il达到其最大值ilp。此外,晶体管9和13分别被切换到关断状态和导通状态。结果,电流减小,直到随后的时刻t32,t32等于t31 toff。

101.在该理想的示例性操作中,晶体管13在时刻t32处被切换到关断状态,并且电流il在时刻t32处被抵消。

102.在时刻t32处,电压vout小于电压vref,晶体管9被切换到导通状态,这标志着新的操作周期的开始。电流il然后增大,直到随后的时刻t33,t33等于t32 ton。

103.在时刻t33处,电流il达到值ilp。此外,晶体管9和13分别被切换到关断状态和导通状态。结果,电流减小,直到随后的时刻t34,t34等于t33 toff。

104.在该理想的示例性操作中,晶体管13在时刻t34处被切换到关断状态,并且电流il在时刻t34处被抵消。

105.在时刻t34处,电压vout小于电压vref,晶体管13被切换到导通状态,这标志着新的操作周期的开始。电流il增加,直到随后的时刻t35,t35等于t34 ton。

106.在时刻t35处,电流il达到值ilp。此外,晶体管9和13分别被切换到关断状态和导通状态。结果,电流减小,直到随后的时刻t36,t36等于t35 toff。

107.在该理想的示例性操作中,晶体管13在时刻t36处被切换到关断状态,并且电流il在时刻t36处被抵消。

108.在时刻t36处,电压vout小于电压vref,新的操作周期开始。

109.在图3a的时序图所示的示例性理论操作中,在每个操作周期结束时,在电流il被抵消的时刻,发生到晶体管13的关断状态的切换。因此,当一个新的操作周期紧随一个操作周期之后,在该新的操作周期中,电流il从零值增加。

110.图3b的时序图图示了转换器1的对应实际操作示例。在该实际操作示例中,考虑了如下实际情况:其中在自其上次切换到导通状态以来已经经过的持续时间toff结束时,晶体管13没有立即切换到关断状态。

111.在时刻t40处,电压vout小于电压vref,操作周期从切换到晶体管9的导通状态开始。结果,电流il增加,直到随后的时刻t41,t41等于t40 ton。

112.在时刻t41处,电流il达到其最大值ilp。此外,晶体管9和13分别被切换到关断状态和导通状态。结果,电流减小,直到随后的时刻t42,t42等于t41 toff。电流然后在时刻t42处被抵消。然而,将晶体管13切换到关断状态仅在时刻t42之后的时刻t43处才有效。因此,在时刻t42和t43之间,电流il为负并且减小。换言之,电流在时刻t42之前在电感15中从节点11循环流向节点2;在时刻t42处被抵消;并且从时刻t42之后,在电感15中从节点2循环流向节点11。

113.在时刻t43处,电压vout小于电压vref,在时刻t43处,晶体管9被切换到导通状态,这标志着新的操作周期的开始。电流il然后增大,直到随后的时刻t44,t44等于t43 ton。

114.在时刻t44处,由于持续时间ton在每个周期中恒定的事实,电流il达到值ilp’,值ilp’小于最大值ilp。此外,晶体管9和13分别被切换到关断状态和导通状态。结果,电流il减小,直到随后的时刻t46,t46等于t44 toff,在时刻t44和t46之间包括的时刻t45处,电流il被抵消。此外,将晶体管13切换为关断状态仅在时刻t46之后的时刻t47处才有效。因此,在时刻t45和t47之间,电流il为负并且减小到比时刻t43达到的值更低(或绝对值大)的值。

115.在时刻t47处,电压vout小于电压vref,在时刻t47处,晶体管9被切换到导通状态,这标志着新的操作周期的开始。电流il然后增大,直到随后的时刻t48,t48等于t47 ton。

116.在时刻t48处,电流il达到值ilp”,值ilp”低于值ilp’。此外,晶体管9和13分别被切换到关断状态和导通状态。结果,电流il减小,直到随后的时刻t50,t50等于t48 toff,电流il在时刻t48和t50之间所包括的时刻t49处被抵消。此外,将晶体管13切换到关断状态仅在时刻t50之后的时刻t51处才有效。因此,在时刻t49和t51之间,电流il为负并且减小到比时刻t47所达到的值更低(或绝对值更大)的值。

117.因为在图3b的时序图所示的每个操作周期中,电流il达到的最大值(时刻t41、t44和t48)越来越小,所以转换器1未向节点2提供足够的能量来将电压vout调节到其值vref,电压vout例如越来越低,这是有问题的。此外,在图3b的时序图所示的每个操作周期中,电流il所达到的负值(时刻t43、t47和t51)越来越低(或绝对值越来越高),因此,转换器1在节点2上汲取越来越多的能量,这是不期望的。理论上,电流il的最大值可以减小到无穷,但是实际上,在此之前晶体管13被电流il的负值破坏,使得晶体管13不能跨其导电端子循环。

118.关于图3b的时序图,描述了一个实际的操作示例,其中,在电流il抵消之后,发生到晶体管13的关断状态的切换。

119.在未图示的另一实际操作示例中,在一个紧接一个地实现的多个连续周期的每个操作周期中,晶体管13被切换到关断状态,同时电流il不为零并且仍然为正。在这种情况下,在这些操作周期的每一个操作周期中,电流il从越来越高的值开始增加,结果,电流il达到越来越高的最大值,并且操作周期以电流il的越来越高的非零且正值结束。该操作没有关于图3b的时序图所描述的那样麻烦,因为在若干操作周期之后,电压vout将重新获得其设定点值vref。因此,随后的操作周期将不会被立即执行,这将为抵消电流il留下时间。然而,相对于关于图3a的时序图描述的理想操作的情况,这样的操作将引起转换器1的更高的消耗,这是不期望的。

120.在一些实施例中,发明人建议使得操作周期的开始服从电导15中的电流il为零的条件。换言之,当在操作周期的结束处,晶体管13被切换到关断状态同时电流il不为零时,发明人建议,只要电流il未再恢复为零值,就延迟随后的操作周期的开始。

121.更具体地,发明人已观察到,当晶体管13被切换到关断状态,同时晶体管9关断且电流il为非零且为正时,电流il在晶体管13的本征或体二极管中循环。结果,节点11的电位为负并且等于

‑

vdiode,vdiode是当电流il在该体二极管中循环时,跨晶体管13的体二极管的端子的电压值(绝对值)。发明人还观察到,当晶体管13被切换到关断状态,同时晶体管9关断且电流il为非零且为负时,电流il接下来在晶体管9的本征或体二极管中循环。结果,节点11的电位为正并且等于vbat vdiode,其中vdiode是当电流il在该体二极管中循环时,跨晶体管9的体二极管的端子的电压值(绝对值)。此外,当节点11的电位等于节点2的电位时,电流il为零。

122.因此,在一些实施例中,发明人建议利用当晶体管9和13处于关断状态时,节点11的电位可以根据电流il而变化的所有三个状态。更具体地,在一些实施例中,发明人建议,在节点11的电位的这三个状态之中,检测节点11的电位等于节点2的电位的状态,这意味着电流il然后为零。为此,在一些实施例中,发明人提出了一种电路,该电路被配置为当晶体管9和13处于关断状态时检测节点11的电位何时大于电源电位vbat、节点11的电位何时小于基准电位gnd以及节点11的电位何时等于节点2的电位,从而使得操作周期的开始经历如下检测:节点11的电位等于节点2的电位。根据一个实施例,该电路被配置为提供在第一状态与第二状态之间切换的信号,第一状态例如为当晶体管9和13处于关断状态并且节点11的电位等于输出节点的电位时的高状态,第二状态例如为当晶体管9和13处于关断状态并且节点11的电位大于电位vbat或小于电位vbat时的低状态。晶体管9到导通状态的切换然后基于该信号进行调节。

123.图4非常示意性地示出了包括这样的电路的dc/dc电压转换器4的一个实施例。转换器4包括与图1的转换器1公共的许多功能或结构元件,因此将不再赘述,这里仅强调这两个转换器1和4之间的差异。

124.相对于转换器1,转换器4包括附加电路40。电路40被配置为当晶体管9和13处于关断状态时检测节点11的电位何时大于电源电位vbat、节点11的电位何时低于基准电位gnd以及节点11的电位何时等于节点2的电位。

125.更具体地,电路40被配置为在电路40的一个输出41上提供信号sig,信号sig在第

一状态(例如,高状态,例如等于轨3的电位vbat)和第二状态(例如,低状态,例如等于轨5的电位gnd)之间切换,第一状态是晶体管9和13处于关断状态并且电路40检测到节点11的电位等于节点2的电位vout时的状态,第二状态是晶体管9和13处于关断状态并且电路40检测到内部节点11的电位等于vbat vdiode(因此大于轨3的电位vbat)、或者等于

‑

vdiode(因此小于轨5的电位gnd)时的状态。

126.电路40包括输入42,输入42被耦合(优选地被连接至)节点11。输入42被配置为接收节点11的电位,在本公开的其余部分中该电位被标记为v11。

127.根据未图示的一个优选实施例,电路40包括附加输入,附加输入被耦合(优选地被连接至)节点2。该附加输入然后被配置为接收电位vout,并且被耦合(优选地被连接至)节点2。

128.尽管此处未示出,但是电路40优选地由电位vbat供电。电路40然后包括分别连接到轨3和轨5的两个供电端子。

129.在图4所示的实施例中,电路40的输出信号sig被直接提供给电路17的输入179。电路17然后被配置为基于信号sig来调节转换器4的每个操作周期的开始。换言之,电路17然后被配置为基于信号sig的状态,在每个操作周期的开始将晶体管9切换到导通状态。换言之,电路17被配置为基于信号sig,确定电感15中的电流il是否为零,并且仅在电流il为零时,才控制到晶体管9的导通状态的切换。

130.图5以电路形式示出了图4的转换器4的一部分的一个实施例。更具体地,图5示出了转换器4的电路40的一个实施例。

131.在该实施例中,电路40包括附加输入(在此处被标记为50),附加输入被配置为接收节点2的电位vout。

132.电路40包括串联耦合在轨3和5之间的两个mos晶体管51和52。电路40被配置为使得节点11的电位v11确定晶体管51和52中的每个晶体管的导通或关断状态。更具体地,电路40被配置为使得:当电位v11等于电位vout时,两个晶体管51和52均处于相同状态,在该实施例中为关断状态。相反,电路40被配置为使得:当电位v11等于vbat vdiode并且当电位v11等于

‑

vdiode时,晶体管51和52处于不同的导通和关断状态。如果当这些晶体管51和52中的一个晶体管处于关断状态时,这些晶体管51和52中的另一晶体管处于导通状态,则晶体管51和52被认为处于不同的关断和导通状态。

133.晶体管51被连接在轨3和电路40的内部节点53之间,晶体管52被连接在节点53和轨5之间。更具体地,晶体管51和52分别是nmos晶体管和pmos晶体管。晶体管51包括导电端子(此处未其源极,被耦合、优选地被连接到节点53)、另一导电端子(此处是其漏极,此处借助电阻r1被耦合到轨3)以及控制端子或栅极(被耦合、优选地被连接到电路40的输入50)。晶体管52包括导电端子(此处为其源极,被耦合、优选地被连接至节点53)、另一导电端子(此处为其漏极,此处借助电阻r2被耦合至轨5)以及控制端子或栅极(被耦合、优选地被连接至电路40的输入50)。换言之,晶体管51和52的控制端子彼此连接,并且被配置为接收节点2的电位vout,晶体管51和52的源极彼此耦合、优选地彼此连接,并且被配置为接收节点11的电位v11。

134.电路40还包括组合电路55,即,包括一个或多个逻辑门的电路。电路55被配置为基于晶体管51和52的漏极的电位来提供信号sig。电路55包括:与晶体管51的漏极连接的第一

输入551、与晶体管52的漏极连接的第二输入552以及与电路40的输出41连接的输出553。电路55的输出553被配置为提供信号sig。

135.根据一个实施例,电路55包括and逻辑门554。门554的输入被耦合、优选地被连接到电路55的输入551,因此被连接到晶体管51的漏极。门554的另一输入通过使用反相器闸555,被耦合到电路55的输入52,因此被耦合到晶体管52的漏极。门554的输出被耦合、优选地被连接到电路50的输出553,因此被连接到电路40的输出41。

136.图5的电路40的操作如下。

137.当电位v11等于vbat vdiode时,晶体管51由于其栅极处于比其源极的电位vbat vdiode小的电位vout的事实而关断。此外,晶体管52由于其栅极处于比其源极的电位vbat vdiode小的电位vout的事实而导通。结果,晶体管51的漏极电位比电位gnd更接近电位vbat,然后被认为处于高电平或状态。此外,晶体管52的漏极电位也比电位gnd更接近电位vbat,然后被认为处于高电平或状态。因此,门554以高电平或状态提供信号sig。

138.当电位v11等于

‑

vdiode时,晶体管51由于晶体管51的栅极处于比其源极的电位

‑

vdiode大的电位vout的事实而导通。此外,晶体管52由于其栅极处于比其源极的电位

‑

vdiode大的电位vout的事实而关断。结果,晶体管51的漏极电位比电位vbat更靠近电位gnd,然后被认为处于低电平或状态。此外,晶体管52的漏极电位比电位vbat更接近电位gnd,然后被认为处于低电平或状态。因此,门554以低电平或状态提供信号sig。

139.当电位v11等于节点2的电位vout时,晶体管51和52由于其栅极处于与其源极相同的电位的事实而均关断。结果,晶体管51的漏极电位比电位gnd更接近电位vbat,然后被认为处于高状态。相反,晶体管52的漏极电位比电位vbat更靠近电位gnd,然后被认为处于低状态。门554以高电平或状态提供信号sig。

140.因此,当在图4的转换器4中提供图5的电路40时,到晶体管9的导通状态的切换的条件是信号sig处于高状态。

141.本领域技术人员能够确定电阻r1和r2的值来获得上文所公开的操作。

142.在未示出的一个实施例变型中,电路55可以使用其他逻辑门来实现,例如,使用nand门代替门554。在后一示例中,信号sig的高状态和低状态然后被反转,并且转换器4的操作相应地适配。

143.在另一未图示的实施例变型中,提供了当不使用该电路40时,例如当图4的转换器4的晶体管9和13中的一个或另一个处于导通状态时,将图5的电路40的输入42断开连接。作为示例,然后在转换器4的节点11和图5的电路40的输入42之间提供开关。转换器4然后包括一电路,该电路被配置为:当晶体管9和13中的一个导通时,将该开关置于断开状态,并且当两个晶体管9和13中的一个关断时,将该开关置于闭合状态。具体地,该电路可以基于由电路17提供的晶体管9和13的控制信号来生成开关的控制信号。

144.图6以电路形式示出了图4的转换器4的一部分的一个实施例变型。更具体地,图6示出了转换器4的电路40的一个实施例变型。

145.在该实施例中,电路40不包括被配置为接收节点2的电位vout的附加输入。

146.电路40包括串联耦合在轨3和5之间的两个mos晶体管61和62。电路40被配置为使得节点11的电位v11确定晶体管61和62中的每一个的导通或关断状态。更具体地,电路40被配置为使得当电位v11等于电位vout时,两个晶体管61和62均处于相同状态,在该实施例中

为导通状态。相反,电路40被配置为使得当电位v11等于vbat vdiode并且当电位v11等于

‑

vdiode时,晶体管61和62处于不同的导通和关断状态。

147.晶体管61被连接在轨3和晶体管62之间,晶体管62被连接在晶体管61和轨5之间。换言之,晶体管61通过其导电端子将轨3耦合到晶体管62的导电端子,晶体管62通过其导电端子将轨5耦合到晶体管61的导电端子。更具体地,晶体管61和62分别是pmos晶体管和nmos晶体管。晶体管61包括:导电端子,此处是其源极,其被耦合、优选地被连接到轨3;另一导电端子,此处是其漏极,此处通过使用电阻r而被耦合到晶体管62;以及控制端子或栅极,其被耦合、优选地被连接到电路40的输入42。晶体管62包括导电端子,此处是其源极,其被耦合、优选地被连接到轨5;另一导电端子,此处是其漏极,此处借助电阻r被耦合到晶体管61;以及控制端子或栅极,其被耦合、优选地被连接到电路40的输入42。换言之,晶体管61和62的控制端子彼此连接并且被配置为接收节点11的电位v11,晶体管61和62的漏极借助电阻r彼此耦合。在未示出的实施例变型中,电阻r被串联在晶体管61和62之间的若干电阻r代替。

148.电路40还包括组合电路55。电路55在此处被配置为基于晶体管61和62的漏极的电位来提供信号sig。电路55的第一输入551被耦合、例如被连接至晶体管61的漏极,电路55的第二输入552被耦合、例如被连接至晶体管62的漏极,并且电路55的输出553被连接至电路40的输出41。

149.图6的电路40的操作如下。

150.当电位v11等于vbat vdiode时,晶体管61由于其栅极处于比其源极电位vbat大的电位v11处的事实而关断。此外,晶体管62由于其栅极处于比其源极电位gnd大的电位v11处的事实而导通。结果,晶体管61的漏极电位比电位vbat更接近电位gnd,然后被认为处于低状态。此外,由于晶体管62导通的事实,晶体管62的漏极电位也比电位vbat更接近电位gnd,然后被认为处于低状态。因此,门554在低状态下提供信号sig。

151.当电位v11等于

‑

vdiode时,晶体管61由于其栅极处于比其源极电位vbat小的电位

‑

vdiode的事实而导通。此外,晶体管62由于其栅极处于比其源极电位gnd小的电位

‑

vdiode处的事实而关断。结果,由于晶体管61导通的事实,晶体管61的漏极电位比电位gnd更接近电位vbat,然后被认为处于高状态。此外,晶体管62的漏极电位比电位gnd更接近电位vbat,然后被认为处于高状态。因此,门554在低状态下提供信号sig。

152.当电位v11等于节点2的电位vout时,晶体管61和62均导通。具体地,晶体管61由于其栅极处于比其源极电位vbat低的电位vout处的事实而导通,并且晶体管62由于其栅极处于比其源极电位gnd大的电位vout处的事实而导通。结果,晶体管61的漏极电位比电位gnd更接近电位vbat,然后被认为处于高状态。相反,晶体管62的漏极电位比电位vbat更靠近电位gnd,然后被认为处于低状态。因此,门554在高状态下提供信号sig。

153.因此,当在图4的转换器4中提供图6的电路40时,到晶体管9的导通状态的切换的条件是信号sig处于高状态。

154.本领域技术人员能够确定将晶体管61和62彼此串联耦合的一个电阻r或多个电阻的值来获得上文所公开的操作。

155.在未示出的一个实施例变型中,电路55可以使用其他逻辑门来实现,例如使用nand门代替门554。在后一示例中,信号sig的高状态和低状态然后被反转,并且转换器4的操作相应地适配。

156.在又一未示出的实施例变型中,提供了当不使用该电路40时,例如当图4的转换器4的晶体管9和13中的一个或另一个处于导通状态时,将图6的电路40去激活。作为示例,然后在晶体管61的漏极和电阻r之间提供一个开关,并且在晶体管62的漏极和电阻r之间提供另一开关。转换器4则包括一电路,该电路被配置为在晶体管9和13之一导通时,将这些开关置于断开状态,而在两个晶体管9和13之一关断时,将这些开关置于闭合状态。具体地,该电路可以基于由电路17提供的晶体管9和13的控制信号来生成开关的控制信号。

157.图7示出了图示图4的转换器的操作的时序图。更具体地,图7的时序图图示了如下情况,其中对于若干连续的操作周期,在转换器4的每个操作周期结束时,电压vout小于电压vref。进一步考虑其中在电流il为负的同时,晶体管13被切换到关断状态的操作示例。

158.在时刻t70处,尽管在图7中未图示,但是电压vout小于vref,并且电路17基于信号sig来确定电流il为零。操作周期然后从切换到晶体管9的导通状态开始。结果,电流il增大,直到随后的时刻t71,t71等于t70 ton。

159.在时刻t71处,电流il达到其最大值ilp。此外,晶体管9和13被电路17分别切换到关断状态和导通状态。结果,电流减小,直到随后的时刻t72,t72等于t71 toff。电流然后在时刻t72处被抵消。然而,将晶体管13切换到关断状态仅在时刻t72之后的时刻t73才有效。因此,在时刻t72和t73之间,电流il为负并且减小。

160.在时刻t73处,电压vout小于电压vref。然而,电路17基于信号sig来确定电流il不为零。因此,在时刻t73处,电路17不将晶体管9切换为导通状态。然后循环流过晶体管13的体二极管的电流il逐渐增加,直到在时刻t73之后的时刻t74为零。在时刻t74处,电路17基于信号sig来确定电流il为零,并且由于电压vout小于电压vref,因此电路17将晶体管9切换到导通状态,这标志着新操作周期开始。电流il然后增加,直到随后的时刻t75,t75等于t74 ton。

161.在时刻t75处,电流il达到值ilp。此外,晶体管9和13分别被切换到关断状态和导通状态。结果,电流il减小,直到随后的时刻t76,t76等于t75 toff。仅在时刻t76之后的时刻t77处将晶体管13切换至关断状态才有效。因此,在时刻t76和t77之间,电流il为负并且减小。

162.在时刻t77处,电压vout小于电压vref。然而,电路17基于信号sig来确定电流il不为零。因此,在时刻t77处,电路17不将晶体管9切换为导通状态。然后循环流过晶体管13的体二极管的电流il逐渐增加,直到在时刻t77之后的时刻t78为零。在时刻t78处,电路17基于信号sig而确定电流il为零,并且由于电压vout小于电压vref,因此电路17将晶体管9切换到导通状态,这标志着新操作周期的开始。电流il然后增加,直到随后的时刻t79,t79等于t78 ton。

163.在时刻t79处,电流il达到值ilp。此外,晶体管9和13分别被切换到关断状态和导通状态。结果,电流il减小,直到随后的时刻t80,t80等于t79 toff。

164.相对于关于图3b的时序图所描述的,尽管在电流il为负的同时发生到晶体管13的关断状态的切换,但是由于电路40及其所提供的信号sig,电路17能够延迟新操作周期的实现(将晶体管9切换到导通状态),直到电流il具有零值。因此,在每个操作周期中,电流il达到相同的最大值ilp,并且保持将电压vout调节到其设定点值。

165.尽管图7的时序图图示了转换器4在电流il为负的同时发生到晶体管13的关断状

态的切换的情况下的操作,但是电路40在以下情况下还具有优势:例如,因为持续时间toff相对于持续时间ton太短,所以晶体管13在电流il仍为正时被切换到关断状态。

166.例如,当在电流il为正且电压vout低于电压vref的同时,晶体管13切换到关断状态时,电路17基于信号sig来确定电流il不为零。电路17因此不将晶体管9切换到导通状态。然后在晶体管9的体二极管中循环的电流il然后减小,直到其被抵消。电路17基于信号sig而确定电流il为零,并且如果电压vout仍低于电压vref,则电路17通过将晶体管9切换到导通状态来控制新的操作周期的开始。在这样的操作状态下,如关于图7所描述的那样,在每个操作周期中,电流il达到相同的最大值ilp,并且保持将电压vout调节到其设定点值。

167.图8示出了图4的转换器的更详细的实施例。此处仅突出显示在图4中未图示的细节,这些细节与转换器4的电路17有关,由图8中的虚线框界定。

168.电路17包括有限状态机300。有限状态机300可以例如使用耦合到存储器的自定义组合逻辑来实现。还可以是其他实现方式,例如使用例如可编程通用控制器。

169.有限状态机300被配置为将晶体管9和13的控制信号提供给相应端子175和177,以执行关于图4至图7所公开的操作。为了确定晶体管9和13的控制信号,有限状态机300接收若干信号。作为示例,有限状态机300由电路实现。电路300由电位vbat供电,并且被连接在轨3和5之间,这些连接在图8中未详细描述,以免使该附图过载。

170.电路17包括比较器302,比较器302被配置为在其输出上提供信号start,信号start表示电位vout的值与其设定点值的比较。比较器302的输出被耦合、例如被连接到电路300。当电位vout的值低于其设定点值时,信号start处于第一状态(例如,高状态),当电位vout的值高于其设定点值时,信号start处于第二状态(例如,低状态)。比较器302包括第一输入(例如,反相输入(

‑

))和第二输入(例如,非反相输入( )),第一输入被配置为接收其值表示电位vout的值的电位,第二输入被配置为接收其值表示电位vout的设定点值的电位。

171.在该示例中,在电位vref的值等于电位vout的设定点值的情况下,比较器302被配置为将电位vref与电位vout进行比较,比较器302的第一输入被连接到节点2,并且比较器302的第二输入被连接到电路17的端子171。

172.在该实施例中,持续时间ton通过将电位斜坡rp与电位vref或电位vout进行比较来确定,后者能够被认为等于电位vref。因此,电路17包括斜坡发生器304和比较器306,斜坡发生器304被配置为提供电位斜坡rp,比较器306被配置为将斜坡rp与电位vref或vout(在该示例中为电位vref)进行比较。电位rp以基准电位gnd为基准。

173.发生器304由电位vbat供电,并被连接在轨3和5之间,这些连接在图8中未详细示出,以免使得该附图过载。

174.通过使用信号cmdp,发生器304被电路300控制。更具体地,当start信号处于指示电位vout的值小于其设定点值的第一状态时,如果两个晶体管9和11处于关断状态并且如果电路300基于其接收的信号sig而确定电流il为零时,电路300控制将晶体管9置于导通状态,并且同时经由信号cmdp来控制电位斜坡rp的启动或开始。作为示例,信号cmdp基于由电路300提供给晶体管9的控制信号来确定,或者与由电路300提供给晶体管9的控制信号相同。

175.根据一个实施例,每个电位斜坡rp是从基准电位gnd开始的递增的斜坡。

176.斜坡rp被传输到比较器306的第一输入(例如,非反相输入( )),比较器306的第二输入(例如,反相输入(

‑

))接收电位vref,并且比较器306的输出将信号comp提供给电路300。

177.根据图8所示的优选实施例,通过使用包括两个输入、输出和控制端子的选择电路308,电位斜坡rp被传输到比较器306。电路308的控制端子从电路300接收信号sel。根据信号sel的状态,电路308在其输出上传输在其输入中的一个或另一个上存在的信号。

178.更具体地,在电路300控制将晶体管9置于导通状态和开始电位斜坡rp的时刻,电路300将信号sel置于第一状态,使得比较器306接收电位斜坡rp。

179.因此,只要信号sel保持在其第一状态,信号comp便处于第一状态(例如,低状态),而电位rp低于电位vref,并且一旦电位rp变得大于电位vref,信号comp切换到第二状态(例如,高状态)。

180.信号comp从其第一状态切换到其第二状态标志着持续时间ton的结束。电路300然后控制将晶体管9置于关断状态并且将晶体管13置于导通状态。优选地,电路300经由信号cmdp来同时控制电位斜坡rp的结束。

181.在该实施例中,持续时间toff通过将电位斜坡rn与电位vref或电位vout比较,并且更具体地在该示例中与电位vref比较来确定。因此,电路17包括斜坡发生器310,斜坡发生器310被配置为提供电位斜坡rn。

182.发生器310由电位vbat供电,并且被连接在轨3和5之间,这些连接在图8中未详细示出,以免使该附图过载。发生器310借助信号cmdn由电路300来控制。

183.更具体地,在持续时间ton结束时,当电路300控制将晶体管9置于关断状态并且将晶体管13置于导通状态时,电路300还经由信号cmdn来控制电位斜坡rn的启动。作为示例,信号cmdn基于由电路300向晶体管13提供的控制信号来确定,或者与由电路300向晶体管13提供的控制信号相同。

184.根据一个实施例,每个电位斜坡rn是从电源电位vbat减小的斜坡。

185.根据图8所示的实施例,斜坡rn与电位vref的比较由比较器306来实现。斜坡rn然后被传输至电路308的第二输入。此外,电路300被配置为将信号sel切换到其第二状态,同时控制将晶体管9置于关断状态并且将晶体管13置于导通状态,使得斜坡rn被传输至比较器306。

186.因此,在每个斜坡rn从电位vbat减小的实施例中,只要信号sel保持在其第二状态,信号comp就处于其第二状态(例如,高状态),而电位rn大于电位vref,并且一旦电位变得低于电位vref,信号comp便切换到其第一状态(例如,低状态rn)。

187.信号comp从其第二状态切换到其第一状态标志着持续时间toff的结束。电路300然后控制将晶体管13置于关断状态。优选地,电路300经由信号cmdn来同时控制电位斜坡rn的结束。

188.在未图示的实施例变型中,电位斜坡rp与电位vref的比较由比较器306来执行,并且电位斜坡rn与电位vref的比较使用在电路17中提供的附加比较器来执行。该附加比较器然后在第一输入(例如,非反相输入( ))上接收电位斜坡rn,并且在第二输入(例如,反相输入(

‑

))上接收电位vref,附加比较器的输出向电路300提供电位斜坡rn与电位vref的代表性比较信号。在该变型中,电路308被省略,并且电路300不生成信号sel。本领域的技术人员

能够使得以上提供的图8的转换器4的公开内容适配用于该实施例变型。

189.在未图示的另一实施例变型中,斜坡rp是从电位vbat减小的电位斜坡和/或电位斜坡rn是从电位gnd增大的电位斜坡。本领域技术人员能够使得转换器4适配用于该情况。

190.此外,尽管已公开了其中斜坡rp和rn与电位vref进行比较的示例性实施例,但是本领域技术人员能够实现斜坡rp和rn与电位vout进行比较的情况。

191.在先前公开的实施例和变型中,当在电流il为负的同时,晶体管13被切换到关断状态时,电位v11从值gnd(晶体管13导通)变为值vbat vdiode(晶体管13关断)。在从值gnd过渡到值vbat vdiode期间,电位v11采用或横穿电位vout的值,这可能导致信号sig切换到其第一状态,但是实际上,电流il不处于稳定的零值。例如为了不重新启动新的操作周期,不考虑将信号sig切换到第一状态可以是所期望的。实际上,这可能导致在电流il不具有稳定的零值时(例如,在电流il为负时),开始新的操作周期。此外,当在电流il仍为正的同时,晶体管13被切换到关断状态时,可能发生信号sig到其第一状态的类似切换。

192.根据一个实施例,转换器4被配置为:在从晶体管13切换到关断状态的预定时间延迟持续时间期间,对信号sig的到其第一状态的切换操作滤波。换言之,转换器4被配置为仅在时间延迟持续时间结束之后才考虑信号sig的到其第一状态的切换。例如,该时间延迟持续时间为10ns的量级,例如等于10ns。

193.根据一个示例,电路17(例如,其电路300)被配置为仅在时间延迟持续时间过去之后,才考虑信号sig的切换操作。

194.根据另一示例,转换器4包括未在图4和图8中示出的附加电路,附加电路被配置为基于信号sig来生成滤波信号,滤波信号对应于信号sig,其区别在于在时间延迟持续时间期间没有任何切换。换言之,附加电路例如被配置为:在时间延迟时段之外提供在信号sig的每次切换之后进行切换的滤波信号,并且在整个时间延迟持续时间内维持滤波信号的状态。换言之,除了在滤波信号保持在第二状态的时间延迟持续时间期间之外,每当信号sig从其第一状态切换到其第二状态时,滤波信号从第一状态切换到第二状态,并且每当信号sig从其第二状态切换至其第一状态时,滤波信号从其第二状态切换至其第一状态。电路17然后被配置为根据滤波信号的状态,调节晶体管9的到导通状态的切换。该滤波信号基于信号sig来获得,电路17实际上被配置为基于信号sig而调节到晶体管9的导通状态的切换。

195.本领域的技术人员能够提供其他实施例,例如通过在时间延迟持续时间期间实现信号sig的切换操作的滤波功能,从而可以避免考虑信号sig切换到不表示具有稳定零值的电流il的第一状态。

196.此外,如在先前描述的实施例和变型中类似,当电感15中的电流il被抵消时,节点11的电位v11实际上可以在电位vout的值附近具有振荡。结果,例如只要电位v11不具有与电位vout的值相等的稳定值,信号sig或以上公开的滤波信号也可以具有振荡。

197.根据一个实施例,转换器4被配置为:在时间延迟持续时间之后,存储信号sig或对应滤波信号的第一状态的第一切换。

198.根据一个示例,该存储由电路300来执行,例如直接由电路300的有限状态机来执行。

199.根据另一个示例,转换器4包括未在图4和图8中示出的、被配置为执行该存储的(其他)附加电路。该附加电路例如被配置为:在时间延迟持续时间之后,当信号sig或滤波

信号切换至其第一状态时,提供切换至第一状态的附加信号,然后在预定的持续时间期间,维持附加信号的第一状态,例如至少直到将晶体管9控制到导通状态,或者至少直到将晶体管13切换到导通状态。作为示例,电路17(例如,其电路300)接收该附加信号,并使得晶体管9的切换(新操作周期的开始)服从该附加信号处于其第一状态的事实。附加信号基于信号sig获得,或者滤波信号进而基于信号sig获得,晶体管9到导通状态的切换实际上基于信号sig或换言之由信号sig来调节。

200.本领域技术人员能够提供其他实施例,例如用于在时间延迟持续时间之后,将信号sig或滤波信号到第一状态的第一切换存储的功能的其他实施例,使得当电流il被抵消时,能够考虑信号sig的任何振荡。

201.根据一个实施例,转换器4包括被配置为实现如上所述的滤波功能和存储功能的电路。该电路然后被配置为:基于信号sig,提供在第一状态和第二状态(例如,分别为低和高)之间切换的信号sig’;在控制晶体管13切换到关断状态之后的预定时间延迟持续时间期间,将信号sig’保持在其第二状态;一旦时间延迟持续时间过去,则在信号sig到其第一状态的第一切换发生期间,将信号sig’切换到其第一状态;以及在预定持续时间期间,将信号sig’保持在其第一状态,之后在时间延迟持续时间之后,进行信号sig’到其第一状态的切换,例如同时至少保持信号sig’的该第一状态,直到晶体管9甚至晶体管13在接下来的操作周期内切换到导通状态。

202.在这样的实施例中,电路17然后被配置为使晶体管9到导通状态的切换服从信号sig’的第一状态。因为信号sig’基于信号sig来获得,所以晶体管9到导通状态的切换确实基于信号sig来调节。此外,在这样的实施例中,可以规定电路300在信号sig’和信号start之间接收由逻辑运算(例如,and逻辑)产生的信号start’,使得信号start’为仅当电压vout低于电压vref且信号sig’处于其第一状态时才处于诸如高状态的状态,否则处于另一状态(例如,低状态)。在该情况下,一旦信号start’处于指示电压vout小于vref并且信号sig’处于其第一状态的状态,则电路300开始新的操作周期。

203.图9示出了被配置为生成如上所述的信号sig’的电路90的一个实施例。

204.电路90包括d触发器92。触发器92的数据输入d被耦合、优选地被连接到与信号sig’的第一状态相对应的电位v。触发器92的输出q提供信号sig’。触发器92的同步输入clk被耦合、优选地被连接到电路40的输出41(图4、图5、图6和图8)来接收信号sig。触发器92还包括初始化输入r,初始化输入r被配置为接收初始化信号init。当初始化信号处于非激活状态(例如,低状态)时,每次将信号sig从其第二状态切换到其第一状态时,输入d的电平被复制在输出q上,以及当信号init处于激活状态(例如,高状态)时,触发器92的输出q被强制为与信号sig’的第二状态相对应的电平。

205.作为示例,当晶体管13处于导通状态时,信号init处于激活状态,并且只要晶体管13切换至关断状态之后的时间延迟持续时间未完成,信号init例如就处于非激活状态。因此,当晶体管13导通时,信号init是激活的,并且信号sig’处于其第二状态。此外,当晶体管9关断但时间延迟持续时间未完成时,信号init是激活的并且信号sig’保持在其第二状态。一旦时间延迟完成,当信号sig从其第二状态切换到其第一状态时,触发器92的输出q切换到电位v,结果信号sig’切换到其第一状态,只要信号init保持非激活,信号sig’就保持在其第一状态。

206.基于以上所公开的操作,将理解,信号init可以基于晶体管13的控制信号来获得,该控制信号在电路17的输出177上可用(图4和图8)。例如,信号init对应于向其施加等于时间延迟持续时间的延迟的晶体管13的控制信号。

207.已描述了各种实施例和变型。本领域技术人员将理解,这些实施例的某些特征可以被组合,并且本领域技术人员将容易想到其他变型。

208.最后,基于上文提供的功能描述,本文描述的实施例和变型的实际实现在方式本领域技术人员的能力之内。具体地,本领域的技术人员能够设计(多个)电路,该电路实现应用于信号sig的滤波功能,以考虑在电感中的电流il不具有零值和稳定值时信号sig到其第一状态的任何第一切换,并且该电路实现滤波功能,以考虑当电流il被抵消时信号sig的任何振荡。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。