1.本发明涉及一种配备有改进的行寻址设备的指纹采集系统。它主要应用于图像传感器,例如布置在触摸屏下面的图像传感器,以便通过在屏幕上的任何位置处识别用户的指纹来标识用户。

背景技术:

2.如已知的那样,在已知为tft面板的东西中使用的检测阵列由以行和以列布置的检测单元p(i,j)(也称为像素)形成。图1示出了这样的布置。按照惯例,注意检测单元p(i,j)位于行l(i)和列col(j)上。每个检测单元p(i,j)由光传感器d(i,j)和薄膜晶体管t(i,j)组成,该光传感器(通常是光电二极管)生成与所接收的光能成比例的电荷并将所述电荷存储在其电容器中,该薄膜晶体管的源极连接到电荷检测器d(i,j)。

3.顺序寻址行l(i)需要提供两个分离的电压:用于保持一行的所有晶体管t(i,j)处于截止状态的一个电压voff,以及用于将一行的所有晶体管t(i,j)置于导通状态的一个电压von。晶体管t(i,j)由选择令牌寻址。与低电平(电压voff低于von)相比,选择令牌是预定时间内的高电平信号(电压von),该高电平信号在给定方向上逐行传播,例如从行l(i)到行l(i 1)。

4.在选择令牌在行l(i)中传播时,令牌的高电平命令该行的所有晶体管的导通状态。选择令牌的高电平被配置为具有大于晶体管的阈值电压的值。存储在行的电荷检测器d(i,j)中的每个的电子通过与电荷检测器d(i,j)相关联的列col(j)传输到电荷积分器,该电荷积分器将这个值转换成电压。列col(j)连接到晶体管t(i,j)的漏极。每列中电荷的积分可以由所有列共用的集成电路(也称为读出集成电路或roic)管理。这将所测量的值转换为数字式的,使得能够逐行生成指纹的图像。

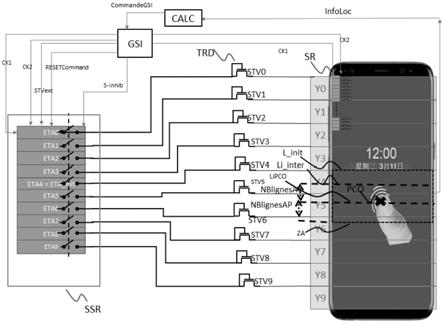

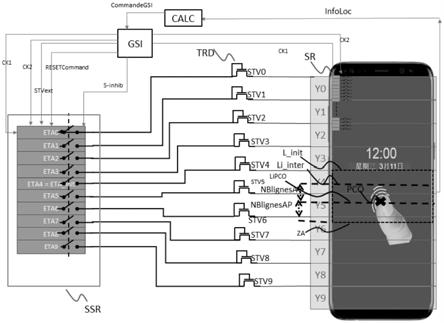

5.选择令牌的逐行传播由行寻址设备或行扫描器(通常称为“行驱动器”或“栅极驱动器”)管理。行控制电路是移位寄存器。专利ep0586398b1描述了用于液晶显示器的移位寄存器的示例。尽管本技术应用于检测阵列而不应用于显示阵列,但是原理是相同的。参考图2,每一级et包括输入端子bini(i=0

…

3)和输出端子bouti(i=0

…

3),该输出端子本身连接到阵列的相应行。可以集成到读出集成电路中的信号发生器gsi生成在相位上彼此相反的两个时钟信号ck1、ck2。每一级eti(i=0

…

3)包括能够接收第一时钟信号ck1的第一时钟端子bck1

‑

i(i=0

…

3)和能够接收第二时钟信号ck2的第二时钟端子bck2

‑

i(i=0

…

3)。脉冲stvext(称为“令牌”)由第一级et0的输入端子bin0接收,并且在第一时钟脉冲,例如第一时钟信号ck1的第一时钟脉冲,令牌由输出端子bout0传输到行l(0),以便读取存储在相对应的行的检测单元中的信息,如上所述。

6.第二级et1的输入端子bin1连接到第一级et0的输出端子bout0。第二时钟信号ck2由第二级et1在第二时钟端子bck2

‑

1接收。令牌因此被传输到第二行l(1)。第一时钟信号ck1和第二时钟信号ck2彼此相位偏移,使得在阵列的读取中没有停滞时间。

7.因此,令牌从一个级传播到另一个级,直到阵列的所有行被读取为止。

8.在不脱离本发明的范围的情况下,可以设想不同于相位相反的两个时钟信号的其他时钟系统。例如,可以设想使用多于两个时钟信号的移位寄存器,或者甚至使用单个时钟信号的移位寄存器。

9.行寻址设备最初布置在阵列的外部,例如通过柔性层连接到阵列。最近已经出现了使用单个n型或p型tft晶体管直接在阵列中实施的行寻址器件。该阵列可以通过在衬底上沉积层来形成,例如非晶硅(a

‑

si)、tft、多晶硅、有机半导体或非晶氧化铟镓锌(ga2o3

‑

in2o3

‑

zno)类型。

10.与外部寻址设备相比,集成到阵列中的这些寻址设备(通常称为goa(阵列上的栅极驱动器))使得可以节省制造成本和占地面积,并使得可以限制连接错误。专利申请fr2975213中描述了goa的一个示例。

11.然而,目前使用的goa在从一个级移动到另一级方面的速度受到极大限制,这与tft技术有关。具体而言,在移位寄存器中从一级移动到另一级需要十到二十微秒之间,而在使用cmos技术的情况下,这种延迟只有一百纳秒,该cmos技术是通常用于外部寻址设备的技术。

12.对于智能手机的触摸屏或任何其他等效设备上的指纹识别应用,阵列的行数大约等于2000,这个数量显然能够因设备而不同。因此,如果手指被放置在屏幕的底部处,选择令牌在移位寄存器的所有级中传播大约需要40毫秒。用于指纹识别方法的执行时间也可以乘以合并数据所需的许多重读操作,通常在3到6次之间。将指纹与被授权的指纹进行比较所需的时间进一步增加了这些延迟。

13.因此,指纹识别方法必须快速执行,特别是在不到200毫秒的时间内,这是根据经验确立的延迟,超过该延迟会让用户检测到时延时间,并因此产生等待的感觉。

14.因此,本发明旨在提供一种goa行寻址设备,其使得可以在阵列的期望位置开始扫描行,同时添加尽可能少的新控制信号。

技术实现要素:

15.因此,本发明的一个主题是一种指纹采集系统,该指纹采集系统包括触摸表面,该触摸表面被配置为提供具有与触摸表面接触的指纹的手指的至少一个接触点的位置信息,其特征在于,该系统包括:

16.‑

tft面板,该tft面板布置在触摸表面下方并包括检测阵列,该检测阵列包括m行,该m行中的至少一些包括用于检测表示指纹的图像的检测单元,行寻址系统被集成到阵列中并且被配置为在行的扫描方向上一行接一行地激活相对应的行的检测单元,

17.‑

计算设备,该计算设备被配置为接收位置信息,并且命令寻址系统从地址范围开始对阵列进行寻址,该地址范围将来自阵列的m行当中的行的子集分组在一起,并且基于位置信息确定。

18.有利的是,寻址系统包括:移位寄存器,该移位寄存器包括m级,m级中的每个具有连接到相对应的行输入的输出;以及附加移位寄存器,该附加移位寄存器包括称为附加级的n级,其中n<m,附加移位寄存器通过移位寄存器连接到行输入,每个附加级连接到移位寄存器的一组级中的第一级。

19.有利的是,计算设备被配置为在行的扫描方向上确定对应于地址范围的开始的称

为初始行的行,并且确定称为初始附加级的附加级,该初始附加级能够激活初始行的检测单元。

20.有利的是,该系统包括信号发生器,该信号发生器被配置为向移位寄存器和附加移位寄存器提供在相位上彼此相反的第一时钟信号和第二时钟信号。

21.有利的是,每个附加级包括:

22.‑

输入端子,该输入端子被配置为接收被称为令牌的高电平信号,

23.‑

第一晶体管,该第一晶体管的栅极直接或间接地连接到输入端子,并且该第一晶体管的漏极被配置为从第一时钟信号或第二时钟信号当中接收时钟信号,

24.‑

中间节点,该中间节点连接到第一晶体管的源极,该中间节点连接到下一个附加级的输入端子,

25.‑

禁止电路,该禁止电路用于连接到附加级的级、由信号发生器提供的第一禁止信号控制,该禁止电路被配置为使得只要第一禁止信号处于低电平,令牌就在每个时钟脉冲被传输到下一个附加级,并且当第一禁止信号处于高电平时,令牌被传输到连接到附加级的级。

26.有利的是,信号发生器被配置为使得当由计算设备确定的初始附加级的输入端子接收到令牌时,第一禁止信号具有高电平。

27.有利的是,禁止电路包括:

28.‑

第二晶体管,该第二晶体管的栅极直接或间接地连接到中间节点,并且该第二晶体管的漏极能够接收禁止信号,

29.‑

输出端子,该输出端子连接到第二晶体管的源极和移位寄存器的级。

30.有利的是,信号发生器被配置为向禁止电路提供第二禁止信号,第二禁止信号在第一禁止信号变为低电平之后立即具有高电平,并且其中输出端子连接到第三晶体管的漏极,该第三晶体管的栅极能够接收第二禁止信号。

31.有利的是,附加移位寄存器的附加级连接到移位寄存器的级,在移位寄存器的级之间具有规则的间隔。

32.有利的是,每个附加级通过二极管连接式晶体管连接到级。

附图说明

33.附图示出了本发明:

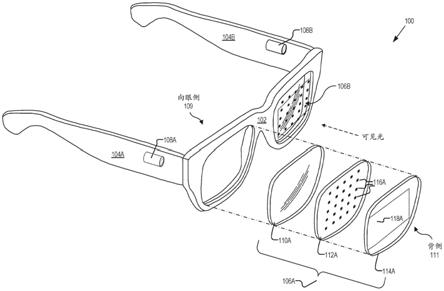

34.[图1]已经描述的图1示出了根据现有技术的检测单元的呈行和列的形式的布置。

[0035]

[图2]已经描述的图2示意性地示出了根据现有技术的移位寄存器。

[0036]

[图3]图3示意性地示出了根据本发明的指纹采集系统。

[0037]

[图4]图4示出了根据本发明的附加移位寄存器的电路图。

[0038]

[图5]图5示出了示出根据本发明的行寻址设备的操作的时序图。

具体实施方式

[0039]

图3示意性示出了根据本发明的指纹采集系统。指纹识别在图3中由智能手机型电话表示的装置上执行,例如为了解锁电话,或者另外地为了确保应用的使用,例如支付。本发明不限于电话上的指纹识别,并且可以在任何类型的电子设备上实施。

[0040]

采集系统包括未示出的触摸表面。电子装置还可以结合触摸表面并入显示功能,然后其组件形成触摸屏。

[0041]

当用户的手指接触到装置的表面上时,布置在电子装置中的计算设备calc检测手指在触摸表面上的接触点pco。检测可以以各种方式进行,例如使用电阻性或电容性技术。在任何情况下,接触点pco对应于触摸表面的平面中的点的坐标。在产生几个有效接触点的扩展接触的情况下,计算设备calc可以认为要用于处理的剩余部分的接触点对应于有效接触点中的一个(例如,上点或下点),或者对应于其坐标对应于有效接触点的坐标平均值的名义接触点。

[0042]

如上所述的检测阵列被布置在触摸表面下方,并且被集成到tft面板中。检测阵列包括m行。行中的至少一些包括检测单元。所有行由集成到阵列中的寻址设备驱动。寻址设备包括移位寄存器sr,该移位寄存器包括m级。每一级连接到阵列的行。这样的级例如在文件fr2975213的图3中示出。

[0043]

根据本发明并在图3中示出的系统允许移位寄存器sr从对应于应该检测指纹的区域的阵列的预定行开始在阵列中传输令牌以及通常使用的时钟信号ck1和ck2。因此,通过避免激活信号在某些移位寄存器sr中的传播,获得了时间节省。

[0044]

为此,根据本发明的系统使用也集成到阵列中的附加移位寄存器ssr。附加移位寄存器ssr包括n个附加级eta,其中n<m。有利的是,比率m/n可以等于20。因此,对于两千行的阵列,并且因此对于两千级的移位寄存器,附加移位寄存器ssr可以包括一百个附加级。在本发明的一个特别有利的实施例中,比率m/n可以等于200。因此,对于两千行的阵列,并且因此对于两千级的移位寄存器,附加移位寄存器ssr可以包括十个附加级。因此,附加移位寄存器ssr的占用空间很小;它可以位于例如阵列的角部。它可以特别地位于靠近输入/输出垫。

[0045]

有利的是,附加移位寄存器ssr的附加级eta连接到移位寄存器sr的级et,在移位寄存器sr的级et之间具有规则的间隔。因此,每个附加级eta将相同数量的级et分组在一起,从而使得更容易实施附加移位寄存器。在前面提及的示例中,间距对应于比率m/n(200)。

[0046]

作为变型,级之间的间隔可以是不规则的;例如,与上部部分和下部部分相比,附加级eta可以在检测器的中心处将更少的级et分组在一起。

[0047]

计算设备calc可以是专用电路(例如asic(“专用集成电路”)或fpga(“现场可编程门阵列”)电路)、或者适当编程的处理器。在最后一种情况下,计算设备可以是也执行其他功能的中央器。计算设备calc从触摸表面接收呈触摸表面的平面中的点的坐标的形式的位置信息infoloc。由计算设备calc基于位置信息infoloc定义要分析用户的指纹的地址范围za。具体而言,在指纹识别程序期间由手指占据的表面的最大尺寸在指纹传感器的领域是已知的。

[0048]

典型地,对于具有500dpi(“每英寸的点”)的分辨率的检测器,在知道拇指纹沿着对应于手指的长度的维度可以被测量超过大约15毫米的情况下,采集300行上的指纹的图像就足够了。

[0049]

计算设备calc因此确定阵列的哪一行对应于接触点pco,并且确定在阵列的行的扫描方向上位于接触点pco之前的150行和在行的扫描方向上位于接触点pco之后的150行。

[0050]

确定对应于触摸表面的接触点pco的阵列的行可以使用所谓的对准程序,这与这样的事实相关,即,阵列的分辨率(两个连续像素之间的间隔)res1和触摸表面的分辨率(两个连续检测元件之间的间隔)res2可能不同。

[0051]

手指在触摸表面的xy平面中的按压位于横轴上的(x*res2)处和纵轴上的(y*res2)处,取(0,0)作为触摸表面的角部,例如触摸表面的左上角。

[0052]

tft阵列上相对于角部(例如左上角)中的像素(0,0)的相对应的点位于:

[0053]

xtft=(x*res2)/res1 deltax/res1

[0054]

以及ytft=(y*res2)/res1 deltay/res1

[0055]

其中deltax和deltay是在工厂测量的tft阵列的(0,0)相对于触摸表面的(0,0)的偏移。

[0056]

因此,对应于接触点pco的阵列lipco的行是从“ytft”和“y”之间的关系导出的。

[0057]

当然,计算设备calc可以定义具有不同的接触点pco之前和之后的行数(例如在接触点pco之前200行和之后200行)的处理范围。

[0058]

nblignesav被定义为需要考虑的接触点pco之前的行数,并且nblignesap被定义为接触点pco之后需要考虑的行数,以便考虑指纹的正常尺寸。

[0059]

例如,nblignesav=nblignesap=150。

[0060]

中间行li_inter的名称被赋予该行,使得:#ligne_inter=#lipco

–

nblignesav,其中#ligne_inter表示中间行的编号,并且#lipco表示对应于接触点pco的阵列lipco的行的编号。

[0061]

按照惯例,初始行l_init是给(通过移位寄存器sr的级et)连接到在阵列的行的扫描方向上包括中间行li_inter的该组行的附加级eta的行的名称。

[0062]

按照惯例,“初始附加级(eta_init)”是赋予能够激活初始行(l_init)的检测单元(p(i,j))的附加级的名称。每个附加级eta连接到移位寄存器sr的第一组级et。在前面提及的示例中,每个附加级eta将200个级et分组在一起,并且因此把200行分组在一起,并且考虑到第一附加级是接收初始脉冲stvext的级,初始附加级对应于第五附加级。在图3中,块y0至y9示出了将各行的分组在一起。

[0063]

根据本发明的系统使得可以从阵列的m行中寻址行的子集。该子集至少包括基于位置信息infoloc确定的地址范围za。

[0064]

计算设备calc命令信号发生器gsi,使得所述信号发生器生成所请求的时钟信号的数量。计算设备calc通过传输命令信号“commandegsi”与信号发生器gsi通信。信号发生器gsi可以包括耦合到电平转换器的专用电路,例如fpga电路。fpga接收由计算设备calc传输的命令信号commandegsi。fpga在低电压(例如0到3.3v)下生成逻辑信号。电平转换器确保fpga的低电压和阵列的高电压(von,voff)兼容。

[0065]

对于阵列上的每个新的读取操作,计算设备calc命令信号发生器gsi生成新的脉冲stvext。计算设备calc确定从生成脉冲stvext的时间开始,必须生成第一时钟信号ck1和第二时钟信号ck2的多少个上升沿。

[0066]

计算设备基于地址范围za的第一行的位置,并且更具体地说,基于地址范围za的第一行位于的该组级et的第一级et的位置,确定上升沿的数量。

[0067]

信号发生器gsi生成信号s

‑

inhib,称为第一禁止信号。仅在初始附加级etainit连

接到的时钟信号在令牌在初始附加级etainit中传播时具有高电平时,第一禁止信号s

‑

inhib才具有高电平。由计算设备calc验证了这个条件。然后,第一禁止信号s

‑

inhib在时钟信号的下降沿变回低电平。

[0068]

在由图3示出的示例中,地址范围za从行800开始,该行连接到附加移位寄存器ssr的附加级中的一个,在这种情况下是第五附加级(eta4)。阵列从行800开始寻址。因此,计算设备calc认为第五附加级eta4是初始附加级etainit。假设第一附加级eta0被第一时钟脉冲ck1激活,第二附加级eta1将被第二时钟脉冲ck2激活,以此类推。第五附加级eta4由对应于第五上升沿ck1/ck2的第一时钟脉冲ck1激活。然后,计算设备calc将第一禁止信号s

‑

inhib递送到附加移位寄存器。

[0069]

信号发生器gsi随后生成第二禁止信号resetcommand,该第二禁止信号在第一禁止信号s

‑

inhib变为低电平之后立即具有高电平。第二禁止信号resetcommand使得可以禁止令牌在附加移位寄存器中传播。因此,它从连接到初始附加级etainit的级开始仅在移位寄存器中传播。

[0070]

每个附加级接收第一时钟信号ck1、第二信号ck2、第一禁止信号s

‑

inhib和第二禁止信号resetcommand。初始脉冲stvext仅传输到第一附加级eta0。

[0071]

有利的是,每个附加级eta通过二极管连接式晶体管trd(也就是说其栅极连接到其漏极)连接到级et。因此,当施加第二禁止信号resetcommand时,二极管连接式晶体管trd使得截图在移位寄存器sr中引导令牌,同时隔离传输令牌的初始附加级eta_init。具体而言,二极管连接式晶体管trd仅引导正电压von;当初始附加级eta_init被重置为voff时,接收令牌的移位寄存器sr的行将其状态保持处于von。

[0072]

在图3中,形成本发明的一些元件被示出在要识别指纹的电子装置的外部。这种描述是示意性的;特别是,附加移位寄存器ssr被集成到goa中;计算设备calc和信号发生器gsi可以布置在连接到goa的电路中。

[0073]

附加移位寄存器的每个附加级eta的电路图在图4中示出。

[0074]

附加级被分解成传播电路cpr和禁止电路cin。传播电路cpr具有类似于文献fr2975213的图3中示出的级的结构,并且以类似的方式操作。

[0075]

输出信号out_n具有电平n的附加级eta的传播电路cpr的输出。传播电路cpr在输入处接收输入信号out_n

‑

1,并提供输出信号out_n。

[0076]

在行寻址设备领域,输入信号的脉冲通常被称为令牌,并且在输入端子be处被接收。在根据本发明的系统中,令牌从附加级传播到附加级,直到初始附加级eta_init,其中令牌然后可以从连接到初始附加级eta_init的寄存器开始在阵列中传播。令牌由前一附加级的输出信号传输。对于第一附加级,令牌可以由信号发生器gsi(信号stvext)生成。

[0077]

当第一晶体管tr1处于导通状态时,其传输时钟信号ck1(或对于奇数附加级为ck2)的脉冲。因此,它的漏极连接到信号发生器gsi。升压电容器cb1连接在第一晶体管tr1的栅极和源极之间。这种电容器负责“自举”效应,该“自举”效应使得可以当第一晶体管tr1从弱导通变为完全导通时以2xvon的电压引导漏极/源极电压。

[0078]

预充电晶体管tr4使得可以对第一晶体管tr1的栅极预充电。预充电晶体管tr4的源极因此连接到第一晶体管tr1的栅极。控制晶体管tr5使得可以使第一晶体管tr1的栅极放电。控制晶体管tr5的漏极因此连接到第一晶体管tr1的栅极。控制晶体管tr5由具有电平

n 1的下一个附加级的输出信号out_n 1命令。因此,控制晶体管tr5的栅极连接到具有电平n 1的下一个附加级的输出信号out_n 1。最后一个附加级的控制晶体管tr5的栅极可以由特定信号命令。特别地,特定信号可以是第二禁止信号resetcommand。然后,控制晶体管tr5的源极被偏置到电压voff。

[0079]

放电晶体管tr6可以连接到具有电平n的附加级的输出out_n。当令牌已经被传输到该行时,它使得更容易使输出out_n放电。放电晶体管tr6的栅极连接到控制晶体管tr5的栅极。然而,由于附加级的相对较少的数量(大约十的量级),放电晶体管tr6存在并不是必需的。具体而言,放电晶体管tr6将第一晶体管tr1的源极处的电压重置为零,以防止不希望的令牌的出现。但是,在具有非常少的数量的附加级的情况下,不希望的令牌的出现不太可能。

[0080]

补偿电容器c3可以布置在第二时钟信号ck2和预充电晶体管tr4的源极之间。这使得可以在施加到第一晶体管tr1的漏极的第一时钟信号ck1的切换期间补偿第一晶体管tr1的栅极和漏极之间的杂散电容的影响。然而,由于相对较少数量的附加级(大约十的量级),它的存在并不是必需的,并且因此杂散干扰的积累比在移位寄存器的传统级中具有少得多的破坏性。具体而言,在包括一千级的量级的移位寄存器中,在没有补偿电容器的情况下,杂散干扰将在阵列的末端乘以这许多级,并且这是不可接受的。

[0081]

中间节点ni布置在传播电路cpr的输出处。输出信号out_n可以在中间节点ni处被提取。中间节点ni连接到下一个附加级的输入端子。

[0082]

连接到附加级eta的级et的禁止电路cin允许附加级禁止连接到附加级eta的级et并且因此将令牌传输到下一个附加级,或者将令牌传输到阵列,使得单元被寻址。为此,禁止电路cin接收输出信号out_n和由计算设备calc提供的第一禁止信号s

‑

inhib。当令牌位于初始附加级eta_init时,计算设备calc传输禁止信号s

‑

inhib的脉冲。如图3所示,计算设备calc命令时钟信号ck1和ck2的生成。因此,它能够确定应该在禁止信号s

‑

inhib中生成上升沿的时间。

[0083]

禁止电路cin包括第二晶体管tr2,该第二晶体管的栅极连接到中间节点ni,并且该第二晶体管的漏极能够接收禁止信号s

‑

inhib。有利的是,二极管连接式预充电晶体管tr7布置在中间节点和第二晶体管tr2的栅极之间。预充电晶体管tr7使得可以对第二晶体管tr2的栅极预充电。

[0084]

输出端子bs连接到第二晶体管tr2的源极和移位寄存器sr的相对应的级et。当由中间节点ni传输的令牌被传输到输出端子时,在输出端子bs处生成验证信号stvn的上升沿。

[0085]

有利的是,第二升压电容器cb2连接在第二晶体管tr2的栅极和源极之间。这种电容器负责“自举”效应,该“自举”效应使得可以当第二晶体管tr2从弱导通变为完全导通时以2xvon的电压引导漏极/源极电压。

[0086]

第二放电晶体管tr8可以连接到具有电平n的附加级的输出端子bs。这使得更容易使第二晶体管tr2放电。它由下一个附加级的输出信号out_n 1命令。最后一个附加级的放电晶体管tr8的栅极可以由第二禁止信号resetcommand命令。

[0087]

禁止电路cin还包括第三晶体管tr3。第三晶体管tr3由信号发生器gsi提供的第二禁止信号resetcommand命令。第二禁止信号resetcommand在第一禁止信号s

‑

inhib变为低

电平后立即具有高电平。输出端子bs连接到第三晶体管tr3的漏极。因此,一旦初始附加级eta_init的验证信号已经被传输到初始附加级eta_init连接到的移位寄存器sr的级,第二禁止信号resetcommand就将验证信号stvn保持处于voff,在阵列的整个读取时间内这样做。

[0088]

图5示出了示出根据本发明的行寻址设备的操作的时序图。在由图5示出的图中,可以认为计算设备calc已经通过触摸表面传输的位置信息infoloc检测到第四附加寄存器可以发送激活信号stv3。例如,对于两千行的阵列,这可以对应于在行600和800之间开始的地址范围,其中移位寄存器sr的二十级附接到附加移位寄存器ssr的每个附加级。

[0089]

在第一附加级eta0的输入端子be处提供脉冲stvext。同时,第一时钟信号ck1具有高电平(处于von的电压);因此,输出信号out0具有高电平。由于第一禁止信号s

‑

inhib处于低电平(处于voff的电压),令牌被传输到第二附加级eta1。第二时钟信号ck2具有高电平;因此,输出信号out1具有高电平。由于第一禁止信号s

‑

inhib仍然处于低电平,令牌被传输到第三附加级eta2。第一时钟信号ck1具有高电平;因此,输出信号out2具有高电平。由于第一禁止信号s

‑

inhib仍然处于低电平,令牌被传输到第四附加级eta3。

[0090]

计算设备已经将第四附加级eta3标识为初始附加级eta_init。因此,当令牌在第四附加级eta3中传播时,第一禁止信号s

‑

inhib具有高电平。输出out3具有高电平,并且由于第一禁止信号s

‑

inhib也具有高电平,激活信号stv3变为von。然后,令牌可以被传输到连接到第四附加级eta3的移位寄存器sr的级et。可以从与该级相关联的行开始寻址该阵列。因此,在这个示例中,在四个时钟脉冲中,阵列从行600开始被寻址。此外,时钟信号是用于移位寄存器的信号,并且因此不需要提供附加时钟发生器。

[0091]

一旦第一禁止信号s

‑

inhib返回到低电平,计算设备calc就将第二禁止信号resetcommand设置为电压von。因此,第三晶体管tr3切换到导通状态,并且下一个附加级被禁止,直到阵列上的最后一个读取操作。

[0092]

在一个实施例中,阵列可以被寻址直到阵列的最后一行。计算设备calc具有与阵列的行的总数相关的信息;因此,当到达阵列的最后一行时,计算设备calc命令信号发生器gsi停止向移位寄存器sr传输时钟信号。

[0093]

作为替代性方案,计算设备calc可以基于位置信息infoloc命令停止阵列的读取。具体而言,基于位置信息infoloc,计算设备calc能够确定地址范围za的最后一行。当到达地址范围za的最后一行时,计算设备calc命令信号发生器gsi停止向移位寄存器sr发送时钟信号。

[0094]

回到由图3示出的示例,如果例如地址范围za的末端处的行对应于行号1240,则计算设备calc命令信号发生器gsi生成五个时钟脉冲,使得令牌在附加移位寄存器ssr中传播,并且然后生成四百个时钟脉冲,使得令牌在组y4和y5中传播,并且最后生成四十个时钟脉冲,使得令牌在行号1200至1240中传播。计算设备calc因此命令信号发生器gsi在445个时钟脉冲之后停止生成时钟信号。

[0095]

根据本发明的系统特别良好地适合于具有包括几千行的大阵列的探测器。

[0096]

根据本发明的系统使得可以具有窗口功能,这是特定于检测器的功能。在tft面板显示器中,这个功能不是特别需要的。

[0097]

添加这个功能而几乎没有成本,具体来说,仅通过向集成到tft面板中的栅极驱动

器添加两个命令和能够根据预期的应用进行适配小的附加移位寄存器。当利用仅包括十个附加级的附加移位寄存器寻址阵列时,可以实现显著的时间节省。

[0098]

而且,由于附加移位寄存器的较小的大小,如果附加移位寄存器能够集成在阵列的空闲位置,则阵列的面积略微增加,或者甚至完全不增加。现在,在制造阵列的清洁室中,故障的数量与阵列的大小成正比,因为能够生成故障的尘埃粒子的数量与阵列的大小成正比。阵列的效率随着阵列的大小增加而降低。因此,根据本发明的系统几乎不影响阵列的效率(如果起作用的话)。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。