1.本发明涉及电力用半导体元件的驱动电路。

背景技术:

2.逆变器等用于对电动机进行驱动的电力变换器通过电力用半导体元件即开关元件的通断而进行电力变换。关于开关元件的驱动,即使维持相同的驱动电路状态,通断状态也会根据通断时的电流值等而变化,因此需要进行具有余量的设计。为了解决该问题,实现低损耗、低噪声化,需要通过驱动电路对在通断时产生的损耗与噪声的产生或尖峰电压之间的折衷关系进行控制。为了实现折衷的改善,需要对通断时的栅极电流进行控制,在通断状态,例如通断时的电流值产生了变化时,与开关元件的传输特性对应地对栅极电压波形进行控制,对栅极电流的变化进行控制。

3.专利文献1:日本特开2013

‑

229654号公报

技术实现要素:

4.为了切换栅极电阻或电源以对栅极电流进行控制,需要用于调整定时(timing)的多个信号及开关,控制电路变得复杂。在专利文献1中,在通断最初,以将栅极电压切换为阈值电压或所设定的一定电压的方式进行控制。但是,在元件温度或通断时的电流值产生变化时,该元件的特性产生变化,应该设定的栅极电压的大小产生变化,因此对于缩短通断时的延迟时间存在极限。另外,与断开时的延迟时间相应地,需要用于防止短路产生的死区时间,需要在死区时间以内可靠地将开关元件断开。另外,在接通时产生了过电流时,限制了栅极电压的上升时间,开关元件长期间地在有源区域进行动作,因此开关元件的损耗变大,为了防止过度的温度上升,需要大的散热鳍片等。

5.本发明公开了用于解决上述问题的技术,其目的在于提供相对于开关元件的电流值或温度的变化,不进行复杂的控制,通断损耗或噪声的变化少的电力用半导体元件的驱动电路。

6.本发明所公开的电力用半导体元件的驱动电路具有栅极驱动电压生成器,该栅极驱动电压生成器基于输入至输入端子的接通、断开的驱动定时信号,产生向开关元件的栅极电极施加的栅极驱动电压,该开关元件具有用于对在第一主电极和第二主电极之间流动的主电流进行控制的所述栅极电极,所述栅极驱动电压生成器具有栅极电流限制电路,该栅极电流限制电路构成为,并联连接有电流限制器和电压限制器,该电流限制器对电流进行限制,该电压限制器对向该电流限制器的两端施加的电压的大小进行限制。

7.发明的效果

8.根据本发明所公开的电力用半导体元件的驱动电路,能够实现相对于开关元件的电流值或温度的变化,不进行复杂的控制,通断损耗或噪声的变化少的电力用半导体元件的驱动电路。

附图说明

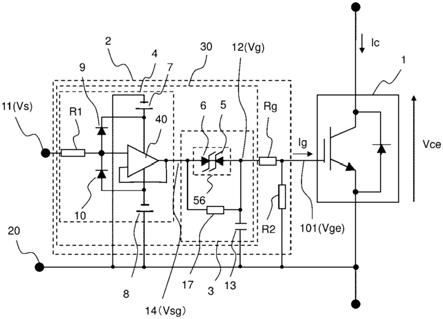

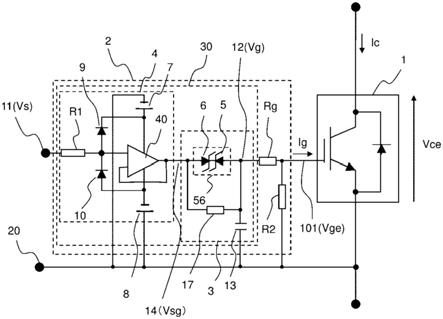

9.图1是表示实施方式1涉及的电力用半导体元件的驱动电路的结构的电路图。

10.图2是表示实施方式1涉及的电力用半导体元件的驱动电路的电压限制器的其它例子的电路图。

11.图3是用于说明实施方式1涉及的电力用半导体元件的驱动电路的动作的曲线图。

12.图4是表示igbt的温度特性例的曲线图。

13.图5是表示齐纳二极管的击穿电压的温度系数的例子的曲线图。

14.图6是表示实施方式2涉及的电力用半导体元件的驱动电路的结构的电路图。

15.图7是表示实施方式3涉及的电力用半导体元件的驱动电路的结构的电路图。

16.图8是表示实施方式4涉及的电力用半导体元件的驱动电路的结构的电路图。

17.图9是用于说明实施方式4涉及的电力用半导体元件的驱动电路的动作的曲线图。

18.图10是表示实施方式5涉及的电力用半导体元件的驱动电路的结构的电路图。

19.在图11中,图11a及图11b是说明电流源的例子的图,该电流源是实施方式4、5、6涉及的电力用半导体元件的驱动电路的栅极电压校正器。

20.图12是用于说明实施方式5涉及的电力用半导体元件的驱动电路的动作的第一曲线图。

21.图13是用于说明实施方式5涉及的电力用半导体元件的驱动电路的动作的第二曲线图。

22.图14是用于说明实施方式5涉及的电力用半导体元件的驱动电路的动作的第三曲线图。

23.图15是用于说明实施方式6涉及的电力用半导体元件的驱动电路的动作的曲线图。

24.图16是用于说明由实施方式6涉及的电力用半导体元件的驱动电路的动作带来的效果的曲线图。

具体实施方式

25.实施方式1.

26.图1是表示实施方式1涉及的电力用半导体元件的驱动电路的电路图。在本发明中,作为电力用半导体元件,以开关元件1是igbt的情况为例而进行说明。在igbt的情况下,作为第一主电极具有集电极(collector)电极(electrode)(也简称为集电极),作为第二主电极具有发射极电极(也简称为发射极),通过施加于栅极电极的电压而对在集电极和发射极之间流动的电流进行控制。作为开关元件,不限于igbt,本发明所公开的技术也能够应用于mosfet等通过施加于栅极电极的电压而对在两个主电极、即第一主电极和第二主电极之间流动的电流进行控制的结构的其它开关元件。

27.就本实施方式1涉及的电力用半导体元件的驱动电路2而言,为了使开关元件1进行通断,与从输入端子11输入的驱动定时信号对应地使栅极电极的电荷充放电,对栅极端子101的电压vge进行控制。驱动电路2的栅极驱动电压生成器30具有栅极电流限制电路3及驱动电压振幅限制电路4。驱动电压振幅限制电路4具有:第一控制电源7;第二控制电源8;二极管9及二极管10,它们用于将输入信号的振幅限制在第一控制电源7及第二控制电源8

的振幅内;电阻r1,其对输入电流进行限制;以及缓冲电路40,其接收驱动定时信号vs而将信号放大。另外,驱动电路2在输出侧具有栅极电阻rg及放电电阻r2。栅极电流限制电路3配置于驱动电压振幅限制电路4和开关元件1的栅极端子101之间,该栅极电流限制电路3具有:电流限制器17,其用于对栅极电流进行限制;电压限制器56,其与电流限制器17并联连接;以及电容器(后面称为栅极电容调整器)13,其用于对电流限制器17和电压限制器56这两者的输出进行接收而对开关元件1的栅极电流进行调整。这里,电流限制器17为电阻。

28.向输入端子11与电位和第二主电极即发射极电极的电位相同的发射极端子20之间输入驱动定时信号vs,通过驱动电压振幅限制电路4,变换为第一控制电源7及第二控制电源8的电压的振幅后的电压vsg被从驱动电压振幅限制电路4输出。这里,在驱动电压振幅限制电路4中,由于具有二极管9、二极管10及在输入侧具有电阻r1,因此在输入至输入端子11的驱动定时信号vs的振幅比第一控制电源7及第二控制电源8大的情况下,输入至缓冲电路40的电压的大小也得到限制,缓冲电路40得到保护。作为缓冲电路40能够使用运算放大器等放大器、或者使用了晶体管的放大电路等。

29.电压限制器56由串联连接体构成,该串联连接体是将齐纳二极管5和齐纳二极管6这两个齐纳二极管以极性的朝向相反的方式串联连接,以对施加于电流限制器17两端的电压的范围进行限制。栅极驱动电压生成器30的输出经由栅极电阻rg而连接于栅极端子101。在栅极电极和发射极电极之间连接有放电电阻r2。

30.电流限制器17通过对电流进行限制,从而对电流限制器17和电压限制器56的连接点12,即栅极驱动电压生成器30的输出的电位vg的变化量进行限制。另外,电压限制器56对由电流限制器17实施电流的限制的电压范围进行限制。在本实施方式1中,作为电压限制器56而将两个齐纳二极管5及齐纳二极管6以极性的朝向相反的方式串联连接。通过该结构,在栅极电流限制电路3的输入侧和输出侧之间产生了大于或等于齐纳二极管5及齐纳二极管6的击穿电压的电位差的情况下,通过电压限制器56急剧地对栅极电容调整器13进行充电。在本实施方式1中,将电流从栅极电流限制电路3的输入侧流向输出侧时的击穿电压,即齐纳二极管5的击穿电压设为vz_5,将电流从栅极电流限制电路3的输出侧流向输入侧时的击穿电压,即齐纳二极管6的击穿电压设为vz_6。

31.在本实施方式1中,作为电压限制器56,通过将齐纳二极管5和齐纳二极管6以极性的朝向相反的方式串联连接,从而设为不管电流的朝向是哪个朝向均能够对电压进行限制的结构。如图2所示,将两个串联连接体朝向相反地并联连接后的电路设为电压限制器56,也会实现如下效果,即,不管电流的朝向是哪个朝向均能够对电压进行限制,该串联连接体是将齐纳二极管和二极管以极性的朝向相反的方式串联连接而得到的。但是,图1所示的将两个齐纳二极管以极性的朝向相反的方式串联连接的结构是简单的结构。另外,如后面叙述的那样,优选电压限制器56配置于与开关元件1相同的模块内,或以成为与开关元件1等同的温度的方式配置于相同的基板内,因此图1所示的电压限制器的结构为有效的结构。

32.在图1所示的电路中,为了对栅极电流的大小进行限制而连接有栅极电容调整器13和栅极电阻rg,但这两者不是必要的,也可以不具有任合一者。而且,在能够利用开关元件1的芯片之上或元件内的常数的情况下,也可以不具有这两者。

33.图3是用于对图1所示的电路的动作进行说明的表示各部分的电压、电流随时间的变化的曲线图。在最上层的曲线图中,将开关元件1的发射极端子20的电位设为0,而分别由

单点划线表示驱动电压振幅限制电路4的输出点14、即栅极电流限制电路3的输入侧的电位vsg,实线表示栅极驱动电压生成器30的输出的电位vg,虚线表示开关元件1的栅极电极

‑

发射极电极间的电压、即栅极电压vge。第2层示出在开关元件1的第一主电极即集电极和第二主电极即发射极间流动的电流、即集电极电流ic,第3层示出开关元件1的集电极

‑

发射极间的电压vce,第4层示出开关元件1的栅极电流ig。

34.在作为驱动定时信号将on信号输入至输入端子11时,如单点划线所示,向栅极电流限制电路3的输入侧即驱动电压振幅限制电路4的输出点14输出与第一控制电源7的电压对应的电位vsg。将从第一控制电源7的电压即驱动定时信号为on时的栅极电流限制电路3的输入侧的电位的值减去齐纳二极管5的击穿电压vz_5而得到的值设为第一阈值电压vgmin,以使得该vgmin成为开关元件1的阈值电压(threshold voltage)vth的方式对vz_5的值进行设定。通过该设定,在驱动定时信号上升时,如实线所示,通过齐纳二极管5及齐纳二极管6,栅极驱动电压生成器30的输出的电位vg上升至不超过开关元件1的阈值电压vth的电位。即,如果栅极驱动电压生成器30的输出的电位vg成为第一阈值电压vgmin,则栅极电流限制电路3的输入侧和输出侧之间的电位差小于或等于通过齐纳二极管5设定的电压vz_5,因此电压限制器56的齐纳二极管5及齐纳二极管6断开,栅极电容调整器13通过电流限制器17被充电。此时,栅极驱动电压生成器30的输出的电位vg的变化受限于由电阻构成的电流限制器17和栅极电容调整器13的时间常数。如果栅极驱动电压生成器30的输出的电位vg产生延迟,栅极电压vge变得大于或等于vth,则开关元件1开始变为on,与栅极电压vge的上升相伴地增加所传输的电流ic,如果ic达到所需要的电流值,则开关元件1转变至米勒期间。如上所述,在驱动定时信号为接通信号时、即接通时,在栅极驱动电压生成器30的输出电压vg小于或等于第一阈值电压vgmin的情况下电流不流过电流限制器17,电压限制器56对电流限制器17两端的电压进行限制,以使得变成大于或等于第一阈值电压vgmin而通过电流限制器17对电流进行限制。由此,在驱动定时信号为接通信号时,电压限制器56使栅极驱动电压生成器30的输出电压vg上升至第一阈值电压vgmin,在vg上升至第一阈值电压vgmin后,通过流过电流限制器17的电流,从而使vg上升。

35.米勒期间是开关元件1的vce产生变化的期间,其变化率dvce/dt依赖于米勒期间的栅极电流(后面称为米勒电流)的大小。米勒期间中的栅极电压(后面称为米勒电压vm)是恒定的,就vm而言,按照开关元件的传输特性,vm的值根据通断时的电流ic的大小及元件的温度而产生变化。但是,由于栅极驱动电压生成器30的输出的电位vg的变化率dvg/dt被电流限制器17限制,因此即使通断电流或元件温度产生变化,米勒电压vm与栅极驱动电压生成器30的输出的电压vg之间的电压差的变化率也不会变化。因此,即使vm产生变化,米勒期间的栅极电流的大小也不会变化,因此开关元件1的集电极

‑

发射极间电压vce被控制为成为恒定的电压变化率。

36.以上,说明了第一阈值电压vgmin与开关元件1的阈值电压vth相等,但第一阈值电压vgmin并非必须与阈值电压vth相等,设定为大于或等于阈值电压vth即可。或者,即使将第一阈值电压vgmin设定得比阈值电压vth低也能够进行动作,但上升的延迟时间变大。因此,为了降低通断的延迟,优选将第一阈值电压vgmin设定为大于或等于阈值电压vth的电压值。另一方面,在将第一阈值电压vgmin设定得比阈值电压vth低的情况下,能够将通断电流刚开始流动之后的电流的变化率di/dt抑制得小。因此,能够将通断时的恢复电流抑制得

小,能够将产生的噪声抑制得小。另外,由于vg仅上升至小于或等于阈值电压vth的电压值,因此还具有能够将阈值电压附近的dvge/dt抑制得小这样的效果。

37.在off时、即驱动定时信号的下降时,由于从栅极电极及栅极电容调整器13释放电荷,因此在栅极电流限制电路3中从输出侧向输入侧流过电流。因此,栅极电流限制电路3的输出侧和输入侧之间的电位差受限于电压限制器56的齐纳二极管6的击穿电压vz_6。齐纳二极管6的击穿电压vz_6被设定为与开关元件1所允许的最大电流值icmax对应的根据开关元件1的传输特性求出的栅极电压vgmax和驱动定时信号为off信号时的驱动电压振幅限制电路4的输出电压vsg之差的电压值。通过该设定,在驱动定时信号的下降时,栅极驱动电压生成器30的输出的电位vg瞬时成为与开关元件1所允许的最大电流值对应的vgmax。在本发明中,vgmax也称为第二阈值电压。

38.在栅极驱动电压生成器30的输出的电位vg成为vgmax后,由于电压限制器56的齐纳二极管5及齐纳二极管6变为off,因此栅极电极及栅极电容调整器13的电荷通过电流限制器17而被释放。此时,vg的变化率dvg/dt受限于电流限制器17和栅极电容调整器13的时间常数。如果栅极电压vge成为米勒电压vm,则开关元件1转变至米勒期间,但与on时相同地dvg/dt受限于电流限制器17,因此米勒期间的栅极电流被控制为,即使通断时的开关元件的电流值及元件温度等产生变化,其也不会大幅变化。即使栅极电压vge变为小于或等于vm,栅极电压vge的变化率vgde/dt也被栅极驱动电压生成器30的输出的电位vg控制,因此通断时的电流ic的di/dt的大小受到限制。由于对开关元件1的di/dt进行限制,因此在开关元件1的二极管流过恢复电流时的恢复噪声被控制为不会大幅变化。如上所述,在驱动定时信号为断开信号时、即断开时,电压限制器56对电流限制器17两端的电压进行限制,以使得栅极驱动电压生成器30的输出电压vg小于或等于第二阈值电压vgmax且通过电流限制器17对电流进行限制。由此,在驱动定时信号为断开信号时,电压限制器56使栅极驱动电压生成器30的输出电压vg下降至第二阈值电压vgmax,在vg下降至第二阈值电压vgmax后,通过流过电流限制器17的电流而使vg下降。

39.对开关元件1的温度变化时的动作进行说明。在图4中示出开关元件1为igbt时的不同温度下的传输特性。如图4所示,如果元件温度上升,则开关元件1的阈值电压vth变化为低电压。需要以受到限制的电压范围向低的电压侧变化的方式进行调整,以使得即使温度上升,开关元件1能够流过电流的栅极电压vge的范围也不会偏离栅极驱动电压生成器30的输出的电位vg的变化率dvg/dt受到限制的电压范围。该电压范围的调整可以通过利用齐纳二极管的击穿电压的温度特性来进行。作为用于利用温度特性的齐纳二极管5,使用击穿电压vz_5大于或等于5.6v的齐纳二极管。图5是表示齐纳二极管的温度特性,即齐纳二极管的击穿电压和击穿电压的温度系数(与温度变化相对的击穿电压的变化率)的关系的图。如图5所示,在击穿电压大于或等于5.6v的齐纳二极管中,击穿电压的温度系数为正。因此,从驱动定时信号为on时的驱动电压振幅限制电路4的输出点14的电位的值减去齐纳二极管5的击穿电压vz_5而得到的值即第一阈值电压vgmin,随着温度上升而自动地变化为低值。即,该第一阈值电压vgmin的温度变化具有与vth的温度变化相同的温度变化倾向。如果在开关元件1和齐纳二极管5之间没有大的温度差,则即使温度上升、开关元件1的vth降低,击穿电压vz_5也变大,因此vth不会偏离栅极电压受到限制的电压范围。在如果齐纳二极管5仅为1个齐纳二极管,则开关元件1的vth的变化与击穿电压的温度变化特性不匹配的情况

下,作为齐纳二极管5,通过设为将击穿电压不同的多个齐纳二极管串联连接的结构,从而能够将齐纳二极管5的温度变化特性调整为与vth的温度变化相匹配。

40.接着,对off时的动作进行说明。下面,作为例子,设想在280a时变为off的情况。在280a这样的大的电流区域中,与元件温度上升相伴地米勒电压vm上升,另一方面,阈值电压vth降低。因此,如果即使温度产生变化也不会使第二阈值电压vgmax变化,则在图3中由tdmax表示的延迟时间增加。为了对延迟时间的增加进行抑制,只要与温度上升相伴地使第二阈值电压vgmax上升即可。通过利用齐纳二极管的击穿电压的温度特性,能够与温度上升相伴地使第二阈值电压vgmax上升。作为齐纳二极管6,使用温度系数为正的齐纳二极管。对于击穿电压大于或等于5.6v的齐纳二极管,由于击穿电压的温度系数为正,因此呈击穿电压相对于温度上升而上升的特性。由此,在温度上升的情况下,由于齐纳二极管6的击穿电压上升,因此第二阈值电压vgmax的值自动地上升,驱动延迟时间tdmax的增加受到抑制。

41.在本实施方式中,优选由齐纳二极管5及齐纳二极管6构成的电压限制器56安装于相同的模块内或相同的冷却基座板之上,以使得其成为与开关元件1相同的温度。但是,即使电压限制器56没有安装于与开关元件1相同的模块内或相同的冷却基座板之上,只要安装于它们附近即可。如果将电压限制器56安装于安装有开关元件1的模块等的附近,则由于模块板或冷却基座板等的环境的温度,在开关元件1的温度上升时,电压限制器56的温度也上升。这样,通过将电压限制器56配置于电压限制器56的温度变化的环境与开关元件1的温度变化的环境相同的位置,从而两者的温度变化倾向变得相同。在电压限制器56的温度变化比开关元件1的温度变化小的情况下,例如,串联地构成多个齐纳二极管来对温度变化特性进行调整,或选择在少许的温度变化下vz_5及vz_6大幅变化的齐纳二极管即可。这样,通过考虑开关元件1和电压限制器56的温度变化的差异对电压限制器56的温度特性进行调整,从而能够使dvge/dt的控制范围不会偏离开关元件1的工作范围。

42.如上所述,根据实施方式1涉及的电力用半导体元件的驱动电路,即使开关元件的温度或电流值产生变化,也不进行复杂的控制,dvge/dt的控制范围自动地变化,因此通断动作的变动少。因此,例如,能够减小死区时间的裕量,进而能够实现通断损耗的变化、或噪声的变化少的电力用半导体元件的驱动电路。

43.实施方式2.

44.图6是表示实施方式2涉及的电力用半导体元件的驱动电路的结构的电路图。与实施方式1的区别在于,在驱动电压振幅限制电路4的输入侧连接有由电压限制器56、电流限制器17、栅极电容调整器13构成的栅极电流限制电路3。驱动电压振幅限制电路4以栅极驱动电压生成器30的输出点12的电位vg成为栅极电流限制电路3的输出侧的电位的方式进行控制。在本实施方式2中,将缓冲电路40的电压增益设为1而进行说明,但增益也可以不是1,通过以缓冲电路40的增益的量,对输入至缓冲电路40的信号的振幅进行调整,对电压限制器56的齐纳二极管5及齐纳二极管6的击穿电压进行调整,从而能够得到与图3相同的特性。本实施方式2如果应用于作为缓冲电路40的特性而具有在高频区域无法得到大增益等的频率特性的情况,则是有效的。在该情况下,如图6所示,将电容器c1连接于栅极电流限制电路3。在本实施方式2中,与on时及off时的开关元件1的特性变化相对的驱动电路2的动作的详情与实施方式1相同。

45.即使与第一控制电源7和第二控制电源8的电压相同或更大的振幅的驱动信号被

输入至输入端子11,也通过二极管9及二极管10将输入的振幅限制成第一控制电源7和第二控制电源8。在输入了on的驱动定时信号时,通过电压限制器56的齐纳二极管5及齐纳二极管6,使栅极电容调整器13的电压瞬时上升至vth。此时,通过经由电容器c1的电流而对栅极电容调整器13进行充电,因此其上升变得陡峭。缓冲电路40进行电流放大,使栅极驱动电压生成器30的输出点12的电位vg上升至vth。之后,由于栅极电容调整器13经由电流限制器17被充电,因此栅极电容调整器13的dv/dt得到控制,接收该电压,缓冲电路40使栅极驱动电压生成器30的输出点12的电压vg上升。

46.通过该结构,在输入了大振幅的信号时,即使存在开关元件1的传输特性的变化也会对dvge/dt进行控制,因此也与实施方式1相同地,栅极驱动电压生成器30对栅极电流进行控制,以使得对温度或通断电流变化时的折衷关系的变化进行抑制。此时,栅极驱动电压生成器30的输出点12的电位vg和栅极端子101的电位vge之间的电位差不会由于通断时的电流的大小或元件温度而大幅变化,因此能够降低通过栅极电阻rg进行调整的栅极电流的大小的温度及电流依赖性。另外,在栅极驱动电压生成器30的输出点12的电压vg的上升时等,通过将电容器c1与电流限制器17并联连接,从而能够增大驱动电路2的高频的增益,能够进行驱动电路2的增益的频率特性的校正。

47.实施方式3.

48.图7是表示实施方式3涉及的电力用半导体元件的驱动电路的结构的电路图。与实施方式1的区别在于,作为缓冲电路40的输入电压的钳位电路,使用了电阻r1、以极性的朝向相反的方式串联连接的齐纳二极管90及齐纳二极管100,而且,作为与电压限制器56并联连接的电流限制器17,使用了将恒流二极管71及恒流二极管72这两个恒流二极管以极性相反的方式串联连接而成的连接体。

49.即使输入至输入端子11的驱动定时信号vs的振幅产生变化,齐纳二极管90及齐纳二极管100也以使得输入至缓冲电路40的信号的振幅变得恒定的方式进行限制。另外,作为构成电流限制器17的两个恒流二极管的恒流值,使用相同值的恒流二极管。但是,也可以设为如下结构,即,作为on时的电流限制用的恒流二极管71和off时的电流限制用的恒流二极管72的恒流值,使用不同值的恒流二极管,从而改变on时和off时的通断速度。另外,栅极电流限制电路3为栅极电容调整器13连接于开关元件1的栅极

‑

发射极间的结构,但栅极电容调整器13是对通断时的速度进行调整的部分,也可以设为不具有栅极电容调整器13而仅对开关元件1的栅极进行充电的结构。另外,在图7中,缓冲电路40设为使用运算放大器,对运算放大器输出电压进行反馈的结构,但也可以是使用应用了互补晶体管等的缓冲电路,或使用对输入进来的信号进行放大的放大器电路等,对缓冲电路40的输出电压进行控制。在图7中,作为电压限制器56,设为将齐纳二极管5及齐纳二极管6这两个齐纳二极管以极性的朝向相反的方式串联连接的结构。齐纳二极管也能够设为如下结构,即,不仅使用击穿电压的温度系数为正的击穿电压大于或等于5.6v的元件,还组合击穿电压小于或等于5.6v的元件,通过多个齐纳二极管,将相对于温度变化的击穿电压的变化调整为与开关元件1的传输特性的温度变化相匹配的变化。

50.在本实施方式3中,如果作为驱动定时信号vs将on信号输入至输入端子11,则缓冲电路40输出第一控制电源7的电位。在输入了on信号时,瞬时地通过齐纳二极管5及齐纳二极管6使栅极电容调整器13的电压上升至开关元件1的阈值电压vth,之后通过电流限制器

17对栅极电容调整器13进行充电。在本实施方式3中,由于大于或等于vth的区域中的栅极电流的大小受到电流限制器17控制,因此栅极电流不会由于缓冲电路40的输出vsg和栅极端子101的电位vge之间的电位差而变化,因此通断速度被控制为恒定。在以往的恒流驱动中,在施加负偏压时、或vth大且从off时的栅极电压至vth为止的电位差大的情况下等,从输入了驱动定时信号时至开关元件驱动为止产生了延迟时间。另一方面,与实施方式1或实施方式2相同地,在本实施方式3中,栅极驱动电压生成器30的输出vg也以缩短该延迟时间的方式追随于元件特性的变化,因此能够缩短通断时所需要的死区时间。通过缩短死区时间,能够降低由死区时间引起的开关电源的输出电压及电流的误差。另外,通过将齐纳二极管5及齐纳二极管6各自设为将多个齐纳二极管串联连接的结构,能够将击穿电压的变化调整为与开关元件1的传输特性的温度变化相匹配。由此,能够以将齐纳二极管5及齐纳二极管6、开关元件1的温度特性、或温度变化的差异等也组合起来的方式,构成追随于温度变化的栅极电流限制电路3。图7所示的在输入处设置齐纳二极管90及齐纳二极管100的结构及使用两个恒流二极管作为电流限制器17的结构也能够应用于其它实施方式。

51.实施方式4.

52.图8是表示实施方式4涉及的电力用半导体元件的驱动电路的结构的电路图。在本实施方式4中,栅极电压校正器18与栅极电阻器rg并联连接。栅极电压校正器18对栅极驱动电压生成器30的输出电压vg进行检测,与其大小对应地输出校正电流iset以对栅极电压进行校正。就其它结构而言,在驱动电压振幅限制电路4的输入侧具有栅极电流限制电路3这一点上,与图6所示的实施方式2相同。

53.图9是用于对图8所示的电路的动作进行说明的表示各部分的电压、电流随时间的变化的曲线图。在on时及off时的动作中,栅极电压达到米勒电压为止的动作与实施方式2相同。在on时,如果栅极驱动电压生成器30的输出的电位vg变为大于或等于第三阈值电压vgmax1,则栅极电压校正器18强制地使开关元件1接通,因此输出使栅极电流增加的方向的校正电流iset1。第三阈值电压vgmax1大于或等于与由开关元件1的规格等决定的所允许的集电极电流的最大值对应的栅极电压,并且被设定为在栅极电压vge从vth达到vgmax1为止的期间,即使开关元件1在饱和状态下进行动作也不会发生破损的动作时间和电流的范围。由此,能够在过电流时等经过特定时间后将发射极

‑

集电极电压vce拉低,能够防止由于由开关元件1在通断时在有源区域进行动作引起的损耗而产生故障。

54.在off时,如果栅极驱动电压生成器30的输出的电位vg变为小于或等于第四阈值电压vgmin1,则栅极电压校正器18强制地使开关元件1断开,因此输出使栅极电极的电荷释放的方向的校正电流iset2。第四阈值电压vgmin1被设定为小于或等于开关元件1的阈值电压vth,通过依靠该电压可靠地使开关元件1断开,从而能够缩短驱动的延迟时间tdmax,能够缩短死区时间。考虑到栅极电极的电位vge与栅极驱动电压生成器30的输出的电位vg之间的电位差变小,通断会延迟,因此将栅极电压vge的下拉幅度增大而可靠地使开关元件1断开。此时,如果在vth附近急剧地下拉栅极电压vge,则恢复噪声会变大,因此考虑到断开的时间,将第四阈值电压vgmin1设定为小于或等于vth的具有裕量的电压。而且,还对作为校正电流的iset2进行控制而对ic的电流变化率di/dt进行限制,以使得栅极电流ig不会由于恢复对策而变得过大,使得vth附近的dvge/dt比预先确定的值小。由此,能够减小恢复电流的峰值,能够对通断噪声进行抑制。由于作为开关元件1的igbt在vth附近,ig的变化率变

小,因此如在实施方式3中说明过那样,即使将恒流二极管用作电流限制器17而使得栅极电压vge的变化率dvge/dt恒定,也能够减小恢复电流的峰值。另外,即使在使用mosfet作为开关元件1的情况下,也能够通过栅极电压校正器18,以使阈值电压vth附近的栅极电压vge的变化率dvge/dt变小的方式通过iset进行控制,降低在恢复电流或集电极

‑

发射极间电压vce产生的异常电压的峰值。

55.栅极电压校正器18并不限定于本实施方式4的结构,也能够应用于其它实施方式的电路,在进行了应用的情况下,能够得到上述说明过的第三阈值电压vgmax1、第四阈值电压vgmin1、及vth附近的动作的效果。

56.实施方式5.

57.图10是表示实施方式5涉及的电力用半导体元件的驱动电路的电路图。本实施方式5涉及的电力用半导体元件的驱动电路具有电流源181(也称为栅极电压校正器181),该电流源181基于开关元件1的温度或通断电流的大小、通断时的高频电流的测定结果等外部信号,对在栅极电极流动的电流进行控制。该电流源(栅极电压校正器)181也可以设置于与在实施方式4中图8所示的栅极电压校正器18相同的位置。实施方式4中的栅极电压校正器18构成为基于栅极驱动电压生成器30的输出电压,对在栅极电极流动的电流进行控制。本实施方式5中的电流源(栅极电压校正器)181如上所述,基于开关元件1的温度或通断电流的大小、通断时的高频电流的测定结果等外部信号使输出电流变化,对在栅极电极流动的电流进行控制。通过使电流源181的电流变化,能够对栅极驱动电压生成器30的输出电压vg的变化率dvg/dt进行调整。

58.电流源181只要是光电耦合器、恒流源、与电压源连接的电阻等能够使所输出的电流值变化的结构即可,可以是任意电流源。作为电流源181,例如能够使用经由图11a所示那样的光电耦合器182供给电流的结构的电流源。通过使电流流过input,能够在与input侧绝缘的output取出电流。在输出负的电流的情况下,将光电晶体管的集电极侧设为output,将负电源连接于发射极侧即可。另外,为了能够输出正负这两者的电流,将上述的输出正电流的光电耦合器和输出负电流的光电耦合器并联连接即可。以上那样的电流源也能够用作实施方式4中的栅极电压校正器18。另外,如在后述的实施方式6中说明的那样,在将电流源181设为交流电流源的情况下,也能够使用经由图11b所示那样的变压器183供给电流的结构的交流电流源。

59.在实施方式1~4中以如下方式进行控制,即,即使开关元件1的温度或通断电流的大小产生变化,米勒电压产生变化,也通过对dvg/dt进行控制而将栅极电流控制为恒定,使通断时的损耗不变。但是,由于dvg/dt的控制,从驱动定时信号vs至通断为止的延迟时间会成为问题。例如,在将开关元件1用于恒压驱动的开关电源的情况下,由于米勒电压产生变化,从驱动定时信号的输入至通断完成为止的时间产生差异,因此存在开关电源的输出电压产生误差这样的问题。

60.在本实施方式5中,也通过由电流限制器17对输出电流进行限制,从而对电流限制器17和电压限制器56的连接点即输出12,即栅极电容调整器13的电位vg的变化量进行限制。另外,电压限制器56对由电流限制器17进行向栅极电容调整器13的电流的限制的电压范围进行限制。电压限制器56由将两个齐纳二极管5及齐纳二极管6以极性的朝向相反的方式串联连接而成的串联连接体构成。通过该结构,不管电流的朝向是哪个朝向均能够对电

压进行限制。另外,如图2所示,在将两个串联连接体朝向相反地并联连接后的电路设为电压限制器56,也会实现如下效果,即,不管电流的朝向是哪个朝向均能够对电压进行限制,其中,该串联连接体是将齐纳二极管和二极管以极性的朝向相反的方式串联连接。但是,作为电压限制器56,图10所示的将两个齐纳二极管以极性的朝向相反的方式串联连接的结构是简单的结构。另外,优选电压限制器56配置于与开关元件1相同的模块内,或以成为与开关元件1等同的温度的方式配置于相同的基板内,因此图10所示的电压限制器56的结构为有效的结构。

61.在图10所示的电路中,为了对栅极电流的大小进行限制连接有栅极电容调整器13和栅极电阻rg,但这两者不是必要的,也可以不具有任何一者。而且,在能够利用开关元件1的芯片之上或元件内的常数的情况下,也可以不具有这两者。

62.图12是表示图10所示的电路的各部分的电压、电流的时间变化的曲线图。在图12的最上层的曲线图中,单点划线是驱动电压振幅限制电路4的输出点14、即栅极电流限制电路3的输入侧的电位vsg,实线是栅极驱动电压生成器30的输出点12的电位vg,虚线是开关元件1的栅极电极

‑

发射极电极间的电压vge。各电位是以开关元件1的发射极端子2的电位为基准而示出的。第2层的图示出在开关元件1的第一主电极即集电极和第二主电极即发射极之间流动的电流即集电极电流ic,第3层的图示出开关元件1的集电极

‑

发射极间的电压vce,第4层示出开关元件1的栅极电流ig。而且,第5层示出由电流源181输出的电流is。

63.在作为驱动定时信号vs而将on信号输入至输入端子11时,如单点划线所示,在驱动电压振幅限制电路4的输出点14输出与第一控制电源7的电压vcc对应的电位。在驱动定时信号vs为on时,将从vcc减去齐纳二极管5的击穿电压vz_5而得到的值作为第一阈值电压vgmin,以使得该vgmin大于或等于开关元件1的阈值电压vth的方式对vz_5的值进行设定。通过该设定,在on时即驱动定时信号vs的上升时,如实线所示,通过齐纳二极管5及齐纳二极管6,栅极电流限制电路3的输出电压vg上升至大于或等于开关元件1的阈值电压vth的电位vgmin。如果栅极电流限制电路3的输出电压vg大于或等于第一阈值电压vgmin,则栅极电流限制电路3的输入侧和输出侧之间的电位差变得小于或等于通过齐纳二极管5设定的电压vz_5,因此栅极电容调整器13通过电流限制器17被充电。

64.此时,栅极电流限制电路3的输出电压vg的变化受限于由电阻构成的电流限制器17和栅极电容调整器13的时间常数。如果开关元件1的栅极端子和发射极端子之间的电压即栅极电压vge大于或等于阈值电压vth,则开关元件1开始变为on,与栅极电压vge的上升相伴地增加所传输的电流ic,如果ic达到所需要的电流值,则开关元件1转变至米勒期间。如上所述,由于对栅极电压vge的变化率dvge/dt进行控制,因此,例如通断时的电流越大,米勒电压vm越大,则从驱动定时信号vs变为接通信号时至实际的通断开始为止的延迟时间td越长。相反,在off时,由于对栅极电压vge的变化率dvge/dt进行控制,因此在上述条件下从断开信号输入时起的延迟时间变短。

65.如上所述,由于米勒电压vm根据通断的电流或温度等条件而产生变化,因此从驱动定时信号vs变为接通信号时至实际的通断为止的延迟时间td产生变化。因此,存在由驱动定时信号vs指定的通断时间与实际的通断时间产生大的差异的问题。为了解决该问题,在本实施方式中设置用于对dvge/dt进行调整的电流源181。

66.在图12中,示出在米勒电压为某个值vm时,将电流源181的电流is的值设为负的状

态。通过该设定,与没有电流源181的情况相比,在on时,由于对栅极电极充电的每单位时间的电荷量减少,因此上升变慢。另一方面,在off时,由于从栅极电极释放的每单位时间的电荷量增加,因此下降变快。在该例子中,通过由电流源181输出的电流is的调整,使通断的延迟时间td在on时和off时相同。

67.在图13中,示出与图12的状态时相比,由于通断电流增加或温度产生了变化等,米勒电压变高而变为vm2的情况下的各部分的电压、电流波形。在图13中,作为vg的变化,为了进行比较,将图11的状态下的vg的变化作为vg_c而示出。在米勒电压上升的情况下,如果不对由电流源181输出的电流值进行调整,则在on时上升时间变长,相反,off时下降时间变短。在图13中,与图11的状态相比,使从电流源181输出的负的电流值减少。通过使从电流源181输出的负的电流值减少,从而如图13所示,on时的vg的变化率dvg/dt比作为比较而示出的vg_c的变化大,能够缩短上升时间,使on时的延迟时间td与图11的状态相同。在off时,vg的变化率dvg/dt比作为比较而示出的vg_c的变化率小,上升时间增加,能够使off时的延迟时间与图11的状态相同。

68.在图14中,示出与图11的状态时相比,由于通断电流减少或温度产生了变化等,米勒电压变低而变为vm3的情况下的各部分的电压、电流波形。在图14中,作为vg的变化,为了进行比较,将图11的状态下的vg的变化作为vg_c而示出。在米勒电压下降的情况下,如果不对由电流源181输出的电流值进行调整,则在on时上升时间变短,相反,off时下降时间变长。在图14中,与图11的状态相比,使从电流源181输出的负的电流值增加。通过使从电流源181输出的负的电流值增加,从而如图14所示,on时的vg的变化率dvg/dt比作为比较而示出的vg_c的变化率小,上升时间增加,能够使on时的延迟时间td与图11的状态相同。在off时,vg的变化率dvg/dt比作为比较而示出的vg_c的变化率大,上升时间减少,能够使off时的延迟时间与图11的状态相同。这样,能够以即使米勒电压产生变化,延迟时间也相同的方式通过电流源181进行控制。

69.这样,在本实施方式中,通过使电流源181的输出电流值变化而对dvg/dt进行调整,能够解决由驱动定时信号vs指定的通断时间和实际的通断时间产生大的差异的问题。即,在米勒电压的大小由于开关元件的温度或电流产生变化而产生变化的情况下,与开关元件的温度或电流的变化对应地,使电流源181的输出电流值变化,以使得on时的延迟时间和off时的延迟时间相同。由此,能够对由与通断电流或开关元件1的温度对应的米勒电压的变化导致的延迟时间进行调整,将on、off的延迟时间控制为一致。

70.此外,以上,作为电流源181的输出仅以负的电流值进行了说明,但由于电流源181是为了对电荷的充电、放电进行控制而设置的,因此不限于负,有时与vm的变化对应地产生输出正的电流值的需要,有时可以仅为负或者仅为正。

71.实施方式6.

72.图15是各部分波形的曲线图,示出实施方式6涉及的电力用半导体元件的驱动电路的动作。驱动电路的结构与图10相同。在本实施方式6中与实施方式4、5的区别在于,电流源181不与通断的定时相匹配地使其大小变化。下面,对连接有栅极电容调整器13的情况进行说明,但也可以省略栅极电容调整器13,还可以是直接对开关元件1的栅极施加输出电压vg的方式。图14的左侧所示的曲线图是由电流源181输出正电流时的曲线图。通过电流源181的电流,on时的栅极电流限制电路3的输出电压vg的斜率变大。而且,在栅极电压vge进

入米勒期间时,以vge和vg之间的电位差δv1变大的方式进行控制。由此,供给大的米勒电流,以通断时的集电极

‑

发射极间电压的变化率dvce/dt变大的方式进行控制。因此,缩短通断时的通断时间而降低损耗,在通断时产生高频带的高频电流。另一方面,如图14的右侧所示的曲线图所示,如果电流源181输出负的电流,则以vg的变化率dvg/dt变小的方式进行限制,以vge和vg之间的电位差δv2变小的方式进行控制。由此,由于以dvce/dt变小的方式进行控制,因此此时产生的通断噪声被限制为低频带。

73.在本实施方式6中,重复图15的左侧的曲线图的动作和右侧的曲线图的动作。如图15的is的曲线图所示,电流源181在时间轴上交替输出正电流和负电流,即电流源181使用交流电流源。电流源181以比输入至输入端子11的驱动定时信号vs的频率慢的变化交替输出正电流和负电流。即,电流源181所输出的交流的频率为比驱动定时信号vs低的频率。

74.以上,以通断的on时为例进行了说明,但在off时,也通过使从电流源181输出的电流变化,从而使off时的通断噪声的频率产生变化,在这一点上与on时相同。

75.为了说明应用了该控制时的效果,在图16中示出开关电源的噪声端子电压op的频率特性。在实施方式1中说明过的将dvce/dt控制为恒定值的情况下,由于dvce/dt的电流依赖性和温度依赖性降低,因此如由“dvce/dt:恒定”所示的曲线那样,会在特定的频率产生噪声峰值。相对于此,通过重复图15的左侧的曲线图的动作和右侧的曲线图的动作,从而噪声的频带产生变化,因此如图16的由“dvce/dt:变动”所示的曲线那样,能够使噪声峰值分散。在该控制的情况下,就噪声的峰值而言,能够通过电流源181所输出的电流的交流的频率及其大小、使频率变动时的重复频率,对其效果进行控制。即,通过对开关电源的噪声端子电压op进行测定,基于该测定值来对由电流源181输出的交流的频率进行控制,从而能够将产生噪声峰值的频带调整为所期望的频带。

76.在本发明中记载有各种例示性的实施方式及实施例,但1个或多个实施方式所记载的各种特征、方式及功能并不限于特定的实施方式的应用,能够单独或通过各种组合而应用于实施方式。因此,在本发明说明书所公开的技术的范围内可想象到没有例示的无数变形例。例如,包含使至少1个结构要素变形的情况、追加的情况或省略情况,以及,提取至少1个结构要素,与其它实施方式的结构要素进行组合的情况。

77.标号的说明

78.1开关元件,2驱动电路,3栅极电流限制电路,4驱动电压振幅限制电路,5、6齐纳二极管,7第一控制电源,8第二控制电源,11输入端子,12栅极驱动电压生成器的输出点,13栅极电容调整器,17电流限制器,18、181栅极电压校正器,20发射极端子,30栅极驱动电压生成器,56电压限制器,101栅极端子,182光电耦合器,183变压器,vgmin第一阈值电压,vgmax第二阈值电压,vgmax1第三阈值电压,vgmin1第四阈值电压,vth阈值电压。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。