1.本公开为一种电压调节系统,特别是一种用以最小化瞬间负载变化造成的电压突波的电压调节系统及其方法。

背景技术:

2.如图1所示,现有技术的电压调节系统100包含:电流-电压转换器110设置以接收参考电流i

ref

并输出参考电压v

ref

;电压调节器120设置以接收参考电压v

ref

并输出调节电压v

reg

;以及多个负载及多个开关,包含:第一负载131设置以经由第一开关132接收调节电压v

reg

,其中第一开关132是由第一控制信号en1所控制;第二负载141设置以经由第二开关142接收调节电压v

reg

,其中第二开关142是由第二控制信号en2所控制;以及以此类推的其他负载及其他开关。在本公开中,“v

dd”表示电源供应节点。电流-电压转换器110包含电阻器111、112以及电容器113,其中电阻器111作为负载以提供电流-电压转换,而电阻器112和电容器113形成低通滤波器。电压调节器120包含:运算放大器122和nmos(n通道金属氧化物半导体)晶体管123设置以形成具有负反馈的控制回路,以使调节电压v

reg

追踪参考电压v

ref

。电流-电压转换器110和电压调节器120在现有技术中都是众所周知的元件,此处不再详细说明。当第一控制信号en1(或第二控制信号en2)为生效(asserted)时,第一开关132(第二开关142)导通,以使第一负载131(第二负载141)通过调节电压v

reg

上电。当第一控制信号en1(或第二控制信号en2)为非生效(de-asserted)时,第一开关132(第二开关142)截止以使第一负载131(第二负载141)断电。根据此操作方式,第一负载131、第二负载141及其他负载可独立地上电或断电。此处的第一控制信号en1以及第二控制信号en2后文又称作逻辑信号en1以及逻辑信号en2。

3.第一负载131、第一开关132及其他负载上发生的瞬间变化可能导致调节电压v

reg

出现突波(spike),由于电压调节器120的控制回路的速度是有限的,无法足够快地起作用来进行调节以应对瞬间变化。为了减轻调节电压v

reg

上的突波,采用一去耦合电容器151以协助在瞬间变化期间更稳定地维持调节电压v

reg

。然而,加入去耦合电容器151将降低电压调节器120的控制回路的稳定性。应当理解,无论负载条件如何变化,都必须保证电压调节器120的稳定性,并且在负载条件发生瞬间变化时,期望调节电压v

reg

上所发生的突波很小。这种要求将大幅提升电压调节器120的设计难度,且通常可能牺牲调节电压v

reg

的调节效率。

4.承前所述,我们所期望的是一种电压调节系统,其可有效地减缓由突然的负载变化引起的电压突波。

技术实现要素:

5.在一些实施例中,一种系统包含:电压调节器,被设置以接收第一参考电压并输出调节电压;偏压电压产生器,包含以二极管形式连接的晶体管,偏压电压产生器被设置以接收偏压电流并输出参考栅极电压;以及多个开关负载电路,所述多个开关负载电路中的每

一者包含被设置以自调节电压接收供电的共漏极晶体管,通过逻辑信号控制的开关从参考栅极电压接收控制,并输出供应电压到负载且分流到去耦合电容器,其中,共漏极晶体管的尺寸是根据一比值将以二极管形式连接的晶体管的尺寸做缩放而得,所述比值是指负载的电流及偏压电流之间的比值。

6.在一些实施例中,一种系统包含:电压调节器,设置以接收第一参考电压并输出调节电压;偏压电压产生器,设置以接收偏压电流并输出参考栅极电压,偏压电压产生器包含串联连接电阻器及二极管连接nmos(n通道金属氧化物半导体)晶体管及低通滤波器;以及多个开关负载电路,所述多个开关负载电路中的每一者包含负载、通过逻辑信号控制的上电开关、去耦合电容器及共漏极nmos晶体管,其中,共漏极nmos晶体管的漏极连接至调节电压,共漏极nmos晶体管的栅极通过上电开关连接至参考栅极电压,共漏极nmos晶体管的源极连接到负载和去耦合电容器,共漏极nmos晶体管的长度等于二极管连接nmos晶体管的长度,且共漏极nmos晶体管的宽度等于二极管连接nmos晶体管的宽度乘以负载电流与偏压电流的比值。

7.在一些实施例中,一种方法包含:纳入电压调节器以根据第一参考电压输出调节电压;纳入偏压电压产生器以根据偏压电流输出参考栅极电压,偏压电压产生器包含串联连接的电阻器及二极管连接nmos(n通道金属氧化物半导体)晶体管以及低通滤波器;结合多个开关负载电路,所述多个开关负载电路中的每一者包含负载、通过逻辑信号控制的上电开关、去耦合电容器及共漏极nmos晶体管,其中,共漏极nmos晶体管的漏极连接至调节电压,共漏极nmos晶体管的栅极通过上电开关连接到参考栅极电压,共漏极nmos晶体管的源极连接到负载和去耦合电容器,共漏极nmos晶体管的长度等于二极管连接nmos晶体管的长度,且共漏极nmos晶体管的宽度等于二极管连接nmos晶体管的宽度乘以负载电流与偏压电流的比值。

附图说明

8.图1为现有技术的电压调节系统的示意图。

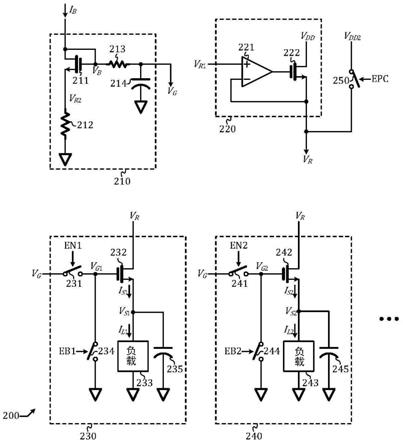

9.图2为根据本公开电压调节系统的一实施例的示意图。

10.符号说明

11.100:电压调节系统

12.110:电流-电压转换器

13.111:电阻器

14.112:电阻器

15.113:电容器

16.120:电压调节器

17.122:运算放大器

18.123:nmos晶体管

19.131:第一负载

20.132:第一开关

21.141:第二负载

22.142:第二开关

23.151:去耦合电容器

24.200:电压调节系统

25.210:偏压电压产生器

26.211:nmos晶体管

27.212:电阻器

28.213:电阻器

29.214:电容器

30.220:电压调节器

31.221:运算放大器

32.222:nmos晶体管

33.230:第一开关负载电路

34.231:上电开关

35.232:共漏极nmos晶体管

36.233:负载

37.234:断电开关

38.235:去耦合电容器

39.240:第二开关负载电路

40.241:上电开关

41.242:nmos晶体管

42.243:负载

43.244:断电开关

44.245:去耦合电容器

45.250:功率切断开关

46.eb1:互补逻辑信号

47.eb2:互补逻辑信号

48.en1:第一控制信号

49.en2:第二控制信号

50.epc:逻辑信号

51.v

reg

:调节电压

52.v

ref

:参考电压

53.v

dd

:电源供应节点

54.v

dd2

:电源供应节点

55.v

g

:栅极电压

56.v

g1

:电压

57.v

g2

:电压

58.v

r

:调节电压

59.v

r1

:第一参考电压

60.v

r2

:第二参考电压

61.v

s1

:电压

62.v

s2

:电压

63.v

b

:偏压电压

64.i

b

:偏压电流

65.i

ref

:参考电流

66.i

s1

:电流

67.i

s2

:电流

68.i

l1

:电流

69.i

l2

:电流

具体实施方式

70.本公开关于电压调节。尽管说明书描述多个本公开的具体示范实施例,其涉及本公开的一实施例实施时的较佳模式,但是应该理解,本公开的一实施例可通过多种方式来实现,并不限于下面描述的特定实施范例或特定方式,且特定实施范例或方式具有被实施的任何特征。在其他情况下,众所周知的细节不会被显示或描述,以避免模糊本公开的一实施例的特征。

71.本领域的技术人员应理解与本公开的一实施例中使用与微电子相关的术语和基本概念,例如,“电压”、“电流”、“功率”、“互补金属氧化物半导体(complementary metal-oxide semiconductor;cmos)”、“n通道金属氧化物半导体(n-channel metal-oxide semiconductor;nmos)晶体管”、“p通道金属氧化物半导体(p-channel metal-oxide semiconductor;pmos)晶体管”、“电阻器”、“电容器”、“开关”、“去耦合”、“低通滤波器”、“运算放大器”及“负反馈”。这些术语用于微电子学的背景中,并且相关概念对于本领域的技术人员来说是显而易见的,因此不会在这里详细解释。

72.本领域的技术人员亦可识别电容器符号及接地符号,可识别pmos晶体管和nmos晶体管的mos(金属氧化物半导体)晶体管符号,并识别其“源极(source)”、“栅极(gate)”和“漏极(drain)”端子。本领域技术人员可阅读包含电容器、nmos晶体管和pmos晶体管的电路示意图,并且不需要在示意图中对一晶体管如何与另一晶体管进行连接的详细描述。本领域的技术人员理解“共漏极(common-drain)”电路的概念,不需要解释。本领域技术人员亦可理解诸如微米(μm)、纳米(nm)、皮法拉(pf)、百万欧姆(mohm)、微安培(μa)及毫安培(ma)之类的单位。本领域技术人员理解欧姆定律(ohm’s law),不需解释。

73.在本公开的一实施例中,“信号”是承载某些信息的电压或电流。

74.从工程角度来呈现本公开的一实施例,例如,“x等于y”表示“x和y之间的差值小于一特定的工程公差”。

75.在本公开的一实施例中,v

dd

定义为电源供应节点(power supply node),后面也用以表示电源供应节点输出的电压(称电源供应电压v

dd

或电压v

dd

)。

76.逻辑信号是具有两种状态的电压信号:“生效(asserted)”状态和“非生效(de-asserted)”状态。开关(switch)是受逻辑信号控制的装置;所述开关近似为短路(short)电路并在逻辑信号生效时被称为导通(turned on),并且近似为开路(open)电路并当逻辑信号非生效时被称为截止(turned off)。开关可通过nmos晶体管实现,其中逻辑信号控制nmos晶体管的栅极,并且nmos晶体管的源极和漏极形成两个输入/输出端子。

77.如果第一逻辑信号和第二逻辑信号总是处于相反的状态,则第一逻辑信号被称为第二逻辑信号的逻辑反转(logical inversion)。即,当第一逻辑信号生效时,第二逻辑信号非生效,当第一逻辑信号非生效时,第二逻辑信号生效。当第一逻辑信号被认为是第二逻辑信号的逻辑反转时,第一逻辑信号及第二逻辑信号被认为是彼此互补。

[0078]“以二极管形式连接的nmos晶体管”是以其栅极连接到其漏极的拓扑结构设置的nmos晶体管。

[0079]“去耦合电容器”是设置以将供应电压维持在节点处的电容器,从而当从节点汲取的电流突然变化时,供应电压稳定并且不具有大的突波(spike)。

[0080]“共漏极nmos晶体管”是在拓扑结构中设置的nmos晶体管,其中在其漏极处的电压基本上为固定的,在其栅极处接收输入,并且从其源极输出输出。

[0081]

当栅极-源极电压低于阈值电压时,nmos晶体管截止;当栅极-源极电压高于阈值电压时,nmos晶体管导通。“过驱动(over-drive)”电压是栅极-源极电压减去阈值电压。nmos晶体管的电流取决于nmos晶体管的过驱动电压、宽度和长度。

[0082]

电路是晶体管、电容器、电阻器、开关和/或以某些方式相互连接的其他电子装置的集合。

[0083]

根据本公开的一些实施例的电压调节系统200的示意图包含:电压调节器220,设置以根据第一参考电压v

r1

输出调节电压v

r

;偏压(bias)电压产生器210,设置以接收偏压电流i

b

并输出参考栅极电压v

g

;多个开关负载电路,包含第一开关负载电路230、第二开关负载电路240等,设置以从调节电压v

r

接收供电并根据参考栅极电压v

g

建立偏压。第一开关负载电路230(第二开关负载电路240)包含通过逻辑信号en1(逻辑信号en2)控制的上电开关231(上电开关241)、共漏极nmos(n通道金属氧化物半导体)晶体管232(晶体管242)、负载233(负载243)及去耦合电容器235(去耦合电容器245)。在另一些实施例中,第一开关负载电路230(第二开关负载电路240)还包含通过互补逻辑信号eb1(互补逻辑信号eb2)控制的断电开关234(断电开关244),其互补逻辑信号eb1(互补逻辑信号eb2)为逻辑信号en1(逻辑信号en2)的逻辑反相。

[0084]

电压调节器220包含nmos晶体管222及运算放大器221。nmos晶体管222被称为功率晶体管,因为它向所述多个开关负载电路230、240等供电。运算放大器221和nmos晶体管222设置以形成具有负反馈的控制回路,以使调节电压v

r

近似等于第一参考电压v

r1

。可以视需要进行补偿(例如,通过使用未在图2中示出但对于本领域技术人员显而易见的并联电容器以设置来将运算放大器221的输出分流(shunt)到电源供应节点“v

dd”或接地的一者),以确保控制回路的稳定性。在控制系统的上下文中,电压调节器220以及“运算放大器”、“控制回路”、“负反馈”、“稳定性”及“补偿”的概念对于本领域技术人员而言是众所周知的,因此这里不再详细描述。在替代的另一些实施例中,功率晶体管即pmos(p通道金属氧化物半导体)晶体管替换nmos晶体管222,并与操作放大器221的“ ”和

“-”

端子交换,从而保留负反馈。所述替代实施例中,对于补偿以确保稳定性的需求在现有技术中也是众所周知的,因此不再详细描述。

[0085]

偏压电压产生器210包含一个以二极管形式连接的nmos晶体管211、两个电阻器212、213及一个电容器214。为了简洁起见,以下将以二极管形式连接的nmos晶体管211简称为nmos晶体管211。偏压电流i

b

经由nmos晶体管211流到电阻器212,从而建立第二参考电压

v

r2

。应用欧姆定律可做到:

[0086]

v

r2

=i

b

.r

212

ꢀꢀꢀ

(公式1)

[0087]

在此,r

212

表示电阻器212的电阻值。偏压电压v

b

在nmos晶体管211的栅极处建立,可用以下等式表示:

[0088]

v

b

=v

r2

v

th211

v

od211

ꢀꢀꢀ

(公式2)

[0089]

在此,“v

th211”为nmos晶体管211的阈值电压,而“v

od211”是nmos晶体管211的过驱动电压,其取决于nmos晶体管211的偏压电流i

b

、宽度及长度。电阻器213和电容器214形成低通滤波器,从而参考栅极电压v

g

近似等于偏压电压v

b

但噪声较小。因此,参考栅极电压v

g

可以下公式表示:

[0090]

v

g

≌v

r2

v

th211

v

od211

ꢀꢀꢀ

(公式3)

[0091]

在第一开关负载电路230中,共漏极nmos晶体管232的栅极经由上电开关231连接至参考栅极电压v

g

,并经由断电开关234连接至接地。为了简洁起见,以下将共漏极nmos晶体管232简称为nmos晶体管232。在此,nmos晶体管232栅极的电压通过电压v

g1

表示,nmos晶体管232源极的电压通过电压v

s1

表示,通过nmos晶体管232输出的源电流由电流i

s1

表示,并且通过负载233汲取的负载电流由负载电流i

l1

表示。当逻辑信号en1非生效时,互补逻辑信号eb1为生效,上电开关231断开以将电压v

g1

与栅极电压v

g

断开,而断电开关234导通以将电压v

g1

拉至接地;在这种情况下,nmos晶体管232关闭(shut off),从而使电流i

s1

为零;因此,电压v

s1

通过负载电流i

l1

拉低并最终下降至接地,负载电流i

l1

不可维持,且也必须降至零;结果,负载233断电。当逻辑信号en1为生效,从而互补逻辑信号eb1非生效时,导通上电开关231将电压v

g1

拉(pull)至栅极电压v

g

,同时截止断电开关234以断开电压v

g1

与地面的连接;在这种情况下,nmos晶体管232导通以输出源极电流i

s1

,从而当负载电流i

l1

通过负载233汲取时可维持电压v

s1

。电压v

s1

可用以下公式表示:

[0092]

v

s1

≌v

g-v

th232-v

od232

=v

r2

v

th211

v

od211-v

th232-v

od232

ꢀꢀꢀ

(公式4)

[0093]

在此,“v

th232”是nmos晶体管232的阈值电压,“v

od232”是nmos晶体管232的过驱动电压,其取决于nmos晶体管232的源极电流i

s1

、宽度和长度。在一个实施例中,nmos晶体管232和nmos晶体管211具有相同长度和相同阈值电压,即,v

th211

等于v

th232

。

[0094]

在一些实施例中,nmos晶体管232的宽度通过电流i

l1

根据以下等式决定:

[0095]

w

232

=w

211

.i

l1

/i

b

ꢀꢀꢀ

(公式5)

[0096]

在此,w

232

是nmos晶体管232的宽度,w

211

是nmos晶体管211的宽度。去耦合电容器235用于使电压v

s1

更稳定,并在电流i

l1

突然变化时减小突波。在稳定状态下,电流i

s1

近似等于电流i

l1

。根据公式5,一公式如下:

[0097]

w

232

≌w

211

.i

s1

/i

b

ꢀꢀꢀ

(公式6)

[0098]

公式6表明nmos晶体管211和nmos晶体管232具有相同电流密度(每单位宽度的电流)。由于nmos晶体管211和nmos晶体管232也具有相同的长度,因此nmos晶体管211和nmos晶体管232必须具有相同的过驱动电压。即,v

od211

等于v

od232

。因此,公式4可简化为:

[0099]

v

s1

≌v

r2

ꢀꢀꢀ

(公式7)

[0100]

如此,电压v

s1

(用于负载233的供应电压)近似等于第二参考电压v

r2

,因此,负载233的供应电压被调节。

[0101]

第二开关负载电路240在功能上与第一开关负载电路230相同,而将上电开关231

替换为上电开关241,nmos晶体管232替换为nmos晶体管242,将断电开关234替换为断电开关244,将负载233替换为负载243,去耦合电容器235替换为去耦合电容器245,逻辑信号en1替换为逻辑信号en2,互补逻辑信号eb1替换为互补逻辑信号eb2,电压v

g1

替换为电压v

g2

,电流i

s1

替换为电流i

s2

,电流i

l1

替换为电流i

l2

。nmos晶体管242和nmos晶体管211具有相同长度,并且nmos晶体管242的宽度通过电流i

l2

根据以下公式决定:

[0102]

w

242

≌w

211

.i

l2

/i

b

ꢀꢀꢀ

(公式8)

[0103]

在此,w

242

是nmos晶体管242的宽度。依照与第一开关负载电路230情况相同的原理,可得出:

[0104]

v

s2

≌v

r2

ꢀꢀꢀ

(公式9)

[0105]

如此,开关负载电路230、240等的每一开关电路可独立地上电或断电,且当其上电时,其负载通过调节的供应电压供应,且近似等于第二参考电压v

r2

。

[0106]

电压调节系统200相对于现有技术的电压调节系统100的优点在于用于减轻负载的电源电压的突波,使之与电压调节器220不直接耦合,因此不影响电压调节器220的稳定性。例如,去耦合电容器235可有效地减轻电压v

s1

的突波,但是由于nmos晶体管232提供反向隔离(reverse isolation)而不与电压调节器220直接耦合。另一个优点是:负载的供应电压对电源供应电压v

dd

非常不敏感,因为有两层隔离:一层由电压调节器220提供,另一层由共漏极晶体管提供。

[0107]

作为示例而非限制,在一些实施例中:使用28nm cmos处理在硅基板上制造电压调节系统200;电压v

dd

为1.35v;第一参考电压v

r1

为1.2v;偏压电流i

b

为100微安培(μa);r

212

为10千欧姆(kohm);电阻器213为1百万欧姆(mohm);电容器214为10皮法拉(pf);nmos晶体管211的宽度/长度为20微米(μm)/250纳米(nm);电流i

l1

为1毫安培(ma);nmos晶体管232的宽度/长度是200μm/250nm;去耦合电容器235为5pf;电流i

l2

为2ma;nmos晶体管232的宽度/长度为400μm/250nm;去耦合电容器245为10pf。

[0108]

在另一些实施例中,电压调节系统200还包含功率切断(power cut)开关250,功率切断开关250(后简称断电开关250)设置以来根据附加逻辑信号epc将调节电压v

r

连接到另一电源供应节点“v

dd2”(称电源供应节点v

dd2

或电压v

dd2

)。当附加逻辑信号epc为生效时,电压调节系统200处于断电模式,其中,调节电压v

r

通过断电开关250拉至电压v

dd2

,并且必须禁能电压调节器220以防止电压调节器220与断电开关250之间发生争夺(contention)。禁能(disabling)电压调节器220可通过各种方式来实现,例如,将运算放大器221断电或将第一参考电压v

r1

设置为零。在这种断电模式下,每一开关负载电路(例如第一开关负载电路230)中的共漏极晶体管(例如nmos晶体管232)仍可为负载(例如负载233处的电压v

s1

)的电压提供电压调节。尽管此断电模式可以提供较少的电压调节,但由于禁能了电压调节器220,因此可会节省功率。换句话说,此架构允许在功耗和电压调节之间进行权衡。在一些实施例中,电源供应节点v

dd2

及电源供应节点v

dd

为相同的电源供应节点,即电源供应节点v

dd2

及电源供应节点v

dd

电性短路。

[0109]

以上所述的实施例仅为说明本发明的技术思想及特点,其目的在于使本领域技术人员能够了解本发明的内容并据以实施,当不能以之限定本发明的权利要求,即大凡依本发明所公开的构思所作的均等变化或修饰,仍应涵盖在本发明的权利要求内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。