技术特征:

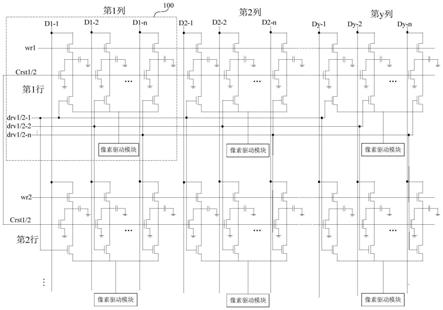

1.一种栅极驱动电路,其特征在于,包括级联的多个栅极驱动单元,至少一个所述栅极驱动单元包括:输出线;输出模块,包括第一薄膜晶体管、第二薄膜晶体管和第三薄膜晶体管,所述第一薄膜晶体管的栅极和所述第二薄膜晶体管的栅极连接第一线,所述第一薄膜晶体管的源极连接第二线,所述第二薄膜晶体管的源极连接第三线,所述第一薄膜晶体管的漏极、所述第二薄膜晶体管的漏极和所述第三薄膜晶体管的栅极互相连接,所述第三薄膜晶体管的源极连接所述第二线或所述第三线,所述第三薄膜晶体管的漏极连接所述输出端;其中,所述第一薄膜晶体管打开时的所述第二线上的电位大于所述第二薄膜晶体管打开时的所述第三线上的电位,且所述第一薄膜晶体管为p型薄膜晶体管,所述第二薄膜晶体管为n型薄膜晶体管。2.如权利要求1所述的栅极驱动电路,其特征在于,所述第三薄膜晶体管的源极连接所述第二线,所述第三薄膜晶体管为p型薄膜晶体管。3.如权利要求1所述的栅极驱动电路,其特征在于,所述第三薄膜晶体管的源极连接所述第三线,所述第三薄膜晶体管为n型薄膜晶体管。4.一种栅极驱动电路,其特征在于,包括级联的多个栅极驱动单元,每一级所述栅极驱动单元包括:上拉模块和下拉模块;所述上拉模块包括第一薄膜晶体管、第二薄膜晶体管和第三薄膜晶体管,所述第一薄膜晶体管的栅极和所述第二薄膜晶体管的栅极连接第一节点,所述第一薄膜晶体管的源极和所述第三薄膜晶体管的源极接入第n条时钟信号,所述第二薄膜晶体管的源极接入恒压低电位,所述第一薄膜晶体管的漏极、所述第二薄膜晶体管的漏极和所述第三薄膜晶体管的栅极均连接第二节点,所述第三薄膜晶体管的漏极连接第n级栅极驱动信号输出端;其中,所述第一薄膜晶体管和所述第三薄膜晶体管为p型薄膜晶体管,所述第二薄膜晶体管为n型薄膜晶体管;所述下拉模块包括第四薄膜晶体管、第五薄膜晶体管和第六薄膜晶体管,所述第四薄膜晶体管的栅极和所述第五薄膜晶体管的栅极接入第n条时钟信号,所述第四薄膜晶体管的源极接入恒压高电位,所述第五薄膜晶体管的源极和所述第六薄膜晶体管的源极均接入恒压低电位,所述第四薄膜晶体管的漏极、所述第五薄膜晶体管的漏极和所述第六薄膜晶体管的栅极均连接第三节点,所述第六薄膜晶体管的漏极连接所述第n级栅极驱动信号输出端;其中,所述第四薄膜晶体管为p型薄膜晶体管,所述第五薄膜晶体管和所述第六薄膜晶体管为n型薄膜晶体管。5.如权利要求4所述的栅极驱动电路,其特征在于,每一级所述栅极驱动单元还包括上拉控制模块,所述上拉控制模块包括第七薄膜晶体管、第八薄膜晶体管、第九薄膜晶体管和第一电容,其中,所述第七薄膜晶体管的栅极、所述第八薄膜晶体管的漏极和所述第九薄膜晶体管的漏极均连接第四节点,所述第七薄膜晶体管的源极接入所述第n

‑

1级栅极驱动信号,所述第七薄膜晶体管的漏极连接所述第一节点,所述第八薄膜晶体管的栅极接入第n

‑

2条时钟信号,所述第八薄膜晶体管的源极接入第n

‑

2级栅极驱动信号,所述第九薄膜晶体管的栅极接入第n条时钟信号,所述第九薄膜晶体管的源极接入恒压低电位,连接所述第四节点,所述第一电容的一端连接第四节点,所述第一电容的另一端接入第n

‑

1级栅极驱动信

号。6.如权利要求4所述的栅极驱动电路,其特征在于,所述下拉模块还包括第十薄膜晶体管,所述第十薄膜晶体管的栅极接入第n 2条时钟信号,所述第十薄膜晶体管的源极接入恒压低电位,所述第十薄膜晶体管的漏极连接所述第一节点。7.如权利要求4所述的栅极驱动电路,其特征在于,每一级所述栅极驱动单元还包括复位模块,所述复位模块包括第十一薄膜晶体管,所述第十一薄膜晶体管的栅极接入复位信号,所述第十一薄膜晶体管的源极接入恒压低电位,所述第十一薄膜晶体管的漏极连接所述第一节点。8.如权利要求4所述的栅极驱动电路,其特征在于,每一级所述栅极驱动单元还包括第二电容,所述第二电容的一端连接所述第一节点,所述第二电容的另一端接入恒压低电位。9.如权利要求4所述的栅极驱动电路,其特征在于,每一级所述栅极驱动单元还包括栅极驱动信号关闭模块,所述栅极驱动信号关闭模块包括第十二薄膜晶体管,所述第十二薄膜晶体管的栅极接入全局控制信号,所述第十二薄膜晶体管的源极接入恒压低电位,所述第十二薄膜晶体管的漏极连接第n级栅极驱动信号输出端。10.如权利要求4所述的栅极驱动电路,其特征在于,所述第一薄膜晶体管、所述第三薄膜晶体管和所述第四薄膜晶体管为低温多晶硅薄膜晶体管,所述第二薄膜晶体管、所述第五薄膜晶体管和所述第六薄膜晶体管为氧化物薄膜晶体管。11.一种显示面板,其特征在于,包括权利要求4

‑

10任一项所述的栅极驱动电路。

技术总结

本申请提供了一种栅极驱动电路及显示面板,该栅极驱动电路的上拉模块和下拉模块通过P型薄膜晶体管输出恒压高电位到第二节点、第三节点和第n级栅极驱动信号,以及通过N型薄膜晶体管输出恒压低电位到第二节点、第三节点和第n级栅极驱动信号,从而提高栅极驱动电路与关键节点连接的薄膜晶体管输出信号的稳定性,且由于采用P型薄膜晶体管和N型薄膜晶体管串联构成的CMOS结构,第一薄膜晶体管和第二薄膜晶体管互相切换输出高低信号,第四薄膜晶体管和第五薄膜晶体管互相切换输出高低信号,使得栅极驱动电路中无常高节点,因此栅极驱动电路中的薄膜晶体管不会由于长期受到电应力而发生阈值电压漂移,从而提高了栅极驱动电路的稳定性。定性。定性。

技术研发人员:曹海明 田超 管延庆 艾飞 刘广辉

受保护的技术使用者:武汉华星光电技术有限公司

技术研发日:2021.08.03

技术公布日:2021/11/14

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。