1.本公开大体上涉及半导体存储器和方法,且更确切地说,涉及用于posit运算的加 速电路系统的设备、系统和方法。

背景技术:

2.存储器装置通常提供为计算机或其他电子系统中的内部电路、半导体电路、集成电 路。存在许多不同类型的存储器,包含易失性及非易失性存储器。易失性存储器可能需 要电力以维持其数据(例如,主机数据、错误数据等),且包含随机存取存储器(randomaccess memory,ram)、动态随机存取存储器(dynamic random access memory,dram)、 静态随机存取存储器(static random access memory,sram)、同步动态随机存取存储器 (synchronous dynamic random access memory,sdram)和晶闸管随机存取存储器 (thyristor random access memory,tram)等等。非易失性存储器可通过在未被供电时保 存所存储数据来提供持久性数据,且可包含nand快闪存储器、nor快闪存储器和电 阻可变存储器,例如相变随机存取存储器(pcram)、电阻性随机存取存储器(rram)和 例如自旋力矩转移随机存取存储器(stt ram)的磁阻随机存取存储器(mram)等等。

3.存储器装置可耦合到主机(例如,主机计算装置)以存储数据、命令和/或指令以在计 算机或电子系统操作时供主机使用。例如,数据、命令和/或指令可在计算或其它电子系 统的操作期间在主机与一或多个存储器装置之间传送。

技术实现要素:

4.一方面,本技术提供一种用于posit运算的加速电路系统的方法,其包括:在可耦 合到加速电路系统的存储器控制器处接收指示执行将第一位串写入到驻存于所述加速 电路系统上的第一缓冲器的操作的信令,所述加速电路系统配置成对以通用数字(unum) 或posit格式格式化的位串执行算术运算、逻辑运算或这两者;在所述存储器控制器处 接收指示执行将第二位串写入到驻存于所述加速电路系统上的第二缓冲器的操作的信 令;将指示待使用写入到所述第一缓冲器的所述第一位串和写入到第二缓冲器的所述第 二位串执行算术运算、逻辑运算或这两者的信令传输到所述加速电路系统;经由所述加 速电路系统且根据由所述加速电路系统接收的所述信令执行所述算术运算、所述逻辑运 算或这两者;以及将指示所述算术运算、所述逻辑运算或这两者的结果的信令传输到所 述存储器控制器。

5.另一方面,本技术提供一种用于posit运算的加速电路系统的方法,其包括:在驻 存于加速电路系统上的第一缓冲器处接收指示以通用数字(unum)或posit格式格式化的 第一位串的信令,所述加速电路系统配置成对以所述unum或posit格式格式化的位串执 行算术运算、逻辑运算或这两者;在驻存于所述加速电路系统上的第二缓冲器处接收指 示以所述unum或posit格式格式化的第二位串的信令;将指示算术运算、逻辑运算或这 两者的信令传输到驻存于所述加速电路系统上的处理电路系统;以及经由所述处理电路 系统使

用所述第一位串和所述第二位串执行所述算术运算、所述逻辑运算或这两者。

6.另一方面,本技术提供一种用于posit运算的加速电路系统的系统,其包括:主机; 以及存储器装置,其可耦合到所述主机且配置成:从所述主机接收指示对以通用数字 (unum)或posit格式格式化的位串执行算术运算、逻辑运算或这两者的主机级指令的信 令;将指示执行所述算术运算、所述逻辑运算或这两者的主机级指令的所述信令解析为 指示执行与所述算术运算、所述逻辑运算或这两者相关联的子运算的机器级指令的信 令;以及根据指示所述机器级指令的所述信令,使用指示所述位串的所述信令执行所述 子运算。

附图说明

7.图1为根据本公开的多个实施例的呈包含设备的计算系统形式的另一功能框图,所 述设备包含主机和存储器装置。

8.图2a为根据本公开的多个实施例的呈包含设备的计算系统形式的功能框图,所述 设备包含主机和存储器装置。

9.图2b为根据本公开的多个实施例的呈包含设备的计算系统形式的另一功能框图, 所述设备包含主机和存储器装置。

10.图3为具有es指数位的n位posit的实例。

11.图4a为用于3位posit的正值的实例。

12.图4b为使用两个指数位的posit构造的实例。

13.图5为根据本公开的多个实施例的呈包含设备的计算系统形式的另一功能框图,所 述设备包含主机和存储器装置。

14.图6为根据本公开的多个实施例的呈包含设备的计算系统形式的另一功能框图,所 述设备包含主机和存储器资源。

15.图7为根据本公开的多个实施例的呈包含设备的计算系统形式的另一功能框图,所 述设备包含主机和存储器资源。

16.图8为根据本公开的多个实施例的呈包含设备的计算系统形式的另一功能框图,所 述设备包含主机和存储器资源。

17.图9为根据本公开的多个实施例的呈包含设备的计算系统形式的另一功能框图,所 述设备包含主机和存储器资源。

18.图10为根据本公开的多个实施例的呈加速电路系统形式的功能框图。

19.图11为根据本公开的多个实施例的呈存储器装置形式的另一功能框图。

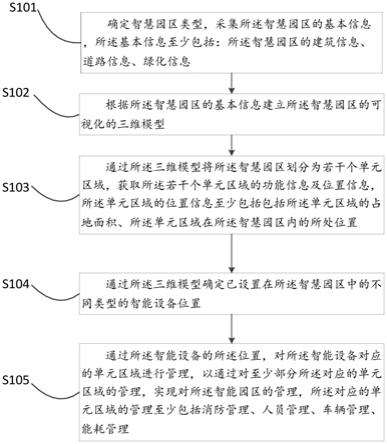

20.图12为根据本公开的多个实施例的表示用于posit运算的加速电路系统的实例方法 的流程图。

21.图13为根据本公开的多个实施例的表示用于posit运算的加速电路系统的实例方法 的另一流程图。

22.图14为根据本公开的多个实施例的表示用于posit运算的加速电路系统的实例方法 的另一流程图。

23.图15是根据本公开的多个实施例的表示用于posit运算的加速电路系统的实例方法 的另一流程图。

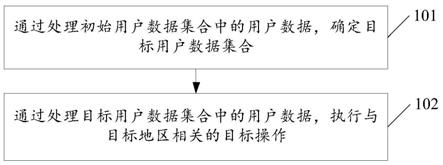

具体实施方式

24.本发明描述与用于posit运算的加速电路系统有关的系统、设备和方法。通用数字 (unum)位串,例如posit位串操作数和表示使用posit位串操作数执行的算术和/或逻辑运 算的结果的posit位串可存储于例如存储器阵列或其它存储器资源的存储器资源中。部 署在存储器装置中的电路系统可存取存储器资源以从存储器资源检索unum位串操作数 和/或使用unum位串操作数执行的算术和/或逻辑运算的结果。例如,可使用存储于存储 器资源中的第一unum位串和存储于存储器资源中的第二unum位串来执行算术运算和/ 或逻辑运算。算术运算和/或逻辑运算的结果可存储于存储器资源中且随后检索。

25.计算系统可执行广泛范围的可包含各种计算的运算,这可需要不同的准确度。然而, 计算系统具有的存储器的数量有限,在所述存储器中存储在其上执行计算的操作数。为 了促进在由有限存储器资源施加的约束内对由计算系统存储的操作数执行运算,在一些 方法中,可以特定格式存储操作数。为简单起见,此类格式被称为“浮点”格式或“浮 点数(float)”(例如,ieee 754浮点格式)。

26.根据浮点标准,就三个整数集或位集

‑

一位集称作“基数”,一位集称作“指数”,且 一位集称作“尾数”(或有效数字)而言表示位串(例如,可表示数目的位串),例如二进制 数串。为简单起见,定义其中存储二进制数串的格式的整数集或位集可在本文中称为“数 值格式”或“格式”。例如,定义浮点位串的上述位的三个整数集(例如,基数、指数和 尾数)可称为格式(例如,第一格式)。如下文更详细地描述,posit位串可包含四个整数集 或位集(例如,符号、底数、指数和尾数),其也可称为“数值格式”或“格式”(例如, 第二格式)。另外,根据浮点标准,两种无穷数(例如, ∞和

‑

∞)和/或两种类型的“非数 (not

‑

a

‑

number;nan)”(安静nan和信令nan)可包含于位串中。

27.浮点标准已在计算系统中使用数年且定义用于由许多计算系统进行的计算的算术 格式、交换格式、舍入规则、运算和异常处理。算术格式可包含二进制和/或十进制浮点 数据,其可包含有穷数、无穷数和/或特殊nan值。交换格式可包含可用以交换浮点数 据的编码(例如,位串)。舍入规则可包含当在算术运算和/或转换运算期间舍入数值时可 满足的一组特性。浮点运算可包含算术运算和/或其它计算运算,例如三角函数。异常处 理可包含异常条件的指示,如除以零、溢出等。

28.浮点的替代格式称作“通用数字”(unum)格式。存在可称为“posit”和/或“有效

”ꢀ

的若干形式的unum格式

‑

i型unum、ii型unum和iii型unum。i型unum是在分数的结 尾处使用“ubit”指示实数是否为准确浮点数或其是否介于相邻浮点数之间的区间中的 ieee 754标准浮点格式的超集。i型unum中的符号位、指数位和分数位根据ieee 754 浮点格式获取其定义,然而,i型unum的指数和分数字段的长度可从单个位显著地改变 到最大用户可定义长度。通过根据ieee 754标准浮点格式获取符号位、指数位和分数 位,i型unum可类似于浮点数而表现,然而,与浮点数相比,在i型unum的指数位和 分数位中呈现的可变位长度可需要额外管理。

29.ii型unum通常与浮点数不兼容,这准许基于所投影的实数的干净的数学设计。ii 型unum可包含n位且可在“u格”方面加以描述,其中圆形投影的象限填充有2

n

‑3‑

1 个实数的有序集。ii型unum的值可围绕将圆形投影等分的轴线反射,使得正值位于圆 形投影的右上象限中,而其负对应值位于圆形投影的左上象限中。表示ii型unum的圆 形投影的下半部可

包含位于圆形投影的上半部中的值的倒数。对大多数运算来说,ii型 unum通常依赖于查找表(lut)。例如,在一些情况下,查找表的大小可能限制ii型unum 的效果。然而,与在一些条件下的浮点数相比,ii型unum可提供改进的计算功能。

30.iii型unum格式在本文中称为“posit格式”或为简单起见称为“posit”。与浮点位 串不同,在某些条件下,posit可允许比具有相同位宽度的浮点数更宽的动态范围和更高 的准确度(例如,精确度)。这可允许由计算系统执行的运算在使用posit时以比使用浮点 数时更高的速率(例如,更快)执行,这转而可通过例如减少在执行运算时使用的时钟周 期的数目从而减少执行此类运算时的处理时间和/或消耗的功率来提高计算系统的性能。 另外,与浮点数相比,在计算系统中使用posit可实现更高的准确度和/或精确度,这与 某些方法(例如,依赖于浮点格式位串的方法)相比可进一步改进计算系统的功能。

31.posit可基于包含于posit中的总位量和/或整数集或位集的量而在精确度和准确度中 高度变化。另外,posit可产生广泛的动态范围。在某些条件下,posit的准确度、精确 度和/或动态范围可大于浮动或其它数字格式的准确度、精确度和/或动态范围,如本文 中更详细描述。posit的可变准确度、精确度和/或动态范围可例如基于其中将使用posit 的应用而加以操纵。另外,posit可减小或消除溢出、下溢、nan和/或与浮点数和其它 数字格式相关联的其它极端情况。此外,与浮点数或其它数字格式相比,使用posit可 允许使用更少的位来表示数值(例如,数)。

32.在一些实施例中,这些特征可允许高度可再配置posit,与依赖于浮点数或其它数字 格式的方法相比,这可提供改进的应用性能。另外,与浮点数或其它数字格式相比,posit 的这些特征可在机器学习应用中提供改进的性能。例如,在计算性能至关重要的机器学 习应用中,可使用posit来训练网络(例如,神经网络),其准确度和/或精确度与浮点数 或其它数字格式相同或比其更高,但使用比浮点数或其它数字格式更少的位。另外,可 使用具有比浮点数或其它数字格式更少的位(例如,更小位宽)的posit来实现机器学习情 形中的推断运算。通过使用与浮动或其它数字格式相比更少的位实现相同或增强的结 果,posit的使用可因此减少执行运算的时间量和/或减小应用中所需的存储器空间的量, 这可改进其中采用posit的计算系统的整体功能。

33.本文中的实施例涉及用于posit运算的加速电路系统。在一些实施例中,加速电路 系统可实施于现场可编程门阵列(fpga)上。控制逻辑可耦合到加速电路系统或为其组 件。外围组件互连高速(pcie)接口可耦合到加速电路系统以与主机通信。例如,pcie接 口可用以将数据(例如,数据阵列)传送到耦合到加速电路系统的本地存储器。本地存储 器可在包含加速电路系统的存储器装置内部、在包含加速电路系统的存储器装置外部或 这两者。来自主机的命令可经由pcie接口传送到加速电路系统。例如,来自主机的命 令可控制数据阵列的处理(例如,执行算术运算、逻辑运算或这两者)。来自处理数据阵 列的结果可写入到本地存储器。来自主机的命令可由耦合到加速电路系统的处理装置解 译。例如处理装置可配置成控制以unum或posit格式格式化的操作数的检索且经由直接 存储器存取(dma)控制器传送结果。处理装置可配置成控制由加速电路系统对数据的处 理。在一些实施例中,处理装置可以是高速缓冲存储器相干精简指令集计算装置,例如 精简指令集计算机(risc)risc

‑

v装置。

34.来自主机的命令可放置于处理装置的队列(例如,本文进一步描述的命令缓冲器)

中。 从主机到处理装置的命令的非限制性实例可包含将数据块从主机的存储器传送到本地 存储器,或从本地存储器传送到主机的存储器,并处理本地存储器中的数据。处理装置 可配置成“就地”处理数据。

35.在一些实施例中,可在可耦合到加速电路系统的dma控制器处接收指示执行将第 一位串写入到驻存于加速电路系统上的第一缓冲器的操作的信令。如本文中所使用,术 语“驻存于

……

上”是指某物在物理上位于特定组件上。例如,处理单元“驻存于”存 储器装置“上”是指处理单元在物理上位于存储器装置上的情况。术语“驻存于

……

上

”ꢀ

可在本文中与例如“部署于

……

上”或“位于

……

上”的其它术语互换使用。加速电路 系统可配置成对以unum或posit格式格式化的位串执行算术运算、逻辑运算或这两者。 可在dma控制器处接收指示执行将第二位串写入到驻存于加速电路系统上的第二缓冲 器的操作的信令。可将指示待使用写入到第一缓冲器的第一位串和写入到第二缓冲器的 第二位串执行算术运算、逻辑运算或这两者的信令传输到加速电路系统。指示算术运算、 逻辑运算或这两者的结果的信令可传输到dma控制器。

36.在一些实施例中,可耦合到主机的存储器装置可配置成从主机接收指示用以对以 unum或posit格式格式化的位串执行算术运算、逻辑运算或这两者的主机级指令的信令。 存储器装置可配置成将指示用以执行算术运算、逻辑运算或这两者的主机级指令的信令 解析为指示用以执行与算术运算、逻辑运算或这两者相关联的子运算的机器级指令的信 令。存储器装置可配置成根据指示机器级指令的信令而使用指示位串的信令执行子运 算。

37.在本公开的以下详细描述中,参考形成本公开的一部分的附图,且所述附图中通过 图示的方式展示可实践本公开的一或多个实施例的方式。足够详细地描述这些实施例以 使得所属领域的一般技术人员能够实践本公开的实施例,且应理解,可利用其它实施例, 且可在不脱离本公开的范围的情况下进行工艺、电气和结构改变。

38.如本文中所使用,例如“x”、“y”、“n”、“j”、“r”等特定地关于图式中的附图标 号的指定符指示可包含多个如此指定的特定特征。还应理解,本文中所使用的术语仅仅 是为了描述具体实施例且并不意图为限制性的。如本文中所使用,除非上下文另外明确 规定,否则单数形式“一(a/an)”和“所述(the)”可包含单个指示物和多个指示物两者。 另外,“多个”、“至少一个”和“一或多个”(例如,多个存储器组)可指一或多个存储器 组,而“多个”意指超过一个此类事物。此外,贯穿本技术以许可的意义(即,有可能、 能够),而非以强制性的意义(即,必须)使用单词“可(can/may)”。

39.术语“包含”和其派生词指“包含但不限于”。视上下文而定,术语“耦合 (coupled/coupling)”意指物理上直接或间接连接或用于存取和移动(传输)命令和/或数据。 视上下文而定,术语“位串”、“数据”和“数据值”在本文中可互换地使用且可具有相 同含义。术语“驻存于

……

上”是指一或多个组件在物理上安置于一或多个不同组件上 的情况。此外,本文中可互换地使用术语“数据”、“多个位”和“位串”,且取决于上 下文,术语“数目”可指位串或多个位。

40.本文中的图式遵循编号定则,其中第一一或多个数字对应于图式编号,且剩余的数 字识别图式中的元件或组件。可通过使用类似数字来识别不同图式之间的类似元件或组 件。例如,120可参考图1中的元件“20”,且类似元件在图2中可表示为220。通常在 本文中可用单个元件符号指代一组或多个类似元件或组件。例如,多个参考元件433

‑

1、 433

‑

2、

……

、433

‑

n可总体称为433。如应了解,可添加、交换和/或去除本文中的各种 实施例中展示的元件,以提供本公开的多个额外实施例。另外,图式中提供的元件的比 例和/或相对尺度意图说明本公开的某些实施例,且不应被视作限制性意义。

41.图1为根据本公开的多个实施例的呈包含设备100的计算系统形式的另一功能框 图,所述设备包含主机102和存储器装置104。如本文中所使用,“设备”可指但不限于 多种结构或结构的组合中的任何一种,例如电路或电路系统、一或多个裸片、一或多个 模块、一或多个装置或一或多个系统。加速电路系统120可类似于图2a和2b中所示出 的加速电路系统220。类似地,主机102可类似于图2a和2b中所示出的主机202,存 储器装置104可类似于图2a和2b中所示出的存储器装置204,且存储器阵列130可类 似于图2a和2b中所示出的存储器阵列230。组件(例如,主机102、加速电路系统120、 逻辑电路系统122、存储器资源124和/或存储器阵列130等)中的每一个可在本文中单独 地称为“设备”。

42.主机102可经由一或多个信道103、105以通信方式耦合到存储器装置104。信道 103、105可以是允许位串、数据和/或命令在主机102与存储器装置105之间传送的接 口或其它物理连接。例如,开始待由加速电路系统120执行的运算(例如,将呈浮点格式 的位串转换为呈posit格式的位串的运算,以及对呈posit格式的位串的后续算术和/或逻 辑运算)的命令可经由信道103、105从主机传送。应注意,在一些实例中,加速电路系 统120可在不存在来自主机102的介入命令的情况下响应于经由信道103、105中的一 或多个从主机102传送的开始命令而执行运算。也就是说,一旦加速电路系统120从主 机102接收到用以开始执行运算的命令,就可由加速电路系统120在不存在来自主机102 的额外命令的情况下执行运算。

43.在一些实施例中,可在不妨碍主机102的情况下产生位串(例如,posit位串)和/或将 其存储在存储器阵列130中。例如,可在不从主机102接收多个命令的情况下产生位串 和/或将其存储在存储器阵列130中。换句话说,在一些实施例中,主机102可将单个命 令发送到存储器装置以请求使用一或多个位串执行运算。响应于接收到请求执行运算的 命令,存储器装置104(例如,控制器110、加速电路系统120或存储器装置104的其它 组件)可在不存在来自主机102的额外命令的情况下执行运算和/或检索所存储的运算结 果。这可减少信道103/105上的运输量,所述运输量的减少可提高与主机102和/或存储 器装置104相关联的计算装置的性能。

44.如图1所示,存储器装置104可包含寄存器存取组件106、高速接口(hsi)108、控 制器110、一或多个扩展行地址(xra)组件112、主存储器输入/输出(i/o)电路系统114、 行地址选通(ras)/列地址选通(cas)链控制电路系统116、ras/cas链组件118、加速电 路系统120和存储器阵列130。如图1所示,加速电路系统120位于物理上不同于存储 器阵列130的存储器装置104的区域中。也就是说,在一些实施例中,加速电路系统120 位于存储器阵列130的外围位置中。

45.寄存器存取组件106可促进从主机102到存储器装置104以及从存储器装置104到 主机102的位串传送和提取。例如,寄存器存取组件106可存储对应于待从存储器装置 104传送到主机102或从主机102传送到存储器装置104的位串的例如存储器地址的地 址(或促进地址的查找)。在一些实施例中,寄存器存取组件106可促进传送和提取待由 加速电路系统120运算的位串,和/或寄存器存取组件106可促进传送和提取已由加速电 路系统120运

算以传送到主机102的位串。

46.hsi 108可在主机102与存储器装置104之间提供接口以用于穿过信道105的位串、 命令和/或数据。hsi 108可以是双倍数据速率(ddr)接口,例如ddr3、ddr4、ddr5 等接口。然而,实施例不限于ddr接口,且hsi 108可以是四倍数据速率(qdr)接口、 外围组件互连(pci)接口(例如,外围组件互连高速(pcie))接口或用于在主机102与存储 器装置104之间传送位串、命令和/或数据的其它合适接口。

47.控制器110可负责执行来自主机102的指令,并存取加速电路系统120和/或存储器 阵列130。控制器110可以是状态机、定序器或某一其它类型的控制器。控制器110可 从主机102(例如,经由hsi 108)接收命令,且基于所接收的命令控制加速电路系统120 和/或存储器阵列130的运算。在一些实施例中,控制器110可从主机102接收命令以使 用加速电路系统120执行运算。响应于接收到此类命令,控制器110可指示加速电路系 统120开始执行一或多个运算。

48.在非限制性实例中,控制器110可指示加速电路系统120执行运算以检索存储在存 储器阵列130中的一或多个位串和/或存储在存储器阵列130中的表示在一或多个位串之 间执行的运算的结果的所得位串。例如,控制器可从主机104接收请求执行一或多个位 串之间的运算的命令,且将命令发送到加速电路系统120以执行运算。加速电路系统120 (例如,驻存于加速电路系统120上的状态机,例如本文中在图2b中所示出的状态机223) 可确定所请求运算的结果是否存储在存储器阵列130中、确定存储器阵列130中存储所 请求运算的结果的地址和/或从存储器阵列130检索所请求运算的结果。加速电路系统 120和/或控制器110可随后使所请求运算的结果传送到主机102或在存储器阵列130外 部的其它电路系统。

49.在一些实施例中,控制器110可以是全域处理控制器,且可为存储器装置104提供 功率管理功能。功率管理功能可包含对由存储器装置104和/或存储器阵列130消耗的功 率的控制。例如,控制器110可控制提供到存储器阵列130的各组的功率,以在存储器 装置104的操作期间控制存储器阵列130的哪些组在不同时间操作。这可包含在向存储 器阵列130的其它组提供功率时关闭存储器阵列130的某些组以优化存储器装置130的 功耗。在一些实施例中,控制存储器装置104的功耗的控制器110可包含控制到存储器 装置的各个核心,例如到加速电路系统120等的功率。

50.一或多个xra组件112预期提供额外功能(例如,外围放大器),所述额外功能感测 (例如,读取、存储、高速缓存)阵列中的存储器单元的数据值且不同于存储器阵列130。 xra组件112可包含锁存器和/或寄存器。例如,额外锁存器可包含于“xra组件112

”ꢀ

中。xra组件112的锁存器可位于存储器装置104的存储器阵列130的外围上(例如, 在一或多个存储器单元组的外围上)。

51.主存储器输入/输出(i/o)电路系统114可促进位串、数据和/或命令到和从存储器阵 列130的传送。例如,主存储器i/o电路系统114可促进将位串、数据和/或命令从主机 102和/或加速电路系统120传送到存储器阵列130和传送来自存储器阵列的位串、数据 和/或命令。在一些实施例中,主存储器i/o电路系统114可包含可将位串、数据块等从 加速电路系统120传送到存储器阵列130(且反之亦然)的一或多个直接存储器存取 (dma)组件。

52.在一些实施例中,主存储器i/o电路系统114可促进将一或多个位串从存储器阵列

130传送到加速电路系统120,以使得加速电路系统120可对一或多个位串执行运算。 类似地,主存储器i/o电路系统114可促进将已由加速电路系统120执行一或多个运算 的位串传送到存储器阵列130。如本文中更详细描述,运算可包含用以将根据浮点标准 格式化的位串转换为格式化为posit(且反之亦然)的位串的运算、对格式化为posit的位 串执行的算术运算、对格式化为posit的位串执行的逻辑运算等。

53.如上所述,可存储和/或从存储器阵列130检索posit位串(例如,数据)。在一些实 施例中,主存储器i/o电路系统114可促进posit位串到和/或从存储器阵列130的存储 和/或检索。例如,可启用主存储器i/o电路系统114以将posit位串传送到待存储的存 储器阵列130,和/或主存储器i/o电路系统114可促进响应于例如来自控制器110和/ 或加速电路系统120的命令而从存储器阵列130检索posit位串(例如,表示一或多个posit 位串操作数之间的所执行运算的posit位串)。

54.行地址选通(ras)/列地址选通(cas)链控制电路系统116和ras/cas链组件118可 与存储器阵列130结合使用以锁存行地址和/或列地址以开始存储器周期。在一些实施例 中,ras/cas链控制电路系统116和/或ras/cas链组件118可解析存储器阵列130的 行地址和/或列地址,与存储器阵列130相关联的读取和写入操作将在所述行地址和/或 列地址处开始或终止。例如,在使用加速电路系统120完成运算后,ras/cas链控制电 路系统116和/或ras/cas链组件118可锁存和/或解析存储器阵列130中的特定位置, 已由加速电路系统120操作的位串将存储到所述位置。类似地,ras/cas链控制电路系 统116和/或ras/cas链组件118可锁存和/或解析存储器阵列130中的特定位置,在加 速电路系统120对位串执行运算之前,位串将从所述位置传送到加速电路系统120。

55.在一些实施例中,ras/cas链控制电路系统116和ras/cas链组件118可与存储 器阵列130结合使用以锁存行地址和/或列地址以开始从存储器阵列130检索一或多个位 串的操作。例如,响应于加速电路系统120(例如,图2b中所示出且驻存于加速电路系 统220上的状态机223)请求存储于存储器阵列130的特定地址处的位串,ras/cas链 控制电路系统116和ras/cas链组件118可锁存对应于一或多个位串的行地址和/或列 地址以促进从存储器阵列130检索所请求的一或多个位串。

56.如结合图2a和2b且下文结合图5更详细地描述,加速电路系统120可配置成接收 具有第一格式的位串(例如,呈浮点格式的位串)、将位串转换为第二格式(例如,将位串 转换为例如posit格式的通用数字格式)和/或使用具有第二格式的一或多个位串执行例如 算术和/或逻辑运算的运算。在一些实施例中,加速电路系统120可使具有第二格式的一 或多个位串和/或包含算术和/或逻辑运算的结果的一或多个位串存储于存储器阵列130 的数据结构(例如,本文中在图6中所示出的数据结构634)中。

57.加速电路系统120可包含逻辑电路系统(例如,图2a和2b中所示出的逻辑电路系 统222)和一或多个存储器资源(例如,图2a和2b中所示出的存储器资源224)。位串可 由加速电路系统120从例如主机102和/或存储器阵列130接收,且由加速电路系统120 存储于例如加速电路系统120的存储器资源中。加速电路系统(例如,加速电路系统120 的逻辑电路系统)可执行位串的运算(或使对其执行运算),如本文中结合图5更详细地描 述。

58.如结合图3和4a

‑

4b更详细描述,posit可提供改进的准确度,且可能需要比以浮 点格式表示的对应位串更少的存储空间(例如,可含有较少数目个位)。因此,通过使用 加

速电路系统120将浮点位串转换为posit位串,与仅利用浮点位串的方法相比,可改 进存储器装置102的性能,这是因为可更快地对posit位串执行运算(例如,因为呈posit 格式的位串较小且因此需要较少时间和/或处理资源来执行运算),且因为在存储器装置 102中需要较少存储器空间来存储呈posit格式的位串,这可释放存储器装置102中的额 外空间以用于其它位串、数据和/或待执行的其它运算。另外,通过将位串存储在存储器 阵列130的数据结构中并随后检索,可随后快速存取位串以用于其它运算和/或由例如主 机102上运行的应用程序使用,其使用方式比每当请求此类运算的结果时需要执行算术 和/或逻辑运算的方法更有效。此外,与一些方法相比,执行算术和/或逻辑运算可能需 要较少的时钟周期,因为可从存储器阵列130检索位串操作数之间的算术和/或逻辑运算 的结果,这与每当请求此类运算的结果时执行位串操作数之间的运算的方法形成对比。

59.加速电路系统120可对所得posit位串执行(或使执行)算术和/或逻辑运算。算术运 算可包含加法、减法、乘法、除法、融合乘法加法、乘积累加、点积单元、大于或小于、 绝对值(例如,fabs())、快速傅立叶变换、反快速傅立叶变换、sigmoid函数、卷积、平 方根、指数和/或修正线性单元(relu),以及例如正弦、余弦、正切等的三角运算,而逻 辑运算可包含与(and)、或(or)、异或(xor)、非(not)等。如将了解,前述的运算列表 并不意欲是穷尽性的,前述的运算列表也不意欲是限制性的,且加速电路系统120可配 置成执行(或使执行)其它算术和/或逻辑运算。如本文中所描述,在此类运算中使用的操 作数(例如,位串操作数)和/或此类运算的结果可存储在存储器阵列130中,且可随后响 应于来自加速电路系统120的命令而从存储器阵列130检索。

60.在一些实施例中,加速电路系统120可结合一或多个机器学习算法的执行来执行以 上列举的运算。例如,加速电路系统120可执行与一或多个神经网络相关的操作。神经 网络可允许历经时间来训练算法以基于输入信号确定输出响应。举例来说,随时间推移, 神经网络可基本上习得更好地最大化完成特定目标的机率。这在机器学习应用中可能是 有利的,因为神经网络可历经时间利用新数据加以训练以实现更好地最大化完成特定目 标的机率。在许多情况下,可随时间推移训练神经网络以改进特定任务和/或特定目标的 操作。

61.然而,在一些方法中,机器学习(例如,神经网络训练)可以是处理密集型的(例如, 可能消耗大量计算机处理资源)和/或可以是时间密集型的(例如,可能需要执行消耗多个 周期的冗长计算)。相比之下,通过使用加速电路系统120来执行此类运算,例如通过对 已由加速电路系统120转换为posit格式的位串执行此类运算,在执行运算时消耗的处 理资源量和/或时间量可相较于使用呈浮点格式的位串来执行此类运算的方法而减小。此 外,通过将对已转换为posit格式的位串的运算结果存储在存储器阵列130中以用于后 续检索,由于运算已执行,所以对于结果的后续请求,可甚至进一步减少执行运算时所 消耗的处理资源量和/或时间量。

62.例如,存储器阵列130可以是dram阵列、sram阵列、stt ram阵列、pcram 阵列、tram阵列、rram阵列、nand快闪阵列和/或nor快闪阵列,但实施例不限 于这些特定实例。存储器阵列130可充当用于图1中所展示的计算系统100的主存储器。 在一些实施例中,存储器阵列130可配置成存储由加速电路系统120运算的位串(例如, 所得位串)和/或存储待传送到加速电路系统120的位串。

63.在一些实施例中,存储器阵列130配置成存储待用作执行算术运算或逻辑运算或这 两者中的操作数的多个位串。耦合到存储器阵列130的控制器110可配置成接收待使用 一或多个位串执行算术运算或逻辑运算或这两者的请求。可从在存储器装置104外部的 电路系统(例如,主机102)接收所述请求。控制器110可配置成确定待在执行算术运算 或逻辑运算中使用的一或多个位串的位大小,且响应于确定执行算术运算或逻辑运算或 这两者而需要一或多个位串的位大小小于预定位大小,从而使用存储于存储器阵列130 中的多个位串中的位串执行算术运算或逻辑运算或这两者。

64.在一些实施例中,耦合到存储器阵列130和加速电路系统120的控制器110可配置 成响应于确定执行算术运算或逻辑运算或这两者而需要一或多个位串的位大小大于预 定位大小,将命令发送到加速电路系统以使加速电路系统执行算术运算或逻辑运算或这 两者。在一些实施例中,预定位大小可以是16位或更小,然而,实施例不限于特定位 大小。

65.如本文中更详细描述,加速电路系统120可配置成将表示算术运算或逻辑运算或这 两者的结果的位串转换为不同于存储于存储器阵列130中的多个位串的格式的格式。例 如,待用作执行算术运算或逻辑运算或这两者中的操作数的多个位串存储于存储器阵列 130中的数据结构中。

66.图2a为根据本公开的多个实施例的呈包含设备的计算系统200形式的功能框图, 所述设备包含主机202和存储器装置204。存储器装置204可包含一或多个存储器模块 (例如,单列直插式存储器模块、双列直插式存储器模块等)。存储器装置204可包含易 失性存储器和/或非易失性存储器。在多个实施例中,存储器装置204可包含多芯片装置。 多芯片装置可包含多个不同的存储器类型和/或存储器模块。例如,存储器系统可包含任 何类型的模块上的非易失性或易失性存储器。另外,组件(例如,主机202、加速电路系 统220、逻辑电路系统222、存储器资源224和/或存储器阵列230)中的每一个可在本文 中单独地称为“设备”。尽管图2a中未明确地展示,但存储器装置204可耦合到一或多 个媒体装置,例如一或多个固态驱动器、快闪媒体装置等。

67.存储器装置204可提供用于计算系统200的主存储器或可在整个计算系统200中用 作额外存储器或存储装置。存储器装置204可包含一或多个存储器阵列230(例如,存储 器单元阵列),所述存储器阵列可包含易失性和/或非易失性存储器单元。例如,存储器 阵列230可以是具有nand架构的快闪阵列。实施例不限于特定类型的存储器装置。例 如,存储器装置204可包含ram、rom、dram、sdram、pcram、rram和快闪 存储器等等。

68.在存储器装置204包含非易失性存储器的实施例中,存储器装置204可包含快闪存 储器装置,例如nand或nor快闪存储器装置。然而,实施例不限于此,且存储器装 置204可包含其它非易失性存储器装置,例如非易失性随机存取存储器装置(例如, nvram、reram、feram、mram、pcm)、例如可变电阻(例如,3

‑

d交叉点(3d xp) 存储器装置)的“新兴”存储器装置、包含自选存储器(ssm)单元阵列的存储器装置等, 或其组合。可变电阻存储器装置可与可堆叠交叉网格化数据存取阵列一起基于体电阻的 改变而执行位存储。另外,与多个基于快闪的存储器相比,可变电阻非易失性存储器可 执行就地写入操作,其中可在不预先擦除非易失性存储器单元的情况下对非易失性存储 器单元进行编程。与基于快闪的存储器和可变电阻存储器相比,自选存储器单元可包含 具有充当存储器单元的开关和存储元件两者的单个硫族化物材料的存储器单元。

69.如图2a所示,主机202可以耦合到存储器装置204。在多个实施例中,存储器装 置204可经由一或多个信道(例如,信道203)耦合到主机202。在图2a中,存储器装置 204经由信道203耦合到主机202,且存储器装置204的加速电路系统220经由信道207 耦合到存储器阵列230。主机202可以是主机系统,例如个人膝上型计算机、台式计算 机、数码相机、智能电话、存储卡读卡器和/或具物联网功能的装置,以及其它各种类型 的主机,且可包含存储器存取装置,例如处理器(或处理装置)。所属领域的一般技术人 员将理解,“处理器”可以是一或多个处理器,例如平行处理系统、多个协同处理器等。

70.主机202可包含系统主板和/或底板,且可包含多个处理资源(例如,一或多个处理 器、微处理器或一些其它类型的控制电路系统)。系统200可包含单独的集成电路或主机 202、存储器装置204两者,且存储器阵列230可在同一集成电路上。例如,系统200 可以是服务器系统和/或高性能计算(hpc)系统和/或其一部分。虽然图2a中所示的实例 示出具有冯

·

诺依曼(von neumann)架构的系统,但本公开的实施例可实施于非冯

·

诺依曼 架构中,所述非冯

·

诺依曼架构可不包含通常与冯

·

诺依曼架构相关联的一或多个组件(例 如,中央处理单元(cpu)、算术逻辑单元(alu)等)。

71.存储器装置204可包含加速电路系统220,所述加速电路系统可包含逻辑电路系统 222和存储器资源224。可以集成电路的形式提供逻辑电路系统222,例如专用集成电路 (asic)、现场可编程门阵列(fpga)、芯片上系统或配置成执行本文中更详细地描述的运 算的硬件和/或电路系统的其它组合。例如,逻辑电路系统222可配置成接收呈第一格式 的一或多个位串(例如,呈浮点格式的多个位)、将一或多个位串转换为第二格式(例如, 以posit格式对多个位进行编码)和/或使用具有第二格式的一或多个位串执行例如算术和 /或逻辑运算的运算。如本文中所使用,呈第二格式的一或多个位串(例如,呈posit格式 的一或多个位串)包含至少一个称为“符号”的位、一组称为“底数”的位、一组称为“指 数”的位和一组称为“尾数”(或有效数字)的位。本文中结合图3和4a

‑

4b更详细地描 述位的符号、底数、指数和尾数集的实例。

72.运算可包含转换运算以将浮点位串(例如,浮点数)转换为posit格式的位串,且反之 亦然。一旦将浮点位串转换为posit格式的位串,逻辑电路系统222就可配置成使用posit 位串执行(或使执行)算术运算和/或运算。算术运算可包含加法、减法、乘法、除法、融 合乘法加法、乘积累加、点积单元、大于或小于、绝对值(例如,fabs())、快速傅立叶 变换、反快速傅立叶变换、sigmoid函数、卷积、平方根、指数和/或修正线性单元(relu), 以及例如正弦、余弦、正切等的三角运算,而逻辑运算可包含例如and、or、xor、 not等的逻辑运算。如将了解,前述的运算列表并不意欲是穷尽性的,前述的运算列表 也不意欲是限制性的,且加速电路系统222可配置成执行(或使执行)其它算术和/或逻辑 运算。

73.逻辑电路系统222可包含alu。alu可包含用以对整数二进制位串(例如,posit格 式的位串)执行例如上文所描述的运算的运算(例如,算术运算、逻辑运算、逐位运算等) 的电路系统(例如,硬件、逻辑、一或多个处理装置等)。

74.加速电路系统220可进一步包含可以通信方式耦合到逻辑电路系统222的存储器资 源224。存储器资源224可包含易失性存储器资源、非易失性存储器资源或易失性与非 易失性存储器资源的组合。在一些实施例中,存储器资源可以是随机存取存储器(ram), 例如静态随机存取存储器(sram)。然而,实施例不限于此,且存储器资源可以是高速 缓冲存

储器、一或多个寄存器、nvram、reram、feram、mram、pcm、例如上 述可变电阻存储器装置等的“新兴”存储器装置或其组合。

75.加速电路系统220可经由一或多个信道207以通信方式耦合到存储器阵列230。存 储器阵列230可以是例如dram阵列、sram阵列、stt ram阵列、pcram阵列、 tram阵列、rram阵列、nand快闪阵列和/或nor快闪阵列。阵列230可包括以通 过存取线(其可在本文中称为字线或选择线)耦合的行和通过感测线(其可在本文中称为 数据线或数字线)耦合的列布置的存储器单元。虽然图2a中展示单个阵列230,但实施 例不限于此。例如,存储器装置204包含多个存储器阵列230(例如,dram单元、nand 快闪单元等的多组)。

76.图2a的实施例可包含以免模糊本公开的实施例而未示出的额外电路系统。例如, 存储器装置204可包含地址电路系统以锁存i/o连接上提供的地址信号通过i/o电路。 地址信号可由行解码器和列解码器接收和解码以存取存储器装置204和/或存储器阵列 230。所属领域的技术人员应了解,地址输入连接的数目可取决于存储器装置204和/或 存储器阵列230的密度和架构。

77.图2b为根据本公开的多个实施例的呈包含设备200的计算系统形式的另一功能框 图,所述设备包含主机202和存储器装置204。如图2b中所示,设备200可包含主机 202,所述主机可经由通信路径203以通信方式耦合到存储器装置204。存储器装置204 可包含加速电路系统220,所述加速电路系统可包含状态机223且任选地包含存储器资 源224。加速电路系统220可经由通信路径207以通信方式耦合到存储器阵列230。组 件(例如,主机202、加速电路系统220、状态机223、存储器资源224和/或存储器阵列 230)中的每一个可在本文中单独地称为“设备”。

78.在图2b中所示的实施例中,其中逻辑电路系统222包括状态机223,所述状态机 223可配置成执行指定指令集以例如写入、读取、复制和/或擦除存储于存储器阵列230 中的位串(例如,数据)。例如,如本文中更详细描述,状态机223可执行指令以从存储 器阵列230的一或多个行和/或列读取数据以检索存储于存储器阵列230中的数据。如结 合图1更详细地描述,数据可尤其包含一或多个posit位串操作数和/或一或多个运算(例 如,算术和/或逻辑运算)结果

79.通过利用配置成执行指定指令集以写入和/或从存储器阵列230检索posit位串的状 态机223,与一些方法相比,可实现存储器装置204性能的改进,这是因为可通过将此 类运算的一或多个结果存储于存储器阵列230中且直接从存储器阵列230检索运算的一 或多个结果来减少执行存储于存储器阵列230中的位串之间的运算的费时型和/或计算 资源密集型过程的量。

80.在一些实施例中,状态机223可确定其中存储相关posit位串的存储器阵列230中 的地址。例如,状态机223可确定存储器阵列230中存储一或多个posit位串操作数的 行和/或列地址和/或存储表示一或多个posit位串操作数之间的算术和/或逻辑运算的执 行的所得posit位串的行和/或列地址。状态机223可随后发送命令或请求以检索存储于 存储器阵列230中的地址处的一或多个posit位串和/或使检索到的posit位串传送到主机 202、耦合到存储器装置202的媒体装置(例如,固态驱动器、快闪存储器装置等)或在存 储器阵列230外部的其它电路系统。

81.图3为具有es指数位的n位通用数字或“unum”的实例。在图3的实例中,n位 unum为

posit位串331。如图3中所示,n位posit 331可包含一组符号位(例如,符号位 333)、一组底数位(例如,底数位335)、一组指数位(例如,指数位337)和一组尾数位(例 如,尾数位339)。尾数位339可在替代方案中称为“分数部分”或“分数位”,且可表 示小数点后的位串的一部分(例如,数字)。

82.符号位333可以是用于正数的零(0)和用于负数的一(1)。下文结合表1描述底数位 335,所述表展示(二进制)位串及其相关数值含义k。在表1中,数值含义k由位串的延 行长度确定。表1的二进制部分中的字母x指示位值与底数的确定不相关,因为(二进制) 位串响应于连续位翻转或当到达位串的结尾时而终止。例如,在(二进制)位串0010中, 位串响应于零翻转到一且随后回到零而终止。因此,最后的零与底数不相关且对于底数 考虑的全部是前导相同位和终止位串的第一相对位(如果位串包含此类位)。

83.二进制00000001001x01xx10xx110x11101111数字(k)

‑4‑3‑2‑

10123

84.表1

85.在图3中,底数位335r对应于位串中的相同位,而底数位对应于终止位串的 相反位。例如,对于表1所示的数字k值

‑

2,底数位r对应于前两个前导零,而一或多 个底数位对应于一。如上所述,对应于由表1中的x表示的数字k的最终位与底数不 相关。

86.如果m对应于位串中相同位的数目,则如果位为零,那么k=

‑

m。如果位为一,那 么k=m

‑

1。这示出在表1中,其中例如(二进制)位串10xx具有单个一且k=m

‑

1=1

ꢀ‑

1=0。类似地,(二进制)位串0001包含三个零,因此k=

‑

m=

‑

3。底数可指示useed

k

的比例因数,其中以下表2中展示used的若干实例值。

87.es01234used222=442=16162=2562562=65536

88.表2

89.指数位337对应于作为无符号数的指数e。与浮点数相比,本文中所描述的指数位 337可不具有与其相关联的偏置。因此,本文中所描述的指数位337可表示以因数2

e

进 行调整。如图3中所展示,取决于n位posit 331的底数位335右方保留多少位,可存在 多达es个指数位(e1、e2、e3、

…

、e

es

)。在一些实施例中,这可允许n位posit 331的准 确度逐渐变小,其中在量值上更接近一的数字的准确度比极大或极小的数字更高。然而, 由于在某些类型的运算中可不频繁地使用极大或极小数,因此图3所示的n位posit 331 的逐渐变小的准确度在广泛范围的情形下可以是合乎需要的。

90.尾数位339(或分数位)表示可以是位于指数位337右方的n位posit 331的部分的任 何额外位。类似于浮点位串,尾数位339表示可类似于分数1.f的分数f,其中f包含一 后的小数点右方的一或多个位。然而,与浮点位串相比,在图3中所展示的n位posit 331 中,“隐藏位”(例如,一)可始终是一(例如,整体),而浮点位串可包含具有“隐藏位

”ꢀ

零(例如,0.f)的次正规数。

91.图4a为用于3位posit的正值的实例。在图4a中,仅投影实数的右半部分,然而, 应了解,对应于图4a中所展示的其正对应值的负投影实数可存在于曲线上,所述曲线 表示围绕图4a中所展示的曲线的y轴的变换。

92.在图4a的实例中,es=2,因此posit 431

‑

1的精确度可通过将 位附加到位串而增大,如图4b中所展示。例如,将具有值一(1)的位附加到posit 431

‑

1 的位串增大如由图4b中的posit 431

‑

2所展示的posit 431

‑

1的准确度。类似地,将具有 值一的位附加到图4b中的posit 431

‑

2的位串增大如由图4b中所展示的posit 431

‑

3所 展示的posit 431

‑

2的准确度。以下是可用于将位附加到图4a中所展示的posit 431

‑

1的 位串以获得图4b中所示出的posit 431

‑

2、431

‑

3的内插规则的实例。

93.如果maxpos是posit 431

‑

1、431

‑

2、431

‑

3的位串的最大正值且minpos是posit 431

‑

1、431

‑

2、431

‑

3的位串的最小值,那么maxpos可等于useed且minpos可等于在maxpos 与

±

∞之间,新位值可以是maxpos*useed,且在零与minpos之间,新位值可以是这些新位值可对应于新底数位335。在现有值x=2

m

且y=2

n

之间,其中m和n相差大 于一,新位值可由对应于新指数位337的几何平均值给出:如果新位 值在现有x与紧接其的y值之间的中间位置,那么新位值可表示对应于新尾数位339的 算术平均值

94.图4b为使用两个指数位的posit构造的实例。在图4b中,仅投影实数的右半部分, 然而,应了解,对应于图4b中所展示的其正对应值的负投影实数可存在于曲线上,所 述曲线表示围绕图4b中所展示的曲线的y轴的变换。图4b所示的posit 431

‑

1、431

‑

2、 431

‑

3各自仅包含两个异常值:当位串的所有位均为零时的零(0),以及当位串为所有零 后的一(1)时的

±

∞。应注意,图4中展示的posit 431

‑

1、431

‑

2、431

‑

3的数值精确地为 useed

k

。也就是说,对于由底数(例如,上文结合图3所描述的底数位335)表示的k值的 幂,图4中展示的posit 431

‑

1、431

‑

2、431

‑

3的数值精确地为useed。在图4b中,posit 431

‑

1具有es=2,因此posit 431

‑

2具有es=3,因此且posit 431

‑

3具有es=4,因此

95.作为将位添加到3位posit 431

‑

1以产生图4b的4位posit 431

‑

2的说明性实例,useed =256,因此对应于256的useed的位串具有附加到其上的额外底数位且之前为16的useed 具有附加到其上的终止底数位如上文所描述,在现有值之间,对应位串具有附加 到其上的额外指数位。例如,数值1/16、1/4、1和4将具有附加到其上的指数位。也就 是说,对应于数值4的最末一是指数位,对应于数值1的最末零是指数位等。此模式可 进一步见于posit 431

‑

3中,所述posit是根据以上规则从4位posit 431

‑

2产生的5位posit。 如果另一位添加到图4b中的posit 431

‑

3以产生6位posit,那么尾数位339将附加到在 1/16与16之间的数值。

96.以下是对posit(例如,posit 431)进行解码以获得其数字等效值的非限制性实例。在 一些实施例中,对应于posit p的位串为

‑2n

‑1到2

n

‑1范围内的无符号整数,k为对应于 底数位335的整数,且e为对应于指数位337的无符号整数。如果尾数位339的集合表 示为{f

1 f2...f

fs

}且f为由1.f

1 f2...f

fs

表示的值(例如,通过尾数位339之后的小数点之 后的一),那么p可由以下等式1给出。

[0097][0098]

等式1

[0099]

下文结合下表3中展示的posit位串0000110111011101提供对posit位串进行解码的 另一说明性实例。

[0100]

符号底数指数尾数0000110111011101

[0101]

表3

[0102]

在表3中,posit位串0000110111011101被分解到其构成位集(例如,符号位333、 底数位335、指数位337和尾数位339)中。由于表3中展示的posit位串中的es=3(例 如,因为存在三个指数位),所以useed=256。因为符号位333是零,所以对应于表3 中展示的posit位串的数值表述的值是正的。底数位335具有对应于值

‑

3的三个连续零 的延行(如上文结合表1所描述)。因此,由底数位335提供的比例因数为256

‑3(例如, useed

k

)。指数位337表示作为无符号整数的五(5)且因此提供2

e

=25=32的额外比例因 数。最后,在表3中作为11011101给出的尾数位339表示作为无符号整数的两百二十 一(221),因此以上作为f给出的尾数位339为使用这些值和等式1,对应于表3 中给出的

[0103]

图5为根据本公开的多个实施例的呈包含设备501的计算系统形式的另一功能框 图,所述设备包含主机502和存储器装置504。存储器装置504可包含实施于现场可编 程门阵列(fpga)上的电路系统。在虚线框540内示出的组件可以是实施于fpga上的电 路系统。然而,本公开的实施例不限于此。

[0104]

存储器装置504可包含处理装置554。在至少一个实施例中,处理装置554可以是 高速缓冲存储器相干精简指令集计算(risc)装置。高速缓冲存储器相干精简指令集计算 装置的非限制性实例为32位risc

‑

v装置。处理装置553可配置成从主机502接收命令。 处理装置553可配置成将指示完成和/或执行来自主机502的命令的信号提供到主机 502。处理装置553可配置成将指示中断的信号提供到主机502。

[0105]

存储器装置504可包含逻辑电路系统522。逻辑电路系统522可类似于结合图2a 所描述的逻辑电路系统222。逻辑电路系统522可耦合到加速电路系统520。然而,本 公开的实施例不限于此。例如,逻辑电路系统522可以是如图2a所示出的加速电路系 统520的组件。加速电路系统520可被称为posit算术逻辑单元(palu)。

[0106]

加速电路系统520可包含配置成从逻辑电路系统522接收数据值的多个缓冲器。配 置成从逻辑电路系统522接收数据值的缓冲器可称为“输入缓冲器(inbuffer)”(例如,输 入缓冲器545)。每一输入缓冲器可配置成存储以unum或posit格式格式化的操作数。操 作数可由位串表示。

[0107]

如由图5所示出,输入缓冲器a 545可配置成存储“操作数a”且输入缓冲器b 546 可配置成存储“操作数b”。操作数a和/或操作数b可以unum或posit格式格式化。 例如,可在

dma控制器542处接收指示执行将第一位串写入到输入缓冲器a 545的操 作和将第二位串写入到输入缓冲器b 546的操作的信令。尽管图5示出两个输入缓冲器 545和546,但本公开的实施例不限于此。例如,加速电路系统520可包含单个输入缓 冲器或多于两个输入缓冲器。在至少一个实施例中,至少一个输入缓冲器可以是先进先 出(fifo)缓冲器。

[0108]

加速电路系统520可包含配置成对由至少一个输入缓冲器存储的至少一个操作数执 行至少一个算术运算、至少一个逻辑运算或两者的电路系统(例如,处理电路系统)。例 如,可将指示待使用写入到输入缓冲器a 545的第一位串和写入到输入缓冲器b 546的 第二位串执行算术运算、逻辑运算或这两者的信令传输到加速电路系统520。如图5所 示出,加速电路系统520可配置成执行运算,包含但不限于加法、减法、乘法、除法、 融合乘法加法、乘积累加、点积单元、大于或小于、绝对值(例如,fabs())、快速傅立 叶变换、反快速傅立叶变换、sigmoid函数、卷积、平方根、指数,以及例如正弦、余 弦、正切等的三角运算、and、or、xor、not等,及其组合。在至少一个实施例中, 加速电路系统520可包含相乘与累积(mac)电路系统548。例如,加速电路系统520可 根据由加速电路系统520所接收的信令来执行算术运算、逻辑运算或这两者。

[0109]

加速电路系统520可包含至少一个缓冲器,所述至少一个缓冲器配置成接收由加速 电路系统520执行至少一个算术运算、至少一个逻辑运算或这两者而得出的数据值。配 置成接收所得数据值的缓冲器可称为“输出缓冲器”(例如,输出缓冲器547)。输出缓 冲器可配置成存储以unum或posit格式格式化的所得数据值。尽管图5示出单个输出缓 冲器547,但本公开的实施例不限于此。例如,加速电路系统520可多于一个输出缓冲 器。在至少一个实施例中,至少一个输出缓冲器可以是fifo缓冲器。指示算术运算、 逻辑运算或这两者的结果的信令可传输到dma控制器542。

[0110]

逻辑电路系统522可包含dma控制器542。dma控制器542可耦合到输入缓冲器 545和546。dma控制器542可耦合到至少一个存储器资源。如由图5所示,dma控 制器542可耦合到互连件551,例如先进可扩展接口(axi)互连件。互连件551可耦合到 多个存储器资源。存储器资源中的至少一个可在存储器装置504内部,例如可扩展ram 553和块ram 555。如本文中所使用,“可扩展ram”是指部署在fpga内的双端口同 步随机存取存储器单元,所述可扩展ram可耦合到多个双端口同步随机存取存储器单 元以增加可扩展ram 553可用的存储位置量。互连件551可耦合到存储器装置504外 部的存储器资源530。外部存储器资源530可类似于分别结合图1和2a

‑

2b描述的存储 器阵列130和存储器阵列230。互连件551可经由存储器控制器550耦合到外部存储器 资源530。外部存储器资源530可以是主存储器。外部存储器资源530的非限制性实例 为双倍数据速率(ddr)存储器,例如ddr3存储器或ddr4存储器。

[0111]

在至少一个实施例中,加速电路系统520可包含存储器控制器,例如dma控制器 542。存储器控制器可耦合到包含至少两个不同存储器组件的存储器。存储器控制器可 配置成至少部分地基于由存储器控制器接收的信令而从存储器的至少两个不同存储器 组件中的特定一个检索第一操作数、第二操作数或这两者。例如,dma控制器542可 配置成从耦合到其的存储器资源中的任一个到输入缓冲器545和546检索至少一个操作 数,所述存储器资源例如可扩展ram 553、块ram 555、外部存储器资源530(例如, 经由存储器控制器550)和其组合。另外,或替代地,为从存储器资源检索操作数,dma 控制器542可配置成从主机502检索操作数。

[0112]

dma控制器542可配置成将所得数据值从输出缓冲器547传递(例如,传送)到耦合 到其的存储器资源中的任一个的至少一个操作数,所述存储器资源例如可扩展ram 553、块ram 555、外部存储器资源530(例如,经由存储器控制器550)和其组合。另外, 或替代地,为了将所得数据值传递到存储器资源,dma控制器542可配置成将所得数 据值传递到主机502。

[0113]

存储器装置504可配置成经由外围组件互连高速(pcie)接口552与主机502通信。

[0114]

在至少一个实施例中,逻辑电路系统522可包含微码控制器544。代替使用加速电 路系统520执行算术运算或逻辑运算,微码控制器544可用以识别算术运算或逻辑运算 的预计算结果。可使用以unum或posit格式格式化的多个操作数来预计算多个算术运算、 多个逻辑运算或这两者的结果。可将预计算结果编译到查找表(lut)中。lut可由微码 控制器544或逻辑电路系统522的其它电路系统存储。微码控制器544可从例如处理装 置554或主机502的cpu的处理装置接收使用多个操作数的特定集合执行多个算术运 算或多个逻辑运算的特定运算的指令。微码控制器544可经由lut识别对应于特定运 算及多个操作数的特定集合的预计算结果中的一个。可使用所识别的结果执行额外的算 术或逻辑运算。

[0115]

存储器装置504可包含如由逻辑电路系统522和加速电路系统520的重叠表示所表 示的逻辑电路系统522和加速电路系统520的多个例子。然而,重叠表示并不意图为逻 辑电路系统522和加速电路系统520的多个例子的物理定向和/或重叠。

[0116]

图6为根据本公开的多个实施例的呈包含设备607的计算系统形式的另一功能框 图,所述设备包含主机602和存储器资源624。存储器资源624可类似于结合图5描述 的可扩展ram 553、块ram 555和/或ddr3存储器530。存储器资源624可配置成经 由pcie接口652与主机602通信。

[0117]

主机602的第一缓冲器,例如数据缓冲器660可配置成存储数据值(例如,数据向量)。 由主机602的数据缓冲器660存储的数据值可传递(例如,传送)到第二缓冲器,例如存 储器资源624的数据缓冲器662。例如,可将指示以unum或posit格式格式化的第一位 串和第二位串的信令从主机602传输到存储器资源624。由存储器资源624的数据缓冲 器662存储的数据值可传递到主机602的数据缓冲器660。

[0118]

可由主机602维持第三缓冲器,即命令缓冲器661。可通过存储器资源624从主机 602接收指示对以通用数字(unum)或posit格式格式化的位串执行算术运算、逻辑运算或 这两者的主机级指令的信令。命令缓冲器661可配置成存储从主机602的cpu传递的 命令。由主机602的命令缓冲器661存储的命令可复制(镜像)到第四缓冲器,即存储器 资源624的命令缓冲器663。例如,可在存储器资源624处对来自主机602的指示使用 以unum格式或posit格式格式化的位串执行算术运算、逻辑运算或这两者的指令的信令 进行镜像。由存储器资源624的命令缓冲器663存储的命令可复制到主机602的命令缓 冲器661。

[0119]

图6示出为risc

‑

v装置的处理装置654可配置成监测存储器资源624的命令缓冲 器623。处理装置654可配置成将由存储器资源624的命令缓冲器663存储的指令解析 为指示执行待由计算电路系统665执行算术运算、逻辑运算或这两者的信号。例如,处 理装置654可将指示执行算术运算、逻辑运算或这两者的主机级指令的信令解析为指示 执行与算术运算、逻辑运算或这两者相关联的子运算的机器级指令的信令。

[0120]

计算电路系统665可包含配置成执行算术运算、逻辑运算或这两者的处理电路系

766

‑

n(共同称为计算电路766)。类似于计算电路系统765,计算电路766中的每一个可 包含缓冲器764和状态机723(例如,fsm)。缓冲器766可配置成存储机器级指令(例如, fsm命令)。然而,计算电路766中的每一个包含耦合到状态机723的quire寄存器767。 quire寄存器767可配置成存储由mac执行的递归运算(例如,算术运算或逻辑运算)的 迭代的结果(例如,中间结果)。在一些实施例中,计算电路766中的每一个可包含除状 态机723之外或替代于所述状态机的感测放大器带、触发器串或这两者。

[0128]

如图7所示出,主机702的命令缓冲器761和存储器资源724的命令缓冲器763各 自包含与计算电路766和计算电路系统765的每一状态机相关联的存储装置(例如,命令 缓冲器)。命令缓冲器761和763包含用于n 1个计算电路766的状态机和计算电路系 统765的状态机723中的每一个的存储装置。

[0129]

如结合图6所描述,处理装置754可将与矩阵乘法(例如,gemm命令)相关联的主 机级命令解析为与点积运算相关联的多个机器级指令。可使用计算电路766并行地执行 点积运算。用于相应点积运算的机器级指令可分布在计算电路766当中。pcie接口752、 存储器资源724、处理装置754、计算电路系统765和/或计算电路766可实施于fpga 上。在计算电路766中的每一个中包含quire寄存器767而非计算电路系统765的加速 电路系统720可减少实施计算电路765的fpga资源量。与设备709相比,通过加速电 路系统520的图5实施方案说明的设备501的加速电路系统520可利用较大量的fpga 资源。在计算电路766中的每一个中包含quire寄存器767可增加可并行地执行的算术 和/或逻辑运算的量,同时减少待实施的fpga资源量。

[0130]

图8为根据本公开的多个实施例的呈包含设备811的计算系统形式的另一功能框 图,所述设备包含主机802和存储器资源824。主机802、pcie接口852、存储器资源 824、处理装置854、计算电路系统865和计算电路866可类似于结合图7描述的主机 702、pcie接口752、存储器资源724、处理装置754、计算电路系统765和计算电路766。

[0131]

与图7所示出的设备709相比,除计算电路系统865的加速电路系统820之外,设 备811还包含耦合到pcie接口852的加速电路系统868。加速电路系统868可具有与计 算电路系统865的加速电路系统820相同或不同的结构。加速电路系统868可直接耦合 到pcie接口852。加速电路系统可映射到与pcie接口852相关联的存储器空间中,例 如,间接寄存器870。间接寄存器870可配置成存储标量操作数、算术或逻辑运算的结 果或这两者。加速电路系统868的输出缓冲器(例如,结合图5描述的输出缓冲器547) 可与忙碌标志组合,使得来自输出缓冲器的读取操作直到加速电路系统868完成算术或 逻辑运算的执行为止才完成。使用设备800及加速电路系统868执行的标量乘法运算可 包含将第一标量操作数(操作数a)写入到加速电路系统868的第一输入缓冲器(例如,输 入缓冲器545),将第二标量操作数(操作数b)写入到加速电路系统868的第二输入缓冲 器(例如输入缓冲器546),以及从乘法结果寄存器读取第一和第二标量操作数的乘法运 算的结果。使用加速电路系统868来执行标量运算可比使用计算电路系统865的加速电 路系统820更有效。

[0132]

在至少一个实施例中,设备800可提供对由存储器资源824存储的操作数的间接存 取。例如,如果将执行标量运算和向量运算的组合,那么可能更有效的是将向量数据加 载到存储器资源824中且维持由存储器资源824对向量数据的存储,使得计算电路866 和计算电路系统865的状态机823可存取向量数据而不必向和从主机802传递数据。如 果将对向量

数据或来自向量运算的结果执行标量运算,那么对存储器资源824执行标量 运算。间接标量乘法运算可包含将存储于存储器资源824中的第一操作数(操作数a)的 地址写入到间接寄存器870,将存储于存储器资源824中的第二操作数(操作数b)的地址 写入到间接寄存器870,以及将使用存储于存储器资源824中的第一和第二操作数的标 量运算的结果的地址写入到间接寄存器870。

[0133]

图9为根据本公开的多个实施例的呈包含设备913的计算系统形式的另一功能框 图,所述设备包含主机902和存储器资源924。主机902、pcie接口952、存储器资源 924、计算电路系统965和计算电路966可类似于结合图8描述的主机802、pcie接口 852、存储器资源824、计算电路系统865和计算电路866。

[0134]

与图8所示出的设备811相比,设备913并不包含耦合到pcie接口952和存储器 资源924的处理装置。计算电路系统965的缓冲器964可映射到pcie接口952的存储 器空间。将缓冲器964映射到pcie接口952的存储器空间可使得主机902的软件驱动 器能够提供由处理装置(例如,结合图8描述的处理装置854)的内置软件提供的功能。 主机902的软件驱动器可以比处理装置的内置软件高的吞吐量操作。

[0135]

在至少一个实施例中,主机902(例如,经由主机902的cpu)可将例如gemm命令 的较高级命令(例如,主机级指令)解析为较低级命令(例如,机器级指令),所述较低级命 令例如与gemm命令的点积运算相关联的状态机命令。较低级命令可由主机902的命 令缓冲器961存储,所述主机包含对应于计算电路966和计算电路系统965的每一状态 机923的存储装置(例如,寄存器)。相应的较低级命令可从对应于计算电路966

‑

0、 966

‑

1、

……

、966

‑

n中的一个或计算电路系统965的状态机的命令缓冲器961的相应存 储装置传递(例如,传送)到计算电路966中的一个或计算电路系统965的状态机的命令 缓冲器964。例如,机器级指令可从对应于计算电路966

‑

1的状态机923的命令缓冲器 961的寄存器传送到计算电路966

‑

1的命令缓冲器964。

[0136]

图10为根据本公开的多个实施例的呈加速电路系统1020形式的功能框图。加速电 路系统1020可类似于结合图5

‑

9描述的加速电路系统520、620、720、820、868、920 和968中的任一个。加速电路系统1020可实施于fpga上。

[0137]

加速电路系统1020可能够存储突发的传入数据,因为可使用两个或更多个操作数 执行算术运算。在相同时钟周期期间,可将对应于两个操作数的数据值供应到加速电路 系统1020。例如,如果以256字节突发的形式从外部存储器资源(例如,结合图5描述 的ddr3存储器530)检索两个操作数,那么不保证数据值将在恰当时间到达。在至少一 个实施例中,加速电路系统1020可包含先进可扩展接口流先进先出(axi

‑

stream fifo), 例如输入缓冲器1046和1046。加速电路系统1020可包含输出缓冲器1047,所述输出 缓冲器可配置成在将来自加速电路系统1020的数据值传递到例如ddr3存储器530之 前缓冲表示来自算术块的结果的数据值。

[0138]

在至少一个实施例中,加速电路系统1020可从输入缓冲器1046和1046读取六十 四位的数据,且将所述数据转换为与配置成执行算术运算的电路系统兼容的格式。例如, 在8位posit环境中,从输入缓冲器1045、输入缓冲器1046或这两者读取的操作数可由 电路系统1072转换为总线上的八个依序输入。电路系统1076可包含配置成选择输出的 多路复用器。电路系统1076可包含alu。alu可包含对整数二进制位串(例如,呈posit 格式的位串)

执行运算(例如,算术运算、逻辑运算、按位运算等)的电路系统(例如,硬件、 逻辑、一或多个处理装置等)。由电路系统1076执行的对应于八个依序输入的运算的结 果可例如由电路系统1076填充到64位字中,随后将64位字写入到输出缓冲器1047。

[0139]

在至少一个实施例中,输入缓冲器1045、输入缓冲器1046、输出缓冲器1047、电 路系统1072和/或电路系统1076可实施于dma块中。

[0140]

在至少一个实施例中,加速电路系统1020可包含电路系统1073,所述电路系统配 置成将以浮点格式格式化的数据值转换为unum或posit格式。加速电路系统1020可包 含电路系统1074,所述电路系统配置成将以unum格式或posit格式格式化的数据值转 换为浮点格式。

[0141]

图11为根据本公开的多个实施例的呈存储器装置1104形式的另一功能框图。pcie 接口1152、存储器资源1124和计算电路系统1165可类似于结合图6描述的pcie接口 652、存储器资源624和计算电路系统865。图11示出计算电路系统1165的状态机1123 的组件。

[0142]

状态机1123可包含多个dma控制器。每一相应dma控制器可耦合到相应缓冲器。 每一缓冲器可以是fifo缓冲器。如由图11所示出,状态机1123可包含第一组dma 控制器和fifo缓冲器1171,所述fifo缓冲器配置成检索(例如,从存储器资源1124) 且存储第一操作数(操作数a(opa))。状态机1123可包含第二组dma控制器和fifo缓 冲器1173,所述fifo缓冲器配置成检索(例如,从存储器资源1124)且存储第二操作数(操 作数b(opb))。状态机1123可包含第三组dma控制器和fifo缓冲器1175,所述fifo 缓冲器配置成检索(例如,从存储器资源1124)且存储第三操作数(操作数c(opc))。在相 应dma控制器的输出端与加速电路系统1120之间的多组1171、1173和1175的fifo 缓冲器可使得加速电路系统1120能够以更快的速度执行运算。

[0143]

计算电路系统1165的加速电路系统1120可从状态机1123的相应fifo缓冲器检索 第一操作数、第二操作数、第三操作数或其组合。尽管图11示出用于检索和存储操作 数的三组dma控制器和fifo缓冲器1171、1173和1175,但实施例不限于此。例如, 状态机1123可包含少于三组dma控制器和fifo缓冲器或多于三组dma控制器和 fifo缓冲器。

[0144]

状态机1123可包含配置成检索、存储和传递来自加速电路系统1120的结果的一组 dma控制器和缓冲器1177。组1177的缓冲器可以是fifo缓冲器。

[0145]

处理装置1158可将待由加速电路系统1120执行的例如计数、地址、大小、步幅和 运算等命令传递到命令缓冲器1164。如图11所示出,计算电路系统1165可包含配置成 存储指示控制信号、状态或这两者的数据的存储器1178。多组1171、1173和1175的 dma控制器可至少部分地基于来自处理装置1158的命令而检索相应操作数,所述相应 操作数包含开始地址、待检索的数据量(例如,开始地址 n*步幅*操作数大小)、运算计 数。如本文中所使用,“步幅”指处理的样本之间的地址增量。例如,

‑

1的步幅可用以 按相反次序从缓冲器读取数据。作为另一实例,步幅2可用以按0、2、4、6、8等的地 址偏移量从缓冲器读取数据。

[0146]

图12为根据本公开的多个实施例的表示用于posit运算的加速电路系统的实例方法 1279的流程图。在框1280处,方法1279可包含在可耦合到加速电路系统的dma控制 器处接收指示执行将第一位串写入到驻存于加速电路系统上的第一缓冲器的操作的信 令。加速电路系统可配置成对以unum或posit格式格式化的位串执行算术运算、逻辑运 算或这两者。第一缓冲器可以是fifo缓冲器。加速电路系统可类似于分别结合图1、2 和5

‑

11描述的

加速电路系统120、220、520、620、720、820、868、920、968、1020 和1120。

[0147]

在框1281处,方法1279可包含在dma控制器处接收指示执行将第二位串写入到 驻存于加速电路系统上的第二缓冲器的操作的信令。第二操作数可以unum或posit格式 格式化。第二缓冲器可以是fifo缓冲器。

[0148]

在框1282处,方法1279可包含将指示待使用写入到第一缓冲器的第一位串和写入 到第二缓冲器的第二位串执行算术运算、逻辑运算或这两者的信令传输到加速电路系 统。

[0149]

在框1283处,方法1279可包含经由加速电路系统且根据由加速电路系统接收的信 令而执行算术运算、逻辑运算或这两者。如上文所描述,算术运算可包含例如加法、减 法、乘法、除法、融合乘法加法、乘积累加、点积单元、大于或小于、绝对值(例如,fabs())、 快速傅立叶变换、反快速傅立叶变换、sigmoid函数、卷积、平方根、指数和/或修正线 性单元(relu),以及例如正弦、余弦、正切等的三角运算等的算术运算,而逻辑运算可 包含例如and、or、xor、not等的逻辑运算。在一些实施例中,方法1279可包含 在执行算术运算、逻辑运算或这两者之前,经由加速电路系统将第一位串、第二位串或 这两者以unum或posit格式格式化。将第一位串、第二位串或这两者以unum或posit 格式格式化可包含经由加速电路系统将第一位串、第二位串或这两者从浮点格式转换为 unum或posit格式。

[0150]

在框1284处,方法1279可包含将指示算术运算、逻辑运算或这两者的结果的信令 传输到dma控制器。结果可以unum或posit格式格式化。在一些实施例中,方法1279 将指示算术运算、逻辑运算或这两者的结果的信令从驻存于加速电路系统上的第三缓冲 器传输到dma控制器。第三缓冲器可以是fifo缓冲器。

[0151]

在一些实施例中,加速电路系统可实施于fpga上。方法1279可进一步包含经由 dma控制器且根据由dma控制器接收的信令而存取驻存于fpga上的存储器,以检索 第一位串、第二位串或这两者。方法1279可进一步包含经由dma控制器且根据由dma 控制器接收的信令而存取在加速电路系统外部的主存储器,以检索第一位串、第二位串 或这两者。

[0152]

在一些实施例中,方法1279可进一步包含将指示第一位串、第二位串或这两者的 信令从可耦合到加速电路系统的主机传输到可耦合到加速电路系统的存储器。方法1279 可进一步包含经由pcie接口将指示第一位串、第二位串或这两者的信令从主机传输到 存储器。方法1279可进一步包含将指示算术运算、逻辑运算或这两者的信令从可耦合 到加速电路系统的主机传输到可耦合到加速电路系统的存储器。方法1279可进一步包 含经由pcie接口将指示算术运算、逻辑运算或这两者的信令从主机传输到存储器。

[0153]

图13为根据本公开的多个实施例的表示用于posit运算的加速电路系统的实例方法 1385的另一流程图。在框1386处,方法1385可包含在驻存于加速电路系统上的第一缓 冲器处接收指示以unum或posit格式格式化的第一位串的信令。加速电路系统可配置成 对以unum或posit格式格式化的位串执行算术运算、逻辑运算或这两者。

[0154]

在框1387处,方法1385可包含在驻存于加速电路系统上的第二缓冲器处接收指示 以unum或posit格式格式化的第二位串的信令。

[0155]

在框1388处,方法1385可包含将指示算术运算、逻辑运算或这两者的信令传输到 驻存于加速电路系统上的处理电路系统。

[0156]

在框1389处,方法1385可包含经由处理电路系统使用第一位串和第二位串执行算 术运算、逻辑运算或这两者。

[0157]

在一些实施例中,方法1385可进一步包含将算术运算、逻辑运算或这两者的结果 从处理电路系统传输到驻存于加速电路系统上的第三缓冲器。方法1385可进一步包含 从可耦合到加速电路系统的存储器传输指示第一位串的信令和指示第二位串的信令。在 一些实施例中,方法1385可进一步包含从可耦合到加速电路系统的第一存储器组件传 输指示第一位串的信令和指示第二位串的信令。第一存储器组件可不同于第二存储器组 件。在一些实施例中,方法1385可进一步包含在可耦合到加速电路系统的处理装置处 将与算术运算、逻辑运算或这两者相关联的主机级指令解析为机器级指令。指示机器级 指令的信令可被传输到处理电路系统。

[0158]

图14为根据本公开的多个实施例的表示用于posit运算的加速电路系统的实例方法 1490的另一流程图。在框1491处,方法1490可包含在可耦合到主机的存储器装置处镜 像来自主机的指示使用以unum或posit格式格式化的位串执行算术运算、逻辑运算或这 两者的指令的信令。

[0159]

在框1492处,方法1490可包含将指示以unum或posit格式格式化的第一位串的信 令从主机传输到存储器装置。

[0160]

在框1493处,方法1490可包含将指示以unum或posit格式格式化的第二位串的信 令从主机传输到存储器装置。

[0161]

在框1494处,方法1490可包含在存储器装置的加速电路系统处且根据所镜像的信 令而使用第一位串和第二位串执行算术运算、逻辑运算或这两者。

[0162]

在一些实施例中,第一位串和第二位串可各自表示矩阵。所镜像的信令可指示使用 第一位串和第二位串执行矩阵乘法运算的指令。方法1490可进一步包含在存储器装置 的处理装置处使用第一位串和第二位串将所镜像的信令解析为指示与矩阵乘法运算相 关联的点积运算的信令。方法1490可进一步包含经由加速电路系统使用第一位串和第 二位串执行相关联的点积运算。方法1490可进一步包含在执行算术运算、逻辑运算或 这两者之前,在加速电路系统处对第一位串和第二位串进行解压,且在加速电路系统处 对点积运算的结果进行压缩。

[0163]

图15为根据本公开的多个实施例的表示用于posit运算的加速电路系统的实例方法 1595的另一流程图。在至少一个实施例中,方法1595可至少部分地由结合图5描述的 微码控制器544实施。在框1596处,方法1595可包含在可耦合到存储器装置的加速电 路系统的微码控制器处接收指示使用以unum或posit格式格式化的多个操作数执行多个 算术运算、多个逻辑运算或这两者的预计算结果的信令。

[0164]

在框1597处,方法1595可包含在微码控制器处接收指示使用所述多个操作数的特 定集合执行多个算术运算或多个逻辑运算的特定运算的指令的信令。如本文中所描述, lut可用以识别lut内的特定算术或逻辑运算的结果而非执行特定算术或逻辑运算。

[0165]

在框1598处,方法1595可包含响应于接收到的指示执行特定运算的指令的信令, 经由微码控制器识别对应于特定运算和多个操作数的特定集合的预计算结果中的一个。

[0166]

在框1599处,方法1595可包含从微码控制器传输指示对应于特定运算和多个操作 数的特定集合的预计算结果中的一个的信令。例如,响应于执行特定算术或逻辑运算的 指令,微码控制器(例如,微码控制器544)可识别特定算术或逻辑运算的结果,而非执 行特定算术或逻辑运算。在一些实施例中,方法1595可进一步包含在微码控制器处维 持包含预计

算结果的lut。识别预计算结果中的一个可包含确定与特定运算的结果和多 个操作数的特定集合相关联的lut的地址。

[0167]

在一些实施例中,方法1595可进一步包含在微码控制器处接收指示操作数的特定 位长度的信令,且在微码控制器处至少部分地基于特定位长度而接收指示多个算术运 算、逻辑运算或这两者的预计算结果的信令。在一些实施例中,方法1595可进一步包 含将指示对应于特定运算和多个操作数的特定集合的预计算结果中的一个的信令传输 到可耦合到存储器装置的主机。

[0168]

尽管已在本文中说明并描述了具体实施例,但所属领域的一般技术人员应了解,经 计算以实现相同结果的布置可取代所展示的具体实施例。本公开意图涵盖本公开的一或 多个实施例的修改或变化。应理解,以上描述是以说明性方式而非限制性方式进行的。 对于所属领域的技术人员而言在审阅上述描述之后上述实施例的组合及本文中未具体 描述的其它实施例将是显而易见的。本公开的一或多个实施例的范围包含其中使用以上 结构和过程的其它应用。因此,本公开的一或多个实施例的范围应参考所附权利要求书 以及此类权利要求被赋予的等效物的完整范围而确定。

[0169]

在前述具体实施方式中,出于简化本公开的目的而将一些特征一并归到单个实施例 中。本公开的此方法不应被理解为反映本公开的所公开实施例必须使用比每一权利要求 中明确陈述的特征更多的特征的意图。相反,如所附权利要求书所反映,本发明主题在 于少于单个所公开实施例的所有特征。因此,所附权利要求书特此并入于具体实施方式 中,其中每一权利要求就其自身而言作为单独实施例。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。