1.至少一个实施例涉及用于执行和促进人工智能的处理资源。例如,至少一个实施例涉及用于根据本文描述的各种新颖技术来训练神经网络的处理器或计算系统。

背景技术:

2.随着用户越来越多地以各种不同的格式数字地消费内容,期望以新的方式呈现或管理该内容。进一步,用户越来越多地观看涉及其他人的体验或表现的内容,诸如通过观看精彩片段(highlight)视频或游戏的合辑(montages)或虚拟现实体验。不幸的是,手动地生成这些合辑通常是成本过高的,并且自动化过程不提供最佳结果,因为它们不能准确地确定内容的哪些部分将是最感兴趣的。

附图说明

3.将参照附图描述根据本公开的各个实施例,在附图中:

4.图1示出了根据至少一个实施例的用于管理虚拟现实内容的呈现的系统;

5.图2a、图2b和图2c示出了根据至少一个实施例的可用于为合辑选择剪辑的图像;

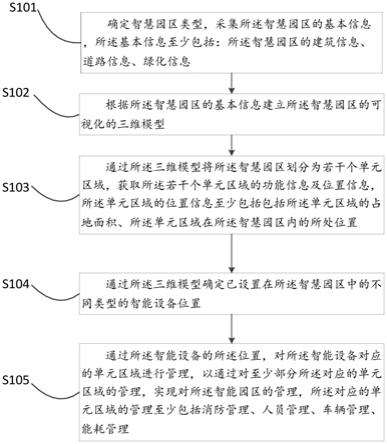

6.图3示出了根据至少一个实施例的精彩片段生成网络的组件;

7.图4示出了根据至少一个实施例的用于生成精彩片段合辑的过程;

8.图5示出了根据至少一个实施例的使用情绪的指示来选择视频片段的过程;

9.图6a示出了根据至少一个实施例的推理和/或训练逻辑;

10.图6b示出了根据至少一个实施例的推理和/或训练逻辑;

11.图7示出了根据至少一个实施例的示例数据中心系统;

12.图8示出了根据至少一个实施例的计算机系统;

13.图9示出了根据至少一个实施例的计算机系统;

14.图10示出了根据至少一个实施例的计算机系统;

15.图11示出了根据至少一个实施例的计算机系统;

16.图12a示出了根据至少一个实施例的计算机系统;

17.图12b示出了根据至少一个实施例的计算机系统;

18.图12c示出了根据至少一个实施例的计算机系统;

19.图12d示出了根据至少一个实施例的计算机系统;

20.图12e和图12f示出了根据至少一个实施例的共享编程模型;

21.图13示出了根据至少一个实施例的示例性集成电路和相关联的图形处理器;

22.图14a

‑

14b示出了根据至少一个实施例的示例性集成电路和相关联的图形处理器;

23.图15a

‑

15b示出了根据至少一个实施例的附加的示例性图形处理器逻辑;

24.图16示出了根据至少一个实施例的计算机系统;

25.图17a示出了根据至少一个实施例的并行处理器;

26.图17b示出了根据至少一个实施例的分区单元;

27.图17c示出了根据至少一个实施例的处理集群;

28.图17d示出了根据至少一个实施例的图形多处理器;

29.图18示出了根据至少一个实施例的多图形处理单元(gpu)系统;

30.图19示出了根据至少一个实施例的图形处理器;

31.图20示出了根据至少一个实施例的处理器的微架构;

32.图21示出了根据至少一个实施例的深度学习应用处理器;

33.图22示出了根据至少一个实施例的示例神经元形态处理器;

34.图23和图24示出了根据至少一个实施例的图形处理器的至少部分;

35.图25示出了根据至少一个实施例的图形处理器核心的至少部分;

36.图26a

‑

26b示出了根据至少一个实施例的图形处理器核心的至少部分;

37.图27示出了根据至少一个实施例的并行处理单元(“ppu”);

38.图28示出了根据至少一个实施例的通用处理集群(“gpc”);

39.图29示出了根据至少一个实施例的并行处理单元(“ppu”)的存储器分区单元;

40.图30示出了根据至少一个实施例的流式多处理器;

41.图31是根据至少一个实施例的用于高级计算管线的示例数据流程图;

42.图32是根据至少一个实施例的用于在高级计算管线中训练、适配、实例化和部署机器学习模型的示例系统的系统图;

43.图33a示出了根据至少一个实施例的用于训练机器学习模型的过程的数据流程图;以及

44.图33b是根据至少一个实施例的用于利用预训练的注释模型来增强注释工具的客户端

‑

服务器架构的示例图示。

具体实施方式

45.在至少一个实施例中,用户102可以经由显示机制观看数字内容,如可以包括虚拟现实(vr)头盔(headset)内部的显示器106。在至少一个实施例中,可以使用诸如监视器、触摸屏、增强现实(ar)显示器或投影之类的替代显示机制来呈现这样的内容。在至少一个实施例中,对于vr内容,这个vr头盔可以与单独的客户端设备110通信,单独的客户端设备110可以提供、传输或渲染要经由vr头盔104呈现的内容。在至少一个实施例中,vr头盔104可包括提供用于用户102的头部的移动的数据的一个或更多个取向(orientation)传感器,该数据可用于控制经由头盔104呈现的内容的观点(pov),以便为用户102提供逼真的和沉浸式的体验。在至少一个实施例中,在客户端设备110上执行的vr应用112可以从头盔104接受取向数据,并且使用该信息来渲染要经由头盔104呈现的vr内容。在至少一个实施例中,客户端设备110可以与至少一个内容服务器130接触,所述至少一个内容服务器130可以通过至少一个网络120(诸如有线或无线通信网络)流式传输或以其他方式传输内容,以用于渲染或呈现此vr内容。在至少一个实施例中,内容服务器130上的传输管理器132可以负责通过适当的网络连接(例如互联网或蜂窝连接)传输适当格式和信道(例如流视频格式)的内容。在至少一个实施例中,要显示的vr内容可以在内容服务器130上渲染,如可以与从头盔104接收的取向数据相关,并且通过网络120传输至客户端设备110并且最终传输至vr头盔104。

46.在至少一个实施例中,用户的vr会话可以持续从几分钟到几小时的任何时间。在至少一个实施例中,在该会话期间可存在可导致用户体验具有不同强度水平的各种不同情绪的若干紧张时刻。在至少一个实施例中,这些情绪的持续时间和强度可以是用户的情绪响应的中央基础。在至少一个实施例中,这些情绪连同其强度和持续时间可被确定,以用于标识在呈现期间触发该用户中的强情绪响应的剪辑或片段的目的。在至少一个实施例中,然后可以使用这些剪辑或片段来生成vr内容精彩片段的一个或更多个合辑或集合。在至少一个实施例中,这样的方法可考虑诸如持续时间和强度之类的因素的瞬时特征和聚合特征两者,并且可将所选精彩片段剪辑的长度与对应情绪的持续时间和强度相关。

47.在至少一个实施例中,vr头盔104可包括一个或更多个相机,诸如红外(ir)相机108,其可捕获用户的双眼的图像。在至少一个实施例中,可使用环境光相机或另一类型的传感器或组件(诸如生物特征传感器、捕获呼吸和语音模式的麦克风、以及运动传感器)来捕获用户的图像信息。

48.在至少一个实施例中,vr头盔104可以包括ir关注跟踪子系统,其包括被配置为捕获佩戴头盔104的用户的双眼的图像的一个或更多个ir相机。在至少一个实施例中,用户眼睛的这些红外图像也具有全脸对应物。在至少一个实施例中,客户端设备110上的用户分析模块114的一个或更多个神经网络可以用于确定个体图像或视频帧的序列中的每一个的类别的指示,以及每个指示的置信度。在至少一个实施例中,诸如检测到的情绪的开始时间和结束时间之类的信息可被提供给内容管理器116组件或模块,该内容管理器116组件或模块可将这些时间与在那些时间呈现的视频的对应剪辑或片段相关联。在至少一个实施例中,该信息可被发送到内容服务器130,内容服务器130也可执行包括内容管理器140组件的内容应用1340。在至少一个实施例中,内容管理器140可聚合这些剪辑并从这些剪辑中进行选择以生成该内容的精彩片段合辑。在至少一个实施例中,内容管理器140可与会话管理器136一起工作以确定会话的所有片段,并使用那些片段的信息(诸如情绪强度和持续时间)来选择该合辑的精彩片段。在至少一个实施例中,关于存储在用户数据库144中的用户的信息或者从内容数据库142显示的内容也可以用于这些确定。

49.在至少一个实施例中,可以在内容呈现的不同片段期间确定不同情绪的指示。在至少一个实施例中,可以如图2a和图2b中所示呈现高尔夫内容的呈现。在至少一个实施例中,这可以包括玩家摆开阵势击球或选择球杆的片段。在至少一个实施例中,在这些片段期间可能几乎没有检测到情绪。在至少一个实施例中,可以在玩家击中球204的片段期间检测情绪的第一指示,如图2a的帧200所示。在至少一个实施例中,可在该球滚动到相应球洞224中的片段期间检测情绪的第二指示,如图2b的帧220所示。在至少一个实施例中,在所有这些片段期间,可以捕获用户眼睛的ir图像242、244,以用于确定情绪的指示的目的。

50.在至少一个实施例中,两个片段的情绪的指示可用于选择用户可能感兴趣的精彩片段合辑的剪辑,因为该用户在两个片段期间都具有情绪体验。然而,在至少一个实施例中,当此玩家击中此球时,此用户仅具有短暂且不是特别紧张的情绪反应,如在帧200中。在至少一个实施例中,可以确定,当该球滚动到对应洞的上方时(如在帧224中),该用户具有更紧张和漫长的情绪反应。在至少一个实施例中,该情绪的强度和持续时间可随后用于确定包含该球滚动到该球洞中的事件的剪辑或片段可能更重要,以包括在精彩片段合辑中,即使两个事件可能已引起相同的情绪、表情或指示。

51.在至少一个实施例中,头戴式设备(hmd)302或其他此类系统可捕获用户数据(诸如ir眼睛图像),并提供与捕获这些眼睛图像同时显示的内容的片段或帧的指示。在至少一个实施例中,此信息可作为输入被提供给可在hmd 302或连接的客户端设备上运行的客户端应用304。在至少一个实施例中,客户端应用304可包括用于确定呈现给用户的一个或更多个媒体文件的相关视频剪辑或片段的剪辑引擎,以及情绪分析器308,其用于确定在那些一个或更多个媒体文件的呈现期间该用户的情绪。

52.在至少一个实施例中,至少一个红外(ir)相机被定位成当被装配到头戴式设备(hmd)中时面向用户的眼睛。在至少一个实施例中,每个ir相机可以在整个内容呈现(诸如游戏会话)中连续地捕获用户的至少一只眼睛的图像,并且可以维持最近的图像或视频帧的缓冲,诸如高达30秒或一分钟的内容帧。在至少一个实施例中,针对双眼的视频馈送可被缝合(stitch)在一起,使得双眼在从hmd 302到客户端应用304的输出视频馈送中串联(in tandem)可见。在至少一个实施例中,客户端应用304可包括将该馈送作为输入的情绪分析器308。在至少一个实施例中,可以利用专家混合(moe)分层分类器,其利用多个变分自动编码器(vae)作为专家。

53.在至少一个实施例中,基于moe的方法可以是集成机器学习技术,其中管理器网络监督多个从属网络以学习输入空间的分离点。在至少一个实施例中,这个管理器模型可以是学习根据这些输入的性质将一个或更多个专家分配给输入的门控网络。在至少一个实施例中,该管理器可以使不同的专家能够对不同种类的输入进行专门化。在至少一个实施例中,取决于该分类中涉及的类别的数量,该moe网络中的多个专家可以是可调谐超参数。在至少一个实施例中,该模型中的最终层可以具有softmax激活函数。在至少一个实施例中,知道哪个或哪些专家已经学习以专门化其中使得此模型能够以无监督的方式对测试输入进行分类。在至少一个实施例中,可以利用分层的moe设计,其中这些专家本身是moe,并且每个专家中和每个层上的子专家数量是附加的超参数。在至少一个实施例中,该分层moe中的根网络可以是高斯变分自动编码器(vae)或向量量化的变分自动编码器(vq

‑

vae)。

54.在至少一个实施例中,定义n类情绪的集合,并且训练该moe中的管理器和专家,以通过对每个情绪的再生来实现无监督分类。在至少一个实施例中,当由一个或更多个ir相机捕获的这些连续图像中的任何一个被该moe成功地分类为情绪时,记录该情绪的开始和结束时间戳。在至少一个实施例中,特定情绪的结束可由未能反映该初始检测到的情绪的第一帧来指示。在至少一个实施例中,为该情绪捕获的图像然后可被馈送到卷积神经网络(cnn),该卷积神经网络可推理该情绪在给定的帧集合上的平均强度。在至少一个实施例中,moe可替代地分层扩展以处理检测到的情绪的强度确定。在至少一个实施例中,情绪分析器308的输出可包括检测到的情绪的类别、经历该情绪的时间和平均强度。

55.在至少一个实施例中,剪辑引擎306可由情绪分析器308以给定情绪的最高强度的时间戳激活。在至少一个实施例中,检测到的情绪的最高强度的时间可被称为t(h),并且可分别与开始和结束时间戳t(s)和t(e)一起提供。在至少一个实施例中,每个方向上的可配置的缓冲时间t(b)可由下式给出:

56.t(b)=n*(t(e)

‑

t(s))

57.其中n可以是值1和10。在至少一个实施例中,起始剪辑尺寸可以被定义为每个方向上的t(b)或2*t(b)。在至少一个实施例中,一个或更多个神经网络可以用于标识在该呈

现的媒体内容中的场景、对象、动作和音频元素,其中给定视频剪辑中的各个帧被标记有相应的关键字。

58.在至少一个实施例中,计算机视觉人工智能技术可用于处理输入媒体(例如,图像、视频或音频),以识别诸如场景、对象、事件或动作之类的特征。在至少一个实施例中,这些特征可以由一个或更多个深度神经网络模型转换成可以与个体帧或片段相关联的一个或更多个关键字。在至少一个实施例中,各个模型的组合或单个模型可被应用于特征识别以生成关键字的集合。

59.在至少一个实施例中,剪辑引擎306内的决策神经网络可以确定呈现连贯事件的以t(h)为中心的最小帧集合的时间戳。这些时间戳分别被指定为用于剪辑开始和剪辑结束的t(s)和t(e)。在至少一个实施例中,使用来自情绪分析器308和实际内容帧的一组输入,剪辑引擎306的输出可以是所生成的精彩片段剪辑的一个或更多个时间戳。

60.在至少一个实施例中,该信息可作为输入提供给精彩片段聚集器312,该精彩片段聚集器312可在远离客户端应用304的服务器310上执行。在至少一个实施例中,精彩片段聚集器312的角色是通过情绪、持续时间和强度来记录所生成的精彩片段。在至少一个实施例中,精彩片段聚集器312可基于强度或持续时间或两者的可配置阈值来选择应用滤波器。在至少一个实施例中,精彩片段聚集器312可跟踪事件和情绪之间的相关性,并且可基于事件来确定特定情绪的强度如何在会话上改变。在至少一个实施例中,精彩片段聚集器312还可用类似的眼睛表示在两个情绪中检测并潜在地校正假阳性检测。在至少一个实施例中,这可包括在其指示中被确定为至少有些相似的情绪,诸如生气和困惑。在至少一个实施例中,如果该情绪被标记为生气,但是基于同一用户或不同用户的该内容的过去结果,决策网络检测到的事件最不可能表示生气,则这可呈现潜在校正的机会。在至少一个实施例中,精彩片段聚集器312可在经由hmd 302向用户呈现最终结果或存储到合辑数据库314以供后续检索之前校正错误分类。

61.在至少一个实施例中,能够以无监督的方式使用人眼的图像(诸如ir图像)来训练情绪分析器308,以便学习从眼睛到情绪的映射。在至少一个实施例中,在数据集上训练情绪分析器308中的cnn,所述数据集包含不同水平的常见情绪的强度,诸如惊讶与震惊、微笑与大笑、或皱眉与强烈愤怒。在至少一个实施例中,可以在不同场景中使用针对关键字集合的有监督机器学习来训练剪辑引擎306中的对象和事件识别模型以及一个或更多个决策模型。在至少一个实施例中,可以使用具有标记数据的有监督机器学习来训练精彩片段聚集器中的校正管理器神经网络。在至少一个实施例中,这些系统可以用于诸如vr内容呈现和vr游戏的应用,但是也可以用作可以至少部分地基于用户的情绪分析的其他有用解决方案的基础。

62.在至少一个实施例中,可利用用于生成精彩片段合辑的过程400,如图4所示。在至少一个实施例中,诸如虚拟现实(vr)内容之类的内容可被呈现402给用户,诸如佩戴vr硬件或以其他方式能够观看此内容呈现的用户。在至少一个实施例中,可以接收其他类型的媒体内容以用于可听或可视呈现。在至少一个实施例中,该输入可包括用于呈现的视频、图像或音频内容。在至少一个实施例中,可以在此内容的呈现期间捕获404该用户的眼睛数据,诸如可以利用此vr头盔的一个或更多个ir相机。在至少一个实施例中,可以分析406该捕获的眼睛数据以确定在该呈现的内容的片段期间的用户情绪的一个或更多个指示。在至少一

个实施例中,这可包括将此眼睛数据作为输入提供给模型,该模型被训练成从此眼睛数据中表示的眼睛的移动、动作或其他方面来确定情绪。在至少一个实施例中,如果没有以至少最小置信度或确定性检测到情绪,则此过程可针对此内容的帧的后续图像继续。在至少一个实施例中,如果确定408检测到至少一个情绪,则可提供410该内容中的开始点和结束点,其指示针对其检测到特定情绪的帧序列。这些端点可作为输入提供给至少一个神经网络,以至少确定该情绪的强度,其中该模型的输出可包括诸如该情绪的类型、强度和持续时间之类的信息。在至少一个实施例中,可以确定412该片段期间的峰值情绪强度的时间。在至少一个实施例中,该峰值可被用于确定以该峰值为中心的内容剪辑,该内容剪辑包括在序列中观看时表示连贯事件的帧。在至少一个实施例中,这使得能够基于在这些帧中检测到的对象、动作或事件来智能地选择该剪辑的内容。在至少一个实施例中,然后可以向精彩片段聚集器提供418该剪辑的数据,以便在必要时校正那些剪辑的方面,并生成一个或更多个精彩片段合辑或所选择的剪辑的其他集合。

63.在至少一个实施例中,可以使用用于选择视频片段的过程500,如图5所示。在至少一个实施例中,在一个或更多个视频文件的呈现期间为一个或更多个观看者捕获502数据。在至少一个实施例中,确定504在这个呈现期间这些一个或更多个观看者的情绪的一个或更多个指示。在至少一个实施例中,在这些一个或更多个视频片段的呈现期间,可以至少部分地基于这些一个或更多个观看者的一个或更多个情绪的一个或更多个指示来选择506这些视频文件的一个或更多个片段。

64.推理和训练逻辑

65.图6a示出了用于执行与一个或更多个实施例相关联的推理和/或训练操作的推理和/或训练逻辑615。下面结合图6a和/或图6b提供关于推理和/或训练逻辑615的细节。

66.在至少一个实施例中,推理和/或训练逻辑615可以包括但不限于代码和/或数据存储601,用于存储前向和/或输出权重和/或输入/输出数据,和/或在一个或更多个实施例的方面中配置被训练为和/或用于推理的神经网络的神经元或层的其他参数。在至少一个实施例中,训练逻辑615可以包括或耦合到用于存储图形代码或其他软件以控制时序和/或顺序的代码和/或数据存储601,其中权重和/或其他参数信息被加载以配置逻辑,包括整数和/或浮点单元(统称为算术逻辑单元(alu))。在至少一个实施例中,代码(诸如图代码)基于该代码所对应的神经网络的架构将权重或其他参数信息加载到处理器alu中。在至少一个实施例中,代码和/或数据存储601存储在使用一个或更多个实施例的方面训练和/或推理期间的输入/输出数据和/或权重参数的前向传播期间结合一个或更多个实施例训练或使用的神经网络的每个层的权重参数和/或输入/输出数据。在至少一个实施例中,代码和/或数据存储601的任何部分都可以包括在其他片上或片外数据存储内,包括处理器的l1、l2或l3高速缓存或系统存储器。

67.在至少一个实施例中,代码和/或数据存储601的任何部分可以在一个或更多个处理器或其他硬件逻辑设备或电路的内部或外部。在至少一个实施例中,代码和/或数据存储601可以是高速缓存存储器、动态随机可寻址存储器(“dram”)、静态随机可寻址存储器(“sram”)、非易失性存储器(例如闪存)或其他存储。在至少一个实施例中,对代码和/或数据存储601是在处理器的内部还是外部的选择,例如,或者由dram、sram、闪存或某种其他存储类型组成,可以取决于存储片上与片外的可用存储空间,正在执行训练和/或推理功能的

延迟要求,在神经网络的推理和/或训练中使用的数据的批大小或这些因素的某种组合。

68.在至少一个实施例中,推理和/或训练逻辑615可以包括但不限于代码和/或数据存储605,用于存储与在一个或更多个实施例的方面中被训练为和/或用于推理的神经网络的神经元或层相对应的反向和/或输出权重和/或输入/输出数据。在至少一个实施例中,在使用一个或更多个实施例的方面训练和/或推理期间,代码和/或数据存储605存储在输入/输出数据和/或权重参数的反向传播期间结合一个或更多个实施例训练或使用的神经网络的每个层的权重参数和/或输入/输出数据。在至少一个实施例中,训练逻辑615可以包括或耦合到用于存储图代码或其他软件以控制时序和/或顺序的代码和/或数据存储605,其中权重和/或其他参数信息被加载以配置逻辑,该逻辑包括整数和/或浮点单元(统称为算术逻辑单元(alu))。在至少一个实施例中,代码(诸如图代码)基于该代码所对应的神经网络的架构将权重或其他参数信息加载到处理器alu中。在至少一个实施例中,代码和/或数据存储605的任何部分可以与其他片上或片外数据存储一起包括,包括处理器的l1、l2或l3高速缓存或系统存储器。在至少一个实施例中,代码和/或数据存储605的任何部分可以在一个或更多个处理器或其他硬件逻辑设备或电路上的内部或外部。在至少一个实施例中,代码和/或数据存储605可以是高速缓存存储器、dram、sram、非易失性存储器(例如闪存)或其他存储。在至少一个实施例中,代码和/或数据存储605是在处理器的内部还是外部的选择,例如,是由dram、sram、闪存还是其他某种存储类型组成,取决于片上与片外的可用存储,正在执行的训练和/或推理功能的延迟要求,在神经网络的推理和/或训练中使用的数据的批大小或这些因素的某种组合。

69.在至少一个实施例中,代码和/或数据存储601以及代码和/或数据存储605可以是分开的存储结构。在至少一个实施例中,代码和/或数据存储601以及代码和/或数据存储605可以是相同的存储结构。在至少一个实施例中,代码和/或数据存储601以及代码和/或数据存储605可以部分是相同的存储结构而部分是分开的存储结构。在至少一个实施例中,代码和/或数据存储601以及代码和/或数据存储605的任何部分可以与其他片上或片外数据存储包括在一起,包括处理器的l1、l2或l3高速缓存或系统存储器。

70.在至少一个实施例中,推理和/或训练逻辑615可以包括但不限于一个或更多个算术逻辑单元(“alu”)610(包括整数和/或浮点单元),用于至少部分地基于训练和/或推理代码(例如,图代码)或由其指示来执行逻辑和/或数学运算,其结果可能会产生存储在激活存储620中的激活(例如,来自神经网络内部的层或神经元的输出值),其是存储在代码和/或数据存储601和/或代码和/或数据存储605中的输入/输出和/或权重参数数据的函数。在至少一个实施例中,激活响应于执行指令或其他代码,根据由alu610执行的线性代数和/或基于矩阵的数学生成在激活存储620中存储的激活,其中存储在代码和/或数据存储605中和/或代码和/或数据存储601中的权重值用作操作数以及其他值,例如偏置值、梯度信息、动量值或其他参数或超参数,可以将任何或所有这些存储在代码和/或数据存储605或代码和/或数据存储601或其他片上或片外存储中。

71.在至少一个实施例中,一个或更多个处理器或其他硬件逻辑设备或电路中包括一个或更多个alu 610,而在另一实施例中,一个或更多个alu610可以在处理器或其他硬件逻辑设备或使用它们(例如协处理器)的电路外。在至少一个实施例中,可以将一个或更多个alu 610包括在处理器的执行单元之内,或者以其他方式包括在由处理器的执行单元可访

问的alu库(bank)中,该处理器的执行单元可以在同一处理器内或者分布在不同类型的不同处理器之间(例如,中央处理单元、图形处理单元、固定功能单元等)。在至少一个实施例中,代码和/或数据存储601、代码和/或数据存储605以及激活存储620可以在相同处理器或其他硬件逻辑设备或电路上,而在另一实施例中,它们可以在不同的处理器或其他硬件逻辑设备或电路中,或在相同和不同处理器或其他硬件逻辑设备或电路的某种组合中。在至少一个实施例中,激活存储620的任何部分可以与其他片上或片外数据存储包括在一起,包括处理器的l1、l2或l3高速缓存或系统存储器。此外,推理和/或训练代码可以与处理器或其他硬件逻辑或电路可访问的其他代码一起存储,并可以使用处理器的提取、解码、调度、执行、退出和/或其他逻辑电路来提取和/或处理。

72.在至少一个实施例中,激活存储620可以是高速缓存存储器、dram、sram、非易失性存储器(例如,闪存)或其他存储。在至少一个实施例中,激活存储620可以完全地或部分地在一个或更多个处理器或其他逻辑电路内部或外部。在至少一个实施例中,可以根据片上与片外的可用存储、执行训练和/或推理功能的延迟要求、在推理和/或训练神经网络中使用的数据的批大小或这些因素的某种组合,选择激活存储620是在处理器的内部还是外部,例如,或者包含dram、sram、闪存或其他存储类型。在至少一个实施例中,图6a中所示的推理和/或训练逻辑615可以与专用集成电路(“asic”)结合使用,例如来自google的处理单元、来自graphcore

tm

的推理处理单元(ipu)或来自intel公司的(例如“lake crest”)处理器。在至少一个实施例中,图6a所示的推理和/或训练逻辑615可与中央处理单元(“cpu”)硬件、图形处理单元(“gpu”)硬件或其他硬件(例如现场可编程门阵列(“fpga”))结合使用。

73.图6b示出了根据至少一个实施例的推理和/或训练逻辑615。在至少一个实施例中,推理和/或训练逻辑615可以包括但不限于硬件逻辑,其中计算资源被专用或以其他方式排他地连同对应于神经网络内的一层或更多层神经元的权重值或其他信息一起使用。在至少一个实施例中,图6b中所示的推理和/或训练逻辑615可以与专用集成电路(asic)结合使用,例如来自google的处理单元,来自graphcore

tm

的推理处理单元(ipu)或来自intel公司的(例如“lake crest”)处理器。在至少一个实施例中,图6b中所示的推理和/或训练逻辑615可以与中央处理单元(cpu)硬件、图形处理单元(gpu)硬件或其他硬件(例如现场可编程门阵列(fpga))结合使用。在至少一个实施例中,推理和/或训练逻辑615包括但不限于代码和/或数据存储601以及代码和/或数据存储605,其可以用于存储代码(例如,图代码)、权重值和/或其他信息,包括偏置值、梯度信息、动量值和/或其他参数或超参数信息。在图6b中所示的至少一个实施例中,代码和/或数据存储601以及代码和/或数据存储605中的每一个都分别与专用计算资源(例如计算硬件602和计算硬件606)相关联。在至少一个实施例中,计算硬件602和计算硬件606中的每一个包括一个或更多个alu,这些alu仅分别对存储在代码和/或数据存储601和代码和/或数据存储605中的信息执行数学函数(例如线性代数函数),执行函数的结果被存储在激活存储620中。

74.在至少一个实施例中,代码和/或数据存储601和605以及相应的计算硬件602和606中的每一个分别对应于神经网络的不同层,使得从代码和/或数据存储601和计算硬件602的一个“存储/计算对601/602”得到的激活提供作为代码和/或数据存储605和计算硬件

606的下一个“存储/计算对605/606”的输入,以便反映神经网络的概念组织。在至少一个实施例中,每个存储/计算对601/602和605/606可以对应于一个以上的神经网络层。在至少一个实施例中,在推理和/或训练逻辑615中可以包括在存储计算对601/602和605/606之后或与之并行的附加存储/计算对(未示出)。

75.数据中心

76.图7示出了可以使用至少一个实施例的示例数据中心700。在至少一个实施例中,数据中心700包括数据中心基础设施层710、框架层720、软件层730和应用程序层740。

77.在至少一个实施例中,如图7所示,数据中心基础设施层710可以包括资源协调器712、分组计算资源714和节点计算资源(“节点c.r.”)716(1)

‑

716(n),其中“n”代表正整数。在至少一个实施例中,节点c.r.716(1)

‑

716(n)可以包括但不限于任何数量的中央处理单元(“cpu”)或其他处理器(包括加速器、现场可编程门阵列(fpga)、图形处理器等),存储器设备(例如动态只读存储器)、存储设备(例如,固态硬盘或磁盘驱动器),网络输入/输出(“nw i/o”)设备,网络交换机,虚拟机(“vm”),电源模块和冷却模块等。在至少一个实施例中,节点c.r.716(1)

‑

716(n)中的一个或更多个节点c.r.可以是具有一个或更多个上述计算资源的服务器。

78.在至少一个实施例中,分组计算资源714可以包括容纳在一个或更多个机架内的节点c.r.的单独分组(未示出),或者容纳在各个地理位置的数据中心内的许多机架(也未示出)。分组的计算资源714内的节点c.r.的单独分组可以包括可以被配置或分配为支持一个或更多个工作负载的分组的计算、网络、存储器或存储资源。在至少一个实施例中,可以将包括cpu或处理器的几个节点c.r.分组在一个或更多个机架内,以提供计算资源来支持一个或更多个工作负载。在至少一个实施例中,一个或更多个机架还可以包括任何数量的电源模块、冷却模块和网络交换机,以任意组合。

79.在至少一个实施例中,资源协调器712可以配置或以其他方式控制一个或更多个节点c.r.716(1)

‑

716(n)和/或分组的计算资源714。在至少一个实施例中,资源协调器712可以包括用于数据中心700的软件设计基础结构(“sdi”)管理实体。在至少一个实施例中,资源协调器可以包括硬件、软件或其某种组合。

80.在至少一个实施例中,如图7所示,框架层720包括作业调度器722、配置管理器724、资源管理器726和分布式文件系统728。在至少一个实施例中,框架层720可以包括支持软件层730的软件732和/或应用程序层740的一个或更多个应用程序742的框架。在至少一个实施例中,软件732或应用程序742可以分别包括基于web的服务软件或应用程序,例如由amazon web services,google cloud和microsoft azure提供的服务或应用程序。在至少一个实施例中,框架层720可以是但不限于一种免费和开放源软件网络应用程序框架,例如可以利用分布式文件系统728来进行大范围数据处理(例如“大数据”)的apache sparktm(以下称为“spark”)。在至少一个实施例中,作业调度器732可以包括spark驱动器,以促进对数据中心700的各个层所支持的工作负载进行调度。在至少一个实施例中,配置管理器724可以能够配置不同的层,例如软件层730和包括spark和用于支持大规模数据处理的分布式文件系统728的框架层720。在至少一个实施例中,资源管理器726能够管理映射到或分配用于支持分布式文件系统728和作业调度器722的集群或分组计算资源。在至少一个实施例中,集群或分组计算资源可以包括数据中心基础设施层710上的分组的计算资源714。在

至少一个实施例中,资源管理器726可以与资源协调器712协调以管理这些映射的或分配的计算资源。

81.在至少一个实施例中,包括在软件层730中的软件732可以包括由节点c.r.716(1)

‑

716(n)的至少一部分,分组的计算资源714和/或框架层720的分布式文件系统728使用的软件。一种或更多种类型的软件可以包括但不限于internet网页搜索软件、电子邮件病毒扫描软件、数据库软件和流视频内容软件。

82.在至少一个实施例中,应用程序层740中包括的一个或更多个应用程序742可以包括由节点c.r.716(1)

‑

716(n)的至少一部分、分组计算资源714和/或框架层720的分布式文件系统728使用的一种或更多种类型的应用程序。一种或更多种类型的应用程序可以包括但不限于任何数量的基因组学应用程序、认知计算、和机器学习应用程序,包括训练或推理软件,机器学习框架软件(例如pytorch、tensorflow、caffe等)或其他与一个或更多个实施例结合使用的机器学习应用程序。

83.在至少一个实施例中,配置管理器724、资源管理器726和资源协调器712中的任何一个可以基于以任何技术上可行的方式获取的任何数量和类型的数据来实现任何数量和类型的自我修改动作。在至少一个实施例中,自我修改动作可以减轻数据中心700的数据中心操作员做出可能不好的配置决定并且可以避免数据中心的未充分利用和/或执行差的部分。

84.在至少一个实施例中,数据中心700可以包括工具、服务、软件或其他资源,以根据本文所述的一个或更多个实施例来训练一个或更多个机器学习模型或者使用一个或更多个机器学习模型来预测或推理信息。例如,在至少一个实施例中,可以通过使用上文关于数据中心700描述的软件和计算资源,根据神经网络架构通过计算权重参数来训练机器学习模型。在至少一个实施例中,通过使用通过本文所述的一种或更多种训练技术计算出的权重参数,可以使用上面与关于数据中心700所描述的资源,使用对应于一个或更多个神经网络的经训练的机器学习模型来推理或预测信息。

85.在至少一个实施例中,数据中心可以使用cpu、专用集成电路(asic)、gpu、fpga或其他硬件来使用上述资源来执行训练和/或推理。此外,上述的一个或更多个软件和/或硬件资源可以配置成一种服务,以允许用户训练或执行信息推理,例如图像识别、语音识别或其他人工智能服务。

86.推理和/或训练逻辑615用于执行与一个或更多个实施例相关联的推理和/或训练操作。本文结合图6a和/或图6b提供关于推理和/或训练逻辑615的细节。在至少一个实施例中,推理和/或训练逻辑615可以在图7的系统中使用,用于至少部分地基于使用神经网络训练操作、神经网络函数和/或体系架构、或者本文所述的神经网络用例计算的权重参数推理或预测操作。

87.推理和/或训练逻辑615用于执行与一个或更多个实施例相关联的推理和/或训练操作。在至少一个实施例中,此逻辑可与这些图的组件一起使用,以选择在呈现一个或更多个视频片段期间与一个或更多个观看者的所确定的情绪相关联的那些片段。

88.计算机系统

89.图8是示出根据至少一个实施例示例性计算机系统的框图,该示例性计算机系统可以是具有互连的设备和组件的系统,片上系统(soc)或它们的某种形成有处理器的组合,

该处理器可以包括执行单元以执行指令。在至少一个实施例中,根据本公开,例如本文所述的实施例,计算机系统800可以包括但不限于组件,例如处理器802,其执行单元包括逻辑以执行用于过程数据的算法。在至少一个实施例中,计算机系统800可以包括处理器,例如可从加利福尼亚圣塔克拉拉的英特尔公司(intel corporation of santa clara,california)获得的处理器家族、xeon

tm

、xscale

tm

和/或strongarm

tm

,core

tm

或nervana

tm

微处理器,尽管也可以使用其他系统(包括具有其他微处理器的pc、工程工作站、机顶盒等)。在至少一个实施例中,计算机系统800可以执行可从华盛顿州雷蒙德市的微软公司(microsoft corporation of redmond,wash.)获得的windows操作系统版本,尽管其他操作系统(例如unix和linux)、嵌入式软件和/或图形用户界面也可以使用。

90.实施例可以用在其他设备中,例如手持设备和嵌入式应用程序。手持设备的一些示例包括蜂窝电话、互联网协议(internet protocol)设备、数码相机、个人数字助理(“pda”)和手持pc。在至少一个实施例中,嵌入式应用程序可以包括微控制器、数字信号处理器(“dsp”)、片上系统、网络计算机(“netpc”)、机顶盒、网络集线器、广域网(“wan”)交换机,或根据至少一个实施例可以执行一个或更多个指令的任何其他系统。

91.在至少一个实施例中,计算机系统800可包括但不限于处理器802,该处理器802可包括但不限于一个或更多个执行单元808,以根据本文描述的技术执行机器学习模型训练和/或推理。在至少一个实施例中,计算机系统800是单处理器台式机或服务器系统,但是在另一实施例中,计算机系统800可以是多处理器系统。在至少一个实施例中,处理器802可以包括但不限于复杂指令集计算机(“cisc”)微处理器、精简指令集计算(“risc”)微处理器、超长指令字(“vliw”)微处理器、实现指令集组合的处理器,或任何其他处理器设备,例如数字信号处理器。在至少一个实施例中,处理器802可以耦合到处理器总线810,该处理器总线810可以在处理器802与计算机系统800中的其他组件之间传输数据信号。

92.在至少一个实施例中,处理器802可以包括但不限于1级(“l1”)内部高速缓存存储器(“cache”)804。在至少一个实施例中,处理器802可以具有单个内部高速缓存或多级内部缓存。在至少一个实施例中,高速缓存存储器可以驻留在处理器802的外部。根据特定的实现和需求,其他实施例也可以包括内部和外部高速缓存的组合。在至少一个实施例中,寄存器文件806可以在各种寄存器中存储不同类型的数据,包括但不限于整数寄存器、浮点寄存器、状态寄存器和指令指针寄存器。

93.在至少一个实施例中,包括但不限于执行整数和浮点运算的逻辑的执行单元808,其也位于处理器802中。在至少一个实施例中,处理器802还可以包括微码(“ucode”)只读存储器(“rom”),用于存储某些宏指令的微代码。在至少一个实施例中,执行单元808可以包括用于处理封装指令集809的逻辑。在至少一个实施例中,通过将打包指令集809包括在通用处理器的指令集中,以及要执行指令的相关电路,可以使用通用处理器802中的打包(packed)数据来执行许多多媒体应用程序使用的操作。在一个或更多个实施例中,可以通过使用处理器的数据总线的全宽度来在封装的数据上执行操作来加速和更有效地执行许多多媒体应用程序,这可能不需要在该处理器的数据总线上传输较小的数据单元来一次执行一个数据元素的一个或更多个操作。

94.在至少一个实施例中,执行单元808也可以用在微控制器、嵌入式处理器、图形设

备、dsp和其他类型的逻辑电路中。在至少一个实施例中,计算机系统800可以包括但不限于存储器820。在至少一个实施例中,存储器820可以实现为动态随机存取存储器(“dram”)设备、静态随机存取存储器(“sram”)设备、闪存设备或其他存储器设备。在至少一个实施例中,存储器820可以存储由处理器802可以执行的由数据信号表示的指令819和/或数据821。

95.在至少一个实施例中,系统逻辑芯片可以耦合到处理器总线810和存储器820。在至少一个实施例中,系统逻辑芯片可以包括但不限于存储器控制器集线器(“mch”)816,并且处理器802可以经由处理器总线810与mch 816通信。在至少一个实施例中,mch 816可以提供到存储器820的高带宽存储器路径818以用于指令和数据存储以及用于图形命令、数据和纹理的存储。在至少一个实施例中,mch 816可以在处理器802、存储器820和计算机系统800中的其他组件之间启动数据信号,并且在处理器总线810、存储器820和系统i/o接口822之间桥接数据信号。在至少一个实施例中,系统逻辑芯片可以提供用于耦合到图形控制器的图形端口。在至少一个实施例中,mch 816可以通过高带宽存储器路径818耦合到存储器820,并且图形/视频卡812可以通过加速图形端口(accelerated graphics port)(“agp”)互连814耦合到mch 816。

96.在至少一个实施例中,计算机系统800可以使用系统i/o接口822,其是将mch 816耦合到i/o控制器集线器(“ich”)830的专有集线器接口总线。在至少一个实施例中,ich 830可以通过本地i/o总线提供与某些i/o设备的直接连接。在至少一个实施例中,本地i/o总线可以包括但不限于用于将外围设备连接到存储器820、芯片组和处理器802的高速i/o总线。示例可以包括但不限于音频控制器829、固件集线器(“flash bios”)828、无线收发器826、数据存储824、包含用户输入和键盘接口825的传统i/o控制器823、串行扩展端口827(例如通用串行总线(usb))和网络控制器834。数据存储824可以包括硬盘驱动器、软盘驱动器、cd

‑

rom设备、闪存设备或其他大容量存储设备。

97.在至少一个实施例中,图8示出了包括互连的硬件设备或“芯片”的系统,而在其他实施例中,图8可以示出示例性片上系统(soc)。在至少一个实施例中,图8中示出的设备可以与专有互连、标准化互连(例如,pcie)或其某种组合互连。在至少一个实施例中,计算机系统800的一个或更多个组件使用计算快速链路(cxl)互连来互连。

98.推理和/或训练逻辑615用于执行与一个或更多个实施例相关联的推理和/或训练操作。本文结合图6a和/或图6b提供关于推理和/或训练逻辑615的细节。在至少一个实施例中,推理和/或训练逻辑615可以在图8的系统中使用,用于至少部分地基于使用神经网络训练操作、神经网络函数和/或体系架构、或者本文所述的神经网络用例计算的权重参数推理或预测操作。

99.推理和/或训练逻辑615用于执行与一个或更多个实施例相关联的推理和/或训练操作。在至少一个实施例中,此逻辑可与这些图的组件一起使用,以选择在呈现一个或更多个视频片段期间与一个或更多个观看者的所确定的情绪相关联的那些片段。

100.图9是示出根据至少一个实施例的用于利用处理器910的电子设备900的框图。在至少一个实施例中,电子设备900可以是,例如但不限于,笔记本电脑、塔式服务器、机架服务器、刀片服务器、膝上型计算机、台式机、平板电脑、移动设备、电话、嵌入式计算机或任何其他合适的电子设备。

101.在至少一个实施例中,系统900可以包括但不限于通信地耦合到任何合适数量或

种类的组件、外围设备、模块或设备的处理器910。在至少一个实施例中,处理器910使用总线或接口耦合,诸如i2c总线、系统管理总线(“smbus”)、低引脚数(lpc)总线、串行外围接口(“spi”)、高清音频(“hda”)总线、串行高级技术附件(“sata”)总线、通用串行总线(“usb”)(1、2、3版等)或通用异步接收器/发送器(“uart”)总线。在至少一个实施例中,图9示出了系统,该系统包括互连的硬件设备或“芯片”,而在其他实施例中,图9可以示出示例性片上系统(soc)。在至少一个实施例中,图9中所示的设备可以与专有互连线、标准化互连(例如,pcie)或其某种组合互连。在至少一个实施例中,图9的一个或更多个组件使用计算快速链路(cxl)互连线来互连。

102.在至少一个实施例中,图9可以包括显示器924、触摸屏925、触摸板930、近场通信单元(“nfc”)945、传感器集线器940、热传感器946、快速芯片组(“ec”)935、可信平台模块(“tpm”)938、bios/固件/闪存(“bios,fw flash”)922、dsp960、驱动器920(例如固态磁盘(“ssd”)或硬盘驱动器(“hdd”))、无线局域网单元(“wlan”)950、蓝牙单元952、无线广域网单元(“wwan”)956、全球定位系统(gps)955、相机(“usb 3.0相机”)954(例如usb 3.0相机)和/或以例如lpddr3标准实现的低功耗双倍数据速率(“lpddr”)存储器单元(“lpddr3”)915。这些组件可以各自以任何合适的方式实现。

103.在至少一个实施例中,其他组件可以通过本文所述的组件通信地耦合到处理器910。在至少一个实施例中,加速度计941、环境光传感器(“als”)942、罗盘943和陀螺仪944可以可通信地耦合到传感器集线器940。在至少一个实施例中,热传感器939、风扇937、键盘936和触摸板930可以通信地耦合到ec 935。在至少一个实施例中,扬声器963、耳机964和麦克风(“mic”)965可以通信地耦合到音频单元(“音频编解码器和d类放大器”)962,其又可以通信地耦合到dsp 960。在至少一个实施例中,音频单元962可以包括例如但不限于音频编码器/解码器(“编解码器”)和d类放大器。在至少一个实施例中,sim卡(“sim”)957可以通信地耦合到wwan单元956。在至少一个实施例中,组件(诸如wlan单元950和蓝牙单元952以及wwan单元956)可以被实现为下一代形式因素(ngff)。

104.推理和/或训练逻辑615用于执行与一个或更多个实施例相关联的推理和/或训练操作。本文结合图6a和/或图6b提供关于推理和/或训练逻辑615的细节。在至少一个实施例中,推理和/或训练逻辑615可以在图9的系统中使用,用于至少部分地基于使用神经网络训练操作、神经网络函数和/或体系架构、或者本文所述的神经网络用例计算的权重参数推理或预测操作。

105.推理和/或训练逻辑615用于执行与一个或更多个实施例相关联的推理和/或训练操作。在至少一个实施例中,此逻辑可与这些图的组件一起使用,以选择在呈现一个或更多个视频片段期间与一个或更多个观看者的所确定的情绪相关联的那些片段。

106.图10示出了根据至少一个实施例的计算机系统1000。在至少一个实施例中,计算机系统1000配置为实现贯穿本公开描述的各种过程和方法。

107.在至少一个实施例中,计算机系统1000包括但不限于至少一个中央处理单元(“cpu”)1002,该中央处理单元(“cpu”)1002连接到使用任何合适协议实现的通信总线1010,诸如pci(“外围设备互联”)、外围组件互连express(“pci

‑

express”)、agp(“加速图形端口”)、超传输或任何其他总线或点对点通信协议。在至少一个实施例中,计算机系统1000包括但不限于主存储器1004和控制逻辑(例如,实现为硬件、软件或其组合),并且数据可以

采取随机存取存储器(“ram”)的形式存储在主存储器1004中。在至少一个实施例中,网络接口子系统(“网络接口”)1022提供到其他计算设备和网络的接口,用于从计算机系统1000接收数据并将数据传输到其他系统。

108.在至少一个实施例中,计算机系统1000在至少一个实施例中包括但不限于输入设备1008、并行处理系统1012和显示设备1006,它们可以使用常规的阴极射线管(“crt”)、液晶显示器(“lcd”)、发光二极管(“led”)、等离子显示器或其他合适的显示技术实现。在至少一个实施例中,从输入设备1008(诸如键盘、鼠标、触摸板、麦克风等)接收用户输入。在至少一个实施例中,前述模块中的每一个可以位于单个半导体平台上以形成处理系统。

109.推理和/或训练逻辑615用于执行与一个或更多个实施例相关联的推理和/或训练操作。本文结合图6a和/或图6b提供关于推理和/或训练逻辑615的细节。在至少一个实施例中,推理和/或训练逻辑615可以在图10的系统中使用,用于至少部分地基于使用神经网络训练操作、神经网络函数和/或体系架构、或者本文所述的神经网络用例计算的权重参数推理或预测操作。

110.推理和/或训练逻辑615用于执行与一个或更多个实施例相关联的推理和/或训练操作。在至少一个实施例中,此逻辑可与这些图的组件一起使用,以选择在呈现一个或更多个视频片段期间与一个或更多个观看者的所确定的情绪相关联的那些片段。

111.图11示出了根据至少一个实施例的计算机系统1100。在至少一个实施例中,计算机系统1100包括但不限于计算机1110和usb盘1120。在至少一个实施例中,计算机1110可以包括但不限于任何数量和类型的处理器(未示出)和存储器(未示出)。在至少一个实施例中,计算机1110包括但不限于服务器、云实例、膝上型计算机和台式计算机。

112.在至少一个实施例中,usb盘1120包括但不限于处理单元1130、usb接口1140和usb接口逻辑1150。在至少一个实施例中,处理单元1130可以是任何指令执行系统、装置或能够执行指令的设备。在至少一个实施例中,处理单元1130可以包括但不限于任何数量和类型的处理核心(未示出)。在至少一个实施例中,处理核心1130包括专用集成电路(“asic”),该专用集成电路被优化为执行与机器学习相关联的任何数量和类型的操作。例如,在至少一个实施例中,处理核心1130是张量处理单元(“tpc”),其被优化以执行机器学习推理操作。在至少一个实施例中,处理核心1130是视觉处理单元(“vpu”),其被优化以执行机器视觉和机器学习推理操作。

113.在至少一个实施例中,usb接口1140可以是任何类型的usb连接器或usb插座。例如,在至少一个实施例中,usb接口1140是用于数据和电源的usb 3.0type

‑

c插座。在至少一个实施例中,usb接口1140是usb 3.0type

‑

a连接器。在至少一个实施例中,usb接口逻辑1150可以包括使处理单元1130能够经由usb连接器1140与设备(例如计算机1110)相连接的任何数量和类型的逻辑。

114.推理和/或训练逻辑615用于执行与一个或更多个实施例相关联的推理和/或训练操作。本文结合图6a和/或图6b提供关于推理和/或训练逻辑615的细节。在至少一个实施例中,推理和/或训练逻辑615可以在图11的系统中使用,用于至少部分地基于使用神经网络训练操作、神经网络函数和/或体系架构、或者本文所述的神经网络用例计算的权重参数推理或预测操作。

115.推理和/或训练逻辑615用于执行与一个或更多个实施例相关联的推理和/或训练

操作。在至少一个实施例中,此逻辑可与这些图的组件一起使用,以选择在呈现一个或更多个视频片段期间与一个或更多个观看者的所确定的情绪相关联的那些片段。

116.图12a示出了示例性架构,其中多个gpu 1210

‑

1213通过高速链路1240

‑

1243(例如,总线/点对点互连等)通信地耦合到多个多核心处理器1205

‑

1206。在一个实施例中,高速链路1240

‑

1243支持4gb/s、30gb/s、80gb/s或更高的通信吞吐量。可以使用各种互连协议,包括但不限于pcie4.0或5.0以及nvlink 2.0。

117.此外,在一个实施例中,两个或更多个gpu 1210

‑

1213通过高速链路1229

‑

1230互连,该高速链路可以使用与用于高速链路1240

‑

1243的协议/链路相同或不同的协议/链路来实现。类似地,两个或更多个多核心处理器1205

‑

1206可以通过高速链路1228连接,该高速链路可以是以20gb/s、30gb/s、120gb/s或更高的速度运行的对称多处理器(smp)总线。可替代地,可以使用类似的协议/链路(例如,通过公共互连结构)来完成图12a中所示的各种系统组件之间的所有通信。

118.在一个实施例中,每个多核心处理器1205

‑

1206分别经由存储器互连1226

‑

1227通信地耦合到处理器存储器1201

‑

1202,并且每个gpu 1210

‑

1213分别通过gpu存储器互连1250

‑

1253通信地耦合到gpu存储器1220

‑

1223。存储器互连1226

‑

1227和1250

‑

1253可以利用相同或不同的存储器访问技术。作为示例而非限制,处理器存储器1201

‑

1202和gpu存储器1220

‑

1223可以是易失性存储器,诸如动态随机存取存储器(dram)(包括堆叠的dram)、图形ddr sdram(gddr)(例如gddr5、gddr6),或高带宽存储器(hbm),和/或可以是非易失性存储器,例如3d xpoint或nano

‑

ram。在一个实施例中,处理器存储器1201

‑

1202的某些部分可以是易失性存储器,而另一部分可以是非易失性存储器(例如,使用两级存储器(2lm)层次结构)。

119.如下面所述,尽管各种处理器1205

‑

1206和gpu 1210

‑

1213可以分别物理地耦合到特定存储器1201

‑

1202、1220

‑

1223,可以实现统一存储器架构,其中相同的虚拟系统地址空间(也称为“有效地址”空间)分布在各个物理存储器之间。例如,处理器存储器1201

‑

1202可以各自包含64gb的系统存储器地址空间,并且gpu存储器1220

‑

1223可以各自包含32gb的系统存储器地址空间(在该示例中,导致总计256gb的可寻址存储器)。

120.图12b示出了根据一个示例性实施例的用于多核心处理器1207和图形加速模块1246之间互连的附加细节。图形加速模块1246可以包括集成在线路卡上的一个或更多个gpu芯片,该线路卡经由高速链路1240耦合到处理器1207。替代地,图形加速模块1246可以集成在具有处理器1207的同一封装或芯片上。

121.在至少一个实施例中,所示的处理器1207包括多个核心1260a

‑

1260d,每个核心都具有转换后备缓冲区1261a

‑

1261d和一个或更多个高速缓存1262a

‑

1262d。在至少一个实施例中,核心1260a

‑

1260d可以包括未示出的各种其他组件,用于执行指令和处理数据。高速缓存1262a

‑

1262d可以包括级别1(l1)和级别2(l2)高速缓存。此外,一个或更多个共享高速缓存1256可以被包括在高速缓存1262a

‑

1262d中,并且由各组核心1260a

‑

1260d共享。例如,处理器1207的一个实施例包括24个核心,每个核心具有其自己的l1高速缓存,十二个共享的l2高速缓存,和十二个共享的l3高速缓存。在该实施例中,两个相邻核心共享一个或更多个l2和l3高速缓存。处理器1207和图形加速模块1246与系统存储器1214连接,该系统存储器1214可以包括图12a中的处理器存储器1201

‑

1202。

122.通过一致性总线1264经由核心间通信为存储在各个高速缓存1262a

‑

1262d、1256和系统存储器1214中的数据和指令维护一致性。在至少一个实施例中,例如,每个高速缓存可以具有与其相关联的高速缓存一致性逻辑/电路,以响应于检测到对特定高速缓存行的读取或写入通过一致性总线1264进行通信。在一个实现方式中,通过一致性总线1264实现高速缓存监听协议,以监听(snoop)高速缓存访问。

123.在至少一个实施例中,代理电路1225将图形加速模块1246通信地耦合到一致性总线1264,从而允许图形加速模块1246作为核心1260a

‑

1260d的对等方参与高速缓存一致性协议。特别地,在至少一个实施例中,接口1235通过高速链路1240(例如,pcie总线、nvlink等)提供到代理电路1225的连接,并且接口1237将图形加速模块1246连接到链路1240。

124.在一个实现方式中,加速器集成电路1236代表图形加速模块1246的多个图形处理引擎1231,1232,n提供高速缓存管理、存储器访问、上下文管理和中断管理服务。在至少一个实施例中,图形处理引擎1231,1232,n可各自包括单独的图形处理单元(gpu)。替代地,图形处理引擎1231,1232,n可以包括gpu内的不同类型的图形处理引擎,诸如图形执行单元、媒体处理引擎(例如,视频编码器/解码器)、采样器和blit引擎。在至少一个实施例中,图形加速模块1246可以是具有多个图形处理引擎1231

‑

1232,n的gpu,或者图形处理引擎1231

‑

1232,n可以是集成在通用封装、线路卡或芯片上的各个gpu。

125.在一个实施例中,加速器集成电路1236包括存储器管理单元(mmu)1239,用于执行各种存储器管理功能,例如虚拟到物理存储器转换(也称为有效到真实存储器转换),还包括用于访问系统存储器1214的存储器访问协议。mmu 1239还可包括转换后备缓冲区(tlb)(未示出),用于高速缓存虚拟/有效到物理/真实地址转换。在一个实现方式中,高速缓存1238存储命令和数据,用于图形处理引擎1231

‑

1232,n有效地访问。在一个实现方式中,将存储在高速缓存1238和图形存储器1233

‑

1234,m,中的数据与核心高速缓存1262a

‑

1262d、1256和系统存储器1214保持一致。如前所述,可以经由代表高速缓存1238和图形存储器1233

‑

1234,m的代理电路1225来完成该任务(例如,将与处理器高速缓存1262a

‑

1262d、1256上的高速缓存行的修改/访问有关的更新发送到高速缓存1238,并从高速缓存1238接收更新)。

126.在至少一个实施例中,一组寄存器1245存储由图形处理引擎1231

‑

1232,n执行的线程的上下文数据,并且上下文管理电路1248管理线程上下文。例如,上下文管理电路1248可以执行保存和恢复操作,以在上下文切换期间保存和恢复各个线程的上下文(例如,其中保存第一线程并且存储第二线程,以便可以由图形处理引擎执行第二线程)。例如,上下文管理电路1248在上下文切换时,可以将当前寄存器值存储到存储器中的(例如,由上下文指针标识的)指定区域。然后,当返回上下文时可以恢复寄存器值。在一个实施例中,中断管理电路1247接收并处理从系统设备接收的中断。

127.在一个实现方式中,mmu 1239将来自图形处理引擎1231的虚拟/有效地址转换为系统存储器1214中的真实/物理地址。在至少一个实施例中,加速器集成电路1236支持多个(例如,4、8、16)图形加速器模块1246和/或其他加速器设备。图形加速器模块1246可以专用于在处理器1207上执行的单个应用程序,或者可以在多个应用程序之间共享。在至少一个实施例中,呈现了虚拟化的图形执行环境,其中图形处理引擎1231

‑

1232,n的资源与多个应用程序或虚拟机(vm)共享。在至少一个实施例中,可以基于处理要求和与vm和/或应用程序

相关联的优先级,将资源细分为“切片”,其被分配给不同的vm和/或应用程序。

128.在至少一个实施例中,加速器集成电路1236作为图形加速模块1246的系统的桥来执行,并提供地址转换和系统存储器高速缓存服务。另外,加速器集成电路1236可以为主机处理器提供虚拟化设施,以管理图形处理引擎1231

‑

1232,n的虚拟化、中断和存储器管理。

129.由于图形处理引擎1231

‑

1232,n的硬件资源被明确地映射到主机处理器1207看到的真实地址空间,因此任何主机处理器都可以使用有效地址值直接寻址这些资源。加速器集成电路1236的一个功能是物理分离图形处理引擎1231

‑

1232,n,使得它们在系统看来为独立的单元。

130.在至少一个实施例中,一个或更多个图形存储器1233

‑

1234,m分别耦合到每个图形处理引擎1231

‑

1232,n。图形存储器1233

‑

1234,m存储指令和数据,所述指令和数据由每个图形处理引擎1231

‑

1232,n处理。在至少一个实施例中,图形存储器1233

‑

1234,m可以是易失性存储器,例如dram(包括堆叠的dram)、gddr存储器(例如,gddr5,gddr6)或hbm,和/或可以是非易失性存储器,例如3d xpoint或nano

‑

ram。

131.在一个实施例中,为了减少链路1240上的数据流量,使用偏置技术以确保存储在图形存储器1233

‑

1234,m中的数据是图形处理引擎1231

‑

1232,n最常使用的,并且最好核心1260a

‑

1260d不使用(至少不经常使用)的数据。类似地,偏置机制试图将核心(并且优选地不是图形处理引擎1231

‑

1232,n)需要的数据保持在核心的高速缓存1262a

‑

1262d、1256和系统存储器1214中。

132.图12c示出了另一个示例性实施例,其中加速器集成电路1236被集成在处理器1207内。在该实施例中,图形处理引擎1231

‑

1232,n经由接口1237和接口1235(同样可以利用任何形式的总线或接口协议)通过高速链路1240直接与加速器集成电路1236通信。加速器集成电路1236可以执行与关于图12b描述的操作相同的操作。但是由于它紧密靠近一致性总线1264和高速缓存1262a

‑

1262d、1256,可能具有更高的吞吐量。至少一个实施例支持不同的编程模型,包括专用进程编程模型(无图形加速模块虚拟化)和共享编程模型(具有虚拟化),所述编程模型可以包括由加速器集成电路1236控制的编程模型和由图形加速模块1246控制的编程模型。

133.在至少一个实施例中,图形处理引擎1231

‑

1232,n专用于单个操作系统下的单个应用程序或进程。在至少一个实施例中,单个应用程序可以将其他应用程序请求汇聚(funnel)到图形处理引擎1231

‑

1232,n,从而在vm/分区内提供虚拟化。

134.在至少一个实施例中,图形处理引擎1231

‑

1232,n可以被多个vm/应用程序分区共享。在至少一个实施例中,共享模型可以使用系统管理程序来虚拟化图形处理引擎1231

‑

1232,n,以允许每个操作系统进行访问。对于没有管理程序的单分区系统,操作系统拥有图形处理引擎1231

‑

1232,n。在至少一个实施例中,操作系统可以虚拟化图形处理引擎1231

‑

1232,n,以提供对每个进程或应用程序的访问。

135.在至少一个实施例中,图形加速模块1246或个体图形处理引擎1231

‑

1232,n使用进程句柄来选择进程元素。在至少一个实施例中,进程元素被存储在系统存储器1214中,并且可使用本文所述的有效地址到真实地址转换技术来寻址。在至少一个实施例中,进程句柄可以是特定于实现方式的值,其在向图形处理引擎1231

‑

1232,n注册其上下文时提供给主机进程(即,调用系统软件以将进程元素添加到进程元素链接列表)。在至少一个实施例

中,进程句柄的较低16位可以是进程元素在进程元素链接列表中的偏移量。

136.图12d示出了示例性加速器集成切片1290。如本文所使用的,“切片”包括加速器集成电路1236的处理资源的指定部分。系统存储器1214中的应用程序有效地址空间1282存储进程元素1283。在一个实施例中,响应于来自在处理器1207上执行的应用程序1280的gpu调用1281,存储进程元素1283。进程元素1283包含相应的应用程序1280的进程状态。包含在进程元素1283中的工作描述符(wd)1284可以是由应用程序请求的单个作业,或者可以包含指向作业队列的指针。在至少一个实施例中,wd 1284是指向应用程序的地址空间1282中的作业请求队列的指针。

137.图形加速模块1246和/或各个图形处理引擎1231

‑

1232,n可以由系统中所有进程或进程子集共享。在至少一个实施例中,可以包括用于设置进程状态并将wd 1284发送到图形加速模块1246以在虚拟化环境中开始作业的基础设施。

138.在至少一个实施例中,专用进程编程模型是特定于实现方式的。在该模型中,单个进程拥有图形加速模块1246或个体图形处理引擎1231。当图形加速模块1246由单个进程拥有时,管理程序初始化用于所拥有的分区的加速器集成电路1236,当指派了图形加速模块1246时,操作系统初始化用于所拥有的进程的加速器集成电路1236。

139.在操作中,加速器集成切片1290中的wd获取单元1291获取下一个wd 1284,其包括要由图形加速模块1246的一个或更多个图形处理引擎完成的工作的指示。来自wd 1284的数据可以存储在寄存器1245中,并由mmu 1239、中断管理电路1247和/或上下文管理电路1248使用,如图所示。例如,mmu 1239的一个实施例包括用于访问os虚拟地址空间1285内的段/页表1286的段/页漫游电路。中断管理电路1247可以处理从图形加速模块1246接收的中断事件1292。当执行图形操作时,由图形处理引擎1231

‑

1232,n生成的有效地址1293被mmu 1239转换为真实地址。

140.在一个实施例中,为每个图形处理引擎1231

‑

1232,n和/或图形加速模块1246复制相同的一组寄存器1245,并且所述寄存器1245可以由管理程序或操作系统初始化。这些复制的寄存器中的每一个可以被包括在加速器集成切片1290中。可以由管理程序初始化的示例性寄存器在表1中示出。

[0141][0142]

表2中示出了可由操作系统初始化的示例性寄存器。

[0143][0144]

在至少一个实施例中,每个wd 1284特定于特定的图形加速模块1246和/或图形处理引擎1231

‑

1232,n。它包含图形处理引擎1231

‑

1232,n完成工作所需的所有信息,或者它可以是指向存储器位置的指针,在该存储器位置应用程序已经设置了要完成的工作的命令队列。

[0145]

图12e示出了共享模型的一个示例性实施例的附加细节。该实施例包括管理程序真实地址空间1298,其中存储了进程元素列表1299。可经由管理程序1296来访问管理程序实地址空间1298,所述管理程序1296虚拟化用于操作系统1295的图形加速模块引擎。

[0146]

在至少一个实施例中,共享编程模型允许来自系统中全部分区或分区子集的全部进程或进程子集使用图形加速模块1246。存在两种编程模型,其中图形加速模块1246由多个进程和分区共享,即,时间切片共享和图形定向共享。

[0147]

在至少一个实施例中,在该模型中,系统管理程序1296拥有图形加速模块1246,并使其功能可用于所有操作系统1295。对于图形加速模块1246通过系统管理程序1296支持虚

拟化,图形加速模块1246可以遵守一下要求:1)应用程序的作业请求必须是自主的(即,不需要在作业之间保持状态),或者图形加速模块1246必须提供上下文保存和恢复机制,2)图形加速模块1246保证应用程序的作业请求在指定的时间量内完成,包括任何转换错误,或者图形加速模块1246提供了抢占作业处理的能力,并且3)在有向共享编程模型中进行操作时,必须确保图形加速模块1246进程之间的公平性。

[0148]

在至少一个实施例中,需要应用程序1280使用图形加速模块1246类型、工作描述符(wd)、权限屏蔽寄存器(amr)值和上下文保存/ 恢复区域指针(csrp)进行操作系统1295系统调用。在至少一个实施例中,图形加速模块1246类型描述了用于系统调用的目标加速函数。在至少一个实施例中,图形加速模块1246类型可以是系统特定的值。在至少一个实施例中,wd是专门为图形加速模块1246格式化的,并且可以采用图形加速模块1246命令、指向用户定义的结构的有效地址指针、指向命令队列的有效地址指针的形式,或描述要由图形加速模块1246完成的工作的任何其他数据结构。在一个实施例中,amr值是用于当前进程的amr状态。在至少一个实施例中,传递给操作系统的值与设置amr的应用程序类似。如果加速器集成电路1236和图形加速模块1246的实现不支持用户权限屏蔽覆写寄存器(uamor),则在管理程序调用中传递amr之前,操作系统可以将当前uamor值应用于amr值。管理程序1296可以在将amr放入进程元素1283中之前选择性地应用当前权限屏蔽覆写寄存器(amor)值。在至少一个实施例中,csrp是寄存器1245中的一个,所述寄存器包含应用程序的有效地址空间1282中的区域的有效地址,供图形加速模块1246保存和恢复上下文状态。如果不需要在作业之间保存状态或者当作业被抢占时,则该指针是可选的。在至少一个实施例中,上下文保存/恢复区域可以是固定的系统存储器。

[0149]

在接收到系统调用时,操作系统1295可以验证应用程序1280已经注册并且被授予使用图形加速模块1246的权限。然后,操作系统1295使用表3中所示的信息来调用管理程序1296。

[0150][0151]

在接收到管理程序调用时,管理程序1296验证操作系统1295已注册并被授予使用图形加速模块1246的权限。然后,管理程序1296将进程元素1283放入相应的图形加速模块1246类型的进程元素链接列表中。进程元素可以包括表4中所示的信息。

[0152][0153]

在至少一个实施例中,管理程序初始化多个加速器集成切片1290寄存器1245。

[0154]

如图12f所示,在至少一个实施例中,使用统一存储器,所述统一存储器可经由用于访问物理处理器存储器1201

‑

1202和gpu存储器1220

‑

1223的公共虚拟存储器地址空间来寻址。在该实现方式中,在gpu1210

‑

1213上执行的操作利用相同的虚拟/有效存储器地址空间来访问处理器存储器1201

‑

1202,反之亦然,从而简化了可编程性。在一个实施例中,虚拟/有效地址空间的第一部分被分配给处理器存储器1201,第二部分被分配给第二处理器存储器1202,第三部分被分配给gpu存储器1220,以此类推。在至少一个实施例中,整个虚拟/有效存储器空间(有时称为有效地址空间)由此分布在处理器存储器1201

‑

1202和gpu存储器1220

‑

1223的每一个中,从而允许任何处理器或gpu采用映射到任何物理存储器的虚拟地址访问该存储器。

[0155]

在一个实施例中,一个或更多个mmu 1239a

‑

1239e内的偏置/一致性管理电路1294a

‑

1294e确保一个或更多个主机处理器(例如,1205)与gpu 1210

‑

1213的高速缓存之间的高速缓存一致性,并实现指示应在其中存储某些类型的数据的物理存储器的偏置技术。虽然在图12f中示出了偏置/一致性管理电路1294a

‑

1294e的多个实例,但可以在一个或更多个主机处理器1205的mmu内和/或在加速器集成电路1236内实现偏置/一致性电路。

[0156]

一个实施例允许将gpu附加的存储器1220

‑

1223映射为系统存储器的一部分,并使用共享虚拟存储器(svm)技术进行访问,但不会遭受与完整系统高速缓存一致性相关的性能缺陷。在至少一个实施例中,将gpu附加的存储器1220

‑

1223作为系统存储器来访问而无需繁重的高速缓存一致性开销的能力为gpu卸载提供了有利的操作环境。该布置允许主机处理器1205的软件设置操作数并访问计算结果,而没有传统的i/o dma数据拷贝的开销。这样的传统拷贝包括驱动程序调用、中断和存储器映射i/o(mmio)访问,相对于简单的存储器访问而言,这些访问效率均较低。在至少一个实施例中,在没有高速缓存一致性开销的情况

下访问gpu附加的存储器1220

‑

1223的能力对于卸载的计算的执行时间可能是关键的。例如,在具有大量流式写入存储器流量的情况下,高速缓存一致性开销可以显著降低gpu 1210

‑

1213所看到的有效写入带宽。在至少一个实施例中,操作数设置的效率、结果访问的效率和gpu计算的效率可能会在确定gpu卸载的有效性方面发挥作用。

[0157]

在至少一个实施例中,gpu偏置和主机处理器偏置的选择由偏置跟踪器数据结构驱动。例如,可以使用偏置表,所述偏置表可以是页面粒度结构(例如,以存储器页面的粒度来控制),该页面粒度结构包括每个gpu附加的存储器页面1或2位。在至少一个实施例中,在gpu 1210

‑

1213中具有或不具有偏置高速缓存(例如,用于高速缓存偏置表的频繁/最近使用的条目)的情况下,可以在一个或更多个gpu附加的存储器1220

‑

1223的被盗存储器范围中实现偏置表。替代地,可以在gpu内维护整个偏置表。

[0158]

在至少一个实施例中,在实际访问gpu存储器之前,访问与对gpu附加的存储器1220

‑

1223的每次访问相关联的偏置表条目,从而引起以下操作。首先,来自gpu 1210

‑

1213的在gpu偏置中找到其页面的本地请求被直接转发到对应的gpu存储器1220

‑

1223。来自gpu的在主机偏置中找到其页面的本地请求被转发至处理器1205(例如,通过本文所述的高速链路)。在一个实施例中,来自处理器1205的在主机处理器偏置中找到所请求页面的请求完成了与正常存储器读取类似的请求。替代地,可以将指向gpu偏置页面的请求转发到gpu 1210

‑

1213。在至少一个实施例中,如果gpu当前不使用页面,则gpu可随后将页面迁移到主机处理器偏置。在至少一个实施例中,页面的偏置状态可以通过基于软件的机制、基于硬件辅助的软件的机制、或者在有限的情况下通过纯粹基于硬件的机制来改变。

[0159]

一种用于改变偏置状态的机制采用api调用(例如opencl),所述api调用随后调用gpu的设备驱动程序,所述设备驱动程序随后发送消息(或使命令描述符入队)到gpu,引导gpu改变偏置状态,并在某些迁移中在主机中执行高速缓存刷新操作。在至少一个实施例中,高速缓存刷新操作用于从主机处理器1205偏置到gpu偏置的迁移,但是不用于相反的迁移。

[0160]

在一个实施例中,高速缓存一致性是通过暂时渲染主机处理器1205无法高速缓存的gpu偏置页面来维护的。为了访问这些页面,处理器1205可以请求来自gpu 1210的访问,gpu 1210可以或可以不立即授予访问权限。因此,为了减少处理器1205和gpu 1210之间的通信,确保gpu偏置页面是gpu所需的页面而不是主机处理器1205所需的页面是有益的,反之亦然。

[0161]

推理和/或训练逻辑615用于执行一个或更多个实施例。本文结合图6a和/或图6b提供关于推理和/或训练逻辑615的细节。

[0162]

推理和/或训练逻辑615用于执行与一个或更多个实施例相关联的推理和/或训练操作。在至少一个实施例中,此逻辑可与这些图的组件一起使用,以选择在呈现一个或更多个视频片段期间与一个或更多个观看者的所确定的情绪相关联的那些片段。

[0163]

图13示出了根据本文所述的各个实施例的示例性集成电路和相关联的图形处理器,其可以使用一个或更多个ip核心来制造。除了图示之外,在至少一个实施例中可以包括其他逻辑和电路,包括附加的图形处理器/核心、外围接口控制器或通用处理器核心。

[0164]

图13是示出根据至少一个实施例的可使用一个或更多个ip核心制造的芯片集成电路1300上的示例性系统的框图。在至少一个实施例中,集成电路1300包括一个或更多个

应用程序处理器1305(例如,cpu)、至少一个图形处理器1310,并且可以另外包括图像处理器1315和/或视频处理器1320,其中任意一个可能是模块化ip核心。在至少一个实施例中,集成电路1300包括外围或总线逻辑,其包括usb控制器1325、uart控制器1330、spi/sdio控制器1335和i22s/i22c控制器1340。在至少一个实施例中,集成电路1300可以包括显示设备1345耦合到高清多媒体接口(hdmi)控制器1350和移动工业处理器接口(mipi)显示接口1355中的一个或更多个。在至少一个实施例中,存储可以由闪存子系统1360提供,包括闪存和闪存控制器。在至少一个实施例中,可以经由存储器控制器1365提供存储器接口以用于访问sdram或sram存储器设备。在至少一个实施例中,一些集成电路还包括嵌入式安全引擎1370。

[0165]

推理和/或训练逻辑615用于执行与一个或更多个实施例相关联的推理和/或训练操作。本文结合图6a和/或图6b提供关于推理和/或训练逻辑615的细节。在至少一个实施例中,推理和/或训练逻辑615可以在集成电路1300中用于至少部分地基于使用神经网络训练操作、神经网络功能和/或架构或本文描述的神经网络用例计算的权重参数来推理或预测操作。

[0166]

推理和/或训练逻辑615用于执行与一个或更多个实施例相关联的推理和/或训练操作。在至少一个实施例中,此逻辑可与这些图的组件一起使用,以选择在呈现一个或更多个视频片段期间与一个或更多个观看者的所确定的情绪相关联的那些片段。

[0167]

图14a

‑

14b示出了根据本文描述的各个实施例的可使用一个或更多个ip核心制造的示例性集成电路和相关联的图形处理器。除了所示出的内容之外,在至少一个实施例中可以包括其他逻辑和电路,包括附加的图形处理器/核心、外围接口控制器或通用处理器核心。

[0168]

图14a

‑

14b是示出了根据本文描述的实施例的在soc内使用的示例性图形处理器的框图。图14a示出了根据至少一个实施例的可使用一个或更多个ip核心制造的片上系统集成电路的示例性图形处理器1410。图14b示出了根据至少一个实施例的可以使用一个或更多个ip核心制造的片上系统集成电路的附加示例性图形处理器1440。在至少一个实施例中,图14a的图形处理器1410是低功率图形处理器核心。在至少一个实施例中,图14b的图形处理器1440是更高性能的图形处理器核心。在至少一个实施例中,图形处理器1410、1440中的每个图形处理器可以是图13的图形处理器1310的变体。

[0169]

在至少一个实施例中,图形处理器1410包括顶点处理器1405和一个或更多个片段处理器1415a

‑

1415n(例如,1415a、1415b、1415c、1415d至1415n

‑

1和1415n)。在至少一个实施例中,图形处理器1410可经由单独逻辑执行不同的着色器程序,使得顶点处理器1405被优化为执行用于顶点着色器程序的操作,而一个或更多个片段处理器1415a

‑

1415n执行用于片段或像素着色器程序的片段(例如,像素)着色操作。在至少一个实施例中,顶点处理器1405执行3d图形管线的顶点处理阶段且产生图元和顶点数据。在至少一个实施例中,一个或更多个片段处理器1415a

‑

1415n使用由顶点处理器1405生成的图元和顶点数据来产生显示在显示设备上的帧缓冲区。在至少一个实施例中,片段处理器1415a

‑

1415n被优化为执行如opengl api中提供的片段着色器程序,其可用于执行与如直接3d api中提供的像素着色器程序类似的操作。

[0170]

在至少一个实施例中,图形处理器1410另外包括一个或更多个存储器管理单元

1517a

‑

1517n)。

[0175]

在至少一个实施例中,fpu 1514a

‑

1514n可以执行单精度(32位)和半精度(16位)浮点运算,而dpfpu 1515a

‑

1515n则执行双精度(64位)浮点运算点操作。在至少一个实施例中,alu 1516a

‑

1516n可以以8位、16位和32位精度执行可变精度整数运算,并且可以配置为混合精度运算。在至少一个实施例中,mpu 1517a

‑

1517n还可被配置用于混合精度矩阵运算,包括半精度浮点运算和8位整数运算。在至少一个实施例中,mpu 1517

‑

1517n可以执行各种矩阵运算以加速机器学习应用程序框架,包括使得能够支持加速的通用矩阵到矩阵乘法(gemm)。在至少一个实施例中,afu 1512a

‑

1512n可以执行浮点数或整数单元不支持的附加逻辑运算,包括三角运算(例如,正弦,余弦等)。

[0176]

推理和/或训练逻辑615用于执行与一个或更多个实施例相关联的推理和/或训练操作。下面结合图6a和/或图6b提供关于推理和/或训练逻辑615的细节。在至少一个实施例中,推理和/或训练逻辑615可以在图形核心1500中用于至少部分地基于使用在此描述的神经网络训练操作、神经网络功能和/或架构或神经网络使用情况计算的权重参数来推理或预测操作。

[0177]

推理和/或训练逻辑615用于执行与一个或更多个实施例相关联的推理和/或训练操作。在至少一个实施例中,此逻辑可与这些图的组件一起使用,以选择在呈现一个或更多个视频片段期间与一个或更多个观看者的所确定的情绪相关联的那些片段。

[0178]

图15b示出了在至少一个实施例中的通用处理单元(gpgpu)1530,其可以被配置为使得高度并行的计算操作能够由一组图形处理单元来执行。在至少一个实施例中,gpgpu 1530可以直接链接到gpgpu 1530的其他实例,以创建多gpu集群以提高用于深度神经网络的训练速度。在至少一个实施例中,gpgpu 1530包括主机接口1532,以实现与主机处理器的连接。在至少一个实施例中,主机接口1532是pci express接口。在至少一个实施例中,主机接口1532可以是厂商专用的通信接口或通信结构。在至少一个实施例中,gpgpu 1530接收主机处理器的命令,并使用全局调度器1534,以将与那些命令相关联的执行线程分配给一组计算集群1536a

‑

1536h。在至少一个实施例中,计算集群1536a

‑

1536h共享高速缓存存储器1538。在至少一个实施例中,高速缓存存储器1538可以用作计算集群1536a

‑

1536h内的高速缓存存储器的更高级别的高速缓存。

[0179]

在至少一个实施例中,gpgpu 1530包括存储器1544a

‑

1544b,所述存储器1544a

‑

1544b经由一组存储器控制器1542a

‑

1542b与计算集群1536a

‑

1536h耦合。在至少一个实施例中,存储器1544a

‑

1544b可以包括各种类型的存储器设备,包括动态随机存取存储器(dram)或图形随机存取存储器,例如同步图形随机存取存储器(sgram),其包括图形双倍数据速率(gddr)存储器。

[0180]

在至少一个实施例中,计算集群1536a

‑

1536h每个都包括一组图形核心,例如图15a的图形核心1500,所述图形核心可以包括多种类型的整数和浮点逻辑单元,所述逻辑单元可以在计算机各种精度范围上执行计算操作,包括适用于机器学习计算的精度。例如,在至少一个实施例中,每个计算集群1536a

‑

1536h中的浮点单元的至少一个子集可以被配置为执行16位或32位浮点运算,而浮点单元的不同子集可以配置为执行64位浮点运算。

[0181]

在至少一个实施例中,gpgpu 1530的多个实例可以被配置为用作计算集群。在至少一个实施例中,计算集群1536a

‑

1536h用于同步和数据交换的通信在实施例之间变化。在

至少一个实施例中,gpgpu 1530的多个实例通过主机接口1532进行通信。在至少一个实施例中,gpgpu 1530包括i/o集线器1539,所述集线器将gpgpu 1530与gpu链路1540耦合,使得能够直接连接到gpgpu 1530的其他实例。在至少一个实施例中,gpu链路1540耦合到专用gpu到gpu桥,所述桥使得gpgp 1530的多个实例之间能够通信和同步。在至少一个实施例中,gpu链路1540与高速互连耦合,以向其他gpgpu或并行处理器发送和接收数据。在至少一个实施例中,gpgpu 1530的多个实例位于单独的数据处理系统中,并通过可通过主机接口1532访问的网络设备进行通信。在至少一个实施例中,gpu链路1540可被配置为使得能够连接到主机除主机接口1532之外或作为其替代的处理器。

[0182]

在至少一个实施例中,gpgpu 1530可以被配置为训练神经网络。在至少一个实施例中,可以在推理平台内使用gpgpu 1530。在至少一个实施例中,在其中使用gpgpu 1530进行推理的情况下,相对于使用gpgpu 1530训练神经网络时,gpgpu 1530可以包括更少的计算集群1536a

‑

1536h。在至少一个实施例中,与存储器1544a

‑

1544b相关联的存储器技术可以在推理和训练配置之间有所不同,其中更高带宽的存储器技术专用于训练配置。在至少一个实施例中,gpgpu 1530的推理配置可以支持推理特定指令。例如,在至少一个实施例中,推理配置可以提供对一个或更多个8位整数点积指令的支持,该指令可以在部署的神经网络的推理操作期间使用。

[0183]

推理和/或训练逻辑615用于执行与一个或更多个实施例相关联的推理和/或训练操作。下面结合图6a和/或图6b提供关于推理和/或训练逻辑615的细节。在至少一个实施例中,推理和/或训练逻辑615可以在gpgpu 1530中用于至少部分地基于使用在此描述的神经网络训练操作、神经网络功能和/或架构或神经网络使用情况计算的权重参数来推理或预测操作。

[0184]

推理和/或训练逻辑615用于执行与一个或更多个实施例相关联的推理和/或训练操作。在至少一个实施例中,此逻辑可与这些图的组件一起使用,以选择在呈现一个或更多个视频片段期间与一个或更多个观看者的所确定的情绪相关联的那些片段。

[0185]

图16示出了根据至少一个实施例的计算机系统1600的框图。在至少一个实施例中,计算机系统1600包括具有一个或更多个处理器1602的处理子系统1601和系统存储器1604,所述系统存储器1604经由可包括存储器集线器1605的互连路径通信。在至少一个实施例中,存储器集线器1605可以是芯片组部件内的单独部件,或者可以集成在一个或更多个处理器1602内。在至少一个实施例中,存储器集线器1605通过通信链路1606与i/o子系统1611耦合。在一个实施例中,i/o子系统1611包括i/o集线器1607,所述i/o集线器可以使计算机系统1600能够接收来自一个或更多个输入设备1608的输入。在至少一个实施例中,i/o集线器1607可以使显示控制器向一个或更多个显示设备1610a提供输出,所述显示控制器可以包括在一个或更多个处理器1602中。在至少一个实施例中,与i/o集线器1607耦合的一个或更多个显示设备1610a可以包括本地,内部或嵌入式显示设备。

[0186]

在至少一个实施例中,处理子系统1601包括经由总线或其他通信链路1613耦合到存储器集线器1605的一个或更多个并行处理器1612中。在至少一个实施例中,通信链路1613可以使用任何一种许多基于标准的通信链路技术或协议,例如但不限于pci express,或者可以是特定于供应商的通信接口或通信结构。在至少一个实施例中,一个或更多个并行处理器1612形成计算集中的并行或矢量处理系统,所述系统可以包括大量处理核心和/

或处理集群,例如多集成核心(mic)处理器。在至少一个实施例中,一个或更多个并行处理器1612形成图形处理子系统,所述图形处理子系统可以将像素输出到经由i/o集线器1607耦合的一个或更多个显示设备1610a之一。在至少一个实施例中,一个或更多个并行处理器1612还可以包括显示控制器和显示接口(未示出),以使得能够直接连接到一个或更多个显示设备1610b。

[0187]

在至少一个实施例中,系统存储单元1614可以连接到i/o集线器1607,以提供用于计算机系统1600的存储机制。在至少一个实施例中,i/o交换机1616可以用于提供一个接口机制,以实现i/o集线器1607与其他组件之间的连接,例如可以集成到平台中的网络适配器1618和/或无线网络适配器1619,以及可以通过一个或更多个附加设备1620添加的各种其他设备。在至少一个实施例中,网络适配器1618可以是以太网适配器或另一有线网络适配器。在至少一个实施例中,无线网络适配器1619可以包括wi

‑

fi、蓝牙、近场通信(nfc)中的一个或更多个,或包括一个或更多个无线电设备的其他网络设备。

[0188]

在至少一个实施例中,计算机系统1600可以包括未明确示出的其他组件,所述其他组件包括usb或其他端口连接、光学存储驱动器、视频捕获设备等,所述其他组件也可以连接到i/o集线器1607。在至少一个实施例中,可以使用任何合适的协议(例如基于pci(外围组件互连)的协议(例如pci

‑

express)或其他总线或点对点通信接口和/或协议)来实现互连图16中各个组件的通信路径,例如nv

‑

link高速互连或互连协议。

[0189]

在至少一个实施例中,一个或更多个并行处理器1612包括为图形和视频处理而优化的电路,所述电路包括例如视频输出电路,并构成图形处理单元(gpu)。在至少一个实施例中,一个或更多个并行处理器1612包括为通用处理而优化的电路。在至少一个实施例中,计算机系统1600的组件可以与单个集成电路上的一个或更多个其他系统元件集成。例如,在至少一个实施例中,并行处理器1612、存储器集线器1605、处理器1602和i/o集线器1607,可以被集成到片上系统(soc)集成电路中。在至少一个实施例中,计算机系统1600的组件可以被集成到单个封装中,以形成系统级封装(sip)配置。在至少一个实施例中,计算机系统1600的组件的至少一部分可以被集成到多芯片模块(mcm)中,所述多芯片模块可以与其他多芯片模块互连到模块化计算机系统中。

[0190]

推理和/或训练逻辑615用于执行与一个或更多个实施例相关联的推理和/或训练操作。下面结合图6a和/或图6b提供关于推理和/或训练逻辑615的细节。在至少一个实施例中,推理和/或训练逻辑615可以在系统1600中用于至少部分地基于使用在此描述的神经网络训练操作、神经网络功能和/或架构或神经网络使用情况计算的权重参数来推理或预测操作。

[0191]

推理和/或训练逻辑615用于执行与一个或更多个实施例相关联的推理和/或训练操作。在至少一个实施例中,此逻辑可与这些图的组件一起使用,以选择在呈现一个或更多个视频片段期间与一个或更多个观看者的所确定的情绪相关联的那些片段。

[0192]

处理器

[0193]

图17a示出了根据至少一个实施例的并行处理器1700。在至少一个实施例中,并行处理器1700的各种组件可以使用一个或更多个集成电路设备来实现,例如可编程处理器、专用集成电路(asic)或现场可编程门阵列(fpga)。在至少一个实施例中,所示的并行处理器1700是根据示例性实施例的图16所示的一个或更多个并行处理器1612的变体。

[0194]

在至少一个实施例中,并行处理器1700包括并行处理单元1702。在至少一个实施例中,并行处理单元1702包括i/o单元1704,其使得能够与其他设备进行通信,包括并行处理单元1702的其他实例。在至少一个实施例中,i/o单元1704可以直接连接到其他设备。在至少一个实施例中,i/o单元1704通过使用集线器或交换机接口(例如,存储器集线器1605)与其他设备连接。在至少一个实施例中,存储器集线器1605与i/o单元1704之间的连接形成通信链路1613。在至少一个实施例中,i/o单元1704与主机接口1706和存储器交叉开关1716连接,其中主机接口1706接收用于执行处理操作的命令,而存储器交叉开关1716接收用于执行存储器操作的命令。

[0195]

在至少一个实施例中,当主机接口1706经由i/o单元1704接收命令缓冲区时,主机接口1706可以引导工作操作以执行那些命令到前端1708。在至少一个实施例中,前端1708与调度器1710耦合,调度器1710配置成将命令或其他工作项分配给处理集群阵列1712。在至少一个实施例中,调度器1710确保在将任务分配给处理集群阵列1712之前,处理集群阵列1712被正确地配置并且处于有效状态。在至少一个实施例中,调度器1710通过在微控制器上执行的固件逻辑来实现。在至少一个实施例中,微控制器实现的调度器1710可配置成以粗粒度和细粒度执行复杂的调度和工作分配操作,从而实现对在处理阵列1712上执行的线程的快速抢占和上下文切换。在至少一个实施例中,主机软件可以证明用于通过多个图形处理门铃(doorbell)之一在处理阵列1712上进行调度的工作负载。在至少一个实施例中,工作负载然后可以由包括调度器1710的微控制器内的调度器1710逻辑在处理阵列1712上自动分配。

[0196]

在至少一个实施例中,处理集群阵列1712可以包括多达“n”个处理集群(例如,集群1714a、集群1714b到集群1714n)。在至少一个实施例中,处理集群阵列1712的每个集群1714a

‑

1714n可以执行大量并发线程。在至少一个实施例中,调度器1710可以使用各种调度和/或工作分配算法将工作分配给处理集群阵列1712的集群1714a

‑

1714n,其可以根据每种程序或计算类型产生的工作负载而变化。在至少一个实施例中,调度可以由调度器1710动态地处理,或者可以在配置为由处理集群阵列1712执行的程序逻辑的编译期间部分地由编译器逻辑来辅助。在至少一个实施例中,可将处理集群阵列1712的不同的集群1714a

‑

1714n分配用于处理不同类型的程序或用于执行不同类型的计算。

[0197]

在至少一个实施例中,处理集群阵列1712可以配置成执行各种类型的并行处理操作。在至少一个实施例中,处理集群阵列1712配置成执行通用并行计算操作。例如,在至少一个实施例中,处理集群阵列1712可以包括执行处理任务的逻辑,该处理任务包括对视频和/或音频数据的过滤,执行建模操作,包括物理操作以及执行数据转换。

[0198]

在至少一个实施例中,处理集群阵列1712配置成执行并行图形处理操作。在至少一个实施例中,处理集群阵列1712可以包括附加逻辑以支持这种图形处理操作的执行,包括但不限于执行纹理操作的纹理采样逻辑,以及镶嵌逻辑和其他顶点处理逻辑。在至少一个实施例中,处理集群阵列1712可以配置成执行与图形处理有关的着色器程序,例如但不限于顶点着色器、曲面细分着色器、几何着色器和像素着色器。在至少一个实施例中,并行处理单元1702可以经由i/o单元1704从系统存储器传送数据以进行处理。在至少一个实施例中,在处理期间,可以在处理期间将传送的数据存储到片上存储器(例如,并行处理器存储器1722),然后将其写回到系统存储器。

[0199]

在至少一个实施例中,当并行处理单元1702用于执行图形处理时,调度器1710可以配置成将处理工作负载划分为近似相等大小的任务,以更好地将图形处理操作分配给处理集群阵列1712的多个集群1714a

‑

1714n。在至少一个实施例中,处理集群阵列1712的部分可以配置成执行不同类型的处理。例如,在至少一个实施例中,第一部分可以配置成执行顶点着色和拓扑生成,第二部分可以配置成执行镶嵌和几何着色,并且第三部分可以配置成执行像素着色或其他屏幕空间操作,以生成用于显示的渲染图像。在至少一个实施例中,可以将由集群1714a

‑

1714n中的一个或更多个产生的中间数据存储在缓冲区中,以允许在集群1714a

‑

1714n之间传输中间数据以进行进一步处理。

[0200]

在至少一个实施例中,处理集群阵列1712可以经由调度器1710接收要执行的处理任务,该调度器1710从前端1708接收定义处理任务的命令。在至少一个实施例中,处理任务可以包括要被处理的数据的索引,例如,表面(补丁)数据、原始数据、顶点数据和/或像素数据,以及状态参数和定义如何处理数据的命令(例如,要执行什么程序)。在至少一个实施例中,调度器1710可以配置成获取与任务相对应的索引,或者可以从前端1708接收索引。在至少一个实施例中,前端1708可以配置成确保在启动由传入命令缓冲区(例如,批缓冲区(batch

‑

buffer)、推送缓冲区等)指定的工作负载之前,处理集群阵列1712配置成有效状态。

[0201]

在至少一个实施例中,并行处理单元1702的一个或更多个实例中的每一个可以与并行处理器存储器1722耦合。在至少一个实施例中,可以经由存储器交叉开关1716访问并行处理器存储器1722,所述存储器交叉开关1716可以接收来自处理集群阵列1712以及i/o单元1704的存储器请求。在至少一个实施例中,存储器交叉开关1716可以经由存储器接口1718访问并行处理器存储器1722。在至少一个实施例中,存储器接口1718可以包括多个分区单元(例如,分区单元1720a、分区单元1720b到分区单元1720n),其可各自耦合至并行处理器存储器1722的一部分(例如,存储器单元)。在至少一个实施例中,多个分区单元1720a

‑

1720n为配置为等于存储器单元的数量,使得第一分区单元1720a具有对应的第一存储器单元1724a,第二分区单元1720b具有对应的存储器单元1724b,第n分区单元1720n具有对应的第n存储器单元1724n。在至少一个实施例中,分区单元1720a

‑

1720n的数量可以不等于存储器设备的数量。

[0202]

在至少一个实施例中,存储器单元1724a

‑

1724n可以包括各种类型的存储器设备,包括动态随机存取存储器(dram)或图形随机存取存储器,例如同步图形随机存取存储器(sgram),包括图形双倍数据速率(gddr)存储器。在至少一个实施例中,存储器单元1724a

‑

1724n还可包括3d堆叠存储器,包括但不限于高带宽存储器(hbm)。在至少一个实施例中,可以跨存储器单元1724a

‑

1724n来存储诸如帧缓冲区或纹理映射的渲染目标,从而允许分区单元1720a

‑

1720n并行地写入每个渲染目标的部分,以有效地使用并行处理器存储器1722的可用带宽。在至少一个实施例中,可以排除并行处理器存储器1722的本地实例,以有利于利用系统存储器与本地高速缓存存储器结合的统一存储器设计。

[0203]

在至少一个实施例中,处理集群阵列1712的集群1714a

‑

1714n中的任何一个都可以处理将被写入并行处理器存储器1722内的任何存储器单元1724a

‑

1724n中的数据。在至少一个实施例中,存储器交叉开关1716可以配置为将每个集群1714a

‑

1714n的输出传输到任何分区单元1720a

‑

1720n或另一个集群1714a

‑

1714n,集群1714a

‑

1714n可以对输出执行

其他处理操作。在至少一个实施例中,每个集群1714a

‑

1714n可以通过存储器交叉开关1716与存储器接口1718通信,以从各种外部存储设备读取或写入各种外部存储设备。在至少一个实施例中,存储器交叉开关1716具有到存储器接口1718的连接以与i/o单元1704通信,以及到并行处理器存储器1722的本地实例的连接,从而使不同处理集群1714a

‑

1714n内的处理单元与系统存储器或不是并行处理单元1702本地的其他存储器进行通信。在至少一个实施例中,存储器交叉开关1716可以使用虚拟通道来分离集群1714a

‑

1714n和分区单元1720a

‑

1720n之间的业务流。

[0204]

在至少一个实施例中,可以在单个插入卡上提供并行处理单元1702的多个实例,或者可以将多个插入卡互连。在至少一个实施例中,并行处理单元1702的不同实例可以配置成相互操作,即使不同实例具有不同数量的处理核心,不同数量的本地并行处理器存储器和/或其他配置差异。例如,在至少一个实施例中,并行处理单元1702的一些实例可以包括相对于其他实例而言更高精度的浮点单元。在至少一个实施例中,结合并行处理单元1702或并行处理器1700的一个或更多个实例的系统可以以各种配置和形式因素来实现,包括但不限于台式机、膝上型计算机或手持式个人计算机、服务器、工作站、游戏机和/或嵌入式系统。

[0205]

图17b是根据至少一个实施例的分区单元1720的框图。在至少一个实施例中,分区单元1720是图17a的分区单元1720a

‑

1720n之一的实例。在至少一个实施例中,分区单元1720包括l2高速缓存1721、帧缓冲区接口1725和光栅操作单元(“rop”)1726。l2高速缓存1721是读/写高速缓存,其配置成执行从存储器交叉开关1716和rop 1726接收的加载和存储操作。在至少一个实施例中,l2高速缓存1721将读取未命中和紧急回写请求输出到帧缓冲区接口1725以进行处理。在至少一个实施例中,还可以经由帧缓冲区接口1725将更新发送到帧缓冲区以进行处理。在至少一个实施例中,帧缓冲区接口1725与并行处理器存储器中的存储器单元(诸如图17a的存储器单元1724a

‑

1724n(例如,在并行处理器存储器1722内))之一相互作用。

[0206]

在至少一个实施例中,rop 1726是一种处理单元,其执行光栅操作,诸如模版、z测试、混合等。在至少一个实施例中,rop 1726然后输出存储在图形存储器中的处理后的图形数据。在至少一个实施例中,rop 1726包括压缩逻辑以压缩被写入存储器的深度或颜色数据并解压缩从存储器读取的深度或颜色数据。在至少一个实施例中,压缩逻辑可以是利用多种压缩算法中的一种或更多种的无损压缩逻辑。rop 1726执行的压缩逻辑可以基于要压缩的数据的统计特性而变化。例如,在至少一个实施例中,基于每图块基础上的深度和颜色数据执行增量颜色压缩。

[0207]

在至少一个实施例中,rop 1726包括在每个处理集群内(例如,图17a的集群1714a

‑

1714n),而不是在分区单元1720内。在至少一个实施例中,通过存储器交叉开关1716而不是像素片段数据传输对像素数据的读取和写入请求。在至少一个实施例中,经处理的图形数据可以在显示设备上(诸如图16的一个或更多个显示设备1610之一)显示,由处理器1602路由以供进一步处理,或者由图17a的并行处理器1700内的处理实体之一路由以供进一步处理。

[0208]

图17c是根据至少一个实施例的并行处理单元内的处理集群1714的框图。在至少一个实施例中,处理集群是图17a的处理集群1714a

‑

1714n之一的实例。在至少一个实施例

中,处理集群1714中的一个或更多个可以配置成并行执行许多线程,其中“线程”是指在特定的一组输入数据上执行的特定程序的实例。在至少一个实施例中,单指令多数据(simd)指令发布技术用于支持大量线程的并行执行而无需提供多个独立的指令单元。

[0209]

在至少一个实施例中,使用单指令多线程(simt)技术来支持并行执行大量一般同步的线程,这使用了公共指令单元,该公共指令单元配置成向每个处理集群内的一组处理引擎发出指令。

[0210]

在至少一个实施例中,可以通过将处理任务分配给simt并行处理器的管线管理器1732来控制处理集群1714的操作。在至少一个实施例中,管线管理器1732从图17a的调度器1710接收指令,通过图形多处理器1734和/或纹理单元1736管理这些指令的执行。在至少一个实施例中,图形多处理器1734是simt并行处理器的示例性实例。然而,在至少一个实施例中,处理集群1714内可以包括不同架构的各种类型的simt并行处理器。在至少一个实施例中,在处理集群1714内可以包括图形多处理器1734的一个或更多个实例。在至少一个实施例中,图形多处理器1734可以处理数据,并且数据交叉开关1740可以用于将处理后的数据分发到多个可能的目的(包括其他着色器单元)地之一。在至少一个实施例中,管线管理器1732可以通过指定要经由数据交叉开关1740分配的处理后的数据的目的地来促进处理后的数据的分配。

[0211]

在至少一个实施例中,处理集群1714内的每个图形多处理器1734可以包括相同的一组功能执行逻辑(例如,算术逻辑单元、加载存储单元等)。在至少一个实施例中,可以以管线方式配置功能执行逻辑,其中可以在先前的指令完成之前发出新的指令。在至少一个实施例中,功能执行逻辑支持多种操作,包括整数和浮点算术、比较操作、布尔运算、移位和各种代数函数的计算。在至少一个实施例中,可以利用相同的功能单元硬件来执行不同的操作,并且可以存在功能单元的任何组合。

[0212]

在至少一个实施例中,传送到处理集群1714的指令构成线程。在至少一个实施例中,跨一组并行处理引擎执行的一组线程是线程组。在至少一个实施例中,线程组在不同的输入数据上执行程序。在至少一个实施例中,线程组内的每个线程可被分配给图形多处理器1734内的不同处理引擎。在至少一个实施例中,线程组可包括比图形多处理器1734内的多个处理引擎更少的线程。在至少一个实施例中,当线程组包括的线程数少于处理引擎的数量时,一个或更多个处理引擎在正在处理该线程组的循环期间可能是空闲的。在至少一个实施例中,线程组还可以包括比图形多处理器1734内的多个处理引擎更多的线程。在至少一个实施例中,当线程组包括比图形多处理器1734内的处理引擎更多的线程时,可以在连续的时钟周期内执行处理。在至少一个实施例中,可以在图形多处理器1734上同时执行多个线程组。

[0213]

在至少一个实施例中,图形多处理器1734包括内部高速缓存存储器,以执行加载和存储操作。在至少一个实施例中,图形多处理器1734可以放弃内部高速缓存并使用处理集群1714内的高速缓存存储器(例如,l1高速缓存1748)。在至少一个实施例中,每个图形多处理器1734还可以访问分区单元(例如,图17a的分区单元1720a

‑

1720n)内的l2高速缓存,这些分区单元在所有处理集群1714之间共享并且可以用于在线程之间传输数据。在至少一个实施例中,图形多处理器1734还可以访问片外全局存储器,其可以包括本地并行处理器存储器和/或系统存储器中的一个或更多个。在至少一个实施例中,并行处理单元1702外部

的任何存储器都可以用作全局存储器。在至少一个实施例中,处理集群1714包括图形多处理器1734的多个实例,它们可以共享可以存储在l1高速缓存1748中的公共指令和数据。

[0214]

在至少一个实施例中,每个处理集群1714可以包括配置成将虚拟地址映射为物理地址的存储器管理单元(“mmu”)1745。在至少一个实施例中,mmu 1745的一个或更多个实例可以驻留在图17a的存储器接口1718内。在至少一个实施例中,mmu 1745包括一组页表条目(pte),其用于将虚拟地址映射到图块的物理地址以及可选地映射到高速缓存行索引。在至少一个实施例中,mmu 1745可以包括地址转换后备缓冲区(tlb)或可以驻留在图形多处理器1734或l1高速缓存或处理集群1714内的高速缓存。在至少一个实施例中,处理物理地址以分配表面数据访问局部性,以便在分区单元之间进行有效的请求交织。在至少一个实施例中,高速缓存行索引可以用于确定对高速缓存线的请求是命中还是未命中。

[0215]

在至少一个实施例中,可以配置处理集群1714,使得每个图形多处理器1734耦合到纹理单元1736,以执行纹理映射操作,所述操作确定纹理样本位置、读取纹理数据以及过滤纹理数据。在至少一个实施例中,根据需要从内部纹理l1高速缓存(未示出)或从图形多处理器1734内的l1高速缓存中读取纹理数据,并从l2高速缓存、本地并行处理器存储器或系统存储器中获取纹理数据。在至少一个实施例中,每个图形多处理器1734将处理后的任务输出到数据交叉开关1740,以将处理后的任务提供给另一处理集群1714以进行进一步处理或将处理后的任务存储在l2高速缓存、本地并行处理器存储器、或经由存储器交叉开关1716的系统存储器中。在至少一个实施例中,prerop 1742(光栅前操作单元)配置成从图形多处理器1734接收数据,将数据引导至rop单元,该rop单元可以与本文所述的分区单元(例如,图17a的分区单元1720a

‑

1720n)一起定位。在至少一个实施例中,prerop 1742单元可以执行用于颜色混合的优化、组织像素颜色数据以及执行地址转换。

[0216]

推理和/或训练逻辑615用于执行与一个或更多个实施例相关联的推理和/或训练操作。下面结合图6a和/或图6b提供关于推理和/或训练逻辑615的细节。在至少一个实施例中,推理和/或训练逻辑615可在图形处理集群1714中使用,用于至少部分地基于使用本文描述的神经网络训练操作、神经网络功能和/或架构或神经网络使用情况计算的权重参数来推理或预测操作。

[0217]

推理和/或训练逻辑615用于执行与一个或更多个实施例相关联的推理和/或训练操作。在至少一个实施例中,此逻辑可与这些图的组件一起使用,以选择在呈现一个或更多个视频片段期间与一个或更多个观看者的所确定的情绪相关联的那些片段。

[0218]

图17d示出了根据至少一个实施例的图形多处理器1734。在至少一个实施例中,图形多处理器1734与处理集群1714的管线管理器1732耦合。在至少一个实施例中,图形多处理器1734具有执行管线,该执行管线包括但不限于指令高速缓存1752、指令单元1754、地址映射单元1756、寄存器文件1758、一个或更多个通用图形处理单元(gpgpu)核心1762和一个或更多个加载/存储单元1766。gpgpu核心1762和加载/存储单元1766通过存储器和高速缓存互连1768与高速缓存存储器1772和共享存储器1770耦合。

[0219]

在至少一个实施例中,指令高速缓存1752从管线管理器1732接收要执行的指令流。在至少一个实施例中,将指令高速缓存在指令高速缓存1752中并将其分派以供指令单元1754执行。在一个实施例中,指令单元1754可以分派指令作为线程组(例如,线程束),将每个线程组分配给gpgpu核心1762内的不同执行单元。在至少一个实施例中,指令可以通过

指定统一地址空间内的地址来访问任何本地、共享或全局地址空间。在至少一个实施例中,地址映射单元1756可以用于将统一地址空间中的地址转换成可以由加载/存储单元1766访问的不同的存储器地址。

[0220]

在至少一个实施例中,寄存器文件1758为图形多处理器1734的功能单元提供了一组寄存器。在至少一个实施例中,寄存器文件1758为连接到图形多处理器1734的功能单元(例如,gpgpu核心1762、加载/存储单元1766)的数据路径的操作数提供了临时存储。在至少一个实施例中,在每个功能单元之间划分寄存器文件1758,使得为每个功能单元分配寄存器文件1758的专用部分。在至少一个实施例中,寄存器文件1758在图形多处理器1734正在执行的不同线程束之间划分。

[0221]

在至少一个实施例中,gpgpu核心1762可以各自包括用于执行图形多处理器1734的指令的浮点单元(fpu)和/或整数算术逻辑单元(alu)。gpgpu核心1762在架构上可以相似或架构可能有所不同。在至少一个实施例中,gpgpu核心1762的第一部分包括单精度fpu和整数alu,而gpgpu核心的第二部分包括双精度fpu。在至少一个实施例中,fpu可以实现用于浮点算法的ieee 754

‑

2008标准或启用可变精度浮点算法。在至少一个实施例中,图形多处理器1734可以另外包括一个或更多个固定功能或特殊功能单元,以执行特定功能,诸如复制矩形或像素混合操作。在至少一个实施例中,gpgpu核心中的一个或更多个还可以包括固定或特殊功能逻辑。

[0222]

在至少一个实施例中,gpgpu核心1762包括能够对多组数据执行单个指令的simd逻辑。在一个实施例中,gpgpu核心1762可以物理地执行simd4、simd8和simd16指令,并且在逻辑上执行simd1、simd2和simd32指令。在至少一个实施例中,用于gpgpu核心的simd指令可以在编译时由着色器编译器生成,或者在执行针对单程序多数据(spmd) 或simt架构编写和编译的程序时自动生成。在至少一个实施例中,可以通过单个simd指令来执行为simt执行模型配置的程序的多个线程。例如,在至少一个实施例中,可以通过单个simd8逻辑单元并行执行执行相同或相似操作的八个simt线程。

[0223]

在至少一个实施例中,存储器和高速缓存互连1768是将图形多处理器1734的每个功能单元连接到寄存器文件1758和共享存储器1770的互连网络。在至少一个实施例中,存储器和高速缓存互连1768是交叉开关互连,其允许加载/存储单元1766在共享存储器1770和寄存器文件1758之间实现加载和存储操作。在至少一个实施例中,寄存器文件1758可以以与gpgpu核心1762相同的频率操作,从而在gpgpu核心1762和寄存器文件1758之间进行数据传输的延迟非常低。在至少一个实施例中,共享存储器1770可以用于启用在图形多处理器1734内的功能单元上执行的线程之间的通信。在至少一个实施例中,高速缓存存储器1772可以用作例如数据高速缓存,以高速缓存在功能单元和纹理单元1736之间通信的纹理数据。在至少一个实施例中,共享存储器1770也可以用作程序管理的高速缓存。在至少一个实施例中,除了存储在高速缓存存储器1772中的自动高速缓存的数据之外,在gpgpu核心1762上执行的线程还可以以编程方式将数据存储在共享存储器中。

[0224]

在至少一个实施例中,如本文所述的并行处理器或gpgpu通信地耦合到主机/处理器核心,以加速图形操作、机器学习操作、图案分析操作以及各种通用gpu(gpgpu)功能。在至少一个实施例中,gpu可以通过总线或其他互连(例如,诸如pcie或nvlink的高速互连)通信地耦合到主机处理器/核心。在至少一个实施例中,gpu可以与核心集成在同一封装或芯

片上,并通过内部处理器总线/互连(即,在封装或芯片的内部)通信地耦合到核心。在至少一个实施例中,不管gpu连接的方式如何,处理器核心可以以工作描述符中包含的命令/指令序列的形式向gpu分配工作。在至少一个实施例中,该gpu然后使用专用电路/逻辑来有效地处理这些命令/指令。

[0225]

推理和/或训练逻辑615用于执行与一个或更多个实施例相关联的推理和/或训练操作。下面结合图6a和/或图6b提供关于推理和/或训练逻辑615的细节。在至少一个实施例中,推理和/或训练逻辑615可以在图形多处理器1734中使用,用于至少部分地基于使用本文描述的神经网络训练操作、神经网络功能和/或架构或神经网络使用情况计算的权重参数来推理或预测操作。

[0226]

推理和/或训练逻辑615用于执行与一个或更多个实施例相关联的推理和/或训练操作。在至少一个实施例中,此逻辑可与这些图的组件一起使用,以选择在呈现一个或更多个视频片段期间与一个或更多个观看者的所确定的情绪相关联的那些片段。

[0227]

图18示出了根据至少一个实施例的多gpu计算系统1800。在至少一个实施例中,多gpu计算系统1800可包括处理器1802,其经由主机接口交换机1804耦合到多个通用图形处理单元(gpgpu)1806a

‑

d。在至少一个实施例中,主机接口交换机1804是将处理器1802耦合到pci快速总线的pci快速交换机设备,处理器1802可通过pci快速总线与gpgpu 1806a

‑

d通信。gpgpu1806a

‑

d可经由高速点对点gpu到gpu链路1816的集合互连。在至少一个实施例中,gpu到gpu链路1816经由专用gpu链路连接到gpgpu 1806a

‑

d中的每一者。在至少一个实施例中,p2pgpu链路1816实现gpgpu 1806a

‑

d中的每一个之间的直接通信,而不需要在处理器1802连接到的主机接口总线1804上的通信。在至少一个实施例中,通过指向p2p gpu链路1816的gpu到gpu流量,主机接口总线1804保持可用于系统存储器访问或例如经由一个或更多个网络设备与多gpu计算系统1800的其他实例通信。虽然在至少一个实施例中,gpgpu 1806a

‑

d经由主机接口交换机1804连接到处理器1802,但是在至少一个实施例中,处理器1802包括对p2p gpu链路1816的直接支持,并且可以直接连接到gpgpu1806a

‑

d。

[0228]

推理和/或训练逻辑615用于执行与一个或更多个实施例相关联的推理和/或训练操作。下面结合图6a和/或图6b提供关于推理和/或训练逻辑615的细节。在至少一个实施例中,推理和/或训练逻辑615可以在多gpu计算系统1800中使用,用于至少部分地基于使用本文描述的神经网络训练操作、神经网络功能和/或架构或神经网络使用情况计算的权重参数来推理或预测操作。

[0229]

推理和/或训练逻辑615用于执行与一个或更多个实施例相关联的推理和/或训练操作。在至少一个实施例中,此逻辑可与这些图的组件一起使用,以选择在呈现一个或更多个视频片段期间与一个或更多个观看者的所确定的情绪相关联的那些片段。

[0230]

图19是根据至少一个实施例的图形处理器1900的框图。在至少一个实施例中,图形处理器1900包括环形互连1902、管线前端1904、媒体引擎1937和图形核心1980a

‑

1980n。在至少一个实施例中,环形互连1902将图形处理器1900耦合到其他处理单元,所述处理单元包括其他图形处理器或一个或更多个通用处理器核心。在至少一个实施例中,图形处理器1900是集成在多核心处理系统内的许多处理器之一。

[0231]

在至少一个实施例中,图形处理器1900经由环形互连1902接收多批命令。在至少一个实施例中,输入的命令由管线前端1904中的命令流转化器(streamer)1903解释。在至

少一个实施例中,图形处理器1900包括可扩展执行逻辑,用于经由图形核心1980a

‑

1980n执行3d几何处理和媒体处理。在至少一个实施例中,对于3d几何处理命令,命令流转化器1903将命令提供给几何管线1936。在至少一个实施例中,对于至少一些媒体处理命令,命令流转化器1903将命令提供给视频前端1934,该视频前端与媒体引擎1937耦合。在至少一个实施例中,媒体引擎1937包括用于视频和图像后处理的视频质量引擎(vqe)1930,以及用于提供硬件加速的媒体数据编码和解码的多格式编码/解码(mfx)1933引擎。在至少一个实施例中,几何管线1936和媒体引擎1937各自生成用于由至少一个图形核心1980a提供的线程执行资源的执行线程。

[0232]

在至少一个实施例中,图形处理器1900包括具有(featuring)模块核心1980a

‑

1980n(有时被称为核心切片)的可扩展线程执行资源,每个图形核心具有多个子核心1950a

‑

1950n,1960a

‑

1960n(有时称为核心子切片)。在至少一个实施例中,图形处理器1900可以具有任意数量的图形核心1980a到1980n。在至少一个实施例中,图形处理器1900包括具有至少第一子核心1950a和第二子核心1960a的图形核心1980a。在至少一个实施例中,图形处理器1900是具有单个子核心(例如1950a)的低功率处理器。在至少一个实施例中,图形处理器1900包括多个图形核心1980a

‑

1980n,每个图形核心包括一组第一子核心1950a

‑

1950n和一组第二子核心1960a

‑

1960n。在至少一个实施例中,第一子核心1950a

‑

1950n中的每个子核心至少包括第一组执行单元1952a

‑

1952n和媒体/纹理采样器1954a

‑

1954n。在至少一个实施例中,第二子核心1960a

‑

1960n中的每个子核心至少包括第二组执行单元1962a

‑

1962n和采样器1964a

‑

1964n。在至少一个实施例中,每个子核心1950a

‑

1950n,1960a

‑

1960n共享一组共享资源1970a

‑

1970n。在至少一个实施例中,共享资源包括共享高速缓存存储器和像素操作逻辑。

[0233]

推理和/或训练逻辑615用于执行与一个或更多个实施例相关联的推理和/或训练操作。下面结合图6a和/或图6b提供关于推理和/或训练逻辑615的细节。在至少一个实施例中,推理和/或训练逻辑615可以在图形处理器1900中使用,用于至少部分地基于使用本文描述的神经网络训练操作、神经网络功能和/或架构或神经网络使用情况计算的权重参数来推理或预测操作。

[0234]

推理和/或训练逻辑615用于执行与一个或更多个实施例相关联的推理和/或训练操作。在至少一个实施例中,此逻辑可与这些图的组件一起使用,以选择在呈现一个或更多个视频片段期间与一个或更多个观看者的所确定的情绪相关联的那些片段。

[0235]

图20是根据至少一个实施例的说明用于处理器2000的微架构的框图,该处理器2000可以包括用于执行指令的逻辑电路。在至少一个实施例中,处理器2000可以执行指令,包括x86指令、arm指令、用于专用集成电路(asic)的专用指令等。在至少一个实施例中,处理器2000可以包括用于存储封装数据的寄存器,例如作为加利福尼亚州圣克拉拉市英特尔公司采用mmx技术启用的微处理器中的64位宽mmx

tm

寄存器。在至少一个实施例中,整数和浮点数形式可用的mmx寄存器可以与封装的数据元素一起运行,所述封装的数据元素伴随单指令多数据(“simd”)和流式simd扩展(“sse”)指令。在至少一个实施例中,与sse2、sse3、sse4、avx或更高版本(一般称为“ssex”)技术有关的128位宽xmm寄存器可以保存此类封装数据操作数。在至少一个实施例中,处理器2000可以执行指令以加速机器学习或深度学习算法、训练或推理。

[0236]

在至少一个实施例中,处理器2000包括有序前端(“前端”)2001,以提取要执行的指令并准备稍后在处理器管线中使用的指令。在至少一个实施例中,前端2001可以包括几个单元。在至少一个实施例中,指令预取器2026从存储器中获取指令并将指令提供给指令解码器2028,指令解码器2028又对指令进行解码或解释。例如,在至少一个实施例中,指令解码器2028将接收到的指令解码为机器可执行的所谓的“微指令”或“微操作”(也称为“微操作”或“微指令”)的一个或更多个操作。在至少一个实施例中,指令解码器2028将指令解析为操作码以及相应的数据和控制字段,其可以由微架构用来使用以根据至少一个实施例来执行操作。在至少一个实施例中,跟踪高速缓存2030可以将解码的微指令组装成微指令队列2034中的程序排序的序列或追踪以供执行。在至少一个实施例中,当追踪高速缓存2030遇到复杂指令时,微码rom 2032提供完成操作所需的微指令。

[0237]

在至少一个实施例中,可以将一些指令转换成单个微操作,而另一些指令则需要几个微操作来完成全部操作。在至少一个实施例中,如果需要多于四个的微指令来完成一条指令,则指令解码器2028可以访问微码rom 2032以执行指令。在至少一个实施例中,可以将指令解码为少量的微指令以在指令解码器2028处进行处理。在至少一个实施例中,如果需要多个微指令完成操作,则可以将指令存储在微码rom 2032中。在至少一个实施例中,追踪高速缓存器2030参考入口点可编程逻辑阵列(“pla”)以确定正确的微指令指针,用于根据至少一个实施例从微码rom 2032读取微码序列以完成一个或更多个指令。在至少一个实施例中,在微码rom 2032完成对指令的微操作排序之后,机器的前端2001可以恢复从追踪高速缓存2030获取微操作。

[0238]

在至少一个实施例中,乱序执行引擎(“乱序引擎”)2003可以准备用于执行的指令。在至少一个实施例中,乱序执行逻辑具有多个缓冲区,以使指令流平滑并重新排序,以在指令沿管线下降并被调度执行时优化性能。在至少一个实施例中,乱序执行引擎2003包括但不限于分配器/寄存器重命名器2040、存储器微指令队列2042、整数/浮点微指令队列2044、存储器调度器2046、快速调度器2002、慢速/通用浮点调度器(“慢速/通用fp调度器”)2004和简单浮点调度器(“简单fp调度器”)2006。在至少一个实施例中,快速调度器2002、慢速/通用浮点调度器2004和简单浮点调度器2006也统称为“微指令调度器2002、2004、2006”。在至少一个实施例中,分配器/寄存器重命名器2040分配每个微指令按序列执行所需要的机器缓冲区和资源。在至少一个实施例中,分配器/寄存器重命名器2040将逻辑寄存器重命名为寄存器文件中的条目。在至少一个实施例中,分配器/寄存器重命名器2040还为两个微指令队列之一中的每个微指令分配条目,存储器微指令队列2042用于存储器操作和整数/浮点微指令队列2044用于非存储器操作,在存储器调度器2046和微指令调度器2002、2004、2006的前面。在至少一个实施例中,微指令调度器2002、2004、2006基于它们的从属输入寄存器操作数源的就绪性和需要完成的执行资源微指令的可用性来确定何时准备好执行微指令。在至少一个实施例中,至少一个实施例的快速调度器2002可以在主时钟周期的每个一半上调度,而慢速/通用浮点调度器2004和简单浮点调度器2006可以在每个主处理器时钟周期调度一次。在至少一个实施例中,微指令调度器2002、2004、2006对调度端口进行仲裁,以调度用于执行的微指令。

[0239]

在至少一个实施例中,执行块2011包括但不限于整数寄存器文件/支路网络2008、浮点寄存器文件/支路网络(“fp寄存器文件/支路网络”)2010、地址生成单元(“agu”)2012

和2014、快速算术逻辑单元(“快速alu”)2016和2018、慢速算术逻辑单元(“慢速alu”)2020、浮点alu(“fp”)2022和浮点移动单元(“fp移动”)2024。在至少一个实施例中,整数寄存器文件/支路网络2008和浮点寄存器文件/旁路网络2010在本文中也称为“寄存器文件2008、2010”。在至少一个实施例中,agu 2012和2014、快速alu 2016和2018、慢速alu 2020、浮点alu 2022和浮点移动单元2024在本文中也称为“执行单元2012、2014、2016、2018、2020、2022和2024”。在至少一个实施例中,执行块2011可以包括但不限于任意数量(包括零)和类型的寄存器文件、支路网络、地址生成单元和执行单元(以任何组合)。

[0240]

在至少一个实施例中,寄存器文件2008、2010可以布置在微指令调度器2002、2004、2006与执行单元2012、2014、2016、2018、2020、2022和2024之间。在至少一个实施例中,整数寄存器文件/支路网络2008执行整数运算。在至少一个实施例中,浮点寄存器文件/支路网络2010执行浮点操作。在至少一个实施例中,寄存器文件2008、2010中的每一个可以包括但不限于支路网络,该支路网络可以绕过或转发尚未写入寄存器文件中的刚刚完成的结果到新的从属对象。在至少一个实施例中,寄存器文件2008、2010可以彼此通信数据。在至少一个实施例中,整数寄存器文件/支路网络2008可以包括但不限于两个单独的寄存器文件、一个寄存器文件用于低阶32位数据,第二寄存器文件用于高阶32位数据。在至少一个实施例中,浮点寄存器文件/支路网络2010可以包括但不限于128位宽的条目,因为浮点指令通常具有宽度为64至128位的操作数。

[0241]

在至少一个实施例中,执行单元2012、2014、2016、2018、2020、2022、2024可以执行指令。在至少一个实施例中,寄存器文件2008、2010存储微指令需要执行的整数和浮点数据操作数值。在至少一个实施例中,处理器2000可以包括但不限于任何数量的执行单元2012、2014、2016、2018、2020、2022、2024及其组合。在至少一个实施例中,浮点alu 2022和浮点移动单元2024,可以执行浮点、mmx、simd、avx和sse或其他操作,包括专门的机器学习指令。在至少一个实施例中,浮点alu 2022可以包括但不限于64位乘64位浮点除法器,以执行除法、平方根和余数微操作。在至少一个实施例中,可以用浮点硬件来处理涉及浮点值的指令。在至少一个实施例中,可以将alu操作传递给快速alu 2016、2018。在至少一个实施例中,快速alu 2016、2018可以以半个时钟周期的有效延迟执行快速操作。在至少一个实施例中,大多数复杂的整数运算进入慢速alu 2020,因为慢速alu 2020可以包括但不限于用于长延迟类型操作的整数执行硬件,例如乘法器、移位、标志逻辑和分支处理。在至少一个实施例中,存储器加载/存储操作可以由agu 2012、2014执行。在至少一个实施例中,快速alu 2016、快速alu 2018和慢速alu 2020可以对64位数据操作数执行整数运算。在至少一个实施例中,可以实现快速alu 2016、快速alu 2018和慢速alu 2020以支持包括十六、三十二、128、256等的各种数据位大小。在至少一个实施例中,浮点alu 2022和浮点移动单元2024可以实现为支持具有各种宽度的位的一定范围的操作数。在至少一个实施例中,浮点alu 2022和浮点移动单元2024可以结合simd和多媒体指令对128位宽打包数据操作数进行操作。

[0242]

在至少一个实施例中,微指令调度器2002、2004、2006在父加载完成执行之前调度从属操作。在至少一个实施例中,由于可以在处理器2000中推测性地调度和执行微指令,处理器2000还可以包括用于处理存储器未命中的逻辑。在至少一个实施例中,如果数据高速缓存中的数据加载未命中,则可能存在在管线中正在运行的从属操作,其使调度器暂时没有正确的数据。在至少一个实施例中,一种重放机制追踪踪并重新执行使用不正确数据的

指令。在至少一个实施例中,可能需要重放从属操作并且可以允许完成独立操作。在至少一个实施例中,处理器的至少一个实施例的调度器和重放机制也可以设计为捕获用于文本串比较操作的指令序列。

[0243]

在至少一个实施例中,术语“寄存器”可以指代可以用作识别操作数的指令的一部分的机载处理器存储位置。在至少一个实施例中,寄存器可以是那些可以从处理器外部使用的寄存器(从程序员的角度来看)。在至少一个实施例中,寄存器可能不限于特定类型的电路。相反,在至少一个实施例中,寄存器可以存储数据、提供数据并执行本文描述的功能。在至少一个实施例中,本文描述的寄存器可以通过处理器内的电路使用多种不同技术来实现,例如专用物理寄存器、使用寄存器重命名动态分配的物理寄存器、专用和动态分配的物理寄存器的组合等。在至少一个实施例中,整数寄存器存储32位整数数据。至少一个实施例的寄存器文件还包含八个用于封装数据的多媒体simd寄存器。

[0244]

推理和/或训练逻辑615用于执行与一个或更多个实施例相关联的推理和/或训练操作。下面结合图6a和/或图6b提供关于推理和/或训练逻辑615的细节。在至少一个实施例中,推理和/或训练逻辑615可以并入执行块2011以及示出的或未示出的其他存储器或寄存器中。例如,在至少一个实施例中,本文描述的训练和/或推理技术可以使用在执行块2011中示出的一个或更多个alu。此外,权重参数可以存储在片上或片外存储器和/或寄存器(示出的或未示出的)中,该权重参数将执行块2011的alu配置为执行一个或更多个机器学习算法、神经网络架构、用例或本文描述的训练技术。

[0245]

推理和/或训练逻辑615用于执行与一个或更多个实施例相关联的推理和/或训练操作。在至少一个实施例中,此逻辑可与这些图的组件一起使用,以选择在呈现一个或更多个视频片段期间与一个或更多个观看者的所确定的情绪相关联的那些片段。

[0246]

图21示出了根据至少一个实施例的深度学习应用程序处理器2100。在至少一个实施例中,深度学习应用程序处理器2100使用指令,如果由深度学习应用程序处理器2100执行,则指令使深度学习应用程序处理器2100执行贯穿本公开描述的一些或全部过程和技术。在至少一个实施例中,深度学习应用程序处理器2100是专用集成电路(asic)。在至少一个实施例中,应用程序处理器2100执行矩阵乘法运算或者“硬连线”到硬件中,作为执行一个或更多个指令或两者的结果。在至少一个实施例中,深度学习应用程序处理器2100包括但不限于处理集群2110(1)

‑

2110(12)、芯片间链路(“icl”)2120(1)

‑

2120(12)、芯片间控制器(“icc”)2130(1)

‑

2130(2)、存储器控制器(“mem ctrlr”)2142(1)

‑

2142(4)、高带宽存储器物理层(“hbm phy”)2144(1)

‑

2144(4)、管理控制器中央处理单元(“管理控制器cpu”)2150、外围组件互连快速控制器和直接存储器访问块(“pcie控制器和dma”)2170、以及十六通道外围组件互连快速端口(“pci express x 16”)2180。

[0247]

在至少一个实施例中,处理集群2110可以执行深度学习操作,包括基于一种或更多种训练技术计算的权重参数的推理或预测操作,包括本文所述的那些技术。在至少一个实施例中,每个处理集群2110可以包括但不限于任何数量和类型的处理器。在至少一个实施例中,深度学习应用程序处理器2100可以包括任何数量和类型的处理集群2100。在至少一个实施例中,芯片间链路2120是双向的。在至少一个实施例中,芯片间链路2120和芯片间控制器2130使多个深度学习应用程序处理器2100能够交换信息,包括从执行一个或更多个神经网络中体现的一种或更多种机器学习算法而产生的激活信息。在至少一个实施例中,

深度学习应用程序处理器2100可以包括任意数量(包括零)和类型的icl 2120和icc 2130。

[0248]

在至少一个实施例中,hbm2 2140提供总共32gb的存储器。hbm22140(i)与存储器控制器2142(i)和hbm phy 2144(i)都相关联。在至少一个实施例中,任何数量的hbm2 2140可以提供任何类型和总量的高带宽存储器,并且可以与任何数量(包括零)和类型的存储器控制器2142和hbm phy 2144相关联。在至少一个实施例中,可以用任何数量和类型的块替换spi、i2c、gpio 3360、pcie控制器2160和dma 2170和/或pcie2180,以任何技术上可行的方式实现任何数量和类型的通信标准。

[0249]

推理和/或训练逻辑1015用于执行与一个或更多个实施例相关联的推理和/或训练操作。本文结合图6a和/或图6b提供关于推理和/或训练逻辑615的细节。在至少一个实施例中,深度学习应用程序处理器2100用于训练机器学习模型(例如神经网络),以预测或推理提供给深度学习应用程序处理器2100的信息。在至少一个实施例中,深度学习应用程序处理器2100用于基于已经由另一处理器或系统或由深度学习应用程序处理器2100训练的经训练的机器学习模型(例如,神经网络)来推理或预测信息。在至少一个实施例中,处理器2100可以用于执行本文所述的一个或更多个神经网络用例。

[0250]

推理和/或训练逻辑615用于执行与一个或更多个实施例相关联的推理和/或训练操作。在至少一个实施例中,此逻辑可与这些图的组件一起使用,以选择在呈现一个或更多个视频片段期间与一个或更多个观看者的所确定的情绪相关联的那些片段。

[0251]

图22是根据至少一个实施例的神经形态处理器2200的框图。在至少一个实施例中,神经形态处理器2200可以从神经形态处理器2200外部的源接收一个或更多个输入。在至少一个实施例中,这些输入可以被传输到神经形态处理器2200内的一个或更多个神经元2202。在至少一个实施例中,可以使用包括一个或更多个算术逻辑单元(alu)的电路或逻辑来实现神经元2202及其组件。在至少一个实施例中,神经形态处理器2200可以包括但不限于成千上万个神经元2202的实例,但是可以使用任何合适数量的神经元2202。在至少一个实施例中,神经元2202的每个实例可以包括神经元输入2204和神经元输出2206。在至少一个实施例中,神经元2202可以生成可以传输到神经元2202的其他实例的输入的输出。在至少一个实施例中,神经元输入2204和神经元输出2206可以经由突触2208互连。

[0252]

在至少一个实施例中,神经元2202和突触2208可以互连,使得神经形态处理器2200操作以处理或分析由神经形态处理器2200接收的信息。在至少一个实施例中,当通过神经元输入2204接收到的输入超过阈值时,神经元2202可以发送输出脉冲(或“触发”或“峰值”)。在至少一个实施例中,神经元2202可以对在神经元输入2204处接收到的信号进行求和或积分。例如,在至少一个实施例中,神经元2202可以实现为有泄漏的积分

‑

触发神经元,其中如果求和(称为“膜电位”)超过阈值,则神经元2202可以使用诸如sigmoid或阈值函数的传递函数来产生输出(或“触发”)。在至少一个实施例中,泄漏的积分

‑

触发神经元可以将在神经元输入2204处接收到的信号求和成膜电位,并且可以应用程序衰减因子(或泄漏)以减小膜电位。在至少一个实施例中,如果在神经元输入2204处接收到足够快以超过阈值的多个输入信号(即,在膜电势衰减得太低而不能触发之前),则泄漏的积分

‑

触发神经元可能会触发。在至少一个实施例中,神经元2202可以使用接收输入、将输入积分到膜电位、并衰减膜电位的电路或逻辑来实现。在至少一个实施例中,可以对输入求平均,或者可以使用任何其他合适的传递函数。此外,在至少一个实施例中,神经元2202可以包括但不限于当将传

递函数应用程序于神经元输入2204的结果超过阈值时在神经元输出2206处产生输出尖峰的比较器电路或逻辑。在至少一个实施例中,一旦神经元2202触发,它可以通过例如将膜电位复位为0或另一合适的默认值来忽略先前接收的输入信息。在至少一个实施例中,一旦膜电位被重置为0,则神经元2202可以在合适的时间段(或修复期)之后恢复正常操作。

[0253]

在至少一个实施例中,神经元2202可以通过突触2208互连。在至少一个实施例中,突触2208可以操作以将从第一神经元2202的输出的信号传输到第二神经元2202的输入。在至少一个实施例中,神经元2202可以在一个以上的突触2208实例上传输信息。在至少一个实施例中,神经元输出2206的一个或更多个实例可以通过突触2208的实例连接到同一神经元2202中神经元输入2204的实例。在至少一个实施例中,相对于突触2208的那个实例,神经元2202的实例产生要在突触2208的实例上传输的输出可以被称为“突触前神经元”。在至少一个实施例中,相对于突触2208的实例,神经元2202的实例接收通过突触2208的实例传输的输入可以被称为“突触后神经元”。在至少一个实施例中,关于突触2208的各种实例,因为神经元2202的实例可以接收来自一个或更多个突触2208实例的输入,并且还可以通过一个或更多个突触2208实例传输输出,因此神经元2202的单个实例可以既是“突触前神经元”又是“突触后神经元”。

[0254]

神经元2202可以被组织成一层或更多层。神经元2202的每个实例可以具有一个神经元输出2206,该神经元输出2206可以通过一个或更多个突触2208扇出到一个或更多个神经元输入2204。在至少一个实施例中,第一层2210中的神经元2202的神经元输出2206可以连接到第二层2212中的神经元2202的神经元输入2204。在至少一个实施例中,层2210可以被称为“前馈层”。在至少一个实施例中,在第一层2210的实例中神经元2202的每个实例可以扇出到第二层2212中的神经元2202的每个实例。在至少一个实施例中,第一层2210可以被称为“完全连接的前馈层”。在至少一个实施例中,在第二层2212的每个实例中的神经元2202的每个实例扇出到少于在第三层2214中的神经元2202的所有实例。在至少一个实施例中,第二层2212可以被称为“稀疏连接的前馈层”。在至少一个实施例中,第二层2212中的神经元2202可以扇出到多个其他层中的神经元2202,包括扇出到(相同的)第二层2212中的神经元2202。在至少一个实施例中,第二层2212可以被称为“循环层”。在至少一个实施例中,神经形态处理器2200可以包括但不限于循环层和前馈层的任何合适的组合,包括但不限于稀疏连接的前馈层和完全连接的前馈层。

[0255]

在至少一个实施例中,神经形态处理器2200可以包括但不限于可重新配置的互连架构或专用硬连线互连,以将突触2208连接到神经元2202。在至少一个实施例中,神经形态处理器2200可以包括但不限于电路或逻辑,其根据神经网络拓扑结构和神经元扇入/扇出,允许根据需要将突触分配给不同神经元2202。例如,在至少一个实施例中,可以使用互连结构(诸如片上网络)或通过专用连接将突触2208连接到神经元2202。在至少一个实施例中,可以使用电路或逻辑来实现突触互连及其组件。

[0256]

推理和/或训练逻辑615用于执行与一个或更多个实施例相关联的推理和/或训练操作。在至少一个实施例中,此逻辑可与这些图的组件一起使用,以选择在呈现一个或更多个视频片段期间与一个或更多个观看者的所确定的情绪相关联的那些片段。

[0257]

图23示出了根据至少一个实施例的处理系统。在至少一个实施例中,系统2300包括一个或更多个处理器2302和一个或更多个图形处理器2308,并且可以是单处理器台式机

系统、多处理器工作站系统或具有大量处理器2302或处理器核心2307的服务器系统。在至少一个实施例中,系统2300是结合在片上系统(soc)集成电路内的处理平台,以在移动、手持或嵌入式设备使用。

[0258]

在至少一个实施例中,系统2300可以包括或结合在基于服务器的游戏平台中,包括游戏和媒体控制台的游戏控制台、移动游戏控制台、手持游戏控制台或在线游戏控制台。在至少一个实施例中,系统2300是移动电话、智能电话、平板计算设备或移动互联网设备。在至少一个实施例中,处理系统2300还可包括与可穿戴设备耦合或集成在可穿戴设备中,例如智能手表可穿戴设备、智能眼镜设备、增强现实设备或虚拟现实设备。在至少一个实施例中,处理系统2300是电视或机顶盒设备,其具有一个或更多个处理器2302以及由一个或更多个图形处理器2308生成的图形界面。

[0259]

在至少一个实施例中,一个或更多个处理器2302每个包括一个或更多个处理器核心2307,以处理指令,该指令在被执行时执行针对系统和用户软件的操作。在至少一个实施例中,一个或更多个处理器核心2307中的每一个被配置为处理特定指令集2309。在至少一个实施例中,指令集2309可以促进复杂指令集计算(cisc)、精简指令集计算(risc),或通过超长指令字(vliw)进行计算。在至少一个实施例中,处理器核心2307可以各自处理不同的指令集2309,该指令集可以包括有助于仿真其他指令集的指令。在至少一个实施例中,处理器核心2307还可以包括其他处理设备,例如数字信号处理器(dsp)。

[0260]

在至少一个实施例中,处理器2302包括高速缓存存储器2304。在至少一个实施例中,处理器2302可以具有单个内部高速缓存或多个级别的内部高速缓存。在至少一个实施例中,高速缓存存储器在处理器2302的各个组件之间共享。在至少一个实施例中,处理器2302还使用外部高速缓存(例如,三级(l3)高速缓存或最后一级高速缓存(llc))(未示出),可以使用已知的高速缓存一致性技术在处理器核心2307之间共享该外部高速缓存。在至少一个实施例中,处理器2302中另外包括寄存器文件2306,处理器可以包括用于存储不同类型的数据的不同类型的寄存器(例如,整数寄存器、浮点寄存器、状态寄存器和指令指针寄存器)。在至少一个实施例中,寄存器文件2306可以包括通用寄存器或其他寄存器。

[0261]

在至少一个实施例中,一个或更多个处理器2302与一个或更多个接口总线2310耦合,以在处理器2302与系统2300中的其他组件之间传输通信信号,例如地址、数据或控制信号。在至少一个实施例中,接口总线2310在一个实施例中可以是处理器总线,例如直接媒体接口(dmi)总线的版本。在至少一个实施例中,接口总线2310不限于dmi总线,并且可以包括一个或更多个外围组件互连总线(例如,pci,pci express)、存储器总线或其他类型的接口总线。在至少一个实施例中,处理器2302包括集成存储器控制器2316和平台控制器集线器2330。在至少一个实施例中,存储器控制器2316促进存储器设备与处理系统2300的其他组件之间的通信,而平台控制器集线器(pch)2330通过本地i/o总线提供到输入/输出(i/o)设备的连接。

[0262]

在至少一个实施例中,存储器设备2320可以是动态随机存取存储器(dram)设备、静态随机存取存储器(sram)设备、闪存设备、相变存储设备或具有适当的性能以用作处理器存储器。在至少一个实施例中,存储设备2320可以用作处理系统2300的系统存储器,以存储数据2322和指令2321,以在一个或更多个处理器2302执行应用程序或过程时使用。在至少一个实施例中,存储器控制器2316还与可选的外部图形处理器2312耦合,其可以与处理

器2302中的一个或更多个图形处理器2308通信以执行图形和媒体操作。在至少一个实施例中,显示设备2311可以连接至处理器2302。在至少一个实施例中,显示设备2311可以包括内部显示设备中的一个或更多个,例如在移动电子设备或膝上型设备或通过显示器接口(例如显示端口(displayport)等)连接的外部显示设备中。在至少一个实施例中,显示设备2311可以包括头戴式显示器(hmd),诸如用于虚拟现实(vr)应用或增强现实(ar)应用中的立体显示设备。

[0263]

在至少一个实施例中,平台控制器集线器2330使外围设备能够通过高速i/o总线连接到存储设备2320和处理器2302。在至少一个实施例中,i/o外围设备包括但不限于音频控制器2346、网络控制器2334、固件接口2328、无线收发器2326、触摸传感器2325、数据存储设备2324(例如,硬盘驱动器、闪存等)。在至少一个实施例中,数据存储设备2324可以经由存储接口(例如,sata)或经由外围总线来连接,诸如外围组件互连总线(例如,pci、pcie)。在至少一个实施例中,触摸传感器2325可以包括触摸屏传感器、压力传感器或指纹传感器。在至少一个实施例中,无线收发器2326可以是wi

‑

fi收发器、蓝牙收发器或移动网络收发器,诸如3g、4g或长期演进(lte)收发器。在至少一个实施例中,固件接口2328使能与系统固件的通信,并且可以是例如统一可扩展固件接口(uefi)。在至少一个实施例中,网络控制器2334可以启用到有线网络的网络连接。在至少一个实施例中,高性能网络控制器(未示出)与接口总线2310耦合。在至少一个实施例中,音频控制器2346是多通道高清晰度音频控制器。在至少一个实施例中,处理系统2300包括可选的传统(legacy)i/o控制器2340,用于将传统(例如,个人系统2(ps/2))设备耦合到系统。在至少一个实施例中,平台控制器集线器2330还可以连接到一个或更多个通用串行总线(usb)控制器2342,该控制器连接输入设备,诸如键盘和鼠标2343组合、相机2344或其他usb输入设备。

[0264]

在至少一个实施例中,存储器控制器2316和平台控制器集线器2330的实例可以集成到离散的外部图形处理器中,例如外部图形处理器2312。在至少一个实施例中,平台控制器集线器2330和/或存储器控制器2316可以在一个或更多个处理器2302的外部。例如,在至少一个实施例中,系统2300可以包括外部存储器控制器2316和平台控制器集线器2330,其可以配置成在与处理器2302通信的系统芯片组中的存储器控制器集线器和外围控制器集线器。

[0265]

推理和/或训练逻辑615用于执行与一个或更多个实施例相关联的推理和/或训练操作。本文结合图6a和/或图6b提供关于推理和/或训练逻辑615的细节。在至少一个实施例中,部分或全部推理和/或训练逻辑615可以结合到图形处理器2300中。例如,在至少一个实施例中,本文描述的训练和/或推理技术可以使用一个或更多个alu,所述alu体现在图形处理器2312中。此外,在至少一个实施例中,本文描述的推理和/或训练操作可以使用除图6a或图6b所示的逻辑之外的逻辑来完成。在至少一个实施例中,权重参数可以存储在片上或片外存储器和/或寄存器(示出或未示出)中,其配置图形处理器2300的alu,以执行一种或更多种本文所述的机器学习算法、神经网络架构、用例或训练技术。

[0266]

推理和/或训练逻辑615用于执行与一个或更多个实施例相关联的推理和/或训练操作。在至少一个实施例中,此逻辑可与这些图的组件一起使用,以选择在呈现一个或更多个视频片段期间与一个或更多个观看者的所确定的情绪相关联的那些片段。

[0267]

图24是根据至少一个实施例的具有一个或更多个处理器核心2402a

‑

2402n、集成

存储器控制器2414和集成图形处理器2408的处理器2400的框图。在至少一个实施例中,处理器2400可以包含附加核心,多达并包括以虚线框表示的附加核心2402n。在至少一个实施例中,每个处理器核心2402a

‑

2402n包括一个或更多个内部高速缓存单元2404a

‑

2404n。在至少一个实施例中,每个处理器核心还可以访问一个或更多个共享高速缓存单元2406。

[0268]

在至少一个实施例中,内部高速缓存单元2404a

‑

2404n和共享高速缓存单元2406表示处理器2400内的高速缓存存储器层次结构。在至少一个实施例中,高速缓存存储器单元2404a

‑

2404n可以包括每个处理器核心内的至少一级指令和数据高速缓存以及共享中级高速缓存中的一级或更多级缓存,例如2级(l2)、3级(l3)、4级(l4)或其他级别的高速缓存,其中将外部存储器之前的最高级别的高速缓存归类为llc。在至少一个实施例中,高速缓存一致性逻辑维持各种高速缓存单元2406和2404a

‑

2404n之间的一致性。

[0269]

在至少一个实施例中,处理器2400还可包括一组一个或更多个总线控制器单元2416和系统代理核心2410。在至少一个实施例中,一个或更多个总线控制器单元2416管理一组外围总线,例如一个或更多个pci或pcie总线。在至少一个实施例中,系统代理核心2410为各种处理器组件提供管理功能。在至少一个实施例中,系统代理核心2410包括一个或更多个集成存储器控制器2414,以管理对各种外部存储器设备(未示出)的访问。

[0270]

在至少一个实施例中,一个或更多个处理器核心2402a

‑

2402n包括对多线程同时进行的支持。在至少一个实施例中,系统代理核心2410包括用于在多线程处理期间协调和操作核心2402a

‑

2402n的组件。在至少一个实施例中,系统代理核心2410可以另外包括电源控制单元(pcu),该电源控制单元包括用于调节处理器核心2402a

‑

2402n和图形处理器2408的一个或更多个电源状态的逻辑和组件。

[0271]

在至少一个实施例中,处理器2400还包括用于执行图处理操作的图形处理器2408。在至少一个实施例中,图形处理器2408与共享高速缓存单元2406和包括一个或更多个集成存储器控制器2414的系统代理核心2410耦合。在至少一个实施例中,系统代理核心2410还包括用于驱动图形处理器输出到一个或更多个耦合的显示器的显示器控制器2411。在至少一个实施例中,显示器控制器2411也可以是经由至少一个互连与图形处理器2408耦合的独立模块,或者可以集成在图形处理器2408内。

[0272]

在至少一个实施例中,基于环的互连单元2412用于耦合处理器2400的内部组件。在至少一个实施例中,可以使用替代性互连单元,例如点对点互连、交换互连或其他技术。在至少一个实施例中,图形处理器2408经由i/o链路2413与环形互连2412耦合。

[0273]

在至少一个实施例中,i/o链路2413代表多种i/o互连中的至少一种,包括促进各种处理器组件与高性能嵌入式存储器模块2418(例如edram模块)之间的通信的封装i/o互连。在至少一个实施例中,处理器核心2402a

‑

2402n和图形处理器2408中的每一个使用嵌入式存储器模块2418作为共享的最后一级高速缓存。

[0274]

在至少一个实施例中,处理器核心2402a

‑

2402n是执行公共指令集架构的同质核心。在至少一个实施例中,处理器核心2402a

‑

2402n在指令集架构(isa)方面是异构的,其中一个或更多个处理器核心2402a

‑

2402n执行公共指令集,而一个或更多个其他处理器核心2402a

‑

2402n执行公共指令集的子集或不同指令集。在至少一个实施例中,就微架构而言,处理器核心2402a

‑

2402n是异构的,其中具有相对较高功耗的一个或更多个核心与具有较低功耗的一个或更多个功率核心耦合。在至少一个实施例中,处理器2400可以在一个或更

多个芯片上实现或被实现为soc集成电路。

[0275]

推理和/或训练逻辑615用于执行与一个或更多个实施例相关联的推理和/或训练操作。下面结合图6a和/或图6b提供关于推理和/或训练逻辑615的细节。在至少一个实施例中,推理和/或训练逻辑615的部分或全部可以结合到处理器2400中。例如,在至少一个实施例中,本文描述的训练和/或推理技术可以使用在图形处理器2312、一个或更多个图形核心2402a

‑

2402n或图24中的其他组件中具体化的alu中的一个或更多个。此外,在至少一个实施例中,本文描述的推理和/或训练操作可以使用除了图6a或图6b中所示出的逻辑之外的逻辑来完成。在至少一个实施例中,可以将权重参数存储在片上或片外存储器和/或寄存器(示出或未示出的)中,该权重参数将图形处理器2400的alu配置成用于执行一个或更多个机器学习算法、神经网络架构、用例或本文描述的训练技术。

[0276]

推理和/或训练逻辑615用于执行与一个或更多个实施例相关联的推理和/或训练操作。在至少一个实施例中,此逻辑可与这些图的组件一起使用,以选择在呈现一个或更多个视频片段期间与一个或更多个观看者的所确定的情绪相关联的那些片段。

[0277]

图25是根据本文描述的至少一个实施例的图形处理器核心2500的硬件逻辑的框图。在至少一个实施例中,图形处理器核心2500包括在图形核心阵列内。在至少一个实施例中,图形处理器核心2500(有时被称为核心切片)可以是模块化图形处理器内的一个或更多个图形核心。在至少一个实施例中,图形处理器核心2500是一个图形核心切片的示例,并且如本文描述的图形处理器可以包括基于目标功率和性能包络的多个图形核心切片。在至少一个实施例中,每个图形核心2500可以包括与多个子核心2501a

‑

2501f(也被称为子切片)耦合的固定功能块2530,所述多个子核心包括具有通用和固定功能逻辑的模块化块。

[0278]

在至少一个实施例中,固定功能块2530包括几何和固定功能管线2536,例如,在较低性能和/或较低功率的图形处理器实施方式中,该几何和固定功能管线2536可以由图形处理器2500中的所有子核心共享。在至少一个实施例中,几何和固定功能管线2536包括3d固定功能管线、视频前端单元,线程产生器和线程分派器以及管理统一返回缓冲区的统一返回缓冲区管理器。

[0279]

在固定的至少一个实施例中,固定功能块2530还包括图形soc接口2537、图形微控制器2538和媒体管线2539。在至少一个实施例中,图形soc接口2537提供了图形核心2500以及片上集成电路系统中的其他处理器核心之间的接口。在至少一个实施例中,图形微控制器2538是可编程子处理器,其可配置为管理图形处理器2500的各种功能,包括线程分派、调度和抢占。在至少一个实施例中,媒体管线2539包括有助于对包括图像和视频数据的多媒体数据进行解码、编码、预处理和/或后处理的逻辑。在至少一个实施例中,媒体管线2539经由对子核心2501

‑

2501f内的计算或采样逻辑的请求来实现媒体操作。

[0280]

在至少一个实施例中,soc接口2537使图形核心2500能够与通用应用程序处理器核心(例如,cpu)和/或soc内的其他组件通信,包括存储器层次结构元素,诸如共享的最后一级高速缓存、系统ram和/或嵌入式片上或封装dram。在至少一个实施例中,soc接口2537还可以使得能够与soc内的固定功能设备(例如,相机成像管线)进行通信,并且使得能够使用和/或实现可以在图形核心2500和soc内部的cpu之间共享的全局存储器原子。在至少一个实施例中,soc接口2537还可以实现用于图形核心2500的电源管理控制,并且启用图形核心2500的时钟域与soc内的其他时钟域之间的接口。在至少一个实施例中,soc接口2537使

得能够从命令流转化器和全局线程分派器接收命令缓冲区,其配置为向图形处理器内的一个或更多个图形核心中的每一个提供命令和指令。在至少一个实施例中,当要执行媒体操作时,可以将命令和指令分派给媒体管线2539,或者当要执行图形处理操作时,可以将其分配给几何形状和固定功能管线(例如,几何形状和固定功能管线2536,几何形状和固定功能管线2514)。

[0281]

在至少一个实施例中,图形微控制器2538可以配置为对图形核心2500执行各种调度和管理任务。在至少一个实施例中,图形微控制器2538可以在子核心2501a

‑

2501f中的执行单元(eu)阵列2502a

‑

2502f、2504a

‑

2504f内的各种图形并行引擎上执行图形和/或计算工作负载调度。在至少一个实施例中,在包括图形核心2500的soc的cpu核心上执行的主机软件可以提交多个图形处理器门铃之一的工作负载,其调用适当的图形引擎上的调度操作。在至少一个实施例中,调度操作包括确定接下来要运行哪个工作负载、将工作负载提交给命令流转化器、抢先在引擎上运行的现有工作负载、监控工作负载的进度以及在工作负载完成时通知主机软件。在至少一个实施例中,图形微控制器2538还可以促进图形核心2500的低功率或空闲状态,从而为图形核心2500提供在图形核心2500内独立于操作系统和/或系统上的图形驱动程序软件的跨低功率状态转换的保存和恢复寄存器的能力。

[0282]

在至少一个实施例中,图形核心2500可以具有比所示的子核心2501a

‑

2501f多或少达n个模块化子核心。对于每组n个子核心,在至少一个实施例中,图形核心2500还可以包括共享功能逻辑2510、共享和/或高速缓存存储器2512、几何/固定功能管线2514以及附加的固定功能逻辑2516以加速各种图形和计算处理操作。在至少一个实施例中,共享功能逻辑2510可以包括可由图形核心2500内的每个n个子核心共享的逻辑单元(例如,采样器、数学和/或线程间通信逻辑)。在至少一个实施例中,共享和/或高速缓存存储器2512可以是图形核心2500内的n个子核心2501a

‑

2501f的最后一级高速缓存,并且还可以用作可由多个子核心访问的共享存储器。在至少一个实施例中,可以包括几何/固定功能管线2514来代替固定功能块2530内的几何/固定功能管线2536,并且可以包括相同或相似的逻辑单元。

[0283]

在至少一个实施例中,图形核心2500包括附加的固定功能逻辑2516,其可以包括供图形核心2500使用的各种固定功能加速逻辑。在至少一个实施例中,附加的固定功能逻辑2516包括用于仅位置着色中使用的附加的几何管线。在仅位置着色中,存在至少两个几何管线,而在几何和固定功能管线2514、2536内的完整几何管线和剔除管线中,其是可以包括在附加的固定功能逻辑2516中的附加几何管线。在至少一个实施例中,剔除管线是完整几何管线的修整版。在至少一个实施例中,完整管线和剔除管线可以执行应用程序的不同实例,每个实例具有单独的环境。在至少一个实施例中,仅位置着色可以隐藏被丢弃的三角形的长剔除运行,从而在某些情况下可以更早地完成着色。例如,在至少一个实施例中,附加固定功能逻辑2516中的剔除管线逻辑可以与主应用程序并行执行位置着色器,并且通常比完整管线更快地生成关键结果,因为剔除管线获取并遮蔽顶点的位置属性,无需执行光栅化和将像素渲染到帧缓冲区。在至少一个实施例中,剔除管线可以使用生成的临界结果来计算所有三角形的可见性信息,而与这些三角形是否被剔除无关。在至少一个实施例中,完整管线(在这种情况下可以称为重播管线)可以消耗可见性信息来跳过剔除的三角形以仅遮盖最终传递到光栅化阶段的可见三角形。

[0284]

在至少一个实施例中,附加的固定功能逻辑2516还可包括机器学习加速逻辑,例

如固定功能矩阵乘法逻辑,用于实现包括用于机器学习训练或推理的优化。

[0285]

在至少一个实施例中,在每个图形子核心2501a

‑

2501f内包括一组执行资源,其可用于响应于图形管线、媒体管线或着色器程序的请求来执行图形、媒体和计算操作。在至少一个实施例中,图形子核心2501a

‑

2501f包括多个eu阵列2502a

‑

2502f、2504a

‑

2504f,线程分派和线程间通信(td/ic)逻辑2503a

‑

2503f,3d(例如,纹理)采样器2505a

‑

2505f,媒体采样器2506a

‑

2506f,着色器处理器2507a

‑

2507f和共享本地存储器(slm)2508a

‑

2508f。eu阵列2502a

‑

2502f、2504a

‑

2504f每个都包含多个执行单元,这些执行单元是通用图形处理单元,能够为图形、媒体或计算操作提供服务,执行浮点和整数/定点逻辑运算,包括图形、媒体或计算着色器程序。在至少一个实施例中,td/ic逻辑2503a

‑

2503f为子核心内的执行单元执行本地线程分派和线程控制操作,并促进在子核心的执行单元上执行的线程之间的通信。在至少一个实施例中,3d采样器2505a

‑

2505f可以将与纹理或其他3d图形相关的数据读取到存储器中。在至少一个实施例中,3d采样器可以基于与给定纹理相关联的配置的采样状态和纹理格式来不同地读取纹理数据。在至少一个实施例中,媒体采样器2506a

‑

2506f可以基于与媒体数据相关联的类型和格式来执行类似的读取操作。在至少一个实施例中,每个图形子核心2501a

‑

2501f可以可替代地包括统一的3d和媒体采样器。在至少一个实施例中,在每个子核心2501a

‑

2501f内的执行单元上执行的线程可以利用每个子核心内的共享本地存储器2508a

‑

2508f,以使在线程组内执行的线程能够使用片上存储器的公共池来执行。

[0286]

推理和/或训练逻辑615用于执行与一个或更多个实施例相关联的推理和/或训练操作。下面结合图6a和/或图6b提供关于推理和/或训练逻辑615的细节。在至少一个实施例中,推理和/或训练逻辑615的部分或全部可以被合并到图形处理器2510中。例如,在至少一个实施例中,本文描述的训练和/或推理技术可以使用在图形处理器2312、图形微控制器2538、几何和固定功能管线2514和2536或图25中的其他逻辑中体现的一个或更多个alu。此外,在至少一个实施例中,本文描述的推理和/或训练操作可以使用除图6a或图6b所示的逻辑以外的逻辑来完成。在至少一个实施例中,权重参数可以存储在片上或片外存储器和/或寄存器(示出或未示出)中,其配置图形处理器2500的alu以执行一种或更多种本文介绍的机器学习算法、神经网络架构、用例或训练技术。

[0287]

推理和/或训练逻辑615用于执行与一个或更多个实施例相关联的推理和/或训练操作。在至少一个实施例中,此逻辑可与这些图的组件一起使用,以选择在呈现一个或更多个视频片段期间与一个或更多个观看者的所确定的情绪相关联的那些片段。

[0288]

图26a

‑

26b示出了根据至少一个实施例的包括图形处理器核心的处理元件的阵列的线程执行逻辑2600。图26a示出了至少一个实施例,其中使用了线程执行逻辑2600。图26b示出了根据至少一个实施例的执行单元的示例性内部细节。

[0289]

如图26a中所示,在至少一个实施例中,线程执行逻辑2600包括着色器处理器2602、线程分派器2604、指令高速缓存2606、包括多个执行单元2608a

‑

2608n的可缩放执行单元阵列、采样器2610、数据高速缓存2612和数据端口2614。在至少一个实施例中,可缩放执行单元阵列可以例如基于工作负载的计算要求,通过启用或禁用一个或更多个执行单元(例如,执行单元2608a、2608b、2608c、2608d至2608n

‑

1和2608n中的任意一个)来动态缩放。在至少一个实施例中,可缩放执行单元通过链路到每个执行单元的互连结构互连。在至少

一个实施例中,线程执行逻辑2600包括通过指令高速缓存2606、数据端口2614、采样器2610和执行单元2608a

‑

2608n中的一个或更多个到存储器(诸如系统存储器或高速缓存存储器)的一个或更多个连接。在至少一个实施例中,每个执行单元(例如2608a)是独立的可编程通用计算单元,其能够执行多个同时的硬件线程,同时针对每个线程并行处理多个数据元素。在至少一个实施例中,执行单元2608a

‑

2608n的阵列可缩放以包括任意数量的单独执行单元。

[0290]

在至少一个实施例中,执行单元2608a

‑

2608n主要用于执行着色器程序。在至少一个实施例中,着色器处理器2602可以处理各种着色器程序并经由线程分派器2604来分派与着色器程序相关联的执行线程。在至少一个实施例中,线程分派器2604包括用于仲裁来自图形和媒体管线的线程初始化庆祝以及在执行单元2608a

‑

2608n中的一个或更多个执行单元上实例化请求的线程的逻辑。例如,在至少一个实施例中,几何管线可以将顶点、镶嵌或几何着色器分派到线程执行逻辑以进行处理。在至少一个实施例中,线程分派器2604还可以处理来自执行着色器程序的运行时线程产生请求。

[0291]

在至少一个实施例中,执行单元2608a

‑

2608n支持一种指令集,该指令集包括对许多标准3d图形着色器指令的本机支持,从而使图形库(例如direct 3d和opengl)中的着色器程序只需最少的转换即可执行。在至少一个实施例中,执行单元支持顶点和几何处理(例如,顶点程序、几何程序、顶点着色器)、像素处理(例如,像素着色器、片段着色器)和通用处理(例如,计算和媒体着色器)。在至少一个实施例中,每个执行单元2608a

‑

2608n包括一个或更多个算术逻辑单元(alu),能够执行多发出单指令多数据(simd),并且多线程操作实现了高效的执行环境尽管有更高的延迟存储器访问。在至少一个实施例中,每个执行单元内的每个硬件线程具有专用的高带宽寄存器文件和相关的独立线程状态。在至少一个实施例中,执行是每个时钟到管线的多次发出,管线能够进行整数、单精度和双精度浮点运算、simd分支功能、逻辑运算、先验运算和其他其他运算。在至少一个实施例中,在等待来自存储器或共享功能之一的数据时,执行单元2608a

‑

2608n内的依赖性逻辑使等待线程休眠直到返回了所请求的数据。在至少一个实施例中,当等待线程正在休眠时,硬件资源可以专用于处理其他线程。例如,在至少一个实施例中,在与顶点着色器操作相关联的延迟期间,执行单元可以对像素着色器、片段着色器或另一类型的着色器程序(包括不同的顶点着色器)执行操作。

[0292]

在至少一个实施例中,执行单元2608a

‑

2608n中的每一个执行单元在数据元素的阵列上进行操作。在至少一个实施例中,多个数据元素是“执行大小”或指令的通道数。在至少一个实施例中,执行通道是用于指令内的数据元素访问、屏蔽和流控制的执行的逻辑单元。在至少一个实施例中,多个通道可以独立于用于特定图形处理器的多个物理算术逻辑单元(alu)或浮点单元(fpu)。在至少一个实施例中,执行单元2608a

‑

2608n支持整数和浮点数据类型。

[0293]

在至少一个实施例中,执行单元指令集包括simd指令。在至少一个实施例中,各种数据元素可以作为封装数据类型存储在寄存器中,并且执行单元将基于那些元素的数据大小来处理各种元素。例如,在至少一个实施例中,当对256位宽的向量进行操作时,将向量的256位存储在寄存器中,并且执行单元对向量进行操作,作为四个单独的64位封装数据元素(四字(qw)大小数据元素)、八个单独的32位封装数据元素(双字(dw)大小数据元素)、十六

个单独的16位封装数据元素(单词(w)大小数据元素)或三十二个单独的8位数据元素(字节(b)大小的数据元素)。然而,在至少一个实施例中,不同的向量宽度和寄存器大小是可能的。

[0294]

在至少一个实施例中,一个或更多个执行单元可以被组合成具有与融合eu共用的线程控制逻辑(2607a

‑

2607n)的融合执行单元2609a

‑

2609n。在至少一个实施例中,可以将多个eu合并成一个eu组。在至少一个实施例中,融合eu组中的eu的数量可以配置为执行单独的simd硬件线程。融合的eu组中的eu的数量可根据各个实施例而变化。在至少一个实施例中,每个eu可以执行各种simd宽度,包括但不限于simd8、simd16和simd32。在至少一个实施例中,每个融合图形执行单元2609a

‑

2609n包括至少两个执行单元。例如,在至少一个实施例中,融合执行单元2609a包括第一eu 2608a、第二eu 2608b以及与第一eu 2608a和第二eu 2608b共用的线程控制逻辑2607a。在至少一个实施例中,线程控制逻辑2607a控制在融合图形执行单元2609a上执行的线程,从而允许融合执行单元2609a

‑

2609n内的每个eu使用公共指令指针寄存器来执行。

[0295]

在至少一个实施例中,一个或更多个内部指令高速缓存(例如2606)被包括在线程执行逻辑2600中以高速缓存用于执行单元的线程指令。在至少一个实施例中,包括一个或更多个数据高速缓存(例如2612)以在线程执行期间高速缓存线程数据。在至少一个实施例中,包括采样器2610以提供用于3d操作的纹理采样和用于媒体操作的媒体采样。在至少一个实施例中,采样器2610包括专门的纹理或媒体采样功能,以在将采样数据提供给执行单元之前在采样过程中处理纹理或媒体数据。

[0296]

在执行期间,在至少一个实施例中,图形和媒体管线通过线程产生和分派逻辑将线程发起请求发送到线程执行逻辑2600。在至少一个实施例中,一旦一组几何对象已经被处理并光栅化成像素数据,则在着色器处理器2602内的像素处理器逻辑(例如,像素着色器逻辑、片段着色器逻辑等)被调用以进一步计算输出信息并且导致将结果写入输出表面(例如,颜色缓冲区、深度缓冲区、模板缓冲区等)。在至少一个实施例中,像素着色器或片段着色器计算要在光栅化对象上插值的各种顶点属性的值。在至少一个实施例中,着色器处理器2602内的像素处理器逻辑然后执行应用程序接口(api)提供的像素或片段着色器程序。在至少一个实施例中,为了执行着色器程序,着色器处理器2602经由线程分派器2604将线程分派到执行单元(例如2608a)。在至少一个实施例中,着色器处理器2602使用采样器2610中的纹理采样逻辑来访问存储在存储器中的纹理贴图中的纹理数据。在至少一个实施例中,对纹理数据和输入几何数据的算术运算为每个几何片段计算像素颜色数据,或者丢弃一个或更多个像素以进行进一步处理。

[0297]

在至少一个实施例中,数据端口2614提供了一种用于线程执行逻辑2600的存储器访问机制,以将处理后的数据输出到存储器以在图形处理器输出管线上进行进一步处理。在至少一个实施例中,数据端口2614包括或耦合到一个或更多个高速缓存存储器(例如,数据高速缓存2612)以高速缓存数据以便经由数据端口进行存储器访问。

[0298]

如图26b所示,在至少一个实施例中,图形执行单元2608可以包括指令获取单元2637、通用寄存器文件阵列(grf)2624、架构寄存器文件阵列(arf)2626、线程仲裁器2622、发送单元2630、分支单元2632、一组simd浮点单元(fpu)2634,以及在至少一个实施例中,一组专用整数simd alu 2635。grf 2624和arf 2626包括一组与可以在图形执行单元2608中

活跃的每个同时硬件线程相关联的通用寄存器文件和架构寄存器文件。在至少一个实施例中,在arf 2626中维护每个线程架构状态,而在线程执行期间使用的数据存储在grf 2624中。在至少一个实施例中,每个线程的执行状态,包括每个线程的指令指针,可以被保存在arf 2626中的线程专用寄存器中。

[0299]

在至少一个实施例中,图形执行单元2608具有一种架构,该架构是同时多线程(smt)和细粒度交错多线程(imt)的组合。在至少一个实施例中,架构具有模块化配置,该模块化配置可以在设计时基于同时线程的目标数量和每个执行单元的寄存器数量来进行微调,其中执行单元资源在用于执行多个同时线程的逻辑上分配。

[0300]

在至少一个实施例中,图形执行单元2608可以共同发布多个指令,每个指令可以是不同的指令。在至少一个实施例中,图形执行单元线程2608的线程仲裁器2622可以将指令分派到发送单元2630、分支单元2632或simd fpu 2634之一以供执行。在至少一个实施例中,每个执行线程可以访问grf 2624中的128个通用寄存器,其中每个寄存器可以存储32个字节,可以作为32位数据元素的simd 8元素向量进行访问。在至少一个实施例中,每个执行单元线程可以访问grf 2624中的4kb,尽管实施例不限于此,并且在其他实施例中可以提供更多或更少的寄存器资源。在至少一个实施例中,尽管每个执行单元的线程数量也可以根据实施例而变化,但是最多可以同时执行七个线程。在其中七个线程可以访问4kb的至少一个实施例中,grf 2624可以存储总共28kb。在至少一个实施例中,灵活的寻址模式可以允许将寄存器一起寻址以有效地建立更宽的寄存器或表示跨步的矩形块数据结构。

[0301]

在至少一个实施例中,经由由消息传递发送单元2630执行的“发送”指令来调度存储器操作、采样器操作和其他更长延迟的系统通信。在至少一个实施例中,将分支指令分派到专用分支单元2632促进simd发散和最终收敛。

[0302]

在至少一个实施例中,图形执行单元2608包括一个或更多个simd浮点单元(fpu)2634,以执行浮点操作。在至少一个实施例中,一个或更多个fpu 2634还支持整数计算。在至少一个实施例中,一个或更多个fpu 2634可以simd执行多达m个32位浮点(或整数)运算,或者simd执行多达2m个16位整数或16位浮点运算。在至少一个实施例中,至少一个fpu提供扩展的数学能力以支持高吞吐量的先验数学函数和双精度64位浮点。在至少一个实施例中,还存在一组8位整数simd alu 2635,并且可以被专门优化以执行与机器学习计算相关的操作。

[0303]

在至少一个实施例中,可以在图形子核心分组(例如,子切片)中实例化图形执行单元2608的多个实例的阵列。在至少一个实施例中,执行单元2608可以跨多个执行通道执行指令。在至少一个实施例中,在图形执行单元2608上执行的每个线程在不同的通道上执行。

[0304]

推理和/或训练逻辑615用于执行与一个或更多个实施例相关联的推理和/或训练操作。下面结合图6a和/或图6b提供关于推理和/或训练逻辑615的细节。在至少一个实施例中,推理和/或训练逻辑615的部分或全部可以被并入执行逻辑2600中。此外,在至少一个实施例中,可以使用除了图6a或图6b中所示的逻辑之外的逻辑来完成在此描述的推理和/或训练操作。在至少一个实施例中,权重参数可以存储在片上或片外存储器和/或寄存器(示出或未示出)中,其配置执行逻辑2600的alu以执行一种或更多种机器学习算法、神经网络架构、用例或本文介绍的训练技术。

[0305]

推理和/或训练逻辑615用于执行与一个或更多个实施例相关联的推理和/或训练操作。在至少一个实施例中,此逻辑可与这些图的组件一起使用,以选择在呈现一个或更多个视频片段期间与一个或更多个观看者的所确定的情绪相关联的那些片段。

[0306]