1.本技术涉及显示领域,尤其涉及一种阵列基板及其制备方法。

背景技术:

2.目前迷你/微发光二极管(mini/micro light emitting diode,mled)显示技术进入加速发展阶段。mled可以应用于中小型显示器,相较有机发光二极管(organic light emitting display,oled)显示器,mled显示器在成本、对比度、高亮度和轻薄外形上表现出更佳性能。在mled显示技术中,阵列基板技术作为关键技术控制着mled的显示,但是目前用于控制led显示的阵列基板容易受到外界环境光的影响,导致阵列基板的稳定性差。

技术实现要素:

3.本技术提供一种阵列基板及其制备方法,可以提高阵列基板的稳定性。

4.一种阵列基板,包括:

5.基板;

6.吸光层,所述吸光层设置于所述基板的一侧;

7.第一金属层,所述第一金属层设置于所述吸光层远离所述基板的一侧,或所述第一金属层设置于所述基板远离所述吸光层的一侧;

8.第二金属层,所述第二金属层设置于所述第一金属层远离所述基板的一侧,所述第二金属层包括栅极、源极、漏极和绑定部,所述绑定部与所述第一金属层连接。

9.在本技术的一些实施方式中,所述吸光层的材料为2,8

‑

二氟

‑

5,11

‑

双(三乙基硅烷基乙炔基)双噻吩蒽、6,12

‑

二(三乙基硅乙炔基)二苯并苯并二噻吩或2,7

‑

二癸基二苯并二噻吩中的一种或多种。

10.在本技术的一些实施方式中,所述吸光层的厚度为1微米至3微米。

11.在本技术的一些实施方式中,所述第二金属层为氧化铟锌/钼/铜的三层金属结构或氧化钼/铜的双层金属结构。

12.在本技术的一些实施方式中,所述阵列基板还包括第一缓冲层,所述第一缓冲层设置于所述吸光层与所述第一金属层之间且靠近所述第一金属层。

13.在本技术的一些实施方式中,所述阵列基板还包括第二缓冲层、半导体层、栅极绝缘层和第一钝化层,所述第二缓冲层覆盖所述第一金属层,所述半导体层设置于所述第二缓冲层远离所述第一金属层的一侧,所述栅极绝缘层覆盖所述半导体层,所述第一钝化层覆盖所述第二金属层,所述源极与所述半导体层和所述第一金属层连接。

14.在本技术的一些实施方式中,所述第一钝化层包括第一开口和第二开口,所述第一开口暴露出所述绑定部,所述第二开口暴露出所述源极。

15.在本技术的一些实施方式中,所述阵列基板还包括第二钝化层和黑色矩阵,所述第二钝化层设置于所述第一钝化层远离所述源极和所述漏极的一侧,所述黑色矩阵设置于所述第二钝化层远离所述第一钝化层的一侧。

16.相应的,本技术还提供一种阵列基板的制备方法,包括:

17.在基板的一侧形成吸光层;

18.在所述吸光层远离所述基板的一侧形成第一金属层,或在所述基板远离所述吸光层的一侧形成第一金属层;

19.在所述第一金属层远离所述基板的一侧形成第二金属层,对所述第二金属层图案化以形成栅极、源极、漏极和绑定部,所述绑定部与所述第一金属层连接。

20.本技术提供一种阵列基板及其制备方法。阵列基板包括:基板。吸光层,所述吸光层设置于所述基板的一侧。第一金属层,所述第一金属层设置于所述吸光层远离所述基板的一侧,或所述第一金属层设置于所述基板远离所述吸光层的一侧。第二金属层,所述第二金属层设置于所述第一金属层远离所述基板的一侧。所述第二金属层包括栅极、源极、漏极和绑定部。所述绑定部与所述第一金属层连接。本技术提供的阵列基板,在基板一侧设置吸光层,提高了阵列基板的光稳定性。与此同时,本技术在同一制程中制备栅极、源极、漏极和绑定部,制备工艺简单,有利于降低制作阵列基板的制作成本。

附图说明

21.为了更清楚地说明本技术中的技术方案,下面将对实施例描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本技术的一些实施例,对于本领域技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

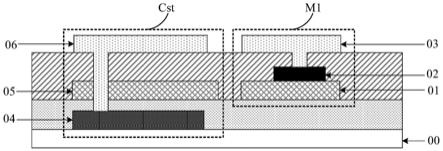

22.图1为本技术实施例提供的阵列基板的结构示意图。

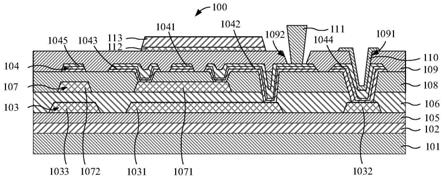

23.图2为本技术提供的阵列基板的第一种实施例沿aa’线的剖面图。

24.图3为本技术提供的阵列基板的第二种实施例沿aa’线的剖面图。

25.图4为本技术提供的阵列基板的制备方法的第一种实施例的流程图。

26.图5为本技术提供的阵列基板的制备方法的第二种实施例的流程图。

27.图6a

‑

6l为本技术提供的阵列基板的制备方法的第二种实施例的示意图。

具体实施方式

28.下面将结合本技术实施例中的附图,对本技术实施例中的技术方案进行清楚、完整地描述。显然,所描述的实施例仅是本技术一部分实施例,而不是全部的实施例。基于本技术中的实施例,本领域技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本技术保护的范围。

29.需要说明的是,本技术所提到的[第一]、[第二]、[第三]和[第四]等序号用语并不代表任何顺序、数量或者重要性,只是用于区分不同的部分。本技术所提到的[上]、[下]、[左]和[右]等方向用语仅是参考附加图式的方向。因此,使用的序号用语、方向用语和位置关系用语是用以说明及理解本技术,而非用以限制本技术。在图中,结构相似的单元是以相同标号表示。

[0030]

本技术提供一种阵列基板及其制备方法,下面将结合具体实施例对本技术进行详细说明。

[0031]

请参阅图1

‑

3,图1为本技术实施例提供的阵列基板的结构示意图。图2为本技术提供的阵列基板的第一种实施例沿aa’线的剖面图。图3为本技术提供的阵列基板的第二种实

施例沿aa’线的剖面图。

[0032]

如图2所示,阵列基板100包括基板101、吸光层102、第一金属层103以及第二金属层104。吸光层102设置于基板101的一侧。第一金属层103可以设置于吸光层102远离基板101的一侧。或者如图3所示,第一金属层103也可以设置于基板101远离吸光层102的一侧。第二金属层104设置于第一金属层103远离基板101的一侧。第二金属层104包括栅极1041、源极1042、漏极1043以及绑定部1044。绑定部1044与第一金属层103连接。

[0033]

其中,基板101可以是玻璃基板或柔性基板。吸光层102可以通过涂布的方式形成。第一金属层103可以由钼(mo)或钼(mo)/铜(cu)的叠层金属形成。第一金属层103可以通过物理气相沉积的方式形成。

[0034]

本技术通过在基板101一侧设置吸光层102,提高了阵列基板100的光稳定性。此外,本技术还通过在同一制程中制备栅极1041、源极1042、漏极1043和绑定部1044,简化了阵列基板100的制备工艺。

[0035]

在一些实施例中,第一金属层103包括遮光部1031、连接部1032和第一极板1033。绑定部1044与连接部1032连接。第二金属层104还包括第二极板1045。第二极板1045与第一极板1033对应设置。第一极板1033在基板101上的正投影与第二极板1045在基板101上的正投影至少部分重叠。

[0036]

在一些实施例中,吸光层102的材料为2,8

‑

二氟

‑

5,11

‑

双(三乙基硅烷基乙炔基)双噻吩蒽、6,12

‑

二(三乙基硅乙炔基)二苯并苯并二噻吩或2,7

‑

二癸基二苯并二噻吩中的一种或多种。

[0037]

噻吩系有机半导体具有较强的光响应特性,作为吸光层102可以减少外界环境光对阵列基板100的影响,提高了阵列基板100的光稳定性。此外,噻吩系的有机半导体还具有含氢量低和稳定性高等特性,作为吸光层102不会对阵列基板100产生不良影响。

[0038]

在一些实施例中,吸光层102的厚度为1微米至3微米。具体的,吸光层102的厚度为1微米、2微米或3微米。

[0039]

本技术通过设置吸光层102的厚度小于3微米,可以避免因吸光层102的厚度过大,而不利于显示装置轻薄化的发展趋势。设置吸光层102的厚度大于1微米可以避免因吸光层102的厚度过薄,而不利于对外界环境光的吸收,从而不利于提高阵列基板100的光稳定性。

[0040]

在一些实施例中,第二金属层104为氧化铟锌(izo)/钼(mo)/铜(cu)的三层金属结构或氧化钼(moo

x

)/铜(cu)的双层金属结构。

[0041]

其中,在izo/mo/cu的三层金属结构中,izo作为低反射功能层。cu作为电极层。通过将mo设置在izo与cu之间,可以提高izo与cu的贴合性。izo的厚度为15纳米至30纳米。具体的,izo的厚度为15纳米、20纳米、25纳米或30纳米。在moo

x

/cu双层金属结构中,moo

x

作为低反射功能层。cu作为电极层。moo

x

的厚度为20纳米至30纳米。具体的,moo

x

的厚度为20纳米、25纳米或30纳米。

[0042]

本技术通过将第二金属层104设置为izo/mo/cu的三层金属结构或moo

x

/cu的双层金属结构。其中,izo和moo

x

作为低反射功能层,可以减少散射光经过栅极、源极和漏极再次反射进入有源层而影响阵列基板100的稳定性。本技术还通过将izo的厚度设置为15纳米至30纳米,moo

x

的厚度设置为20纳米至30纳米,有利于在对第二金属层104图案化时,izo和moo

x

易于除去。

[0043]

在一些实施例中,阵列基板100还包括第一缓冲层105。第一缓冲层105设置于吸光层102与第一金属层103之间且靠近第一金属层103。

[0044]

其中,第一缓冲层105可以由氧化硅(sio

x

)或氧化硅(sio

x

)/氮化硅(sin

x

)的叠层形成。第一缓冲层105可以通过化学气相沉积的方式形成。

[0045]

本技术通过在吸光层102与第一金属层103之间且靠近第一金属层103的一侧设置第一缓冲层105,可以提高第一金属层103与基板101的贴合性,保证第一金属层103不易发生脱落。

[0046]

在一些实施例中,阵列基板还包括第二缓冲层106、半导体层107、栅极绝缘层108和第一钝化层109。第二缓冲层106覆盖第一金属层103。半导体层107设置于第二缓冲层106远离第一金属层103的一侧。栅极绝缘层108覆盖半导体层107。第一钝化层109覆盖第二金属层104。源极1042与半导体层107和第一金属层103连接。

[0047]

在一些实施例中,半导体层107包括有源部1071和第三极板1072。有源部1071与遮光部1031对应设置。第三极板1072与第一极板1033和第二极板1045对应设置。其中,第一极板1033、第三极板1072以及第二缓冲层106形成第一电容。第二极板1045、第三极板1072以及栅极绝缘层108形成第二电容。第一电容和第二电容并联连接。

[0048]

其中,第二缓冲层106可以由sio

x

或sio

x

/sin

x

的叠层形成。第二缓冲层106可以通过化学气相沉积的方式形成。半导体层107可以由氧化镓铟锌(igzo)、氧化镓锌铟锡(igzto)或氧化镓铟锡(igto)中的一种或多种形成。栅极绝缘层108可以由sio

x

或sio

x

/sin

x

的叠层形成。第一钝化层109可以由sio

x

或sio

x

/sin

x

的叠层形成。第一钝化层109可以通过化学气相沉积的方式形成。

[0049]

在一些实施例中,第一钝化层109包括第一开口1091和第二开口1092。第一开口1091暴露出绑定部1044。第二开口1092暴露出源极1042。

[0050]

本技术通过在第一钝化层109中设置第一开口1091并暴露出绑定部1044,可以实现绑定部1044与数据线的连接。通过在第一钝化层109中设置第二开口1092并暴露出源极1042,可以实现源极1042与发光二极管111的连接。

[0051]

在一些实施例中,第一开口1091内设置有保护层110。保护层110覆盖绑定部1044。第二开口1092内设置有发光二极管111,发光二极管111与源极1042连接。

[0052]

其中,发光二极管111可以是miniled或microled中的一种。保护层110可以由氧化铟锡(ito)或氧化铟锌(izo)等金属氧化物形成。保护层110可以通过物理气相沉积的方式形成。保护层110的厚度为50纳米至100纳米。具体的保护层110的厚度为50纳米、60纳米、70纳米、80纳米、90纳米或100纳米。

[0053]

本技术通过在绑定部1044上设置保护层110,可以防止绑定部1044被外界水汽侵蚀,还可以防止在后续制程中,高温引起绑定部1044发生热氧化,造成绑定不良。同时,由于ito和izo的成膜性好,通过在绑定部1044上设置保护层110,还可以提高绑定部1044的平整度,从而提高绑定的可靠性。

[0054]

在一些实施例中,阵列基板100还包括第二钝化层112和黑色矩阵113。第二钝化层112设置于第一钝化层109远离源极1042和漏极1043的一侧。黑色矩阵113设置于第二钝化层112远离第一钝化层109的一侧。

[0055]

其中,第二钝化层112可以由sio

x

或sio

x

/sin

x

的叠层形成。第二钝化层112可以通

过化学气相沉积的方式形成。黑色矩阵113可以由高遮光的光阻材料形成。黑色矩阵113可以作为薄膜晶体管沟道区的遮光层。

[0056]

本技术通过在黑色矩阵113与第一钝化层109之间设置第二钝化层112,防止在形成黑色矩阵113时,对第二金属层104产生影响。通过设置黑色矩阵113,可以阻挡外界光线对薄膜晶体管的影响,从而提高阵列基板100的稳定性。

[0057]

请参阅图4,图4为本技术提供的阵列基板的制备方法的第一种实施例的流程图。

[0058]

本技术提供一种阵列基板的制备方法,包括:

[0059]

步骤b10:在基板的一侧形成吸光层。

[0060]

其中,基板可以是玻璃基板或柔性基板。吸光层可以为2,8

‑

二氟

‑

5,11

‑

双(三乙基硅烷基乙炔基)双噻吩蒽、6,12

‑

二(三乙基硅乙炔基)二苯并苯并二噻吩或2,7

‑

二癸基二苯并二噻吩中的一种或多种。吸光层可以通过涂布的方式形成。经波长为250纳米至300纳米的紫外光照射5分钟至10分钟固化,再在温度为200摄氏度至300摄氏度的条件下高温烘烤1小时至2小时。具体的,紫外光的波长可以为250纳米、280纳米或300纳米。紫外光的照射时间可以为5分钟、8分钟或10分钟。烘烤温度可以为200摄氏度、250摄氏度或300摄氏度。烘烤的时间为1小时、1.5小时或2小时。具体的,吸光层的厚度为1微米至3微米。吸光层102的厚度可以为1微米、2微米或3微米。

[0061]

步骤b20:在所述吸光层远离所述基板的一侧形成第一金属层,或在所述基板远离所述吸光层的一侧形成第一金属层。

[0062]

其中,第一金属层可以由mo或mo/cu的叠层金属形成。第一金属层可以通过物理气相沉积的方式形成。

[0063]

步骤b30:在所述第一金属层远离所述基板的一侧形成第二金属层,对所述第二金属层图案化以形成栅极、源极、漏极和绑定部,所述绑定部与所述第一金属层连接。

[0064]

其中,第二金属层可以由izo/mo/cu的三层金属结构或moo

x

/cu双层金属结构形成。其中,在izo/mo/cu的三层金属结构中,izo作为低反射功能层。cu作为电极层。通过将mo设置在izo与cu之间,可以提高izo与cu的贴合性。izo的厚度为15纳米至30纳米。具体的,izo的厚度为15纳米、20纳米、25纳米或30纳米。在moo

x

/cu双层金属结构中,moo

x

作为低反射功能层。cu作为电极层。moo

x

的厚度为20纳米至30纳米。具体的,moo

x

的厚度为20纳米、25纳米或30纳米。

[0065]

本技术通过在基板一侧设置吸光层,提高了阵列基板的光稳定性。此外,本技术还通过在同一制程中制备栅极、源极、漏极以及绑定部,简化了阵列基板的制备工艺。本技术还通过采用具有低反射功能层的材料制备栅极、源极、漏极以及绑定部,减少了外界环境光的散射,从而减少外界环境光对阵列基板的影响。

[0066]

请参阅图5和6a

‑

6l,图5为本技术提供的阵列基板的制备方法的第二种实施例的流程图。图6a

‑

6l为本技术提供的阵列基板的制备方法的第二种实施例的示意图。

[0067]

本技术还提供一种阵列基板的制备方法,包括:

[0068]

步骤b10:在基板的一侧形成吸光层。

[0069]

如图6a所示,在基板101的一侧形成吸光层102。基板101可以是玻璃基板或柔性基板。吸光层102可以为2,8

‑

二氟

‑

5,11

‑

双(三乙基硅烷基乙炔基)双噻吩蒽、6,12

‑

二(三乙基硅乙炔基)二苯并苯并二噻吩或2,7

‑

二癸基二苯并二噻吩中的一种或多种。

[0070]

步骤b40:在吸光层远离基板的一侧形成第一缓冲层;或在基板远离吸光层的一侧形成第一缓冲层。

[0071]

如图6b

‑

6c所示,在吸光层102远离基板101的一侧形成第一缓冲层105;或在基板101远离吸光层102的一侧形成第一缓冲层105。第一缓冲层105可以由sio

x

或sio

x

/sin

x

的叠层形成。第一缓冲层105可以采用化学气相沉积的方式形成。

[0072]

步骤b50:在吸光层远离基板的一侧形成第一金属层,或在基板远离吸光层的一侧形成第一金属层,对第一金属层图案化以形成遮光部、连接部和第一极板。

[0073]

如图6d所示,在吸光层102远离基板101的一侧形成第一金属层103,或在基板101远离吸光层102的一侧形成第一金属层103。可以采用双氧水系蚀刻液对第一金属层103图案化以形成遮光部1031、连接部1032和第一极板1033。第一金属层103可以由mo或mo/cu的叠层金属形成。第一金属层103可以通过物理气相沉积的方式形成。

[0074]

步骤b60:形成覆盖第一金属层的第二缓冲层。

[0075]

如图6e所示,形成覆盖第一金属层103的第二缓冲层106。第二缓冲层106可以由sio

x

或sio

x

/sin

x

的叠层形成。第二缓冲层106可以采用化学气相沉积的方式形成。

[0076]

步骤b70:在第二缓冲层远离第一金属层的一侧形成半导体层。

[0077]

如图6e所示,在第二缓冲层106远离第一金属层103的一侧形成半导体层107。在第二缓冲层106远离第一金属层103的一侧形成半导体层107之前需要高温退火处理2

‑

3小时,退火温度为300摄氏度至400摄氏度。具体的,退火温度可以为300摄氏度、350摄氏度或400摄氏度。具体的,退火时间可以为2小时、2.3小时或3小时。半导体层107可以由igzo、igzto或igto中的一种或多种形成。对半导体层107图案化以形成有源部1071和第三极板1072。其中,有源部1071与遮光部1031对应设置。遮光部1031在基板101上的正投影覆盖有源部1071在基板101上的正投影。

[0078]

步骤b80:在半导体层远离第二缓冲层的一侧形成栅极绝缘层。

[0079]

如图6f所示,在半导体层107远离第二缓冲层106的一侧形成栅极绝缘层108。栅极绝缘层108可以由sio

x

或sio

x

/sin

x

的叠层形成。

[0080]

步骤b90:在第二缓冲层和栅极绝缘层中形成第一开孔、第二开孔、第三开孔和第四开孔,第一开孔和第二开孔暴露出第一金属层,第三开孔和第四开孔暴露出半导体层形成沟道区和非沟道区。

[0081]

如图6g所示,在第二缓冲层106和栅极绝缘层108中形成第一开孔1081、第二开孔1082、第三开孔1083和第四开孔1084。第一开孔1081和第二开孔1082暴露出第一金属层103,第三开孔1083和第四开孔1084暴露出半导体层107形成沟道区和非沟道区。其中,采用等离子处理第三开孔1083和第四开孔1084。将有源部1071形成薄膜晶体管的沟道区和非沟道区。其中,有源部1071被导体化的区域为薄膜晶体管的非沟道区。

[0082]

步骤b100:在第一金属层远离基板的一侧形成第二金属层,对第二金属层图案化以形成栅极、源极、漏极、绑定部和第二极板,绑定部与连接部连接,第二极板与第一极板对应设置。

[0083]

如图6h所示,在第一金属层103远离基板101的一侧形成第二金属层104。对第二金属层104图案化以形成栅极1041、源极1042、漏极1043、绑定部1044和第二极板1045。绑定部1044与连接部1032接。第二极板1045与第一极板1033对应设置。第二金属层104可以由izo/

mo/cu的三层金属结构或moo

x

/cu双层金属结构形成。其中,在izo/mo/cu的三层金属结构中,izo作为低反射功能层。cu作为电极层。通过将mo设置在izo与cu之间,可以提高izo与cu的贴合性。izo的厚度为15纳米至30纳米。具体的,izo的厚度为15纳米、20纳米、25纳米或30纳米。在moo

x

/cu双层金属结构中,moo

x

作为低反射功能层。cu作为电极层。moo

x

的厚度为20纳米至30纳米。具体的,moo

x

的厚度为20纳米、25纳米或30纳米。

[0084]

步骤b110:形成覆盖第二金属层的第一钝化层,对第一钝化层图案化以形成第一开口和第二开口,第一开口与第一开孔对应设置,第一开口暴露出绑定部,第二开口暴露出源极。

[0085]

如图6i所示,形成覆盖第二金属层104的第一钝化层109,对第一钝化层109图案化以形成第一开口1091和第二开口1092。第一钝化层109可以由sio

x

或sio

x

/sin

x

的叠层形成。第一钝化层109可以通过化学气相沉积的方式形成。

[0086]

步骤b120:在第一开口内形成保护层。

[0087]

如图6j所示,在第一开口1091内形成保护层110。保护层110覆盖绑定部1044。保护层110以由ito或izo形成。保护层110可以通过物理气相沉积的方式形成。保护层110的厚度为50纳米至100纳米。具体的保护层110的厚度为50纳米、60纳米、70纳米、80纳米、90纳米或100纳米。

[0088]

步骤b130:在第一钝化层远离第二金属层的一侧形成第二钝化层。

[0089]

如图6k所示,在第一钝化层109远离第二金属层104的一侧形成第二钝化层112。第二钝化层112可以由sio

x

或sio

x

/sin

x

的叠层形成。第二钝化层112可以通过化学气相沉积的形成。

[0090]

步骤b140:在第二钝化层远离第一钝化层的一侧形成黑色矩阵。

[0091]

如图6l所示,在第二钝化层112远离第一钝化层109的一侧形成黑色矩阵113。黑色矩阵113可以由高遮光的光阻材料形成。黑色矩阵113可以作为薄膜晶体管沟道区的遮光层,防止外界环境光进入到薄膜晶体管的沟道区,影响薄膜晶体管的稳定性。

[0092]

步骤b150:在第二开口内形成发光二极管。

[0093]

如图2所示,在第二开口1092内形成发光二极管111。发光二极管111可以是miniled或microled中的一种。

[0094]

在一些实施例中,在第二开口1092内形成发光二极管111之前还可以包括锡膏印刷和acf胶贴合。

[0095]

本技术通过在基板一侧设置吸光层,提高了阵列基板的光稳定性。此外,本技术还通过在同一制程中制备栅极、源极、漏极以及绑定部,简化了阵列基板的制备工艺。通过采用具有低反射功能层的材料制备栅极、源极、漏极以及绑定部,减少了外界环境光的散射,从而减少外界环境光对阵列基板的影响。

[0096]

综上所述,虽然本技术实施例的详细介绍如上,但上述实施例并非用以限制本技术,本领域的普通技术人员应当理解:其依然可以对前述实施例所记载的技术方案进行修改,或者对其中部分技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本技术实施例的技术方案的范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。