一种高精度多模多频北斗导航soc芯片

技术领域:

:1.本发明属于卫星导航

技术领域:

:,具体地说,是涉及一种高精度多模多频北斗导航soc芯片。

背景技术:

::2.2019年北斗全球系统系统已全部部署完毕,标志着全球系统核心星座部署完成,将为全球用户提供性能优异的导航服务,以及全球短报文通信、国际搜救等特色服务,相较于北斗之前的系统系统,北斗全球系统有四方面的性能提升:一是更高的精度,北斗全球基本系统建成后,全球定位精度10米;在亚太地区定位精度,由原来的6米提升至5米;二是更强的原子钟,北斗卫星采用了更高性能的铷原子钟和氢原子钟,铷原子钟天稳定度为10-14量级,氢原子钟天稳定度为10-15量级。三是更新的技术,北斗卫星通过采用新的技术,空间信号精度优于0.5m。四是更优的信号,北斗卫星增加了性能更优的互操作信号b1c,同时,在全球系统中将b2i信号升级为性能更优的b2a信号。3.北斗全球系统更为优越的性能,未来需求将呈爆发式增长,无论军用、行业应用还是民用北斗设备都将在未来2-3年内更换为北斗全球系统装备。相比基于导航芯片实现的基带产品,传统的基于fpga实现的方案存在以下几个问题,一是成本居高不下,fpga本身的成本都在数百元,加上外部的ad器件等器件成本单个基带产品的成本至少在2000元以上,成本的居高不下限制了北斗产品的进一步推广,特别是单兵和弹载方面,需求量非常大,降低成本已是必然要求,本产品的顺利实施预期将单颗基带产品降低50%,极大促进基带芯片的推广应用;二是目前基于fpga的方案集成度不高,板卡体积无法做小,导致设备体积大,携带不变,单兵应用对产品的小型化和轻便化有着强烈的要求;三是基于fpga的功耗大,对于便携式设备,需要工作时间长,对降低功耗有着强烈的需求;四是fpga大多采用国外的产品实现,在自主、安全和可控方面对国产化芯片替代有着强烈要求。基于以上几点,设计低功耗、高集成度和高精度的北斗导航芯片是北斗产业发展的必然选择。4.目前国内主要的北斗芯片存在以下几个问题:1、只支持单一频点,不支持多模多频;2、芯片只支持基带功能,没有soc化;3、芯片定位精度不够,不支持厘米级定位。技术实现要素:5.为了解决上述现有技术存在的问题,本发明提出了一种高精度多模多频北斗导航soc芯片,在达到高精度的同时,支持bds的全部信号格式,包含民码和军码,包括b1i、b1c、b1a、b2a、b3i、b3q、b3a、b3ae,而且支持gps的l1c\a、l1c、l2c频点,gln的g1和geo和e10s频点,gln的g1和geo和e10s频点,做到多模多频兼容。6.本发明芯片由基带算法模块、高性能微处理器、高性能adc模块、ddr3接口模块和低速扩展接口等部分组成。7.基带算法模块包含:gnss跟踪模块、抗干扰模块、电文与伪距处理模块、时间同步与授时模块、低功耗长码直捕模块。8.高性能微处理器部分包含:双核mcu采用非对称架构,每个内核具有独享的外设,两个内核也有共享的外设。两个mcu处理器内核可以具有不同的主频。cpu1的所有外设均为可以为两个cpu访问,即是共享外设。cpu0的部分外设仅cpu0可访问,cpu1不可访问,处理器内核及浮点协处理器完成pvt解算,输出定位、测速结果,同时对用户提供一个开放的可编程处理器接口,可根据用户需求完成进一步的功能。9.为了提高系统集成度,增加系统可靠性和降低成本考虑,片上集成了10路高精度adc,由五个2通道adc构成。10.此芯片具有ddr3/ddr3l的控制器,并且内部集成了pub和phy,能够连接ddr3或者ddr3l的存储器。支持ddr3或者ddr3l的存储器,支持32位宽,最大支持2gb地址空间。此芯片中规划64mb的ddr空间为cpu0运行ucos-ii/freertos操作系统时存储堆栈的数据;同时为bd3基带规划128mb存储空间,用于基带信息处理时的数据缓存。外接512mb~2gb的存储器,建议型号为:mt41k128m16(256mb@16bit)、mt41k256m16(512mb@16bit)、mt41k512m16(1024mb@16bit)。11.此芯片具有一个dap(debugaccessport)-lite接口。包含以下组件:serialwirejtagdebugport(swj-dp)、advancedperipheralbusaccessport(apb_ap)、advancedperipheralbusmultiplexor(apb_mux)、readonlymemory(rom)table。12.本发明芯片的设计中,主要包含以下接口:usb接口、i2c接口、uart接口、spi接口、iccard、可编程gpio接口。13.与现有技术相比,本发明的优点和积极效果是:本发明在soc实现上,相比现有技术产品功能更为齐备,芯片处理能力更强,采用了mcu处理器,是目前所有导航芯片中处理器性能最为先进的,设计频率600m(最差条件),实测频率可达1ghz以上,同时本发明采用了ddr3和千兆以太网接口,适用于高性能系统要求,兼容性更好。本发明的功耗和集成度均明显优于现有技术,实现了soc芯片的小尺寸、低成本、高集成度设计。附图说明14.图1为本发明soc芯片架构图。具体实施方式15.下面结合附图对本发明的具体实施方式作进一步详细地说明。16.本发明芯片是一款面向北斗三号卫星导航系统应用的基于非对称架构双核mcu处理器的bd-iii基带soc,能够实现各导航频点中频信号的基带信息处理与信息处理,实现定位、测速、导航等功能。其内部包含基带算法模块、高性能微处理器、高性能adc模块、ddr3接口模块和低速扩展接口等主要功能模块,芯片实现采用40nmll工艺设计,采用高性能、低功耗、高可靠性设计方法,按照严格的sign-off标准执行,实现了高精度多模多频产品的小型化、低功耗、低成本设计。17.下面结合附图对soc芯片内部的主要功能模块进行具体阐述。18.基带算法模块包含:gnss跟踪模块、抗干扰模块、电文与伪距处理模块、时间同步与授时模块、低功耗长码直捕模块,这部分主要完成功能如下:(1)具有独立的gnss信号处理通道和独立的rdss信号处理通道;(2)gnss支持bd2-b1、b2、b3频点,gps-l1频点和glonass-l1频点信号的捕获、跟踪;(3)rdss支持信号定位、短报文和指挥功能,具有“单发双收”与“双收单发”两种定位模式,并能自动切换;(4)gnss具备单系统和多系统的pvt解算功能;(5)gnss可输出伪距、多普勒、电文等原始观测量;(6)b3频点和rdss信号具有窄带干扰抑制能力。19.高性能微处理器包含:双核mcu采用非对称架构,每个内核具有独享的外设,两个内核也有共享的外设。两个mcu处理器内核可以具有不同的主频。20.cpu1的所有外设均为可以为两个cpu访问,即是共享外设。cpu0的部分外设仅cpu0可访问,cpu1不可访问,处理器内核及浮点协处理器完成pvt解算,输出定位、测速结果,同时对用户提供一个开放的可编程处理器接口,可根据用户需求完成进一步的功能,主要性能指标如下:(1)icache、dcache容量:32kb;(2)l2cache512kb(3)sharememory512k(4)tlb容量:64条目;(5)持浮点指令;(6)支持硬件一致性;(7)频率600m。21.ddr3接口模块:此芯片具有ddr3/ddr3l的控制器,并且内部集成了pub和phy,能够连接ddr3或者ddr3l的存储器。支持ddr3或者ddr3l的存储器,支持32位宽,最大支持2gb地址空间。22.此芯片中规划64mb的ddr空间为cpu0运行ucos-ii/freertos操作系统时存储堆栈的数据;同时为bd3基带规划128mb存储空间,用于基带信息处理时的数据缓存。外接512mb~2gb的存储器,建议型号为:mt41k128m16(256mb@16bit)、mt41k256m16(512mb@16bit)、mt41k512m16(1024mb@16bit)。23.高性能adc模块:为了提高系统集成度,增加系统可靠性和降低成本考虑,片上集成了10路高精度adc,由五个2通道adc构成。24.低速扩展接口:多模多频导航芯片的多种应用场景,要求其具备丰富的信息接口,以适应各种场景的应用需求。在芯片的设计中,主要包含以下接口:(1)usb接口;(2)i2c接口;(3)uart接口;(4)spi接口;(5)iccard;(6)可编程gpio接口。当前第1页12当前第1页12

技术领域:

:1.本发明属于卫星导航

技术领域:

:,具体地说,是涉及一种高精度多模多频北斗导航soc芯片。

背景技术:

::2.2019年北斗全球系统系统已全部部署完毕,标志着全球系统核心星座部署完成,将为全球用户提供性能优异的导航服务,以及全球短报文通信、国际搜救等特色服务,相较于北斗之前的系统系统,北斗全球系统有四方面的性能提升:一是更高的精度,北斗全球基本系统建成后,全球定位精度10米;在亚太地区定位精度,由原来的6米提升至5米;二是更强的原子钟,北斗卫星采用了更高性能的铷原子钟和氢原子钟,铷原子钟天稳定度为10-14量级,氢原子钟天稳定度为10-15量级。三是更新的技术,北斗卫星通过采用新的技术,空间信号精度优于0.5m。四是更优的信号,北斗卫星增加了性能更优的互操作信号b1c,同时,在全球系统中将b2i信号升级为性能更优的b2a信号。3.北斗全球系统更为优越的性能,未来需求将呈爆发式增长,无论军用、行业应用还是民用北斗设备都将在未来2-3年内更换为北斗全球系统装备。相比基于导航芯片实现的基带产品,传统的基于fpga实现的方案存在以下几个问题,一是成本居高不下,fpga本身的成本都在数百元,加上外部的ad器件等器件成本单个基带产品的成本至少在2000元以上,成本的居高不下限制了北斗产品的进一步推广,特别是单兵和弹载方面,需求量非常大,降低成本已是必然要求,本产品的顺利实施预期将单颗基带产品降低50%,极大促进基带芯片的推广应用;二是目前基于fpga的方案集成度不高,板卡体积无法做小,导致设备体积大,携带不变,单兵应用对产品的小型化和轻便化有着强烈的要求;三是基于fpga的功耗大,对于便携式设备,需要工作时间长,对降低功耗有着强烈的需求;四是fpga大多采用国外的产品实现,在自主、安全和可控方面对国产化芯片替代有着强烈要求。基于以上几点,设计低功耗、高集成度和高精度的北斗导航芯片是北斗产业发展的必然选择。4.目前国内主要的北斗芯片存在以下几个问题:1、只支持单一频点,不支持多模多频;2、芯片只支持基带功能,没有soc化;3、芯片定位精度不够,不支持厘米级定位。技术实现要素:5.为了解决上述现有技术存在的问题,本发明提出了一种高精度多模多频北斗导航soc芯片,在达到高精度的同时,支持bds的全部信号格式,包含民码和军码,包括b1i、b1c、b1a、b2a、b3i、b3q、b3a、b3ae,而且支持gps的l1c\a、l1c、l2c频点,gln的g1和geo和e10s频点,gln的g1和geo和e10s频点,做到多模多频兼容。6.本发明芯片由基带算法模块、高性能微处理器、高性能adc模块、ddr3接口模块和低速扩展接口等部分组成。7.基带算法模块包含:gnss跟踪模块、抗干扰模块、电文与伪距处理模块、时间同步与授时模块、低功耗长码直捕模块。8.高性能微处理器部分包含:双核mcu采用非对称架构,每个内核具有独享的外设,两个内核也有共享的外设。两个mcu处理器内核可以具有不同的主频。cpu1的所有外设均为可以为两个cpu访问,即是共享外设。cpu0的部分外设仅cpu0可访问,cpu1不可访问,处理器内核及浮点协处理器完成pvt解算,输出定位、测速结果,同时对用户提供一个开放的可编程处理器接口,可根据用户需求完成进一步的功能。9.为了提高系统集成度,增加系统可靠性和降低成本考虑,片上集成了10路高精度adc,由五个2通道adc构成。10.此芯片具有ddr3/ddr3l的控制器,并且内部集成了pub和phy,能够连接ddr3或者ddr3l的存储器。支持ddr3或者ddr3l的存储器,支持32位宽,最大支持2gb地址空间。此芯片中规划64mb的ddr空间为cpu0运行ucos-ii/freertos操作系统时存储堆栈的数据;同时为bd3基带规划128mb存储空间,用于基带信息处理时的数据缓存。外接512mb~2gb的存储器,建议型号为:mt41k128m16(256mb@16bit)、mt41k256m16(512mb@16bit)、mt41k512m16(1024mb@16bit)。11.此芯片具有一个dap(debugaccessport)-lite接口。包含以下组件:serialwirejtagdebugport(swj-dp)、advancedperipheralbusaccessport(apb_ap)、advancedperipheralbusmultiplexor(apb_mux)、readonlymemory(rom)table。12.本发明芯片的设计中,主要包含以下接口:usb接口、i2c接口、uart接口、spi接口、iccard、可编程gpio接口。13.与现有技术相比,本发明的优点和积极效果是:本发明在soc实现上,相比现有技术产品功能更为齐备,芯片处理能力更强,采用了mcu处理器,是目前所有导航芯片中处理器性能最为先进的,设计频率600m(最差条件),实测频率可达1ghz以上,同时本发明采用了ddr3和千兆以太网接口,适用于高性能系统要求,兼容性更好。本发明的功耗和集成度均明显优于现有技术,实现了soc芯片的小尺寸、低成本、高集成度设计。附图说明14.图1为本发明soc芯片架构图。具体实施方式15.下面结合附图对本发明的具体实施方式作进一步详细地说明。16.本发明芯片是一款面向北斗三号卫星导航系统应用的基于非对称架构双核mcu处理器的bd-iii基带soc,能够实现各导航频点中频信号的基带信息处理与信息处理,实现定位、测速、导航等功能。其内部包含基带算法模块、高性能微处理器、高性能adc模块、ddr3接口模块和低速扩展接口等主要功能模块,芯片实现采用40nmll工艺设计,采用高性能、低功耗、高可靠性设计方法,按照严格的sign-off标准执行,实现了高精度多模多频产品的小型化、低功耗、低成本设计。17.下面结合附图对soc芯片内部的主要功能模块进行具体阐述。18.基带算法模块包含:gnss跟踪模块、抗干扰模块、电文与伪距处理模块、时间同步与授时模块、低功耗长码直捕模块,这部分主要完成功能如下:(1)具有独立的gnss信号处理通道和独立的rdss信号处理通道;(2)gnss支持bd2-b1、b2、b3频点,gps-l1频点和glonass-l1频点信号的捕获、跟踪;(3)rdss支持信号定位、短报文和指挥功能,具有“单发双收”与“双收单发”两种定位模式,并能自动切换;(4)gnss具备单系统和多系统的pvt解算功能;(5)gnss可输出伪距、多普勒、电文等原始观测量;(6)b3频点和rdss信号具有窄带干扰抑制能力。19.高性能微处理器包含:双核mcu采用非对称架构,每个内核具有独享的外设,两个内核也有共享的外设。两个mcu处理器内核可以具有不同的主频。20.cpu1的所有外设均为可以为两个cpu访问,即是共享外设。cpu0的部分外设仅cpu0可访问,cpu1不可访问,处理器内核及浮点协处理器完成pvt解算,输出定位、测速结果,同时对用户提供一个开放的可编程处理器接口,可根据用户需求完成进一步的功能,主要性能指标如下:(1)icache、dcache容量:32kb;(2)l2cache512kb(3)sharememory512k(4)tlb容量:64条目;(5)持浮点指令;(6)支持硬件一致性;(7)频率600m。21.ddr3接口模块:此芯片具有ddr3/ddr3l的控制器,并且内部集成了pub和phy,能够连接ddr3或者ddr3l的存储器。支持ddr3或者ddr3l的存储器,支持32位宽,最大支持2gb地址空间。22.此芯片中规划64mb的ddr空间为cpu0运行ucos-ii/freertos操作系统时存储堆栈的数据;同时为bd3基带规划128mb存储空间,用于基带信息处理时的数据缓存。外接512mb~2gb的存储器,建议型号为:mt41k128m16(256mb@16bit)、mt41k256m16(512mb@16bit)、mt41k512m16(1024mb@16bit)。23.高性能adc模块:为了提高系统集成度,增加系统可靠性和降低成本考虑,片上集成了10路高精度adc,由五个2通道adc构成。24.低速扩展接口:多模多频导航芯片的多种应用场景,要求其具备丰富的信息接口,以适应各种场景的应用需求。在芯片的设计中,主要包含以下接口:(1)usb接口;(2)i2c接口;(3)uart接口;(4)spi接口;(5)iccard;(6)可编程gpio接口。当前第1页12当前第1页12

再多了解一些

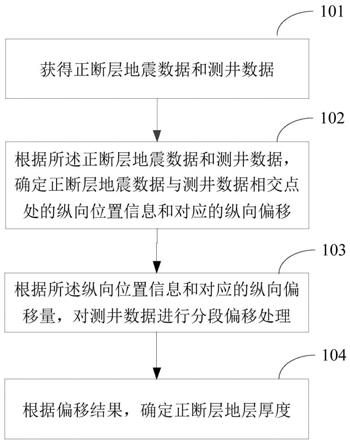

本文用于企业家、创业者技术爱好者查询,结果仅供参考。