soi横向匀场高压功率半导体器件及制造方法和应用

技术领域

1.本发明属于功率半导体领域,主要提出了一种soi横向匀场高压功率半导体器件及其制造方法和应用。

背景技术:

2.功率半导体器件由于具有输入阻抗高、开关速度快、损耗低、安全工作区宽等特性,已被广泛应用于计算机及外设、消费电子、网络通信,电子专用设备与汽车电子、仪器仪表、led显示屏以及电子照明等多个方面。横向器件由于源极、栅极、漏极都在同一表面,易于通过内部连接与其他器件及电路集成,被广泛运用于功率集成电路中。soi材料由于其具有泄漏电流小、无隔离阱形成寄生pn结电容、扛闩锁效应强、抗辐照性能好而广受应用,在高速、低功耗、抗辐照以及耐高温等领域有广泛应用,被誉为“21世纪硅集成技术”。

技术实现要素:

3.针对上述问题,本发明提出了一种soi横向匀场高压功率半导体器件及其制造方法,通过在器件关态引入全域mis耗尽机制,提高器件耐压。同时,在器件开态时,浮空场板表面能够形成积累层,降低比导通电阻,并提高饱和电流。该结构提高了器件电流密度,消除了snapback现象对器件输出特性的影响,提高器件的稳定性。

4.为实现上述发明目的,本发明技术方案如下:

5.具有一种soi横向匀场高压功率半导体器件,包括:

6.第一导电类型半导体衬底11、第一导电类型阱区12、第一导电类型源端重掺杂区13,第二导电类型漂移区21、第二导电类型阱区22、第二导电类型源端重掺杂区23,第二导电类型漏端重掺杂区24,第一介质氧化层31、第二介质氧化层32、第三介质氧化层33、埋氧层34、多晶硅电极41、控制栅多晶硅电极42、源极金属52,漏极金属53;

7.其中,埋氧层34位于第一导电类型半导体衬底11上方,第二导电类型漂移区21位于埋氧层34上方,第一导电类型阱区12位于第二导电类型漂移区21的左侧,第一导电类型源端重掺杂区13和第二导电类型源端重掺杂区23位于第一导电类型阱区12中,第二导电类型阱区22位于第二导电类型漂移区21的右侧,第二导电类型漏端重掺杂区24位于第二导电类型阱区22中;第二介质氧化层32位于第一导电类型阱区12上方,并且其左端与第二导电类型源端重掺杂区23相接触,右端与第二导电类型漂移区21相接触;第三介质氧化层33位于第二介质氧化层32与第二导电类型漏端重掺杂区24之间的第二导电类型漂移区21的上表面;控制栅多晶硅电极42覆盖在第二介质氧化层32的上表面并部分延伸至第三介质氧化层33的上表面;

8.第一介质氧化层31和多晶硅电极41构成纵向延伸的纵向浮空场板,纵向浮空场板的个数为1个到多个;源漏方向上相邻的纵向浮空场板错开排布;纵向浮空场板周期性的分布在整个第二导电类型漂移区21中,形成具有多个等势浮空槽的耐压层,同时等势浮空槽与埋氧层34相连接,多晶硅电极41插入埋氧层34内,但不穿通埋氧层34;相邻纵向浮空场板

的纵向间距和横向间距相等,横向为源漏方向,纵向为垂直于源漏方向。

9.作为优选方式,纵向浮空场板的截面形状是矩形、或圆形、或椭圆形、或六边形。

10.作为优选方式,在第二导电类型漂移区21的表面引入电场钳位层14,即ptop层。

11.作为优选方式,器件改为ligbt器件,或pldmos器件。

12.作为优选方式,在源端下方去除一部分埋氧层;或者/并且在漏端下方去除一部分埋氧层。

13.作为优选方式,埋氧层34的厚度根据所需耐压等级决定。

14.作为优选方式,所述的所有介质氧化层通过热生长形成,或通过淀积并刻蚀形成。

15.本发明还提供一种所述的一种soi横向匀场高压功率半导体器件的制造方法,包括如下步骤:

16.步骤1:选择soi外延片;

17.步骤2:在soi外延片注入推结得到第二导电类型漂移区21;

18.步骤3:通过光刻以及刻蚀挖穿埋氧层形成槽;

19.步骤4:在槽壁形成第一介质氧化层,淀积多晶并刻蚀至硅平面;

20.步骤5:通过离子注入第二导电类型杂质并推结,形成第二导电类型阱区22;

21.步骤6:热氧化形成第二介质氧化层32,并淀积刻蚀形成第三介质氧化层33;

22.步骤7:通过离子注入第一导电类型杂质并推结,形成第一导电类型阱区12;

23.步骤8:淀积多晶硅并刻蚀,形成控制栅多晶硅电极42;

24.步骤9:注入激活形成第一导电类型源端重掺杂区13,第二导电类型源端重掺杂区23与第二导电类型漏端重掺杂区24。

25.作为优选方式,所述制造方法进一步为:步骤2中通过注入并推结形成的第二导电类型漂移区21通过外延的方法得到;并且/或者步骤6中通过注入并推结而得到的第一导电类型阱区12与第二导电类型阱区22,通过多次不同能量的注入并激活来形成。

26.作为优选方式,所述制造方法进一步为:在工艺步骤3中,槽挖穿埋氧层到达衬底,利用纵向场板对衬底进行辅助耗尽。

27.作为优选方式,所述制造方法进一步为:步骤2中第二导电类型漂移区21采用了热推阱的工艺,其浓度分布为余误差分布。

28.本发明还提供一种所述的一种soi横向匀场高压功率半导体器件的制造方法,在制备sic、gan宽禁带半导体中的应用。

29.本发明的有益效果为:器件的第二导电类型漂移区21中引入由第一介质氧化层31和多晶硅电极41构成的介质层相连的纵向浮空场板结构,由于硅的介电系数是二氧化硅的三倍,在相同漂移区长度下,介质层能够取得更大的电场,提高击穿电压。本发明在器件开态时,纵向浮空场板表面能够形成积累层,提高了器件的饱和电流。同时电极深入介质层,电极自适应在氧化层内部产生电荷,增加介质电场,实现endif效果,提高器件的击穿电压。同时,由于纵向场板结构的存在,减缓了横向电场对反型层电荷的抽取,反型层电荷被束缚在槽内,增强埋氧层的电场,提高器件的耐压。同时该器件由于mis结构的辅助耗尽作用,在较厚的漂移区厚度下,漂移区浓度仍然可以做的很高,解决soi衬底耗尽不足漂移区浓度淡的问题。是一个具备可量产化的endif soi器件。

附图说明

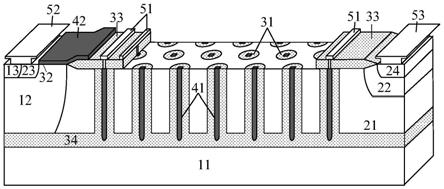

30.图1为实施例1的一种soi横向匀场高压功率半导体器件结构示意图;

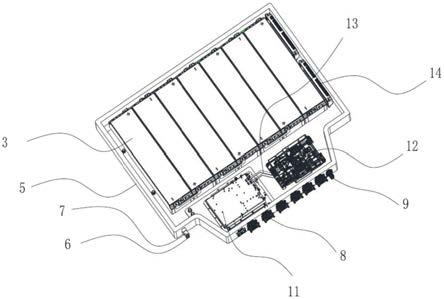

31.图2为实施例2的一种soi横向匀场高压功率半导体器件结构示意图;

32.图3为实施例3的一种soi横向匀场高压功率半导体器件结构示意图;

33.图4为实施例4的一种soi横向匀场高压功率半导体器件结构示意图;

34.图5为实施例5的一种soi横向匀场高压功率半导体器件结构示意图;

35.图6为实施例6的一种soi横向匀场高压功率半导体器件结构示意图;

36.图7为实施例7的一种soi横向匀场高压功率半导体器件结构示意图;

37.图8为实施例8的一种soi横向匀场高压功率半导体器件结构示意图;

38.图9(a)

‑

图9(i)为实施例1所述器件的工艺流程示意图。

39.图10为纵向场板电极是否插入埋氧层的等势线比较图。

40.图11为纵向场板电极是否插入埋氧层的漏端电场比较图。

41.11为第一导电类型半导体衬底,12为第一导电类型阱区,13为第一导电类型源端重掺杂区,14为电场钳位层,21为第二导电类型漂移区,22为第二导电类型阱区,23为第二导电类型源端重掺杂区,24为第二导电类型漏端重掺杂区,31为第一介质氧化层,32为第二介质氧化层,33为第三介质氧化层,34为埋氧层,41为多晶硅电极,42为控制栅多晶硅电极,51为纵向场板的表面金属,52为源极金属,53为漏极金属。

具体实施方式

42.以下通过特定的具体实例说明本发明的实施方式,本领域技术人员可由本说明书所揭露的内容轻易地了解本发明的其他优点与功效。本发明还可以通过另外不同的具体实施方式加以实施或应用,本说明书中的各项细节也可以基于不同观点与应用,在没有背离本发明的精神下进行各种修饰或改变。

43.图10和图11是电极是否插入埋氧层的仿真性能比较。图10给出了纵向场板电极是否插入埋氧层的两种情况下,两个器件的等势线分布情况,可以看到,电极插入埋氧层中,等势线被限制在埋氧层内。而图11给出了沿着漏端纵向画一条线的电场的分布图,在漏电极,也可以明显的发现,电极插入埋氧层中,埋氧层的电场峰值明显更高,是电极插入埋氧层器件的三倍,因此,电极插入埋氧层中的器件可以实现endif效果。

44.实施例1

45.实施例1所述的一种soi横向匀场高压功率半导体器件,如图1所示,具体包括:

46.第一导电类型半导体衬底11、第一导电类型阱区12、第一导电类型源端重掺杂区13,第二导电类型漂移区21、第二导电类型阱区22、第二导电类型源端重掺杂区23,第二导电类型漏端重掺杂区24,第一介质氧化层31、第二介质氧化层32、第三介质氧化层33、埋氧层34、多晶硅电极41、控制栅多晶硅电极42、源极金属52,漏极金属53;

47.其中,埋氧层34位于第一导电类型半导体衬底11上方,第二导电类型漂移区21位于埋氧层34上方,第一导电类型阱区12位于第二导电类型漂移区21的左侧,第一导电类型源端重掺杂区13和第二导电类型源端重掺杂区23位于第一导电类型阱区12中,第二导电类型阱区22位于第二导电类型漂移区21的右侧,第二导电类型漏端重掺杂区24位于第二导电类型阱区22中;第二介质氧化层32位于第一导电类型阱区12上方,并且其左端与第二导电

类型源端重掺杂区23相接触,右端与第二导电类型漂移区21相接触;第三介质氧化层33位于第二介质氧化层32与第二导电类型漏端重掺杂区24之间的第二导电类型漂移区21的上表面;控制栅多晶硅电极42覆盖在第二介质氧化层32的上表面并部分延伸至第三介质氧化层33的上表面;

48.第一介质氧化层31和多晶硅电极41构成纵向延伸的纵向浮空场板,纵向浮空场板的个数为1个到多个;源漏方向上相邻的纵向浮空场板错开排布;纵向浮空场板周期性的分布在整个第二导电类型漂移区21中,形成具有多个等势浮空槽的耐压层,同时等势浮空槽与埋氧层34相连接,多晶硅电极41插入埋氧层34内,但不穿通埋氧层34;相邻纵向浮空场板的纵向间距和横向间距相等,横向为源漏方向,纵向为垂直于源漏方向。

49.纵向浮空场板的截面形状是矩形、或圆形、或椭圆形、或六边形。

50.该器件也可以是igbt或者pmos器件。

51.埋氧层34的厚度根据所需耐压等级决定。

52.本实施例的基本工作原理如下:以第一导电类型半导体材料为p型为例,在不加栅压的情况下,第二导电类型漂移区21与第一导电类型阱区12构成的pn结在反向电压v

d

作用下开始耗尽,同时第一导电类型半导体衬底11与第二导电类型漂移区21构成的pn结也在漏压下开始耗尽。同时,纵向场板中的浮空电极对漂移区有辅助耗尽的作用,使得表面电场分布均匀,其中击穿电压大部分由介质层承担,由于二氧化硅介电系数小于硅的介电系数,器件耐压大大提高,提高了器件的击穿电压。当栅极偏置电压v

g

大于阈值电压时,第一导电类型阱区12靠近第二介质氧化层32的表面出现反型层电子,从而使得源漏导通。由于纵向场板结构的存在,减缓了横向电场对反型层电荷的抽取,反型层电荷被束缚在槽内,增强埋氧层的电场,提高器件的耐压。同时该器件由于mis结构的辅助耗尽作用,在较厚的漂移区厚度下,漂移区浓度仍然可以做的很高,解决soi衬底耗尽不足漂移区浓度淡的问题。综上所述,本发明所提出的具有电场钳位层的匀场器件较常规具有更高的击穿电压和更低的比导通电阻。

53.图7为一种soi横向匀场高压功率半导体器件及其制造方法,包括如下步骤:

54.步骤1:选择soi外延片;

55.步骤2:在soi外延片注入推结得到第二导电类型漂移区21;

56.步骤3:通过光刻以及刻蚀挖穿埋氧层形成深槽;

57.步骤4:在槽壁形成第一介质氧化层,淀积多晶并刻蚀至硅平面;

58.步骤5:通过高能离子注入第二导电类型杂质并推结,形成第二导电类型阱区22;

59.步骤6:热氧化形成第二介质氧化层32,并淀积刻蚀形成第三介质氧化层33;

60.步骤7:通过离子注入第一导电类型杂质并推结,形成第一导电类型阱区12;

61.步骤8:淀积多晶硅并刻蚀,形成控制栅多晶硅电极42;

62.步骤9:注入激活重掺杂形成第一导电类型源端重掺杂区13,第二导电类型源端重掺杂区23与第二导电类型漏端重掺杂区24;

63.本工艺适用于sic、gan等宽禁带半导体和其他类型半导体。

64.优选的,所述的所有介质氧化层通过热生长形成,或通过淀积并刻蚀形成。

65.优选的,步骤2中通过注入并推结形成的第二导电类型漂移区21通过外延的方法得到;并且/或者步骤6中通过注入并推结而得到的第一导电类型阱区12与第二导电类型阱

区22,通过多次不同能量的注入并激活来形成。

66.实施例2

67.如图2所示,为实施例2的一种soi横向匀场高压功率半导体器件结构示意图,本例与实施例1的结构不同之处在于,在第二导电类型漂移区21的表面引入电场钳位层14,即ptop层。ptop层的引入带来了双电荷自平衡,mis电极高电位辅助耗尽p型杂质,低电位辅助耗尽n型杂质,同时p型杂质和n型杂质之间可以相互耗尽,因此可以大大增大漂移区浓度,从而降低比导通电阻。同时,ptop层保证了耗尽的连续性,具有钳位表面电场的作用,使得在很宽的漂移区浓度内保持高的击穿电压,具有高容差性。工艺上和第一导电类型阱区采用同一张版,利用场氧化层的阻挡作用,高能注入形成,不需要额外的版次。在终端处不注入ptop层以保证不引入额外的pn结,导致源端提前击穿,在过渡区ptop和pwell连接在一起,防止由于漂移区浓度过大导致其提前击穿。其工作原理与实施例1相同。

68.实施例3

69.如图3所示,为实施例3的一种soi横向匀场高压功率半导体器件结构示意图,本例与实施例1的结构不同之处在于,把器件改为了ligbt。由于纵向场板在开态和关态的状态下都能够辅助耗尽,因此可以大大该结构可以大大降低比导通电阻。

70.实施例4

71.如图4所示,为实施例4的一种soi横向匀场高压功率半导体器件结构示意图,本例与实施例1的结构不同之处在于,把器件改成了pldmos器件。由于pldmos器件没有resurf效果,导致其应用范围有限。而该器件由于纵向场板既可以辅助耗尽n型杂质也可以辅助p型杂质,因此,可以把p外延层的浓度做的很高,提高应用范围。

72.实施例5

73.如图5所示,为实施例5的一种soi横向匀场高压功率半导体器件结构示意图,本例与实施例1的结构不同之处在于,在源端下方去除一部分埋氧层,这样在维持原有效果的同时,可以增大其散热性。其工作原理与实施例1相同。

74.实施例6

75.如图6所示,为实施例6的一种soi横向匀场高压功率半导体器件结构示意图,本例与实施例1的结构不同之处在于,在漏端下方去除一部分埋氧层,可以使得衬底也参与一部分耐压,综合了体硅和soi的特点,降低了器件的自热效应。其工作原理与实施例1相同。

76.实施例7

77.如图7所示,为实施例7的一种soi横向匀场高压功率半导体器件结构示意图,本例与实施例1的结构不同之处在于,在工艺步骤3中,槽挖穿埋氧层到达衬底,利用纵向场板对衬底进行辅助耗尽。其工作原理与实施例1相同。

78.实施例8

79.如图8所示,为实施例8的一种soi横向匀场高压功率半导体器件结构示意图,本例与实施例1的结构不同之处在于,步骤2中第二导电类型漂移区21采用了热推阱的工艺,其浓度分布为余误差分布,可以做厚外延层,更适合高压器件。其工作原理与实施例1相同。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。