图形处理中的通用寄存器和波槽分配

1.本专利申请要求享受2019年3月26日提交的、标题为“general purpose register and wave slot allocation in graphics processing”的美国非临时申请no.16/364,829的优先权,该申请已经转让给本技术的受让人,故以引用方式将其明确地并入本文。

背景技术:

2.图形处理单元(gpu)越来越多地用于不同类型的设备,这些设备包括诸如智能手机、虚拟现实(vr)设备、增强现实(ar)设备、平板计算机、智能手表等等之类的移动设备。许多gpu利用可以内置到gpu中的流处理器(sp)。gpu中的流处理器可以处理大多数传统的图形渲染任务,和/或可以被编程以进行更通用的数字处理。流处理器非常适合传统的以gpu为中心的任务(例如,图形、图像、视频和信号处理),也适用于光线追踪、计算流体动力学、天气建模等等。

3.作为生成图形内容的一部分,gpu和/或流处理器可以执行纹理映射,纹理映射可以是用于定义在场景中渲染的图形或三维(3d)模型上的高频细节、表面纹理或颜色信息的过程。特别是,流处理器可以非常适合于纹理映射任务。但是,与流处理器以及许多其它硬件组件相关联的约束,是可供使用的存储器、寄存器、执行单元的波槽等等的总量。

技术实现要素:

4.本文所描述的系统、方法和设备均具有一些方面,这些方面中没有任何单一方面单独地对其期望特性起作用。在不限制本公开内容的保护范围的情况下,现在将简要地描述一些非限制性特征。

5.本文描述了用于生成图形内容的方法、设备、装置和计算机可读介质。一种方法可以包括:获取与纹理操作相对应的纹理操作指令;响应于确定可用于所述纹理操作的不足的通用寄存器空间、或者可用于所述纹理操作的不足的波槽中的至少一项,生成关于所述纹理操作对应于延迟波的指示;执行所述纹理操作;向纹理处理器发送与被执行的所述纹理操作相对应的初始纹理采样指令;并接收与所述初始纹理采样指令相对应的经纹理映射数据。

6.在一些实施例中,该方法还可以包括:生成与所述纹理操作相对应的虚拟波槽。

7.在另外的实施例中,该方法还可以包括:在确定可用于所述纹理操作的不足的通用寄存器空间、或者可用于所述纹理操作的不足的波槽中的至少一项之后,确定足够的通用寄存器空间可用于所述纹理操作并且足够的波槽可用于所述纹理操作;将所述虚拟波槽转换为波槽;并将与所述纹理操作相对应的纹理属性存储在所述通用寄存器中。

8.在另外的实施例中,该方法可以包括:在转换所述虚拟波槽和存储所述纹理属性之后,使用所述波槽和所述纹理属性,对所述纹理映射数据执行后处理。

9.在一些实施例中,该方法可以包括:使用像素内插单元来执行所述纹理操作。

10.在另外的实施例中,该方法可以包括:向处理器的下游组件发送与所述纹理映射数据相对应的数据,其中所述数据还对应于输出到显示器的内容的帧。

11.在另外的实施例中,该方法可以包括:重复地判断是否有足够的通用寄存器空间和波槽可用于所述纹理操作;并在确定足够的通用寄存器空间可用于所述纹理操作并且足够的波槽可用于所述纹理操作时,执行以下操作:将所述虚拟波槽转换为波槽;将与所述纹理操作相对应的纹理属性存储在所述通用寄存器中。

12.在一些实施例中,该方法可以包括:获取与第二纹理操作相对应的第二纹理操作指令;确定可用于所述第二纹理操作的不足的通用寄存器空间、或者可用于所述第二纹理操作的不足的波槽中的至少一项;确定所述第二纹理操作需要缓冲存储空间和波槽;将与所述第二纹理操作相对应的虚拟波槽存储在所述纹理缓冲器中;并将与所述第二纹理操作相对应的纹理属性存储在所述纹理缓冲器中。

13.一种设备可以包括存储器和耦合到所述存储器的处理器,其被配置为使所述设备执行包括以下操作的方法:获取与纹理操作相对应的纹理操作指令;响应于确定可用于所述纹理操作的不足的通用寄存器空间、或者可用于所述纹理操作的不足的波槽中的至少一项,生成关于所述纹理操作对应于延迟波的指示;执行所述纹理操作;向纹理处理器发送与被执行的所述纹理操作相对应的初始纹理采样指令;并接收与所述初始纹理采样指令相对应的经纹理映射数据。

14.在一些实施例中,所述设备可以包括显示器和/或所述存储器可以包括纹理缓冲器。

15.在另外的实施例中,所述设备可以是无线通信设备。

16.一种计算机可读介质可以是非暂时性计算机可读介质,所述非暂时性计算机可读介质存储包含指令的程序,当所述指令被设备的处理器执行时,使所述设备执行包括以下操作的方法:获取与纹理操作相对应的纹理操作指令;响应于确定可用于所述纹理操作的不足的通用寄存器空间、或者可用于所述纹理操作的不足的波槽中的至少一项,生成关于所述纹理操作对应于延迟波的指示;执行所述纹理操作;向纹理处理器发送与被执行的所述纹理操作相对应的初始纹理采样指令;并接收与所述初始纹理采样指令相对应的经纹理映射数据。

17.一种装置可以包括:用于获取与纹理操作相对应的纹理操作指令的单元;用于响应于确定可用于所述纹理操作的不足的通用寄存器空间、或者可用于所述纹理操作的不足的波槽中的至少一项,生成关于所述纹理操作对应于延迟波的指示的单元;用于执行所述纹理操作的单元;用于向纹理处理器发送与被执行的所述纹理操作相对应的初始纹理采样指令的单元;以及用于接收与所述初始纹理采样指令相对应的经纹理映射数据的单元。

附图说明

18.提供以下附图和相关描述以说明本公开内容的实施例,并且不限制权利要求的保护范围。当结合附图进行考虑时,由于参照下面的具体实施方式,能更好地完整理解本公开内容的各方面,因此将容易地理解本公开内容的各方面以及其多个附带优点,其中:

19.图1示出了与所公开的实施例一致的包括流处理器和纹理处理器的示例设备。

20.图2示出了与所公开的实施例一致的包括流处理器和纹理处理器的示例设备。

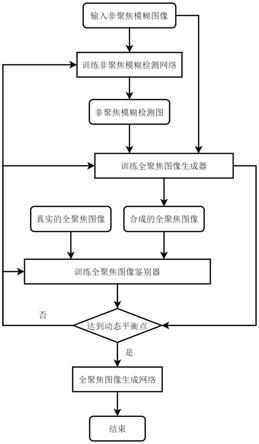

21.图3是与所公开的实施例一致的用于在流处理器上分配通用寄存器空间和波槽的示例过程的流程图。

22.图4是与所公开的实施例一致的用于在流处理器上分配通用寄存器空间和波槽的示例过程的流程图。

23.图5是与所公开的实施例一致的用于将虚拟波槽异步转换为物理波槽的示例过程的流程图。

24.图6是示出与所公开的实施例一致的具有包括至少一个流处理器的图形处理器的示例设备的框图。

具体实施方式

25.尽管本文描述了特定的实施例,但是其它实施例对于本领域普通技术人员来说将是显而易见的,这些其它实施例包括没有提供本文所阐述的所有益处和特征的实施例。

26.本说明书描述了多线程流处理器(例如,也称为流处理器),其可以是图形处理器,或者可以包括在图形处理器(例如,gpu)中。本说明书进一步描述了将通用寄存器(一组通用寄存器,以下简称gpr)和执行单元的物理波槽高效分配给流处理器正在执行的线程。在本说明书中,流处理器可以被配置为获取和调度与线程相关联的指令的执行,并且可以包括或访问一组寄存器(例如,gpr)。gpr可以包括能够存储(例如,临时地存储)与指令的执行相关联的数据的一个或多个寄存器(例如,通用寄存器块、通用寄存器空间、通用寄存器印记等),并且gpr可以是易失性或非易失性存储器。此外,流处理器可以包括用于执行计算的一个或多个执行单元(例如,算术逻辑单元(alu))、与存储器操作相关联的一个或多个单元等等。

27.流处理器可以执行多个线程。在一些情况下,可以根据特定代码(例如,指令)将这些线程组合在一起,并且可以并行地执行组合的线程。例如,一组线程(例如,翘曲(warp)、波前、波等,以下称为波)可以包括特定数量的线程,每个线程重复地执行相同的代码部分,例如着色器(如,与以特定、独特的方式渲染图像相关联的指令)或内核(例如,计算内核)。流处理器可以并行地执行(1)多个线程和/或(2)多个线程组,并且可以在任何情况下应用本文所描述的技术。举一个例子,流处理器可以执行多组线程,每组线程对应于代码的相应部分的执行。例如,流处理器可以在线程组之间进行交替,从而可以执行每一个组。再举一个例子,流处理器可以执行多个线程,每个线程对应于相应的代码部分的执行。为了方便起见,本说明书将线程称为特定线程或一组线程,两者都与特定的代码部分的执行相关联。

28.在流处理器中,纹理操作可能具有相对较长的延迟。延迟可能是图形处理器性能的一个重要方面。可以通过在gpu上执行更多线程来缓解这种延迟,使得一些线程可以执行alu操作,而其它线程正在等待纹理操作完成。这可以称为“延迟隐藏”。例如,为了增加延迟隐藏,可以在图形处理器上包含更多存储器。然而,包括另外的存储器(例如,增加存储器的大小)通常会增加成本。例如,gpr可以为并行执行的不同线程存储数据。可以增加gpr大小以提高执行线程的延迟隐藏能力。但是,gpr可以是多端口随机存取存储器(ram),它比单端口ram更昂贵并且使用更多的物理空间(例如,单端口ram的比特面积的三到四倍)。因此,增加gpr大小的成本可能很高。

29.此外,波槽可以是流处理器用来调度执行单元(例如,alu)的工作的物理存储。“wave(波)”可以代表执行单元的最小调度工作单元,并且可以包括多个线程(例如,64个线程)。与gpr大小类似,可以增加物理波槽的数量以改善执行线程时的延迟隐藏。然而,增加

物理波槽的数量的成本同样很高。因此,可以通过更高效地利用可用的物理波槽和gpr来改进gpu技术。

30.本公开内容的各方面涉及gpr空间和物理波槽的高效分配。

31.通常,流处理器通过以下方式来处理纹理操作:分配物理波槽,以便执行单元执行与纹理操作相对应的波;并分配gpr空间来存储纹理属性。执行单元可以按顺序处理物理波槽,和/或在等待存储器操作完成时暂停波。当执行单元被调度时,执行单元可以访问存储的纹理属性来处理纹理操作波,执行单元可以确定纹理坐标,然后可以将纹理坐标存储在gpr中,并且执行单元可以确定纹理请求,其中纹理请求可以发送到纹理加载单元。基于纹理请求,纹理加载单元可以从gpr中检索纹理坐标,并将纹理采样指令发送到纹理处理器。基于纹理采样指令,纹理处理器可以执行例如纹理映射和纹理滤波,并将经纹理映射的数据输出到纹理加载单元。然后,纹理加载单元可以将经纹理映射的数据写入gpr,随后可以将其用于后处理。

32.如上所述,流处理器在向纹理处理器发送纹理采样指令之前,分配物理波槽和gpr空间。然而,对于一些纹理操作,流处理器可能能够在向纹理处理器发送纹理采样指令之前,在不使用执行单元的情况下进行操作。

33.例如,对于一些纹理操作,流处理器(和/或像素内插单元(pi))可以生成初始纹理采样指令,并将其发送到纹理处理器,而不使用执行单元。因为在该阶段不使用执行单元,所以流处理器可以在不初始分配物理波槽和/或gpr空间的情况下执行纹理操作。在后续的时间(例如,在从纹理处理器接收到经滤波和纹理映射的数据之后),流处理器可以分配物理波槽和gpr空间以用于存储返回数据(例如,用于后处理操作)。因此,通过最初不为这种纹理操作分配物理波槽和gpr空间,更多的物理波槽和gpr空间可用于其它操作,并且流处理器可以不必等到有空间可用于执行纹理操作。因此,可以增加流处理器的吞吐量。

34.在另一个实施例中,即使是更复杂的纹理操作,纹理缓冲器也可以用于增加纹理处理延迟隐藏的量。纹理缓冲器可以是一种类型的存储器(例如,单端口ram),与另外的物理波槽和/或gpr空间相比,将该类型的存储器添加到流处理器的成本更低。例如,在更复杂的纹理操作中,当物理波槽和/或gpr空间已满时,流处理器可以使用存储在纹理缓冲器中的虚拟波槽,而不是物理波槽,并进一步使用纹理缓冲器来存储纹理属性,直到物理波槽和gpr空间变得可用为止。通过在纹理缓冲器中存储虚拟波槽和纹理属性,流处理器可以继续发出初始纹理采样指令(例如,对于不使用执行单元的简单操作),而不是等待物理波槽和gpr空间来用于更复杂的纹理操作。

35.应当理解,在一些情况下,纹理操作可以对应于一个以上的波,并且因此与一个以上的物理或虚拟波槽相关联。但是,为了简明起见,以下描述可以指代物理或虚拟波槽(即,用单数),但在适当的情况下,相同或相似的过程可以应用于与所公开的实施例相一致的一个以上的物理或虚拟波槽。因此,对单个物理或虚拟波槽的提及并非旨在进行限制。

36.关于纹理操作来说明了本文所描述的实施例,然而,在其它实施例中,本文所描述的技术也可以用于其它操作,例如检索颜色信息或执行通用计算任务。因此,以下与纹理映射操作相关的描述只是用于说明目的,而不是为了限制。

37.图1示出了与所公开的实施例一致的包括流处理器110和纹理处理器170的示例设备100。如图1中所示,流处理器110包括定序器130、波队列140、执行单元145、gpr 150、像素

内插单元160、多路复用器165和纹理加载单元180。流处理器110可以接收输入120,并且可以发送输出190。流处理器110还可以向纹理处理器170发送,并从纹理处理器170进行接收。

38.图1中的设备100描绘的组件仅仅用于说明目的,而并非旨在进行限制。例如,设备100、流处理器110和/或纹理处理器170可以包括更少的组件或者图1中没有示出的其它组件。例如,设备100可以包括gpu管道的其它组件,以及其它处理器、存储器和其它类型的计算机组件。流处理器110可以包括其它组件例如指令高速缓存、上下文寄存器、本地存储器、时钟组件、电源组件、调度器、高层级任务管理器等等,并且能够与其它组件例如高层级定序器、存储器、其它gpu组件、其它处理器等等)进行通信。

39.在一些实施例中,流处理器110的输入120可以包括操作的属性和/或描述操作(例如,纹理操作)的分组。例如,可以从高层级定序器、流处理器110的高层级任务管理器、另一个gpu组件和/或另一个流处理器110组件接收输入120,并且输入120可以是指令和/或纹理属性(其包括例如i/j重心系数数据)。

40.在另外的实施例中,定序器130可以是能够接收输入120、分配波槽、分配gpr空间和利用像素内插单元160的任何类型的组件。例如,定序器130可以接收输入120,可以生成虚拟波槽,可以分配物理波槽,可以分配gpr空间,和/或可以推迟为某些操作分配gpr空间,如下面进一步详细描述的。

41.在另外的实施例中,波队列140可以是具有多个槽的存储组件,以用于调度执行单元145的工作。在一些实现中,波队列140可以具有一组可用的物理波槽,以用于流处理器110的调度操作。因此,如果所有物理波槽都被分配,则在物理波槽变得可用之前,无法继续执行需要物理波槽的其它操作。

42.在另外的实施例中,执行单元145可以是任何类型的一个或多个处理组件和电路。例如,执行单元145可以包括一个或多个alu、浮点单元、地址生成单元、加载存储单元、分支执行单元、寄存器等等。执行单元145可以按顺序执行与波队列140的物理波槽相对应的操作,和/或在等待供波完成的一个或多个先决操作(例如,存储器操作、加载纹理数据等等)时暂停波。在一些实现中,执行单元145可以从gpr 150读取数据和向gpr150写入数据。在进一步的实现中,执行单元145可以向纹理加载单元180发送纹理请求。

43.在一些实施例中,gpr 150可以是存储组件,其能够用于存储用于流处理器110的数据,例如,纹理属性(如,u/v坐标或i/j系数数据)。在一些实现中,gpr 150可以从定序器130接收纹理属性(例如,i/j系数数据),从执行单元145接收纹理属性(例如,u/v坐标)和/或从纹理加载单元180接收纹理属性。在另外的实现中,gpr 150可以向执行单元145和/或纹理加载单元180提供纹理属性。

44.在另外的实施例中,像素内插单元160可以是能够向纹理处理器170发出初始纹理采样指令的任何类型的组件。在一些实现中,像素内插单元160可以是定序器130的一部分,同时,在其它实现中,像素内插单元160可以是单独的组件。如本文所使用的,在一些例子中,初始纹理采样指令可以指代像素内插单元(例如,简单着色器操作)生成的指令和/或在不使用流处理器的执行单元的情况下生成的指令。初始纹理采样指令可以包括使纹理处理器执行例如纹理映射和滤波的指令。

45.在另外的实施例中,多路复用器165可以是能够将两个信号组合成一个信号的任何类型的组件(例如,将来自像素内插单元160和纹理加载180的纹理采样指令组合成去往

纹理处理器170的一个信号)。

46.在一些实施例中,纹理处理器170可以是进行以下操作的组件:接收初始纹理采样指令和纹理采样指令、执行纹理映射、执行纹理滤波和/或将纹理映射数据返回到纹理加载单元180。

47.在另外的实施例中,纹理加载单元180可以是从执行单元145接收纹理请求、从gpr 150检索纹理属性、确定纹理采样指令(例如,基于纹理请求和纹理属性)、向纹理处理器170发送纹理采样指令、从纹理处理器170接收经纹理映射数据、并输出(例如,输出190)经纹理映射数据(例如,输出到另一个组件,输出到gpr 150等)的组件。如本文所使用的,在一些例子中,纹理采样指令可以指代使用由流处理器的执行单元处理的数据所生成的指令。纹理采样指令可以包括使纹理处理器执行例如纹理映射和滤波的指令。

48.在另外的实施例中,输出190可以是来自流处理器110、纹理加载单元180、gpr 150和/或流处理器110的另一个组件的输出。例如,输出190可以包括经纹理映射数据。在一些实施例中,输出190可以是用于后处理操作的经纹理映射数据。在另外的实施例中,可以在流处理器110内执行后处理操作,并且输出190可以是推送到gpu管道中的下游组件的经后处理的经纹理映射数据。

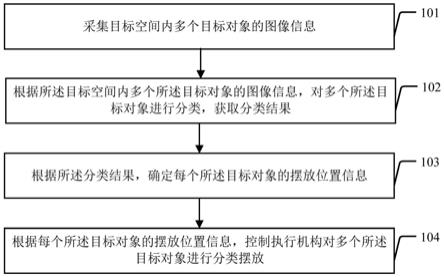

49.图2示出了与所公开的实施例一致的包括流处理器210和纹理处理器270的示例设备200。如图2中所示,流处理器210包括定序器230、波队列240、执行单元245、gpr 250、像素内插单元260、多路复用器265、纹理加载单元280和纹理缓冲器285。流处理器210可以接收输入220,并且可以发送输出290。流处理器210还可以向纹理处理器270发送,并从纹理处理器270进行接收。

50.图2中的设备200描述的组件仅仅用于说明目的,而并非旨在进行限制。例如,设备200、流处理器210和/或纹理处理器270可以包括更少的组件或者图2中没有示出的其它组件。例如,设备200可以包括gpu管道的其它组件,以及其它处理器、存储器和其它类型的计算机组件。流处理器210可以包括其它组件(例如,指令高速缓存、上下文寄存器、本地存储器、时钟组件、电源组件、调度器、高层级任务管理器等等),并且能够与其它组件(例如,高层级定序器、存储器、其它gpu组件、其它处理器等等)进行通信。

51.在一些实施例中,流处理器210的输入220可以包括操作的属性和/或描述操作(例如,纹理操作)的分组。例如,可以从高层级定序器、流处理器210的高层级任务管理器、另一个gpu组件和/或另一个流处理器210组件接收输入220,并且输入220可以是指令和/或纹理属性(其包括例如i/j重心系数数据)。

52.在另外的实施例中,定序器230可以是能够接收输入220、分配波槽、分配gpr空间、利用像素内插单元260、并将数据(例如,虚拟波槽数据)存储到纹理缓冲器285的任何类型的组件。例如,定序器230可以接收输入220,可以生成虚拟波槽,可以在纹理缓冲器285中存储用于虚拟波槽的数据(例如,如果没有可用的物理波槽的话),可以分配物理波槽,可以分配gpr空间,和/或可以推迟为某些操作分配gpr空间和物理波槽,如下面进一步详细描述的。

53.在另外的实施例中,波队列240可以是具有多个槽的存储组件,以用于调度执行单元245的工作。

54.在另外的实施例中,执行单元245可以是任何类型的一个或多个处理组件和电路。

例如,执行单元245可以包括一个或多个alu、浮点单元、地址生成单元、加载存储单元、分支执行单元、寄存器等等。执行单元245可以按顺序执行与波队列240的物理波槽相对应的操作,和/或在等待供波完成的一个或多个先决操作(例如,存储器操作、加载纹理数据等等)时暂停波。在一些实现中,执行单元245可以从gpr 250读取数据和向gpr250写入数据。在进一步的实现中,执行单元245可以向纹理加载单元280发送纹理请求。

55.在一些实施例中,gpr 250可以是存储组件,其能够用于存储用于流处理器210的数据,例如,纹理属性(如,u/v坐标或i/j系数数据)。在一些实现中,gpr 250可以从定序器230、执行单元245和/或从纹理加载单元280接收纹理属性。在另外的实现中,gpr 250可以向执行单元245和/或纹理加载单元280提供纹理属性。

56.在另外的实施例中,像素内插单元260可以是能够向纹理处理器179发出初始纹理采样的任何类型的组件。在一些实现中,像素内插单元260可以是定序器230的一部分,同时,在其它实现中,像素内插单元260可以是单独的组件。

57.在另外的实施例中,多路复用器265可以是能够将两个信号组合成一个信号的任何类型的组件(例如,将来自像素内插单元260和纹理加载280的纹理采样指令组合成去往纹理处理器270的一个信号)。

58.在一些实施例中,纹理处理器270可以是接收初始纹理采样指令和纹理采样指令、执行纹理映射、执行纹理滤波和/或将经纹理映射数据返回到纹理加载单元280的组件。

59.在另外的实施例中,纹理加载单元280可以是进行以下操作的组件:从执行单元245接收纹理请求、从gpr 250和纹理缓冲器285检索纹理属性、确定纹理采样指令(例如,基于纹理请求和纹理属性)、向纹理处理器270发送纹理采样指令、从纹理处理器270接收经纹理映射数据、并输出(例如,输出290)经纹理映射数据(例如,输出到另一个组件,输出到gpr 250等)。

60.在另外的实施例中,纹理缓冲器285可以是存储组件,其能够用于存储用于流处理器210的数据,例如纹理属性(如,u/v坐标或i/j系数数据)、虚拟波槽数据、经纹理映射数据等。在一些实现中,纹理缓冲器285可以从定序器230和/或纹理加载单元280接收纹理属性和/或虚拟波槽数据。在另外的实现中,纹理缓冲器285可以从纹理处理器270和/或纹理加载单元280接收经纹理映射数据。例如,如果虚拟波槽没有被转换为物理波槽,如下面进一步详细讨论的,从纹理处理器270接收的纹理映射数据可以存储在纹理缓冲器285中,直到物理波槽可用为止。在另外的实现中,一旦物理波槽变得可用并且虚拟波槽可以被转换为物理波槽,纹理缓冲器285就可以向例如定序器230提供纹理属性和/或虚拟波槽数据。在一些实现中,例如,当从纹理处理器270接收到经纹理映射数据之后物理波槽变得可用时,纹理缓冲器可以向纹理加载单元280提供纹理属性、虚拟波槽数据和/或经纹理映射数据。

61.在另外的实施例中,输出290可以是来自流处理器210、纹理加载单元280、和/或流处理器210的另一个组件的输出。例如,输出290可以包括经纹理映射数据。在一些实施例中,输出290可以是用于后处理操作的经纹理映射数据。在另外的实施例中,可以在流处理器210内执行后处理操作,并且输出290可以是推送到gpu管道中的下游组件的经后处理的经纹理映射数据。

62.图3是与所公开的实施例一致的用于在流处理器上分配通用寄存器空间和波槽的示例过程300的流程图。在一些实施例中,可以使用任何类型的计算设备(例如,个人计算

机、无线通信设备、视频游戏控制台、增强现实头戴式设备、虚拟现实头戴式设备、混合现实头戴式设备等等)来执行过程300。在另外的实施例中,过程300可以由计算设备的gpu来执行。在更进一步的实施例中,可以使用计算设备的gpu的流处理器和纹理处理器来执行过程300。例如,可以使用流处理器110和纹理处理器170或者流处理器210和纹理处理器270来执行过程300。

63.当计算设备(例如,计算设备的gpu的流处理器)获得纹理操作指令时,过程300可以在框310中开始。在一些实施例中,纹理操作指令可以对应于和/或包括纹理属性。在另外的实施例中,可以对纹理操作指令进行处理以确定纹理属性(例如,用于二维(2d)的i/j,或者用于3d、重心系数数据的i/j/k)。在更进一步的实施例中,可以由编译器处理纹理操作指令,以生成用于计算设备的执行线程、生成用于纹理操作的(多个线程的)执行波,并且在线程中包括采样指令结束指示符以指示波的纹理采样何时完成。在另外的实施例中,纹理操作指令可以包括:用于描述要执行的纹理操作的分组。

64.在框315中,计算设备可以针对纹理操作指令的纹理操作的执行波,生成虚拟波槽。在一些实施例中,虚拟波槽可以控制与波相关联的信息。例如,虚拟波槽可以保存指向与波相关联的着色器程序的当前指令指针、用于确定波中的活动线程的执行掩码、和/或指向与波相关联的存储基础的指针(无论当前是否可用)等等。

65.在框320中,计算设备可以判断是否存在可用于纹理操作的gpr空间和/或物理波槽。例如,计算设备可以基于可用的gpr空间的数量、可用物理波槽的数量、与纹理操作相关联的纹理属性的大小/数量、与纹理操作相关联的执行线程的数量、与纹理操作相关联的执行波的数量等等,来执行该判断。

66.如果在框320中,计算设备确定没有足够可用的gpr空间和/或物理波槽(框320

‑

否),则过程可以转到框325。在框325中,计算设备可以判断纹理操作的执行波是否需要gpr空间和/或物理波槽。例如,因为执行波对应于简单的着色器操作(例如,该操作是2d操作并且包括i/j系数数据),因此计算设备可以确定不需要gpr空间和物理波槽。再举一个例子,计算设备可以确定需要gpr空间和物理波槽,这是因为纹理操作对应于更复杂的操作(例如,该操作是3d操作并且包括i/j/k系数数据,计算偏差(例如,基于输入k),执行颜色合成,需要确定w坐标等等)。

67.如果在框325中,计算设备确定第一波不需要gpr空间和/或物理波槽(框325

‑

否),则过程300可以转到框330。在框330中,计算设备可以在不初始分配或使用gpr空间和/或物理波槽的情况下执行纹理操作。例如,纹理操作可以是简单的2d着色器操作,它使用i/j系数数据(纹理属性)和来自本地存储器的数据来确定u/v坐标。在一些实现中,可以使用像素内插单元代替计算设备的执行单元,来执行简单的2d着色器操作。因此,由于可以使用像素内插单元来执行纹理操作,所以在当前阶段可能不需要分配执行单元的物理波槽和gpr空间,尽管在稍后阶段可能需要物理波槽和/或gpr空间用于纹理操作(例如,用于后处理操作)。

68.在框335中,计算设备可以将用于纹理操作的执行波标记为延迟波。如本文所使用的,延迟波是当前没有被分配物理波槽的操作所对应的波。在一些实现中,可以将该标志包括在初始纹理采样指令中(例如,如在框340中生成的),将该指令发送到纹理处理器,并且在从纹理处理器接收的纹理映射数据中接收(例如,如在框350中)。因此,可以通过纹理处

理器来传播该标志。

69.在一些实施例中,计算设备可以维持延迟波容量计数器,以管理当前正在保持的延迟波的数量。例如,当一个新的延迟波被标记时,可以调整(例如,递减)延迟波容量计数器以指示正在维持一个另外的延迟波。当针对延迟波处理采样指令的结束时,可以调整(例如,递增)延迟波容量计数器以指示少了一个正在维持的延迟波。

70.在另外的实施例中,计算设备可以使用写/读指针来维护延迟波队列(例如,在定序器中存储的先进先出(fifo)缓冲器中),以保存覆盖掩码(即,三角形覆盖的像素部分)和覆盖掩码的分配状态。分配状态可以指示是否已经分配了物理波槽或者物理波槽的分配是否在等待中。在生成延迟波后,物理波槽的分配在等待中,直到物理波槽变得可用为止。在一些实施例中,延迟波队列中的第一个延迟波对于变得可用的下一个物理波时隙可以具有优先权。

71.在框340中,计算设备可以生成初始纹理采样指令,并将其发送到纹理处理器。在一些实施例中,初始纹理采样指令可以是基于像素内插单元的处理(例如,简单着色器操作),并且可以包括使纹理处理器执行例如纹理映射和滤波的指令。在另外的实施例中,初始纹理采样指令可以包括:指示初始纹理采样指令与延迟波相关联的标志。

72.在一些实施例中,当纹理处理器正在处理初始采样指令时,如果物理波槽和/或gpr空间变得可用,则计算设备可以将可用的物理波槽分配给延迟波,分配gpr空间,将物理波槽更新为延迟波的覆盖掩码,并将延迟波队列中的分配状态更改为已分配。

73.在350中,计算设备可以从纹理处理器接收经纹理映射数据。例如,计算设备的gpu的流处理器可以从gpu的纹理处理器接收该数据。在一些实施例中,所接收的数据可以包括指示数据对应于延迟波的标志。在另外的实施例中,如果数据与采样指令的结束相关联,则可以调整延迟波容量计数器。

74.在355中,计算设备可以输出纹理映射数据。在一些实施例中,计算设备可以将纹理映射数据输出到gpr,在gpr处可以执行后处理操作。在这样的实施例中,可能需要在后处理操作之前分配gpr空间和物理波槽。因此,如果物理波槽没有变得可用,gpr空间不可用,和/或延迟波的分配保持在等待中,则计算设备可能不得不等待,直到物理波槽和/或gpr空间变得可用以便为纹理映射数据的后处理分配物理波槽为止。在另外的实施例中,可以从流处理器向gpu的其它下游组件输出经纹理映射数据(例如,在已经执行后处理操作之后)。在更进一步的实施例中,经纹理映射数据可以对应于输出到计算设备的显示器的图像帧。

75.返回到框320,如果在框320中计算设备确定gpr空间和物理波槽可用(框320

‑

是),则该过程可以转到框360。或者,返回到框325,如果计算设备确定需要gpr空间和物理波槽(框325

‑

是)(例如,该操作是3d操作并且包括i/j/k系数数据,计算偏差(例如,基于输入k)、执行颜色合成、需要确定w坐标等等),该过程可以转到框360,但可能必须等到gpr空间和/或物理波槽可用为止。

76.在框360和框370中,计算设备可以为纹理操作分配物理波槽和gpr空间。在框360中,计算设备可以通过将虚拟波槽转换为物理波槽来分配物理波槽。例如,计算设备可以将物理波槽更新为虚拟波槽的覆盖掩码。

77.在框370中,计算设备可以将纹理操作的纹理属性(例如,i/j/k系数数据)写入到gpr中。

78.在框375中,计算设备可以执行纹理操作。在一些实施例中,计算设备可以使用计算设备的执行单元(例如,alu)来执行纹理操作。在另外的实施例中,可以使用纹理属性来执行纹理操作,其中执行单元可以从gpr中检索纹理属性。例如,纹理操作可以是3d着色器操作,其使用i/j/k系数数据(从gpr检索的纹理属性)和来自本地存储器的数据来确定u/v/w坐标。然后,执行单元可以将确定的u/v/w坐标存储到gpr。基于纹理操作,执行单元可以向纹理加载单元发送与纹理操作相对应的纹理请求,纹理加载单元可以从gpr中检索i/j/k系数数据和u/v/w坐标。使用检索到的数据,纹理加载单元可以生成纹理采样指令。

79.在框380中,计算设备可以向纹理处理器发送纹理采样指令。在一些实施例中,纹理采样指令可以是基于执行单元的处理(例如,更复杂的操作),并且可以包括使纹理处理器执行纹理映射和滤波的指令。

80.在框350中,计算设备可以接收经纹理映射数据,如上所述。

81.图4是与所公开的实施例一致的用于在流处理器上分配通用寄存器空间和波槽的示例过程400的流程图。在一些实施例中,可以使用任何类型的计算设备(例如,个人计算机、无线通信设备、视频游戏控制台、增强现实头戴式设备、虚拟现实头戴式设备、混合现实头戴式设备等等)来执行过程400。在另外的实施例中,过程400可以由计算设备的gpu来执行。在更进一步的实施例中,可以使用计算设备的gpu的流处理器和纹理处理器来执行过程400。例如,可以使用流处理器110和纹理处理器170或者流处理器210和纹理处理器270来执行过程400。

82.当计算设备(例如,计算设备的gpu的流处理器)获得纹理操作指令时,过程400可以在框405中开始。在一些实施例中,纹理操作指令可以对应于和/或包括纹理属性。在另外的实施例中,可以对纹理操作指令进行处理以确定纹理属性(例如,用于2d的i/j,或者用于3d重心系数数据的i/j/k、)。在更进一步的实施例中,可以由编译器处理纹理操作指令,以生成用于计算设备的执行线程、生成用于纹理操作的(多个线程的)执行波,并且在线程中包括采样指令结束指示符以指示波的纹理采样何时完成。在另外的实施例中,纹理操作指令可以包括:用于描述要执行的纹理操作的分组。

83.在框410中,计算设备可以针对纹理操作指令的纹理操作的执行波,生成虚拟波槽。

84.在框415中,计算设备可以判断是否存在可用于纹理操作的gpr空间和/或物理波槽。例如,计算设备可以基于可用的gpr空间的数量、可用物理波槽的数量、与纹理操作相关联的纹理属性的大小/数量、与纹理操作相关联的执行线程的数量、与纹理操作相关联的执行波的数量等等,来执行该判断。

85.如果在框415中,计算设备确定没有足够可用的gpr空间和/或物理波槽(框415

‑

否),则过程可以转到框420。在框420中,计算设备可以判断纹理操作的执行波是否需要缓冲存储空间和/或波槽。

86.如果在框420中,计算设备确定执行波不需要缓冲存储空间和/或波槽(框420

‑

否),则过程400可以转到框425。在框425中,计算设备可以在不初始分配或使用gpr空间和/或物理波槽的情况下执行纹理操作。在一些实现中,可以使用像素内插单元代替计算设备的执行单元来执行简单的纹理操作。因此,由于可以使用像素内插单元来执行纹理操作,所以在当前阶段可能不需要分配执行单元的物理波槽和gpr空间,尽管在稍后阶段可能需要

物理波槽和/或gpr空间用于纹理操作(例如,用于后处理操作)。

87.在框430中,计算设备可以将纹理操作的执行波标记为延迟波。在一些实现中,该标志是纹理操作对应于延迟波的指示。在另外的实现中,可以将该标志包括在初始纹理采样指令中(例如,如在框435中生成的),将该指令发送到纹理处理器,并且在从纹理处理器接收的纹理映射数据中接收(例如,如在框440中)。因此,可以通过纹理处理器来传播该标志。

88.在一些实施例中,计算设备可以维持延迟波容量计数器以管理当前正在保持的延迟波的数量,并使用写/读指针来维护延迟波队列以保存覆盖掩码(即,三角形覆盖的像素部分)和覆盖掩码的分配状态,如上所述。

89.在框435中,计算设备可以生成初始纹理采样指令,并将其发送到纹理处理器。在一些实施例中,初始纹理采样指令可以是基于像素内插单元的处理(例如,简单着色器操作),并且可以包括使纹理处理器执行例如纹理映射和滤波的指令。在另外的实施例中,初始纹理采样指令可以包括:指示初始纹理采样指令与延迟波相关联的标志。

90.在一些实施例中,当纹理处理器正在处理初始采样指令时,如果物理波槽和/或gpr空间变得可用,则计算设备可以将可用的物理波槽分配给延迟波,分配gpr空间,将物理波槽更新为延迟波的覆盖掩码,并将延迟波队列中的分配状态更改为已分配。

91.在440中,计算设备可以从纹理处理器接收经纹理映射数据。例如,计算设备的gpu的流处理器可以从gpu的纹理处理器接收该数据。在一些实施例中,所接收的数据可以包括指示数据对应于延迟波的标志。在另外的实施例中,如果数据与采样指令的结束相关联,则可以调整延迟波容量计数器。在一些实现中,所接收的经纹理映射数据可以由纹理加载单元(例如,图2中所示的纹理加载单元280)进行接收。例如,如果在流处理器接收经纹理映射数据之前将与经纹理映射数据相对应的虚拟波槽转换为物理波槽,则纹理加载单元可以接收经纹理映射数据。在其它实现中,所接收的经纹理映射数据可以由纹理缓冲器(例如,图2中所示的纹理缓冲器285)进行接收。例如,如果在流处理器接收经纹理映射数据之前没有将与经纹理映射数据相对应的虚拟波槽转换为物理波槽,则可以接收经纹理映射数据并将其存储在纹理缓冲器中,直到物理波槽变得可用为止。

92.在445中,计算设备可以输出经纹理映射数据。在一些实施例中,计算设备可以将经纹理映射数据输出到gpr,在gpr处可以执行后处理操作。在这样的实施例中,可能需要在后处理操作之前分配gpr空间和物理波槽。因此,如果物理波槽没有变得可用,没有足够的gpr空间可用,和/或延迟波的分配保持在等待中,则计算设备可能不得不等待,直到物理波槽和/或gpr空间变得可用以便为纹理映射数据的后处理分配物理波槽为止。在另外的实施例中,可以从流处理器向gpu的其它下游组件输出经纹理映射数据(例如,在已经执行后处理操作之后)。在更进一步的实施例中,经纹理映射数据可以对应于输出到计算设备的显示器的图形内容的图像帧。

93.返回到框420,如果计算设备确定需要缓冲存储空间和波槽(框420

‑

是),则该过程可以转到框450。

94.在框450中,计算设备可以将虚拟波槽数据存储在纹理缓冲器中。

95.在框455中,计算设备可以将纹理操作的纹理属性写入到纹理缓冲器中。

96.因此,如上所述,纹理缓冲器可以允许流处理器继续接收纹理操作,而不是等待用

于当前操作的波槽或gpr空间。此外,计算设备可以继续向纹理处理器发送初始纹理采样指令(例如,如在框435中)。

97.在框460中,计算设备可以执行纹理操作。在一些实施例中,计算设备可以使用计算设备的执行单元(例如,alu)来执行纹理操作。在另外的实施例中,可以使用纹理属性来执行纹理操作,其中执行单元可以从纹理缓冲器中检索纹理属性。然后,执行单元可以将确定的u/v/w坐标存储到纹理缓冲器或gpr(如果空间可用的话)。基于纹理操作,执行单元可以向纹理加载单元发送与纹理操作相对应的纹理请求,纹理加载单元可以从纹理缓冲器(或gpr)中检索执行单元所存储的纹理属性和坐标。使用检索到的数据,纹理加载单元可以确定纹理采样指令。

98.在框470中,计算设备可以确定纹理采样指令,并将其发送到纹理处理器。在一些实施例中,纹理采样指令可以是基于执行单元的处理(例如,更复杂的操作),并且可以包括使纹理处理器执行纹理映射和滤波的指令。在各种实施例中,在框460之前、当在执行框460时、在框460之后、在框470之前、当在执行框470时、在框470之后、在从纹理处理器接收经纹理映射数据时的框440之后等等情况下,可以将虚拟波槽转换为物理波槽,和/或可以将纹理缓冲器中的纹理属性写入gpr中。

99.返回到框415,如果在框415中计算设备确定gpr空间和物理波槽可用(框415

‑

是),则该过程可以转到框480。

100.在框480和框485中,计算设备可以为纹理操作分配物理波槽和gpr空间。在框480中,计算设备可以通过将虚拟波槽转换为物理波槽来分配物理波槽。例如,计算设备可以将物理波槽更新为虚拟波槽的覆盖掩码。

101.在框485中,计算设备可以将纹理操作的纹理属性(例如,i/j/k系数数据)写入到gpr中。

102.在框490中,计算设备可以执行纹理操作。在一些实施例中,计算设备可以使用计算设备的执行单元(例如,alu)来执行纹理操作。然后,执行单元可以将所确定的坐标存储到gpr中。基于纹理操作,执行单元可以向纹理加载单元发送与纹理操作相对应的纹理请求。

103.在框495中,在纹理加载单元处,计算设备可以确定纹理采样指令并将其发送到纹理处理器。在一些实施例中,纹理采样指令可以是基于执行单元所存储的坐标(例如,更复杂的操作),并且可以包括使纹理处理器执行纹理映射和滤波的指令。

104.在框440中,计算设备可以接收经纹理映射数据,如上所述。

105.图5是与所公开的实施例一致的用于将虚拟波槽异步转换为物理波槽的示例过程500的流程图。在一些实施例中,可以使用任何类型的计算设备(例如,个人计算机、无线通信设备、视频游戏控制台、增强现实头戴式设备、虚拟现实头戴式设备、混合现实头戴式设备等等)来执行过程500。在另外的实施例中,过程500可以由计算设备的gpu来执行。在更进一步的实施例中,可以使用计算设备的gpu的流处理器和纹理处理器来执行过程500。例如,可以使用流处理器110和纹理处理器170或者流处理器210和纹理处理器270来执行过程500。另外,可以结合图3中描述的过程300和/或图4中描述的过程400来异步地执行过程500。

106.该过程可以在框510中开始。在框510中,计算设备可以判断延迟波队列是否为空。

如果延迟波队列为空(框510

‑

是),则该过程可以返回到框510。因此,计算设备可以重复和/或连续地监测波队列直到它不再是空为止。如果延迟波队列不为空(框510

‑

否),则该过程可以转到框520。

107.在框520中,计算设备可以判断是否存在可用的gpr空间和/或物理波槽以用于延迟波队列中的优先位置(例如,fifo队列中的第一波槽)中的纹理操作。例如,计算设备可以基于可用的gpr空间的数量、可用的物理波槽的数量、与纹理操作相关联的纹理属性的大小/数量、与纹理操作相关联的执行线程的数量、与纹理操作相关联的执行波的数量等等,来执行该判断。

108.如果在框520中,计算设备确定没有足够的gpr空间和/或物理波槽可用(框520

‑

否),则该过程可以返回到框520。因此,计算设备可以重复地和/或持续地监测gpr空间和物理波槽,直到其可用于优先位置的纹理操作为止。

109.如果在框520中,计算设备确定gpr空间和物理波槽可用(框520

‑

是),则该过程可以转到框530。

110.在框530和框540中,计算设备可以为纹理操作分配物理波槽和gpr空间。在框480中,计算设备可以通过将虚拟波槽转换为物理波槽来分配物理波槽。例如,计算设备可以将物理波槽更新为虚拟波槽的覆盖掩码,并且从延迟波队列中去除虚拟波。

111.在框540中,计算设备可以将用于纹理操作的纹理属性(例如,i/j/k系数数据)写入到gpr中。

112.因此,可以与图3和图4中描述的过程异步地,将延迟波从虚拟波槽转换到物理波槽。例如,在确定初始纹理采样并将其发送到纹理处理器(例如,图3中的340或者图4中的435)之前,可以将延迟波转换为物理波槽,或者在从纹理处理器(例如,图3中的350或图4中的440)接收到经纹理映射数据之后,但在对经纹理映射数据执行后处理之前,可以将延迟波转换为物理波槽,并且,在一些例子中,经纹理映射数据可以存储在纹理缓冲器中。在另一个例子中,可以在执行单元(例如,图4中的460)处执行纹理操作之前和/或在确定纹理采样并将其发送到纹理处理器(例如,图4中的470)之前,将延迟波转换为物理波槽。

113.在一些实施例中,后处理可能需要物理波槽和gpr空间。因此,在这样的实施例中,在执行框530和框540之后,才可能发生延迟波纹理操作的后处理。在另外的实施例中(例如,对应于不使用纹理缓冲器的图1的实施例),在执行纹理操作之前可能需要物理波槽和gpr空间。因此,在这样的实施例中,可以直到在执行框530和框540之后,才执行针对延迟波的纹理操作。

114.图6是示出与所公开的实施例一致的具有图形处理器和至少一个流处理器的示例设备的框图。在图6中,描绘了可以执行图形处理的电子设备的示例图,并且通常将其指定为电子设备600。电子设备600可以对应于移动设备(例如,诸如蜂窝手机之类的无线通信设备)、计算机(例如,服务器、膝上型计算机、平板计算机或桌面型计算机)、接入点、基站、可穿戴电子设备(例如,个人相机、头戴式显示器、vr头戴式设备、ar头戴式设备、智能眼镜或智能手表)、车辆控制系统或控制台(例如,高级驾驶员辅助系统)、自动驾驶车辆(例如,机器人汽车或无人机)、家用电器、机顶盒、娱乐设备、导航设备、个人数字助理(pda)、电视、监视器、调谐器、无线电台(例如,卫星无线电台)、音乐播放器(例如,数字音乐播放器或便携式音乐播放器)、视频播放器(例如,诸如数字视频光盘(dvd)播放器或便携式数字视频播放

器之类的数字视频播放器)、机器人、医疗保健设备、其它电子设备或它们的组合。

115.电子设备600包括一个或多个处理器,例如处理器610和图形处理单元(gpu)696。处理器610可以包括中央处理单元(cpu)、数字信号处理器(dsp)、另一个处理设备或者其组合。在图6的例子中,gpu 696可以包括渲染引擎612和流处理器604。在其它实施例中,渲染引擎612和/或流处理器604可以包括在处理器610等等中。在另外的实施例中,流处理器604可以是渲染引擎612的一部分。

116.处理器610可以耦合到gpu 696。在说明性示例中,处理器610可以被配置为使用图形应用程序编程接口(api)调用,与gpu 696进行通信。例如,gpu 696可以包括api调用分析器(没有示出),并且处理器610可以被配置为在gpu 696执行的图形处理期间,向api调用分析器提供api调用。

117.电子设备600还可以包括一个或多个存储器(例如,存储器632)。存储器632可以耦合到处理器610、gpu 696或两者。存储器632可以包括随机存取存储器(ram)、磁阻随机存取存储器(mram)、闪存、只读存储器(rom)、可编程只读存储器(prom)、可擦除可编程只读存储器(eprom)、电可擦除可编程只读存储器(eeprom)、一个或多个寄存器、硬盘、可移动磁盘、压缩光盘只读存储器(cd

‑

rom)、另一种存储设备或者它们的组合。

118.存储器632可以存储指令660。指令660可以由处理器610、gpu 696或两者执行。在一些实施例中,指令660可以指示处理器610和/或gpu 696执行关于图3

‑

5所描述的过程。

119.编码器/解码器(codec)634也可以耦合到处理器610。codec 634可以耦合到一个或多个麦克风(例如,麦克风638)。codec 634也可以耦合到一个或多个扬声器(例如,扬声器636)。codec 634可以包括存储可由codec 634执行的指令695的存储器690。

120.图6还示出了耦合到处理器610和显示器628的显示控制器626。在一些实施例中,电子设备600还可以包括耦合到天线642的无线控制器640。在其它实施例中,电子设备600还可以包括耦合到计算机网络电缆的有线网络控制器(没有示出)。

121.电子设备600还可以包括传感器650(例如,相机)。传感器650可以是被配置为捕捉图像的任何类型的传感器。

122.在特定的例子中,处理器610、gpu 696、存储器632、显示控制器626、codec 634和无线控制器640包括在片上系统(soc)设备622中。此外,输入设备630和电源644可以耦合到soc设备622。此外,在特定的例子中,如图6中所示,显示器628、输入设备630、扬声器636、麦克风638、天线642、电源644和传感器650在soc设备622的外部。然而,显示器628、输入设备630、扬声器636、麦克风638、天线642、电源644和传感器650中的每一个可以耦合到soc设备622的组件(例如,耦合到接口或控制器)。

123.如本文所使用的,“耦合”可以包括通信耦合、电耦合、磁耦合、物理耦合、光耦合以及其组合。两个设备(或组件)可以通过一个或多个其它设备、组件、电线、总线、网络(例如,有线网络、无线网络、或它们的组合)等等,来直接地或间接地耦合(例如,通信耦合、电耦合或物理耦合)。电耦合的两个设备(或组件)可以包括在同一设备中,也可以包括在不同的设备中,并且可以通过电子设备、一个或多个连接器或电感耦合进行连接,作为说明性而非限制性的例子。在一些实现中,通信耦合(例如,利用电通信进行耦合)的两个设备(或组件),可以例如通过一个或多个电线、总线、网络等等,直接或间接地发送和接收电信号(数字信号或模拟信号)。

124.可以使用计算机文件(例如,包括图形数据库系统ii(gdsii)、gerber等等文件格式的计算机文件),来设计和表示前述公开的设备和功能。计算机文件可以存储在计算机可读介质上。可以将一些或所有此类文件提供给基于此类文件制造设备的制造处理者。由此产生的产品包括晶圆,然后将其切割成管芯并封装成集成电路(或“芯片”)。然后,在电子设备(例如,图6的电子设备600)中采用集成电路。

125.虽然为了方便起见已经单独描述了某些示例,但是应当注意,可以在不脱离本公开内容的保护范围的情况下适当地组合这些示例的各方面。例如,设备100和200可以被配置为:基于参考图3

‑

5中的每一个所描述的方面来操作。本领域普通技术人员将认识到落入本公开内容的保护范围内的其它此类修改。

126.结合本文所公开示例描述的各种示例性的逻辑框、配置、模块、电路和算法步骤可以实现成电子硬件、由处理器执行的计算机软件或二者的组合。上面对各种示例性的部件、框、配置、模块、电路和步骤均围绕其功能进行了总体描述。至于这种功能是实现成硬件还是实现成处理器可执行指令,取决于特定的应用和对整个系统所施加的设计约束条件。熟练的技术人员可以针对每个特定应用,以变通的方式实现所描述的功能,但是,这种实现决策不应解释为背离本发明的保护范围。

127.本文所描述的方法或者算法的一个或多个操作可直接体现为硬件、由处理器执行的软件模块或二者的组合。例如,图3的过程300、图4的过程400或图5的过程500中的一个或多个操作,可以由现场可编程门阵列(fpga)设备、专用集成电路(asic)、诸如cpu的处理单元、数字信号处理器(dsp)、控制器、另一个硬件设备、固件设备或它们的组合来发起、控制或执行。软件模块可以位于ram、mram、闪存、rom、eprom、eeprom、寄存器、硬盘、移动硬盘、cd

‑

rom或者本领域已知的任何其它形式的非暂时性存储介质中。可以将一种示例性的存储介质连接至处理器,从而使该处理器能够从该存储介质读取信息,并可向该存储介质写入信息。另外地或替代地,存储介质也可以是处理器的组成部分。处理器和存储介质可以驻留在asic中。asic可以驻留在计算设备或用户终端中。另外地或替代地,处理器和存储介质可以作为分立组件驻留在计算设备或用户终端中。

128.为使本领域任何普通技术人员能够实现或者使用所公开的示例,上面围绕所公开的示例进行了描述。对于本领域普通技术人员来说,对这些示例的各种修改是显而易见的,并且,本文定义的总体原理也可以在不脱离本公开内容的保护范围的基础上应用于其它示例。因此,本公开内容并不限于本文所示出的示例,而是可以与所附权利要求书规定的原理和新颖性特征的最广范围相一致。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。