1.本技术涉及芯片唤醒技术领域,具体地,涉及一种唤醒电路、芯片系统和电子设备。

背景技术:

2.随着集成电路制造工艺的不断发展,芯片的制程越来越先进,且集成度越来越高。另一方面,互联网的浪潮已经慢慢步入了第三个阶段:步入了可穿戴和物联网的时代,所以这些设备已经成为了芯片的设计主流。在这种技术前提下,功耗就成为了芯片性能中不可忽视的问题,如何能够通过降低芯片正常工作中的功耗,使这种可穿戴或者物联网设备在不插电的模式下,工作比较长的时间,便成为了各家设计厂商必须要解决的设计课题。

3.一般而言,系统功耗总体上可分为静态功耗和动态功耗两大部分,其中,时钟的翻转占据系统动态功耗的绝大部分,所以就降低系统动态功耗而言,有两种基本的方法:关掉时钟或者关掉电源。所以为了整个芯片功耗的考虑,一个芯片系统(system on chip,soc)在常规的情况下,会有下面几种低功耗模式:

4.睡眠模式(sleep

‑

mode):关掉了芯片系统中主中央处理器(central processing unit,cpu)的时钟,芯片系统中的其它模块都正常工作。

5.停止模式(stop

‑

mode):关掉除芯片系统常开域(always

‑

on domian)模块之外,芯片系统中的其余模块的时钟。

6.待机模式(standby

‑

mode):关掉除芯片系统常开域(always

‑

on domian)模块之外,芯片系统中的其余模块的电源,这种模式最为省电。

7.为了降低功耗的考虑,根据使用场景会进入上面的三种低功耗模式中的某一种,从而使整个芯片系统的功耗降到最低。

8.现有技术中存在的问题:

9.当芯片系统进入到上面三种低功耗模式中的某一种后,一般需要有一个常开时钟,以保证对外部唤醒源的实时响应,以使芯片系统能够顺利退出低功耗模式。由于这个常开时钟的存在,同样会使芯片系统在低功耗模式下消耗一定的功耗,降低设备的使用时间,并没有达到低功耗模式的真正目的。

技术实现要素:

10.本技术实施例中提供了一种唤醒电路、芯片系统和电子设备,以解决芯片系统在低功耗模式下存在的功耗问题。

11.根据本技术实施例的第一个方面,提供了一种唤醒电路,包括触发器,所述触发器的时钟端与唤醒源电连接,所述触发器的数据端与电源电连接,所述触发器的输出端与处理器电连接;

12.所述触发器用于在接收到所述唤醒源发送的唤醒触发信号的情况下,向所述处理器发送唤醒响应信号。

13.根据本技术实施例的第二个方面,提供了一种芯片系统,所述芯片系统包括:唤醒电路、唤醒源、电源和处理器,所述唤醒电路包括触发器,所述触发器的时钟端与所述唤醒源电连接,所述触发器的数据端与所述电源电连接,所述触发器的输出端与所述处理器电连接;

14.所述触发器用于在接收到所述唤醒源发送的唤醒触发信号的情况下,向所述处理器发送唤醒响应信号。

15.根据本技术实施例的第三个方面,提供了一种电子设备,包括如第二方面所述的芯片系统。

16.采用本技术实施例中提供的唤醒电路、芯片系统和电子设备,通过唤醒源与触发器的时钟端电连接,触发器的数据端与电源电连接,能够实现在无常开时钟的情况下,唤醒源产生的唤醒触发信号能够直接唤醒处理器,将芯片系统从低功耗模式中唤醒。这种方式,在芯片系统进入低功耗模式下,不存在时钟翻转,避免了系统动态功耗;同时,又能够完成芯片系统从低功耗模式退出的应用需求。

附图说明

17.此处所说明的附图用来提供对本技术的进一步理解,构成本技术的一部分,本技术的示意性实施例及其说明用于解释本技术,并不构成对本技术的不当限定。在附图中:

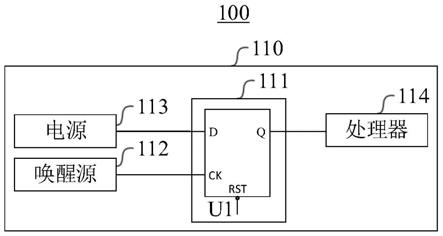

18.图1为现有技术的一种唤醒电路的电路示意图;

19.图2为本技术实施例提供的一种电子设备的结构示意图;

20.图3为本技术实施例提供的一种唤醒电路的电路示意图;

21.图4为本技术实施例提供的另一种唤醒电路的电路示意图;

22.图5为本技术实施例提供的又一种唤醒电路的电路示意图;

23.图6为本技术实施例提供的又一种唤醒电路的电路示意图。

24.100

‑

电子设备;110

‑

芯片系统;111

‑

唤醒电路;112

‑

唤醒源;113

‑

电源;114

‑

处理器;115

‑

测试时钟模块;116

‑

中断清除寄存器;117

‑

复位模块;118

‑

使能模块;u1

‑

触发器;u2

‑

第一反相器;u3

‑

第二反相器;u4

‑

第一与门;u5

‑

第二与门;k1

‑

第一选择器;k2

‑

第二选择器;k3

‑

第三选择器。

具体实施方式

25.在实现本技术的过程中,发明人发现,如图1所示,现有技术中将芯片系统从低功耗模式唤醒方式为,将触发器的时钟端与常开时钟电连接,触发器的数据端与唤醒源电连接,触发器的输出端与处理器电连接。常开时钟向触发器的时钟端提供常开时钟信号,当唤醒源向触发器的数据端发送唤醒触发信号时,触发器依据常开时钟信号能够采集到唤醒触发信号,并通过触发器的输出端向处理器发送唤醒响应信号,以使处理器从低功耗模式中被唤醒。

26.由于这个常开时钟的存在,会使芯片系统在低功耗模式下消耗一定的功耗,降低电子设备的使用时间,并没有达到低功耗模式的真正目的。

27.针对上述问题,本技术实施例中提供了一种唤醒电路、芯片系统和电子设备,通过唤醒源与触发器的时钟端电连接,触发器的数据端与电源电连接,能够实现在无常开时钟

的情况下,唤醒源产生的唤醒触发信号能够直接唤醒处理器,将芯片系统从低功耗模式中唤醒。这种方式,在芯片系统进入低功耗模式下,不存在时钟翻转,避免了系统动态功耗;同时,又能够完成芯片系统从低功耗模式退出的应用需求。

28.本技术实施例中的系统芯片可以支持各种计算机语言,例如,面向对象的程序设计语言java和直译式脚本语言javascript等。

29.为了使本技术实施例中的技术方案及优点更加清楚明白,以下结合附图对本技术的示例性实施例进行进一步详细的说明,显然,所描述的实施例仅是本技术的一部分实施例,而不是所有实施例的穷举。需要说明的是,在不冲突的情况下,本技术中的实施例及实施例中的特征可以相互组合。

30.请参照图2,为本技术实施例提供的一种电子设备100的结构示意图,该电子设备100包括芯片系统110,芯片系统110包括:唤醒电路111、唤醒源112、电源113和处理器114,唤醒电路111包括触发器u1,触发器u1的时钟端与唤醒源112电连接,触发器u1的数据端与电源113电连接,触发器u1的输出端与处理器114电连接。

31.触发器u1用于在接收到唤醒源112发送的唤醒触发信号的情况下,向处理器114发送唤醒响应信号。

32.应理解,电源113为触发器u1的数据端提供高电平,在芯片系统110进入低功耗模式的情况下,若唤醒源112向触发器u1的时钟端发送唤醒触发信号(上升沿或高电平),触发器u1在唤醒触发信号的触发下,产生唤醒响应信号(高电平),并发送至处理器114,以使处理器114退出低功耗模式。

33.其中,触发器u1的数据端连接电源113,能够使触发器u1的数据端和时钟端之间不会有setup(建立时间)或hold(保持时间)的时序违例,降低了使用风险。

34.可见,通过唤醒源112与触发器u1的时钟端电连接,触发器u1的数据端与电源113电连接,能够实现在无常开时钟的情况下,唤醒源112产生的唤醒触发信号能够直接唤醒处理器114,将芯片系统110从低功耗模式中唤醒。这种方式,在芯片系统110进入低功耗模式下,不存在时钟翻转,避免了系统动态功耗;同时,又能够完成芯片系统110从低功耗模式退出的应用需求。

35.其中,电子设备100可以为可穿戴设备或物联网设备,处理器114可以为中央处理器(central processing unit,cpu)、网络处理器(networkprocessor,np)等,触发器u1可以为d触发器u1,唤醒源112可以为芯片系统110上的pad(测试点)。

36.应理解,唤醒源112可以与外部唤醒设备电连接,外部唤醒设备通过唤醒源112向触发器u1发送唤醒触发信号。该外部唤醒设备可以为具有i2c(inter-integrated circuit)功能的芯片。

37.在本技术实施例中,唤醒源112提供的唤醒触发信号可以为上升沿、高电平、下降沿和低电平,即唤醒电路111可以响应四种唤醒触发信号。其实现原理为:

38.如图3所示,唤醒电路111还包括第一选择器k1和第一反相器u2,唤醒源112与第一选择器k1的第一输入端电连接,唤醒源112通过第一反相器u2与第一选择器k1的第二输入端电连接,第一选择器k1的输出端与触发器u1的时钟端电连接。

39.第一选择器k1用于在唤醒触发信号为上升沿或高电平的情况下,通过第一选择器k1的第一输入端将唤醒触发信号发送至第一选择器k1的输出端;第一选择器k1还用于在唤

醒触发信号为下降沿或低电平的情况下,通过第一选择器k1的第二输入端将唤醒触发信号发送至第一选择器k1的输出端。

40.应理解,在唤醒触发信号为上升沿或高电平的情况下,将第一选择器k1的第一输入端与第一选择器k1的输出端连通,第一选择器k1的第二输入端与第一选择器k1的输出端断开连接,使得唤醒触发信号通过第一选择器k1的第一输入端发送至第一选择器k1的输出端;在唤醒触发信号为下降沿或低电平的情况下,将第一选择器k1的第二输入端与第一选择器k1的输出端连通,第一选择器k1的第一输入端与第一选择器k1的输出端断开连接,使得唤醒触发信号通过第一选择器k1的第二输入端发送至第一选择器k1的输出端。

41.其中,通过设置第一选择器k1的选择端,能够实现第一选择器k1的输出端与第一输入端和第二输入端选择连接。例如,若第一选择器k1的选择端输入为低电平的选择信号,第一选择器k1的输出端与第一输入端连通,第一选择器k1的输出端与第二输入端断开连接;若第一选择器k1的选择端输入为高电平的选择信号,第一选择器k1的输出端与第二输入端连通,第一选择器k1的输出端与第一输入端断开连接。

42.同时,为了保证芯片系统110在dft(design for test)模式下的测试覆盖率,请参照图4,芯片系统110还包括测试时钟模块115,唤醒电路111还包括第二选择器k2,第二选择器k2的第一输入端与第一选择器k1的输出端电连接,第二选择器k2的第二输入端与测试时钟模块115电连接,第二选择器k2的输出端与触发器u1的时钟端电连接。

43.第二选择器k2用于在唤醒处理器114的情况下,通过第二选择器k2的第一输入端将唤醒触发信号发送至触发器u1的时钟端;第二选择器k2还用于在测试模式下,通过第二选择器k2的第二输入端将测试时钟模块115产生的测试时钟发送至触发器u1的时钟端。

44.应理解,测试模式即为dft模式,测试模式的原理为:在芯片设计过程中引入测试逻辑,并利用这部分测试逻辑完成测试向量的自动生产,从而达到快速有效的芯片测试的目的。

45.故在芯片系统110进入测试模式的情况下,为了保证触发器u1可以被测试到,则需向触发器u1的时钟端提供测试时钟。即,在测试模式下,第二选择器k2的第二输入端与第二选择器k2的输出端连通,第二选择器k2的第一输入端与第二选择器k2的输出端断开连接;在唤醒处理器114的情况下,即在芯片系统110处于低功耗模式下,第二选择器k2的第一输入端与第二选择器k2的输出端连通,第二选择器k2的第二输入端与第二选择器k2的输出端断开连接。

46.其中,通过设置第二选择器k2的选择端,能够实现第二选择器k2的输出端与第一输入端和第二输入端选择连接。例如,若第二选择器k2的选择端输入为低电平的选择信号,第二选择器k2的输出端与第一输入端连通,第二选择器k2的输出端与第二输入端断开连接;若第二选择器k2的选择端输入为高电平的选择信号,第二选择器k2的输出端与第二输入端连通,第二选择器k2的输出端与第一输入端断开连接。

47.图4所示的唤醒电路111,为唤醒电路111可以响应四种唤醒触发信号的情况下,考虑芯片系统110在dft模式下的测试覆盖率,在图3所示的唤醒电路111的基础上增设了第二选择器k2。在另一种实施例中,可以不用考虑唤醒电路111是否可以响应四种唤醒触发信号,只考虑芯片系统110在dft模式下的测试覆盖率。如图5所示,在图2所示的唤醒电路111的基础上增设第二选择器k2,第二选择器k2的第一输入端与唤醒源112电连接,第二选择器

k2的第二输入端与测试时钟模块115电连接,第二选择器k2的输出端与触发器u1的时钟端电连接。

48.图5所示的唤醒电路111与图4所示的唤醒电路111的区别为,第二选择器k2的第一输入端连接关系不同,图5所示的第二选择器k2的第一输入端直接与唤醒源112电连接,图4所示的第二选择器k2的第一输入端通过第一选择器k1和第一反相器u2与唤醒源112电连接。虽然第二选择器k2的第一输入端连接关系不同,但第二选择器k2的第一输入端接收的信号是相同的,均接收唤醒触发信号。同时,第二选择器k2的工作原理也是相同的。故图5所示的第二选择器k2的工作原理可以参照图4所示的第二选择器k2的工作原理,在此不在累述。

49.当处理器114成功响应了唤醒响应信号,顺利从低功耗模式中恢复之后,为了避免处理器114频繁去响应唤醒响应信号,可以对触发器u1进行复位操作。如图6所示,芯片系统110还包括中断清除寄存器116,唤醒电路111还包括第一与门u4和第二反相器u3,所述第一与门u4的输入端与中断清除寄存器116电连接,第一与门u4的输出端通过第二反相器u3与触发器u1的复位端电连接,中断清除寄存器116还与处理器114电连接。

50.第一与门u4和第二反相器u3用于将中断清除寄存器116产生的唤醒清除信号发送至触发器u1的复位端;其中,中断清除寄存器116在处理器114被唤醒后产生唤醒清除信号;触发器u1还用于依据唤醒清除信号复位。

51.应理解,芯片系统110包括多个唤醒源112,每个唤醒源112对应设置有唤醒电路111,即唤醒源112的数量与唤醒电路111的数量相同。每个唤醒源112上对应设置有一个中断清除寄存器116,当处理器114从低功耗模式中恢复之后,被唤醒的处理器114访问对应唤醒换上的中断清除寄存器116,当处理器114给中断清除寄存器116写1时,中断清除寄存器116对应产生唤醒清除信号,并将该唤醒清除信号通过第一与门u4和第二反相器u3发送至触发器u1的复位端。

52.其中,触发器u1的复位端有低电平出现时,触发器u1的输出端的唤醒响应信号会被清除掉,使得触发器u1的输出端回到默认值。而由于中断清除寄存器116产生的唤醒清除信号为高电平,故设置第二反相器u3,第二反相器u3可将为高电平的唤醒清除信号反相为低电平的唤醒清除信号。

53.利用触发器u1的复位机制,可以将唤醒响应信号清除掉,避免了芯片系统110频繁的去响应唤醒响应信号。

54.在触发器u1进行复位功能时,为了满足dft测试需求,继续参照图6,芯片系统110还包括复位模块117,唤醒电路111还包括第三选择器k3,第一与门u4的输出端通过第二反相器u3与第三选择器k3的第一输入端电连接,第三选择器k3的第二输入端与复位模块117电连接,第三选择器k3的输出端与触发器u1的复位端电连接。

55.第三选择器k3用于在测试模式下,通过第三选择器k3的第二输入端将复位模块117产生的复位信号发送至触发器u1的复位端;第三选择器k3还用于在非测试模式下,通过第三选择器k3的第一输入端将唤醒清除信号发送至触发器u1的复位端。

56.应理解,当芯片系统110进入测试模式(即dft模式)时,为了保证触发器u1的复位功能能够被测试,第三选择器k3的第二输入端与第三选择器k3的输出端连通,第三选择器k3的第一输入端与第三选择器k3的输出端断开连接,由复位模块117为触发器u1提供正常

的复位信号;在芯片系统110处于非测试模式下(例如,芯片系统110处于低功耗模式下),第三选择器k3的第一输入端与第三选择器k3的输出端连通,第三选择器k3的第二输入端与第三选择器k3的输出端断开连接,由中断清除寄存器116为触发器u1提供唤醒清除信号。

57.其中,通过设置第三选择器k3的选择端,能够实现第三选择器k3的输出端与第一输入端和第二输入端选择连接。例如,若第三选择器k3的选择端输入为低电平的选择信号,第三选择器k3的输出端与第一输入端连通,第三选择器k3的输出端与第二输入端断开连接;若第三选择器k3的选择端输入为高电平的选择信号,第三选择器k3的输出端与第二输入端连通,第三选择器k3的输出端与第一输入端断开连接。

58.可见,当芯片系统110进入测试模式时,第三选择器k3的输出端与第三选择器k3的第二输入端连通,由复位模块117为触发器u1提供正常的复位信号,触发器u1可以被正常复位,不会影响测试覆盖率。

59.在本实施例中,唤醒电路111还包括第二与门u5,第二与门u5的第一输入端与触发器u1的输出端电连接,第二与门u5的第二输入端与使能模块118电连接,第二与门u5的输出端与处理器114电连接。

60.应理解,第二与门u5用于依据使能模块118发送的使能信号和触发器u1发送的唤醒响应信号,向处理器114发送唤醒信号,处理器114依据唤醒信号从低功耗模式中退出。

61.为了防止处理器114被误唤醒,第二与门u5同时接收到唤醒响应信号和使能信号,才会向处理器114发送唤醒信号,使处理器114从低功耗模式中退出。若第二与门u5只接收到唤醒响应信号和使能信号中的一个,或均为接收到,第二与门u5不会向处理器114发送唤醒信号,处理器114无法被唤醒。

62.综上,本技术提供了一种唤醒电路、芯片系统和电子设备,芯片系统包括:唤醒电路、唤醒源、电源和处理器,唤醒电路包括触发器,触发器的时钟端与唤醒源电连接,触发器的数据端与电源电连接,触发器的输出端与处理器电连接;触发器用于在接收到唤醒源发送的唤醒触发信号的情况下,向处理器发送唤醒响应信号。通过唤醒源与触发器的时钟端电连接,触发器的数据端与电源电连接,能够实现在无常开时钟的情况下,唤醒源产生的唤醒触发信号能够直接唤醒处理器,将芯片系统从低功耗模式中唤醒。这种方式,在芯片系统进入低功耗模式下,不存在时钟翻转,避免了系统动态功耗;同时,又能够完成芯片系统从低功耗模式退出的应用需求。

63.尽管已描述了本技术的优选实施例,但本领域内的技术人员一旦得知了基本创造性概念,则可对这些实施例作出另外的变更和修改。所以,所附权利要求意欲解释为包括优选实施例以及落入本技术范围的所有变更和修改。

64.显然,本领域的技术人员可以对本技术进行各种改动和变型而不脱离本技术的精神和范围。这样,倘若本技术的这些修改和变型属于本技术权利要求及其等同技术的范围之内,则本技术也意图包含这些改动和变型在内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。