一种32路rs485接口卡的实现系统

技术领域

1.本发明涉及计算机接口通信技术领域,特别是一种32路rs485接口卡的实现系统。

背景技术:

2.在工业控制领域,rs485接口是一种常用的通信接口,一般采用rs485接口芯片实现,该实现方法存在以下问题:

3.1)rs485接口芯片一般最多只有4路rs485串行接口,如果实际需求路数较多时需要多片接口芯片并联实现,并且需要额外增加pcie交换芯片,占用的印制板面积大,成本比较高;

4.2)rs485多路同时通信时,由于主机处理能力有限,可能出现读写不及时,产生丢包。

技术实现要素:

5.本发明解决的技术问题是:克服现有技术的不足,提供了一种32路rs485接口卡的实现系统。

6.为了解决上述技术问题,本发明实施例提供了一种32路rs485接口卡的实现系统,所述系统包括:fpga芯片、rs485电平转换芯片和内存芯片,所述fpga芯片包括32个串口模块、ddr ip核和axi总线,其中,每个所述串口模块通过所述rs485电平转换芯片与rs485接口连接,所述ddr ip核分别与所述axi总线和所述内存芯片连接,所述内存芯片以缓存通过所述rs485接口收发的数据。

7.可选地,所述fpga芯片还包括:内存读写模块、中断产生模块、pcie模块和axi

‑

lite总线,其中,

8.所述内存读写模块分别与所述axi总线和所述串口模块连接;

9.所述pcie模块与所述axi总线,所述pcie模块通过所述axi

‑

lite总线与所述中断产生模块连接;

10.所述中断产生模块还与所述内存读写模块连接。

11.可选地,所述串口模块包括:发送fifo单元、发送单元、接收fifo单元和接收单元,其中,

12.所述串口模块的数据流向包括数据接收通路和数据发送通路;

13.在数据接收通路中,所述接收单元通过接收引脚接收串口波形信号并转换为字节数据发送到所述接收fifo单元,所述内存读写模块通过判断所述接收fifo单元的空信号以读取所述接收fifo单元的数据;

14.在数据发送通路中,内存读写模块发送的字节数据被串口模块写入所述发送fifo单元,所述发送单元将所述发送fifo中的字节数据转换为串口波形,经发送引脚发送到所述rs485电平转换芯片。

15.可选地,所述中断产生模块的数量为8个,32个所述串口模块中每四个分为一组,

每组的串口模块共用一个所述中断产生模块。

16.可选地,所述串口模块中的接收单元通过状态机实现字节数据到串口波形的转换,所述状态机包括空闲状态、接收起始位、接收数据位、接收停止位、发送写使能,状态机的启动信号为接收引脚出现下降沿。

17.可选地,所述串口模块中的发送单元通过状态机实现串口波形到字节数据的转换,状态机包括空闲、发送读使能,锁存发送数据,发送起始位,发送数据位,发送停止位,状态机的启动信号为空信号为0。

18.可选地,所述内存读写模块,被配置为实现所述串口模块内的发送fifo单元和接收fifo单元与所述内存芯片之间的数据转移控制;

19.所述内存读写模块包括内存读通路和内存写通路,

20.在所述内存读通路中,所述内存读写模块将所述内存芯片32个发送区域中的发送数据通过所述串口模块发送;

21.在所述内存写通路中,所述内存读写模块将32个所述串口模块接收的数据写入到所述内存芯片的32个接收区域中,并产生中断请求信号至所述中断产生模块。

22.可选地,在所述中断产生模块接收到内存读写模块产生的任一个中断产生模块的请求信号后,将连接到所述pcie模块的中断输出信号置1,以使所述pcie模块产生主机中断;

23.在主机响应中断后,通过所述pcie模块的所述axi总线读取内存相应区域的数据,并通过所述pcie模块的axi

‑

lite总线给中断产生模块发送应答信号,所述中断产生模块将中断输出清零。

24.可选地,在所述内存读通路中,将所述内存芯片中的发送数据通过串口模块发送;

25.主机通过所述pcie模块的axi总线将要发送的数据写入所述内存芯片的存储区域中,并更改所述存储区域的写指针;

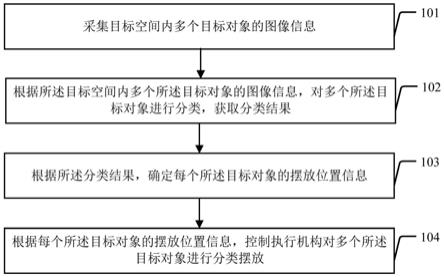

26.fpga程序循环查询所述内存芯片中32个发送区域中的读指针和写指针,如果两个指针位置不同,则通过所述axi总线读取内存中的数据并写入对应串口模块中的发送fifo中,并更新内存区域的读指针;

27.在所述内存写通路中,循环查询所述32个串口模块的接收fifo单元,若所述接收fifo单元中有数据,则将数据读出并通过所述axi总线写入内存相应区域,更新该内存区域的写指针,并产生中断请求信号至所述中断产生模块。

28.本发明与现有技术相比的优点在于:

29.本发明实施例相比传统的专用串口芯片方法更加灵活,扩展性更好,而采用多路rs485串行接口的两级缓存方法,即fifo和内存芯片两级缓存,解决了多路rs485串行接口同时通信的丢包问题,该方法同样适用于其他类型的多路接口电路中;并且给出了fpga和上位机的中断处理方法,提高了系统的效率,并解决了中断过多导致主机丢中断的问题。

附图说明

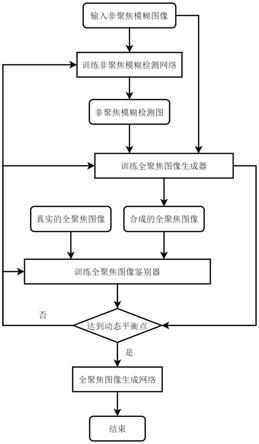

30.图1为本发明实施例提供的一种32路rs485接口卡的实现系统的结构框图;

31.图2为本发明实施例提供的一种32路rs485接口卡的fpga实现原理的示意图;

32.图3为本发明实施例提供的一种串口模块的示意图;

33.图4为本发明实施例提供的一种串口发送单元的示意图;

34.图5为本发明实施例提供的一种串口接收单元的示意图。

具体实施方式

35.实施例一

36.参照图1,示出了本发明实施例提供的一种32路rs485接口卡的实现系统的示意图,如图1所示,所述32路rs485接口卡的实现系统100可以包括:fpga(field

‑

programmable gate array,现场可编程门阵列)芯片110、rs485电平转换芯片120和内存芯片130,所述fpga芯片110包括32个串口模块121、ddr ip核122和axi(advanced extensible interface)总线123,其中,每个所述串口模块121通过所述rs485电平转换芯片120与rs485接口连接,所述ddr ip核122分别与所述axi总线123和所述内存芯片130连接,所述内存芯片130以缓存通过所述rs485接口收发的数据。

37.本发明实施例通过fpga逻辑实现rs485串行接口,并通过使用内存和fifo两级缓存、分组中断的方式实现pcie和32路rs485串行接口的无丢包可靠通信。

38.接下来结合图2对本发明实施例进行如下详细描述。

39.参照图2,示出了本发明实施例提供的一种32路rs485接口卡的fpga实现原理的示意图,如图2所示,fpga芯片、rs485电平转换芯片、内存芯片为32路rs485接口卡的主要芯片,fpga芯片是接口卡的核心芯片,实现32路串口模块、内存读写模块、中断产生模块、pcie(peripheral component interconnect express,高速串行计算机扩展总线标准)模块、ddr ip核、模块间的axi总线和axi

‑

lite总线等功能;电平转换芯片将rs485信号转换为ttl电平的串口波形接入串口模块,并将串口模块输出的ttl电平的串口波形转换为rs485信号;内存芯片用于缓存rs485接口的收发数据,其存储区域划分为32个接收区域和32个发送区域,分别用于缓存32路rs485接口的接收数据和32路rs485接口的发送数据,每个区域的头两个字节存储该区域的读指针和写指针;主机通过pcie x1接口与fpga芯片相连。

40.图2所示的fpga芯片中,串口模块0~串口模块31为32路相同的串口模块,实现32路rs485串口通信,串口模块的组成框图见图3。

41.图2所示ddr ip核实现了axi总线与内存芯片之间的通信,使内存读写模块和pcie模块可以通过axi总线读写内存芯片。

42.图2所示内存读写模块完成串口模块的发送fifo单元和接收fifo单元与内存芯片之间的数据转移控制,实现fifo和内存的二级数据缓存。内存读写模块包括内存读通路和内存写通路。

43.内存读通路将内存中的发送数据通过串口模块发送。主机通过pcie模块的axi总线将要发送的数据写入内存芯片的存储区域中,并更改该区域的写指针;fpga程序循环查询内存芯片中32个发送区域中的读指针和写指针,如果两个指针位置不同,则通过axi总线读取内存中的数据并写入对应串口模块中的发送fifo单元中,然后更更新内存区域的读指针;内存写通路循环查询串口模块0~串口模块31的接收fifo单元,如果接收fifo单元中有数据,则将数据读出并通过axi总线写入内存相应区域,更新该内存区域的写指针,并产生中断请求信号到中断产生模块;

44.由于串口路数较多,如果每一路都能产生中断会造成主机的中断丢失,因此将32

路串口分为8组,每4路串口1组,共用一个中断,因此总共有8个中断。图2所示中断产生模块接收到内存读写模块产生的某一个中断请求信号后,将连接到pcie模块的中断输出信号置1,使pcie模块产生主机中断;主机响应中断后,通过pcie模块的axi总线读取内存相应区域的数据,更新该区域的读指针,并通过pcie模块的axi

‑

lite总线给中断产生模块发送应答信号,中断产生模块将中断输出清零。

45.接下来结合图3对串口模块进行如下详细描述。

46.参照图3,示出了本发明实施例提供的一种串口模块的示意图,如图3所示,串口模块按照数据流方向可分为数据接收通路和数据发送通路:数据接收通路中,接收模块通过接收引脚接收串口波形信号并转换为字节数据发送到接收fifo单元,内存读写模块通过判断接收fifo单元中的空信号来读取接收fifo单元缓存的数据;数据发送通路中,内存读写模块发送的字节数据被串口模块写入发送fifo单元,发送模块将发送fifo单元中的字节数据转换为串口波形,经发送引脚发送到rs485电平转换芯片。

47.接下来,结合图4对本发明实施例提供的串口模块的发送单元进行如下详细描述。

48.参照图4,示出了本发明实施例提供的一种串口发送单元的示意图,如图4所示,串口发送单元通过状态机实现串口波形到字节数据的转换,状态机包括空闲、发送读使能,锁存发送数据,发送起始位,发送数据位,发送停止位。当发送fifo单元的空信号为0时,状态机开始一个字节数据的发送。

49.接下来,结合图5对本发明实施例提供的串口模块的接收单元进行如下详细描述。

50.参照图5,示出了本发明实施例提供的一种串口接收单元的示意图,如图5所示,串口接收单元通过状态机实现字节数据到串口波形的转换,状态机包括空闲、接收起始位、接收数据位、接收停止位、发送写使能。当接收引脚出现下降沿时,状态机开始一个字节数据的接收。

51.本发明实施例提供的32路rs485接口卡的实现系统,相较于现有技术具有如下有益效果:

52.相比传统的专用串口芯片方法更加灵活,扩展性更好,而采用多路rs485串行接口的两级缓存方法,即fifo和内存芯片两级缓存,解决了多路rs485串行接口同时通信的丢包问题,该方法同样适用于其他类型的多路接口电路中;并且给出了fpga和上位机的中断处理方法,提高了系统的效率,并解决了中断过多导致主机丢中断的问题。

53.本技术所述具体实施方式可以使本领域的技术人员更全面地理解本技术,但不以任何方式限制本技术。因此,本领域技术人员应当理解,仍然对本技术进行修改或者等同替换;而一切不脱离本技术的精神和技术实质的技术方案及其改进,均应涵盖在本技术专利的保护范围中。

54.本发明说明书中未作详细描述的内容属本领域技术人员的公知技术。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。