1.本发明属于计算技术领域,涉及一种实现素数域大整数模乘计算加速的方法。

背景技术:

2.随着科技的不断进步,计算机技术的飞速发展,用户对隐私保护有了更高的要求,密码学也随之被大量应用到网络通信技术中。例如,电子商务、软件分发等面向海量用户的互联网衍生产业通过密钥协商和数字签名实现在互联网上的隐私保护和安全通信。大整数模乘是许多非对称密码算法的核心计算负载。世界主流的非对称密码算法ecc(elliptic curve cryptography)的主要计算负载是素数域的大整数模乘。因此,素数域大整数模乘的运算速度直接影响到密钥协商及数字签名实现的速率,针对素数域中的大整数模乘高性能实现的研究十分重要。

3.gpus(graphics processing units)在计算机图形和图像处理方面非常高效,因而更加擅长浮点数的运算。gpus的浮点数的计算能力在过去十年间增长超过十倍。此外,nvidia公司推出的cuda并行计算框架使得原本只适用于图形处理计算的gpus计算资源也可以用于加速科学计算。很多研究人员利用gpus的计算资源加速主流的密码原语。例如,pan等人利用gpus的定点数计算能力加速ecdsa,niall等人利用gpus的双精度浮点数计算能力加速rsa,吞吐量都达到了新的峰值。为了适应gpus浮点数计算能力发展快速这一特点,本发明结合基于双精度浮点数的积和熔加指令和整数域算数指令,加速素数域的大整数模乘运算。

4.当前计算机基本数据类型有对应的固定字长,大整数在计算机中无法通过基本数据类型直接表示,研究人员一般拆分大整数,用多个基本数据类型表示一个大整数,采用多精度计算方式计算大整数模乘。

5.本发明使用的双精度浮点数格式符合ieee 754所规定的浮点数标准。ieee754标准中一个浮点数由符号位,阶码和尾码组成,其中尾码包含1位隐含位和若干位分数部分。一个双精度浮点数包含1位符号位,12位阶码,1位隐含位和52位分数部分,隐含位即在计算机中不显示表示。

技术实现要素:

6.本发明提供一种实现素数域大整数模乘计算加速的方法,能够充分利用计算资源的双精度浮点计算能力,提升大整数模乘的计算速度。

7.一种实现素数域大整数模乘计算加速的方法,其步骤为:

8.1)将定义在素数域f

p

上长度为k比特的大整数a和b分为n段,前(n

‑

1)段每段为w比特,第n段为r比特,w≥r;其中,p为2

k

‑

σ,σ为小于2

w

的素数;

9.2)将被乘数a、乘数b的每段分别转化为双精度浮点数;采用积和熔加运算对被转化后的被乘数a、乘数b进行乘加操作,并将运算结果转化为一定点数r;

10.3)将该定点数r分为2n段,在r数值不变的情况下,将r的前(2n

‑

1)段的段长设置为

w比特;利用乘法操作和加法操作将r约减为n段定点数利用乘法操作,加法操作和移位操作将超过k比特的部分消减,使得为k比特的定点数;

11.4)判断是否为所选素数域上的整数,如果是所选素数域上的整数,则即为大整数a和大整数b的模乘结果;如果不是所选素数域上的整数,则将减去p作为大整数a和大整数b的模乘结果。

12.其中,“大整数”是指无法仅用一个双精度浮点数表示的整数。

13.进一步的,被乘数a和乘数b的分段长度其中52为双精度浮点数的尾码长度;被乘数a和乘数b的前(n

‑

1)段的比特长度w和第n段比特长度r满足等式(n

‑

1)

×

w r=k,并且在52≥w≥r的情况下,使得w

‑

r尽量小。

14.进一步的,对被乘数和乘数分段后,a[0:n

‑

1]表示被乘数a的第0~(n

‑

1)的n个段,a’[0:n

‑

1]为a[0:n

‑

1]的浮点数形式,b[0:n

‑

1]表示乘数的第0~(n

‑

1)的n个段,b’[0:n

‑

1]为b[0:n

‑

1]的浮点数形式。

[0015]

进一步的,所述采用积和熔加运算对被转化后的被乘数a、乘数b进行乘加操作,包括:首先初始化2n个定点数记为r[0:2n

‑

1];其次按照段扫描的大整数乘法次序∑

i,j

a'[i]

·

b'[j],计算被乘数a’的一个段a’[i]和乘数b’的一个段b’[j]与加数c0的乘加结果m

ij

[0],然后计算被乘数a’的一个段a’[i]和乘数b’的一个段b’[j]与加数c1的乘加结果m

ij

[1],其中0≤i,j<n;设conv_2_bin(x)的操作为求x的二进制形式,将conv_2_bin(m

ij

[0])累加到定点数r[i j 1]中,将conv_2_bin(m

ij

[1])累加到r[i j]中。

[0016]

进一步的,2n个定点数r[0:2n

‑

1]的初始化方法是:当t∈[0,n

‑

1]时,r[t]=

‑

[(t

×

(0x433 w) (t 1)

×

0x433)&0xfff]<<52,当t∈[n,2n

‑

1]时,r[t]=

‑

[((t 1)

×

(0x433 w) t

×

0x433)&0xfff]<<52。其中,0x433为双精度浮点数阶码位的偏移量1023加上52的十六进制形式。0xfff为2

12

‑

1的十六进制形式。

[0017]

进一步的,加数c0的值为2

52

w,加数c1的值为2

52 w

2

52

‑

m

ij

[0]。

[0018]

进一步的,将r的前(2n

‑

1)段的段长设置为w比特的方法为:r

t 1

=r

t 1

(r

t

>>w),t∈[0,2n

‑

2]。其中,r

t

表示r中的第t 1段,r

t 1

表示r中的第t 2段。

[0019]

进一步的,所述利用乘法操作和加法操作将r约减为n段定点数包括:约减后的取值范围为[0,2

k

σ

·2digit

‑

r

),其中digit为一个双精度浮点数的比特长度,由于a和b为大整数,其比特长度k远大于一个双精度浮点数的比特长度,所以即

[0020]

进一步的,表示的第0~(n

‑

1)的n个段,记的高digit

‑

r位为进位carry,根据的范围可知,carry的取值为0或1;所述利用乘法操作,加法操作和移位操作将超过k比特的部分消减,使得为k比特的定点数,包括:首先令为k比特的定点数,包括:首先令其中mask

r

为2

r

‑

1;然后当t∈[0,n

‑

2]

时,令经过进位消减的的取值范围为:当carry为0的时候,当carry为1的时候,由于σ为小素数且digit远小于k,所以进位消减后的取值范围可统一为[0,2

k

‑

1]。

[0021]

进一步的,如果小于素数p,则为大整数a和大整数b相乘再对p取模的结果;如果大于素数p,则为大整数a和大整数b相乘再对p取模的结果。

[0022]

与现有技术相比,本发明的积极效果为:

[0023]

本发明在计算素数域大整数模乘时,首先将被乘数与乘数拆分并转化为多个双精度浮点类型的数值,在浮点数转化过程中,充分利用了双精度浮点数尾数中的分数部分;利用浮点数的积和熔加指令对转化后的被乘数和乘数进行乘加操作,并将乘加结果转换为二进制形式累加到定点数中,对存放累加结果的定点数进行位数约减得到模乘结果,本方法利用浮点数计算指令实现素数域大整数模乘,构思新颖,计算高效,最大化利用计算机的双精度浮点数存储格式,提升了大整数模乘的计算速度。

附图说明

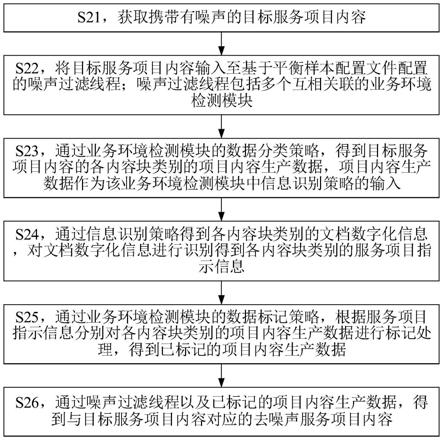

[0024]

图1为本发明的利用浮点数计算指令实现素数域大整数模乘计算加速方法流程图。

具体实施方式

[0025]

下面对本发明的技术方案进行详细说明,但是本发明的保护范围不局限于所述实施例。

[0026]

对于给定的素数域f

p

,p=2

221

‑

3,a和b为素数域f

p

上的大整数,计算a乘以b对p取模时,利用浮点数计算指令实现素数域大整数模乘计算加速方法,主要包括以下步骤:

[0027]

1)将长度为221比特的被乘数a和乘数b分别分为n段,n=5;其中,前4段每段为45比特,第5段为41比特;

[0028]

2)对被乘数和乘数分段后,a[0:4]表示被乘数a的第0~4的5个段,b[0:4]表示乘数b的第0~4的5个段。将a[0:4]的每一段转化为双精度浮点形式记为a’[0:4],将b[0:4]的每一段转化为双精度浮点形式记为b’[0:4]。

[0029]

3)按照段扫描的大整数乘法次序∑

i,j

a'[i]

·

b'[j],i,j∈[0,4],先计算被乘数a’的一个段a’[i],和乘数b’的一个段b’[j]与加数c0的乘加结果m

ij

[0],其中,c0=2

97

;然后计算被乘数a’的一个段a’[i],和乘数b’的一个段b’[j]与加数c1的乘加结果m

ij

[1],其中c1=2

97

2

52

‑

m

ij

[0]。

[0030]

4)初始化定点数r,将其分为2n段,记为r[0:2n

‑

1];r[0:2n

‑

1]的初始化方式为:

[0031][0032]

5)设conv_2_bin(x)的操作为求x的二进制形式,将conv_2_bin(m

ij

[0])累加到定点数r[i j 1]中,将conv_2_bin(m

ij

[1])累加到r[i j]中。

[0033]

6)将r[0:9]的前9段的段长设置为45比特,设置方法为:

[0034]

r

t 1

=r

t 1

(r

t

>>45),t∈[0,8]

[0035]

7)利用乘法操作和加法操作将10段定点数r约减为5段定点数的计算方法为:

[0036][0037]

即

[0038]

约减后的取值范围为[0,2

221

3

·223

)。

[0039]

8)表示的第0~(n

‑

1)的n个段,记的高23位为进位carry,根据步骤7)中的范围可知,carry的取值为0或1;利用乘法操作,加法操作和移位操作将n段定点数消减为221比特。令消减为221比特。令然后当t∈[0,3]时,令经过进位消减操作后,

[0040]

9)判断是否小于素数p,若小于素数p,则为大整数a和大整数b相乘再对p取模的结果;如果大于素数p,则为大整数a和大整数b相乘再对p取模的结果。

[0041]

最后,通过对密码学中常用的7个素数域,用本发明提出的利用浮点数计算指令实现素数域大整数模乘计算加速方法计算相关参数,得出以下表1。

[0042]

表1.常用素数域的分组长度和段长选择

[0043]

pkσnwr2

221

‑

32213545412

222

‑

117222117545422

251

‑

92519551472

255

‑

1925519551512

382

‑

105382105848462

383

‑

187383187848472

414

‑

174141785250

[0044]

基于同一发明构思,本发明的另一实施例提供一种非对称密码方法,其中包含素数域大整数模乘计算,所述素数域大整数模乘采样本发明的方法进行计算。

[0045]

基于同一发明构思,本发明的另一实施例提供一种电子装置(计算机、服务器、智能手机等),其包括存储器和处理器,所述存储器存储计算机程序,所述计算机程序被配置为由所述处理器执行,所述计算机程序包括用于执行本发明方法中各步骤的指令。

[0046]

基于同一发明构思,本发明的另一实施例提供一种计算机可读存储介质(如rom/ram、磁盘、光盘),所述计算机可读存储介质存储计算机程序,所述计算机程序被计算机执行时,实现本发明方法的各个步骤。

[0047]

以上公开的本发明的具体实施例,其目的在于帮助理解本发明的内容并据以实施,本领域的普通技术人员可以理解,在不脱离本发明的精神和范围内,各种替换、变化和修改都是可能的。本发明不应局限于本说明书的实施例所公开的内容,本发明的保护范围以权利要求书界定的范围为准。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。