具有集成存储器一致性互连的存储器和存储控制器

1.其他申请的交叉引用

2.本技术要求2020年5月4日提交的标题为“memory and storage controller with integrated memory coherency interconnect”的美国临时专利申请第63/019,698号和2020年9月2日提交的美国非临时专利申请第17/010,739号的优先权,这些申请出于所有目的通过引用并入本文。

3.发明背景

4.越来越多的技术产生大量数据。例如,社交媒体网站、自主车辆、物联网、手机应用、工业设备和传感器以及线上线下交易,都产生了海量的数据。在某些情况下,认知计算和人工智能被用来分析这些数据。这些不断增长的数据源的结果是对存储器(memory)和存储装置(storage)的需求增加。因此,期望用于存储器和存储装置的改进的技术。

5.附图简述

6.在以下详细描述和附图中公开了本发明的各种实施例。

7.图1a示出了系统100的示例,其中处理器102(例如,cpu或加速器)经由cxl芯片104和存储器/存储控制器(memory/storage controller)106访问dram或其他介质108。

8.图1b示出了连接到一个或更多个存储器/存储控制器ip核(core)的cxl ip核的示意图。

9.图2a示出了改进的系统200的示例,其中处理器202(例如,cpu或加速器)经由集成控制器206访问dram或其他介质208,该集成控制器206将cxl和ddr/其他存储协议(storage protocol)集成在单个设备中。

10.图2b示出了单个集成控制器ip核206的示意图。

11.图2c示出了单个集成控制器ip核206的另一个示意图。

12.图3a示出了在传统系统中需要更多的资源,在传统系统中,cpu或加速器经由cxl芯片和存储器/存储控制器访问dram或其他介质。

13.图3b示出了,在cpu或加速器经由集成控制器访问dram或其他介质的系统中,需要更少的资源,该集成控制器将cxl和ddr/其他存储协议集成在单个设备中。

14.图4示出了用于改进的系统的过程400的示例,在该改进的系统中,处理器经由集成控制器访问dram或其他介质,该集成控制器将cxl和ddr/其他存储协议集成在单个设备中。

15.详细描述

16.本发明可以以多种方式实现,包括作为过程、装置、系统、物质的组合、体现在计算机可读存储介质上的计算机程序产品、和/或处理器,例如被配置为执行存储在耦合到处理器的存储器上和/或由该存储器提供的指令的处理器。在本说明书中,这些实现或者本发明可以采取的任何其他形式可以被称为技术。通常,在本发明的范围内,可以改变所公开的过程的步骤顺序。除非另有说明,否则被描述为被配置为执行任务的诸如处理器或存储器的组件可以被实现为被临时配置为在给定时间执行任务的通用组件或被制造为执行任务的特定组件。如本文所使用的,术语“处理器”指的是被配置成处理数据(例如计算机程序指

令)的一个或更多个设备、电路和/或处理核心。

17.下面提供了本发明的一个或更多个实施例的详细描述以及示出本发明原理的附图。结合这些实施例描述了本发明,但是本发明不限于任何实施例。本发明的范围仅由权利要求限定,并且本发明包括许多替代物、修改和等同物。为了提供对本发明的全面理解,在以下描述中阐述了许多具体细节。这些细节是出于示例的目的而提供的,并且本发明可以根据权利要求来实施,而不需要这些具体细节中的一些或全部。为了清楚起见,没有详细描述与本发明相关的技术领域中已知的技术材料,以便不会不必要地模糊本发明。

18.双数据速率同步动态随机存取存储器(double data rate synchronous dynamic random

‑

access memory,ddr sdram)是计算机中使用的双数据速率(ddr)同步动态随机存取存储器(sdram)类存储器集成电路。随着动态随机存取存储器(dram)的密度的不断增加和接口速度的不断提高,存储器行业经历了多代,包括第1代ddr1、第2代ddr2、第3代ddr3、第4代ddr4和第5代ddr5行业标准。

19.pci express(外设部件互连express),官方缩写为pcie或pci

‑

e,是高速串行计算机扩展总线标准;它是个人计算机图形卡、硬盘、固态驱动器(ssd)、wi

‑

fi和以太网硬件连接的通用主板接口。

20.目前,计算机系统利用集成的ddr存储器控制器作为存储器子系统,并且利用pcie进行存储。然而,这些计算机系统是低效的,因为ddr的软件堆栈与pcie的非常不同。例如,基于ddr的系统是一致的(coherent),而基于pcie的系统则不是。

21.为了解决这个问题,业界设计了一种高性能i/o总线体系结构,称为计算快速链路(compute express link,cxl)(有关更多信息,请参见https://www.computeexpresslink.org/)。cxl可用于互连外围设备,这些外围设备可以是传统的非一致i/o设备,也可以是具有额外功能的加速器。cxl使cxl总线上的所有事务一致。

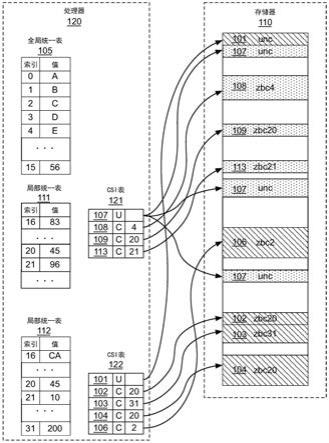

22.在其他技术中,中央处理单元(cpu)或加速器经由cxl芯片和存储器/存储控制器访问动态随机存取存储器(dram)或其他介质。其他介质包括存储介质、永久介质等。图1a示出了系统100的示例,其中处理器102(例如,cpu或加速器)经由cxl芯片104和存储器/存储控制器106访问dram或其他介质108。存储器/存储控制器106发送和接收在处理器和处理器的存储器或存储装置之间流动的数据。如图1a所示,处理器102经由cxl总线与cxl芯片104通信。cxl芯片104经由专有总线与存储器/存储控制器106通信。存储器/存储控制器106经由低功率ddr sdram(lpddr sdram)总线、ddr总线、onfi总线、me toggle总线或其他介质接口与多个dram或其他介质108通信。ddr包括ddr1、ddr2、ddr3、ddr4和ddr5。

23.图1b示出了连接到一个或更多个存储器/存储控制器ip核的cxl ip核的示意图。cxl ip核104包括pcie物理接口(phy)104a、cxl控制器104b和片上系统(soc)接口104c(例如高级可扩展接口(axi))。cxl ip核104经由专有总线,例如片上网络(noc)总线或soc总线,与一个或更多个存储器/存储控制器ip核106通信。存储器/存储控制器ip核106包括诸如axi的soc接口106b。存储器/存储控制器ip核106还包括存储器或存储控制器106c,例如lpddr、ddr或存储装置级存储器(storage class memory,scm)控制器。存储器/存储控制器ip核106还包括phy 106d,例如lpddr phy或ddr phy。

24.但是,如图1a和图1b所示的经由cxl芯片和存储器/存储控制器访问dram或其他介质会导致更高的延迟,并可能产生难以调试的互操作性问题。此外,需要更多的逻辑,这增

加了芯片面积和成本。

25.本技术中的控制器设备包括被配置为经由互连总线接收数据操作请求的通信接口。该设备包括集成互连协议组件,该集成互连协议组件在控制器设备上并被配置为处理经由互连总线的通信,该集成互连协议组件支持控制器设备外部的多个不同处理设备之间的一致性(coherency)。该设备包括同一控制器设备上的集成存储器或存储控制器组件,并且被配置为处理数据操作请求,包括被配置为管理与控制器设备外部的存储器或数据存储设备的通信。

26.图2a示出了改进的系统200的示例,其中处理器202(例如,cpu或加速器)经由集成控制器206访问dram或其他介质208,该集成控制器206将cxl和ddr/其他存储协议集成在单个设备中。其他介质包括存储介质、永久介质等。dram或其他介质208的示例包括低功率ddr sdram(lpddr sdram)、ddr和存储装置级存储器(scm)。如图2a所示,cpu或加速器202经由cxl总线与集成控制器206通信。而且,单个集成控制器206经由低功率ddr sdram(lpddr sdram)总线、ddr总线、onfi总线、me toggle总线或其他介质接口与多个dram和/或其他介质208通信。例如,单个集成控制器206可以包括用于不同介质类型的多个控制器。单个集成控制器206可以经由不同于ddr或onfi的协议(包括其他专有协议)与其他类型的设备通信。

27.图2b示出了单个集成控制器ip核206的示意图。单个集成控制器ip核206包括通信接口,该通信接口被配置成经由诸如cxl总线的互连总线接收数据操作请求(例如,读或写请求)。通信接口可以是pcie物理接口(phy)206a。单个集成控制器ip核206还包括cxl控制器206b。cxl控制器206b是单个集成控制器ip核206上的集成互连协议组件,其被配置为处理经由互连总线的通信,该集成互连协议组件支持集成控制器ip核206外部的多个不同处理设备(例如,cpu或加速器)之间的一致性。集成控制器ip核206还包括一个或更多个集成存储器或存储控制器组件,并且每个集成存储器或存储控制器组件被配置为处理数据操作请求,包括被配置为管理与集成控制器ip核206外部的存储器或存储设备的通信。cxl控制器206b经由定制和优化的接口与一个或更多个存储器/存储控制器206c通信。例如,一个或更多个存储器/存储控制器206c可以包括具有lpddr phy 206d的lpddr控制器、具有ddr phy 206d的ddr控制器和具有scm phy 206d的scm控制器。cxl控制器206b经由定制和优化的接口与每个存储器/存储控制器直接连接。改进的系统200消除了传统系统100中对cxl ip核104上的soc接口104c和存储器/存储控制器ip核106上的soc接口106b的需要。soc接口是可以从改进的系统中移除的翻译器的一个示例。改进的系统200还消除了使用标准总线以在cxl ip核104和存储器/存储控制器ip核106之间进行通信的需要。图2c示出了单个集成控制器ip核206的另一个示意图。

28.在一些实施例中,集成控制器ip核206被集成到另一个芯片中。例如,集成控制器ip核206可以被放置在同一管芯上或者被集成为处理器(例如,cpu或加速器)的组成部分。在另一个示例中,集成控制器ip核206可以被放置在同一管芯上或者被集成为专用集成电路(asic)的一部分,并且该asic可以通过cxl总线连接到处理器。

29.改进的系统有很多优点。改进的系统使用了简化的通信方法,减少或消除了开销,具有更低的延迟和更少的故障点,并且更易于调试。此外,改进的系统简化了逻辑,这减少了芯片面积和成本。

30.图3a示出了在传统系统中需要更多的资源,在传统系统中,cpu或加速器经由cxl

芯片和存储器/存储控制器访问dram或其他介质。如图3a所示,cxl芯片包括cxl队列、缓冲器、翻译器、同步器或其他电路。存储器/存储控制器包括它自己的队列、缓冲器、翻译器、同步器或其他电路。例如,如图1b所示,cxl ip核104包括在不同子模块之间的cxl队列和缓冲器(104d、104e和104f)。存储器/存储控制器ip核106包括它自己的队列和缓冲器(106a、106e和106f)。cxl ip核104中的soc接口104c和存储器/存储控制器ip核106中的soc接口106b都具有它们自己的队列和缓冲器的集合(104f和106a)。

31.图3b示出了,在cpu或加速器经由集成控制器访问dram或其他介质的系统中,需要更少的资源,该集成控制器将cxl和ddr/其他存储协议集成在单个设备中。统一的队列、缓冲器、翻译器或其他电路可以在统一设备上的cxl和其他协议之间共享。因此,改进的系统使用了简化的通信方法,减少或消除了开销,具有更低的延迟和更少的故障点,并且更容易调试。例如,如图2c所示,cxl控制器206b与一个或更多个存储器/存储控制器206c中的每一个共享统一的队列或缓冲器206e,从而将队列或缓冲器资源减少一半。

32.改进的系统的另一个优点是,它提供了统一的存储器系统。在传统系统100中,cpu 102可能只可以访问存储器或存储装置的一部分。例如,如图1a所示,cpu 102可能只可以访问两组(用纯色表示)存储器或存储装置108,但不能访问另外两组存储器或存储装置(用影线色表示)。相比之下,在图2a中的改进的系统200中,cpu 202获得对全部四组dram或其它介质208(用纯色表示)的完全访问权。

33.图4示出了用于改进的系统的过程400的示例,在该改进的系统中,处理器经由集成控制器访问dram或其他介质,该集成控制器将cxl和ddr/其他存储协议集成在单个设备中。在步骤402,由控制器设备的通信接口经由互连总线接收数据操作请求。在一些实施例中,控制器设备的通信接口包括pcie phy接口。在一些实施例中,互连总线包括cxl总线。

34.在步骤404,经由互连总线的通信由控制器设备上的集成互连协议组件处理。集成互连协议组件支持控制器设备外部的多个不同处理设备之间的一致性。在一些实施例中,集成存储器或存储控制器组件可以是ddr sdram控制器、lpddr控制器或scm控制器。

35.在步骤406,数据操作请求由同一控制器设备上的集成存储器或存储控制器组件处理。集成存储器或存储控制器组件被配置成管理与控制器设备外部的存储器或数据存储设备的通信。存储器或数据存储设备可以是lpddr sdram、ddr sdram或scm。

36.在一些实施例中,控制器设备上的集成互连协议组件和控制器设备上的集成存储器或存储控制器组件经由单个定制和优化的接口直接连接。在一些实施例中,控制器设备上的集成互连协议组件和控制器设备上的集成存储器或存储控制器组件直接连接,而不需要集成互连协议组件上的单独接口或集成存储器或存储控制器组件上的另一单独接口。在一些实施例中,控制器设备上的集成互连协议组件和控制器设备上的集成存储器或存储控制器组件在没有标准化总线的情况下直接连接。在一些实施例中,使用队列或缓冲器的统一集合来存储数据,其中队列或缓冲器的统一集合在控制器设备上的集成互连协议组件和控制器设备上的集成存储器或存储控制器组件之间共享。在一些实施例中,用于控制器设备上的集成互连协议组件的队列或缓冲器的集合和用于控制器设备上的集成存储器或存储控制器组件的队列或缓冲器的另一集合被组合成队列或缓冲器的单个统一集合。

37.尽管为了清楚理解的目的,已经对前述实施例进行了一些详细描述,但是本发明不限于所提供的细节。有许多实现本发明的替代方式。所公开的实施例是说明性的而非限

制性的。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。