1.本技术涉及深度学习技术领域,特别是涉及一种神经网络配置方法、装置、计算机设备和存储介质。

背景技术:

2.在最近几年,卷积神经网络在深度学习领域已经取得了巨大的成功。然而,如图形分类的推理任务仍然是一个计算负荷极高的工作,需要构建特别应用程序的硬件,以及在低功耗硬件上高效执行推理程序的库。gpgpu(general

‑

purpose computing on graphics processing units,通用图形处理单元)是其中一个广为应用的硬件。此外,为新兴的神经网络体系结构开发高效的子程序库是一项非常重要的工作。这种方法在现有库的基础上提供了另一种层优化,使推理引擎能够充分利用底层硬件的功能和效率,而不是来自传统库的接口。

3.如cudnn(compute

‑

unified device architecture deep neural network library,基于cuda的深度神经网络库)的深度学习的函数库,向用户提供了用于将数据层的输入、过滤、输出的张量存储至内存的配置选项。相应地,如tensorflow、pytorch等的深度学习架构,在发现这些配置选项对常用的神经网络有用时,则会采用这些配置选项,以进一步优化神经网络执行训练任务或推理任务的表现。

4.然而,由于推理引擎的开发人员在进行开发工作时通常是直接使用如cudnn的库,而不是通过上述深度学习框架,因此也就无法对神经网络的张量存储相关的参数进行有效的配置,从而影响了神经网络的运行效率。

5.因此,现有的神经网络配置方法存在着影响神经网络运行效率的问题。

技术实现要素:

6.基于此,有必要针对上述技术问题,提供一种神经网络配置方法、装置、计算机设备和存储介质。

7.第一方面,提供了一种神经网络配置方法,包括:

8.确定神经网络中的待配置卷积层;所述待配置卷积层具有多种可用的张量数据存储格式;

9.在多种所述张量数据存储格式中,选取待测试张量数据存储格式;

10.获取所述待配置卷积层采用所述待测试存储格式执行基准测试任务时的运行延迟;

11.根据所述运行延迟,确定所述待配置卷积层的目标存储格式;

12.返回至所述确定神经网络中的待配置卷积层的步骤,直至确定所述神经网络的各个卷积层各自的目标存储格式。

13.在一个实施例中,所述根据所述运行延迟,确定所述待配置卷积层的目标存储格式,包括:

14.获取当前优化运行延迟;

15.当所述运行延迟小于所述当前优化运行延迟时,将所述当前优化运行延迟的数值更新为所述运行延迟的数值,以及,将预设的当前优选存储格式标识更新为所述待测试存储格式的标识;

16.返回至所述在多种所述张量数据存储格式中,选取待测试存储格式的步骤,直至遍历多种可用的所述张量数据存储格式后,将所述当前优选存储格式标识对应的张量数据存储格式,确定为所述待配置卷积层的目标存储格式。

17.在一个实施例中,所述获取所述待配置卷积层采用所述待测试存储格式执行基准测试任务时的运行延迟,包括:

18.将所述待测试存储格式的标识传入预设的基准测试函数;

19.运行所述基准测试函数,得到所述基准测试函数返回的所述运行延迟。

20.在一个实施例中,还包括:

21.当所述运行延迟不小于所述当前优化运行延迟时,返回至所述在多种所述张量数据存储格式中,选取待测试存储格式的步骤。

22.在一个实施例中,所述张量数据存储格式包括nchw、nhwc、chwn中的至少一种。

23.第二方面,提供了一种神经网络配置装置,包括:

24.确定模块,被配置为确定神经网络中的待配置卷积层;所述待配置卷积层具有多种可用的张量数据存储格式;

25.格式选取模块,被配置为在多种所述张量数据存储格式中,选取待测试张量数据存储格式;

26.延迟获取模块,被配置为获取所述待配置卷积层采用所述待测试存储格式执行基准测试任务时的运行延迟;

27.目标格式确定模块,被配置为根据所述运行延迟,确定所述待配置卷积层的目标存储格式;

28.返回模块,被配置为返回至所述确定神经网络中的待配置卷积层的步骤,直至确定所述神经网络的各个卷积层各自的目标存储格式。

29.在一个实施例中,所述目标格式确定模块,还被配置为:

30.获取当前优化运行延迟;

31.当所述运行延迟小于所述当前优化运行延迟时,将所述当前优化运行延迟的数值更新为所述运行延迟的数值,以及,将预设的当前优选存储格式标识更新为所述待测试存储格式的标识;

32.返回至所述在多种所述张量数据存储格式中,选取待测试存储格式的步骤,直至遍历多种可用的所述张量数据存储格式后,将所述当前优选存储格式标识对应的张量数据存储格式,确定为所述待配置卷积层的目标存储格式。

33.在一个实施例中,所述延迟获取模块,还被配置为:

34.将所述待测试存储格式的标识传入预设的基准测试函数;

35.运行所述基准测试函数,得到所述基准测试函数返回的所述运行延迟。

36.第三方面,提供了一种计算机设备,包括存储器和处理器,所述存储器存储有计算机程序,所述处理器执行所述计算机程序时实现上述第一方面的神经网络配置方法。

37.第四方面,提供了一种计算机可读存储介质,其上存储有计算机程序,所述计算机程序被处理器执行时实现上述第一方面的神经网络配置方法。

38.上述神经网络配置方法、装置、计算机设备和计算机可读存储介质,首先确定神经网络中待配置卷积层可用的多种张量数据存储格式,然后从中选取出待测试张量数据存储格式,并获取待配置卷积层采用待测试张量数据存储格式执行基准测试任务的运行延迟,根据该运行延迟确定待配置卷积层的目标存储格式,最后针对下一个待配置卷积层进行优化配置,直至确定各个卷积层各自的目标存储格式,从而对神经网络中的每个卷积层均独立地进行了优化配置,提升了访问内存的张量数据的效率,从而提升了神经网络执行推理任务的效率。

附图说明

39.图1是一个实施例的一种神经网络配置方法的流程示意图;

40.图2是一个实施例的一种输入图像的示意图;

41.图3是一个实施例的一种四维图像在内存中存储的示意图;

42.图4是一个实施例的一种基于四维张量进行卷积运算的示意图;

43.图5是一个实施例的张量数据在内存中的不同数据存储格式的示意图;

44.图6是一个实施例的一种遍历各种张量数据存储格式的步骤的流程示意图;

45.图7是一个实施例的一种神经网络配置装置的结构框图;

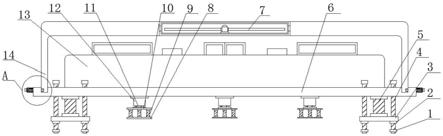

46.图8是一个实施例的一种计算机设备的内部结构图。

具体实施方式

47.为了使本技术的目的、技术方案及优点更加清楚明白,以下结合附图及实施例,对本技术进行进一步详细说明。应当理解,此处描述的具体实施例仅仅用以解释本技术,并不用于限定本技术。

48.在一个实施例中,如图1所示,提供了一种神经网络配置方法。本实施例提供的神经网络配置方法,可以应用于服务器或服务器组成的服务器集群,也可以应用于各类终端,例如,可以是但不限于各种个人计算机、笔记本电脑、智能手机、平板电脑和便携式可穿戴设备。

49.首先需要说明的是,目前针对不同的处理器尽可能开发出用以高效执行深度学习任务的多个函数库。然而,开发一个优秀的用于卷积神经网络的函数库是极具挑战的任务,其原因主要由以下几个方面:

50.1)不同的硬件代差,甚至同一个硬件制造商制造的不同系列的处理器,可能都有着不同的运算能力;

51.2)在内存中的数据结构(也称为数据存储格式)会极大影响在gpu上执行数学运算操作时的延迟。对于一些数学运算操作,内存中特定的数据结构比起其他数据结构更有助于降低访问延迟;

52.3)对于新开发的神经网络,由于在新的神经网络中,访问数据的层(即神经网络中执行特定数学运算操作的层)可能不同于其他神经网络,因此,如何为新的神经网络选择内存中的数据结构变得困难。

53.目前,由于推理引擎的开发人员在进行开发工作时通常是直接使用cudnn库,而不是通过上述深度学习框架,因此也就无法直接利用深度学习框架选择优化的数据结构。然而,在深度学习函数库层面,数据结构的变化,对于用户来说变得不可预测且不可靠,用户难以依赖经验来判断所选择的数据结构的优劣,如果所选择的数据结构并不适用于神经网络,可能会增加了运行延迟,影响神经网络的运行效率。

54.针对上述问题,本公开提出了一种神经网络配置方法,以实现神经网络各层卷积层的数据结构的完全自动化配置,以使得神经网络可以高效运行。该方法可以包括以下步骤:

55.步骤s102,确定神经网络中的待配置卷积层;所述待配置卷积层具有多种可用的张量数据存储格式。

56.其中,张量数据存储格式用于描述张量数据在内存中存储的数据结构。

57.在一个实施例中,张量数据存储格式包括nchw、nhwc、chwn中的至少一种。

58.nchw、nhwc、chwn是目前较为常见的张量数据存储格式。当然,本领域技术人员可以根据本公开提供的思路将本技术的配置方法应用至各种张量数据存储格式。

59.在本实施例中,可以首先在神经网络的多个卷积层中确定出待配置卷积层,并确定底层库对该待配置卷积层所支持的张量数据存储格式,即,确定该待配置卷积层可用的张量数据存储格式。

60.需要补充说明的是,一个推理引擎需要经过多个阶段才能运行一个神经网络。首先,需要从输入文件中读取网络图形数据。读取图形数据后,将对其进行解析,并创建节点对象和连接。在执行推理任务之前,需要为每个节点配置适当的参数。最后,执行神经网络各层的引擎来完成相应的推理运算。其中,推理运算包括有卷积层基于一定的卷积算法所进行的卷积运算。

61.通常,在包括卷积层的神经网络中,输入张量(input tensor)、滤波器(filters)、输出张量(output tensor)均是四维的。在深度学习的卷积神经网络(cnn,convolutional neural networks)中,四维张量通过n、c、h、w四个字母来定义二维图像的格式。其中,n代表每批图像的数量(number of images in mini

‑

batch),c代表输入特征图的数量(number of input feature maps),h代表输入图像的高度(height of input image),w代表输入图像的宽度(width of input image)。

62.例如,如图2所示的一个实施例的一种输入图像的示意图,示出了一组n=1、c=3、h=5、w=4的图像,c=0、c=1、c=2该三个通道的图像,其像素元素均采用一组整数序列来表示。当在主函数(main function)中创建输入缓冲区时,四维图像将以nchw的格式存储在内存中。图3示出了一个实施例的一种四维图像在内存中存储的示意图。如图所示,从第一个通道(c=0)开始,像素元素按行优先的次序连续地存储在内存中。然后,继续第二个通道(c=1)和第三个通道(c=2),直至所有通道的像素元素存储至内存中。最后,如果存在有多批数据时(n>1),则继续处理下一批图像数据。

63.深度学习框架通常在内存中使用如nchw、nhwc等的张量数据存储格式。针对张量数据的内存访问模式会影响并行计算单元的执行时间,因此,选择不同的张量数据存储格式可能会影响神经网络的表现。因此,基于不同硬件或不同算法执行卷积任务,则可能会产生不同的运行延迟。

64.图4是一个实施例的一种基于四维张量进行卷积运算的示意图。如图所示,将nchw输入张量与kcrs权值张量进行卷积运算,产生nkpq输出张量,运算过程中输入、中间、输出数据均为四维张量。其中,k代表输出特征图的数量(number of output feature maps),r代表过滤器核的高度(height of filter kernel),s代表过滤器核的宽度(width of filter kernel)。

65.图5是一个实施例的张量数据在内存中的不同数据存储格式的示意图。如图所示,对于同一批张量数据,采用nchw、nhwc、chwn等不同的数据存储格式存储在内存中时,像素元素具有不同的排列方式。

66.具体地,为了针对神经网络中每个单独的卷积层进行优化配置,可以首先确定一个卷积层作为上述的待配置卷积层,在完成一个卷积层的配置后,再进行下一个卷积层的配置。

67.步骤s104,在多种所述张量数据存储格式中,选取待测试张量数据存储格式。

68.具体地,可以在多种可供选择的张量数据存储格式中,选取一个当前进行测试的格式,作为上述的待测试张量数据存储格式。

69.步骤s106,获取所述待配置卷积层采用所述待测试存储格式执行基准测试任务时的运行延迟。

70.具体地,可以将待测试张量数据存储格式对应的标识作为基准测试函数的测试参数,测试待配置卷积层,得到基准测试函数返回的待配置卷积层的运行延迟。

71.步骤s108,根据所述运行延迟,确定所述待配置卷积层的目标存储格式。

72.具体地,针对每个待测试张量数据存储格式,均可以得到对应的运行延迟。遍历多种张量数据存储格式,即可以根据多种张量数据存储格式所对应的运行延迟,确定最短运行延迟,由此,可以将最短运行延迟所对应的张量数据存储格式,确定为待配置卷积层的目标存储格式,从而,完成对神经网络的一个卷积层的张量数据存储格式的配置,使得该待配置卷积层可以采用使得运行延迟最短的张量数据存储格式将张量数据存储在内存中。

73.步骤s110,返回至所述确定神经网络中的待配置卷积层的步骤,直至确定所述神经网络的各个卷积层各自的目标存储格式。

74.具体地,在完成对神经网络的一个卷积层的配置后,可以对神经网络的下一个卷积层进行配置,直至完成神经网络中各个卷积层的配置。从而,使得每层卷积层均可以采用使得神经网络的运行延迟最短的张量数据存储格式将张量数据存储在内存中,从而提升推理运算的效率。

75.需要说明的是,本实施例中,以卷积层的配置优化为例子进行说明,但在实际应用中,还可以采用本实施例的神经网络配置对反卷积层进行配置优化。由于具体实施方式与上述针对卷积层的具体实施方式类似,在此不再赘述。

76.在上述的神经网络配置方法中,首先确定神经网络中待配置卷积层可用的多种张量数据存储格式,然后从中选取出待测试张量数据存储格式,并获取待配置卷积层采用待测试张量数据存储格式执行基准测试任务的运行延迟,根据该运行延迟确定待配置卷积层的目标存储格式,最后针对下一个待配置卷积层进行优化配置,直至确定各个卷积层各自的目标存储格式,从而对神经网络中的每个卷积层均独立地进行了优化配置,提升了访问内存的张量数据的效率,从而提升了神经网络执行推理任务的效率。

77.进一步地,由于遍历了各种可用的张量数据存储格式,避免了由于选择了次优配置而影响运行效率的问题。同时,配置过程实现了完全的自动化,无须用户参与,降低了开发成本。

78.进一步地,即使升级到新版本的库或者新一代硬件,仍然可以采用上述的神经网络配置方法进行配置优化,而无须更改代码内容,配置方法的通用性较高,从而降低了开发成本。

79.进一步地,上述的神经网络配置方法可以在配置阶段或者推理引擎预热阶段执行,因此,不会影响推理任务的执行效率。从而,在保证了神经网络执行推理任务的执行效率的同时,提升了神经网络的运行效率。

80.在一个实施例中,如图6所示,步骤s108可以具体包括以下步骤:

81.步骤s1081,获取当前优化运行延迟;

82.步骤s1082,当所述运行延迟小于所述当前优化运行延迟时,将所述当前优化运行延迟的数值更新为所述运行延迟的数值,以及,将预设的当前优选存储格式标识更新为所述待测试存储格式的标识;

83.步骤s1083,返回至步骤s104,直至遍历多种可用的所述张量数据存储格式后,将所述当前优选存储格式标识对应的张量数据存储格式,确定为所述待配置卷积层的目标存储格式。

84.具体地,可以预先设置一个当前优化运行延迟,将其初始化为最大值。在执行基准测试任务得到运行延迟后,将所得到的运行延迟与当前优化运行延迟进行比较。

85.当所得到的运行延迟小于当前优化运行延迟时,将当前优化运行延迟的数值,更新为所得到的运行延迟的数值。

86.例如,当前优化运行延迟为10ms(毫秒),执行基准测试任务后,所得到的运行延迟为8ms,所得到的运行延迟小于当前优化运行延迟,则可以将当前优化运行延迟更新为8ms,形成新的当前优化运行延迟。

87.此外,还可以预先设置一个当前优选存储格式标识,将其初始化为空值。当所得到的运行延迟小于当前优化运行延迟时,将预设的当前优选存储格式标识更新为待测试存储格式的标识。

88.例如,当前优化运行延迟为10ms,按照“nchw”执行基准测试任务后,所得到的运行延迟为8ms,所得到的运行延迟小于当前优化运行延迟,则可以将预设的当前优选存储格式标识更新为“nchw”的标识。

89.然后,返回至步骤s104,即,选取新的张量数据存储格式,并重复步骤s106、步骤s1081、步骤s1082。

90.需要说明的是,选取新的张量数据存储格式并重复执行步骤s106、步骤s1081、步骤s1082的过程中,当前优化运行延迟已经被更新为上一次执行基准测试任务时的运行延迟,如果本次的采用新的张量数据存储格式执行基准测试任务所得到的运行延迟小于当前优化运行延迟,则采用本次基准测试任务所得到的运行延迟的数值再次更新当前优化运行延迟的数值,并相应更新,反之,则不更新。

91.在遍历所有张量数据存储格式后,可以将当前优选存储格式标识对应的张量数据存储格式,确定为待配置卷积层的目标存储格式。

92.由此可见,本实施例通过迭代的方式不断更新当前优化运行延迟的数值,不断地逼近最短运行延迟,在遍历所有张量数据存储格式后,最后更新的当前优化运行延迟,即为待配置卷积层在特定张量数据存储格式的配置下执行卷积运算时所能达到的最短的运行延迟。相应地,最后更新的当前优选存储格式标识对应的张量数据存储格式,即为使得卷积层达到最优配置的张量数据存储格式。

93.上述的神经网络配置方法,通过迭代的方式得到使得卷积层达到最优配置的目标存储格式,整个配置过程无须复杂的运算,提升了神经网络的配置效率。

94.在一个实施例中,所述获取所述待配置卷积层采用所述待测试存储格式执行基准测试任务时的运行延迟,包括:

95.将所述待测试存储格式的标识传入预设的基准测试函数;运行所述基准测试函数,得到所述基准测试函数返回的所述运行延迟。

96.具体地,可以通过基准测试函数(benchmark function)来实现基准测试任务的执行。将待测试张量数据存储格式的标识作为函数参数传入至基准测试函数,并运行基准测试函数。基准测试函数运行后返回的时间数值,即为上述的运行延迟。

97.上述的神经网络配置方法,利用基准测试函数获取运行延迟,从而可以通过便捷的方式得到运行延迟,提升了神经网络的配置效率。

98.在一个实施例中,所述方法还包括:

99.当所述运行延迟不小于所述当前优化运行延迟时,返回至步骤s104。

100.具体地,当出现运行延迟大于或等于当前优化运行延迟的情况,表明新选取的张量数据存储格式并非更优的配置,因此,无须进行当前优化运行延迟、当前优选存储格式标识的更新,而直接开始下一轮迭代,以提升神经网络的配置效率。

101.为了便于本领域技术人员深入理解本技术实施例,以下将结合具体的示例性代码进行说明。

102.[0103][0104]

上述示例性代码中,对tensor_formats赋值nchw和nhwc两种卷积层可用的张量数据存储格式。设置best_config(初始化的卷积层配置),best_config.time(卷积层配置中的运行延迟)初始化为最大值(float_max)。

[0105]

然后,通过循环语句for tensor_format in tensor_formats,遍历各种张量数据存储格式。将tensor_format(张量数据存储格式)传参至benchmark_conv2d()(基准测试函数),得到其返回的time值。

[0106]

当满足time<best_config.time的条件时,则通过best_config.tensor_format=tensor_format、best_config.time=time进行赋值更新并返回循环开始语句。直至遍历所有的tensor_format。

[0107]

最后,通过return best_config返回卷积层的best_config(优化后的卷积层配置),best_config中的tensor_format,即对应使得time(运行延迟)最短的张量数据存储格式。

[0108]

应该理解的是,虽然图1和图6的流程图中的各个步骤按照箭头的指示依次显示,但是这些步骤并不是必然按照箭头指示的顺序依次执行。除非本文中有明确的说明,这些步骤的执行并没有严格的顺序限制,这些步骤可以以其它的顺序执行。而且,图1和图6中的至少一部分步骤可以包括多个子步骤或者多个阶段,这些子步骤或者阶段并不必然是在同一时刻执行完成,而是可以在不同的时刻执行,这些子步骤或者阶段的执行顺序也不必然是依次进行,而是可以与其它步骤或者其它步骤的子步骤或者阶段的至少一部分轮流或者交替地执行。

[0109]

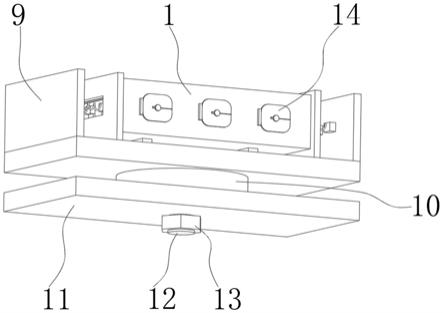

在一个实施例中,如图7所示,提供了一种神经网络配置装置,包括:

[0110]

确定模块702,被配置为确定神经网络中的待配置卷积层;所述待配置卷积层具有多种可用的张量数据存储格式;

[0111]

格式选取模块704,被配置为在多种所述张量数据存储格式中,选取待测试张量数据存储格式;

[0112]

延迟获取模块706,被配置为获取所述待配置卷积层采用所述待测试存储格式执行基准测试任务时的运行延迟;

[0113]

目标格式确定模块708,被配置为根据所述运行延迟,确定所述待配置卷积层的目标存储格式;

[0114]

返回模块710,被配置为返回至所述确定神经网络中的待配置卷积层的步骤,直至确定所述神经网络的各个卷积层各自的目标存储格式。

[0115]

在一个实施例中,所述目标格式确定模块708,还被配置为:

[0116]

获取当前优化运行延迟;

[0117]

当所述运行延迟小于所述当前优化运行延迟时,将所述当前优化运行延迟的数值更新为所述运行延迟的数值,以及,将预设的当前优选存储格式标识更新为所述待测试存储格式的标识;

[0118]

返回至所述在多种所述张量数据存储格式中,选取待测试存储格式的步骤,直至遍历多种可用的所述张量数据存储格式后,将所述当前优选存储格式标识对应的张量数据存储格式,确定为所述待配置卷积层的目标存储格式。

[0119]

在一个实施例中,所述延迟获取模块706,还被配置为:

[0120]

将所述待测试存储格式的标识传入预设的基准测试函数;

[0121]

运行所述基准测试函数,得到所述基准测试函数返回的所述运行延迟。

[0122]

在一个实施例中,所述装置还被配置为:

[0123]

当所述运行延迟不小于所述当前优化运行延迟时,返回至所述在多种所述张量数据存储格式中,选取待测试存储格式的步骤。

[0124]

在一个实施例中,所述张量数据存储格式包括nchw、nhwc、chwn中的至少一种。

[0125]

关于神经网络配置装置的具体限定可以参见上文中对于神经网络配置方法的限定,在此不再赘述。上述神经网络配置装置中的各个模块可全部或部分通过软件、硬件及其组合来实现。上述各模块可以硬件形式内嵌于或独立于计算机设备中的处理器中,也可以以软件形式存储于计算机设备中的存储器中,以便于处理器调用执行以上各个模块对应的操作。

[0126]

上述提供的神经网络配置装置可用于执行上述任意实施例提供的神经网络配置方法,具备相应的功能和有益效果。

[0127]

在一个实施例中,提供了一种计算机设备,该计算机设备可以是终端,其内部结构图可以如图8所示。该计算机设备包括通过系统总线连接的处理器、存储器、网络接口、显示屏和输入装置。其中,该计算机设备的处理器用于提供计算和控制能力。该计算机设备的存储器包括非易失性存储介质、内存储器。该非易失性存储介质存储有操作系统和计算机程序。该内存储器为非易失性存储介质中的操作系统和计算机程序的运行提供环境。该计算机设备的网络接口用于与外部的终端通过网络连接通信。该计算机程序被处理器执行时以实现一种空气传感器的室内定位方法。该计算机设备的显示屏可以是液晶显示屏或者电子

墨水显示屏,该计算机设备的输入装置可以是显示屏上覆盖的触摸层,也可以是计算机设备外壳上设置的按键、轨迹球或触控板,还可以是外接的键盘、触控板或鼠标等。

[0128]

本领域技术人员可以理解,图8中示出的结构,仅仅是与本技术方案相关的部分结构的框图,并不构成对本技术方案所应用于其上的计算机设备的限定,具体的计算机设备可以包括比图中所示更多或更少的部件,或者组合某些部件,或者具有不同的部件布置。

[0129]

在一个实施例中,提供了一种计算机设备,包括存储器和处理器,存储器中存储有计算机程序,该处理器执行计算机程序时实现以下步骤:

[0130]

确定神经网络中的待配置卷积层;所述待配置卷积层具有多种可用的张量数据存储格式;

[0131]

在多种所述张量数据存储格式中,选取待测试张量数据存储格式;

[0132]

获取所述待配置卷积层采用所述待测试存储格式执行基准测试任务时的运行延迟;

[0133]

根据所述运行延迟,确定所述待配置卷积层的目标存储格式;

[0134]

返回至所述确定神经网络中的待配置卷积层的步骤,直至确定所述神经网络的各个卷积层各自的目标存储格式。

[0135]

在一个实施例中,提供了一种计算机可读存储介质,其上存储有计算机程序,计算机程序被处理器执行时实现以下步骤:

[0136]

确定神经网络中的待配置卷积层;所述待配置卷积层具有多种可用的张量数据存储格式;

[0137]

在多种所述张量数据存储格式中,选取待测试张量数据存储格式;

[0138]

获取所述待配置卷积层采用所述待测试存储格式执行基准测试任务时的运行延迟;

[0139]

根据所述运行延迟,确定所述待配置卷积层的目标存储格式;

[0140]

返回至所述确定神经网络中的待配置卷积层的步骤,直至确定所述神经网络的各个卷积层各自的目标存储格式。

[0141]

本领域普通技术人员可以理解实现上述实施例方法中的全部或部分流程,是可以通过计算机程序来指令相关的硬件来完成,所述的计算机程序可存储于一非易失性计算机可读取存储介质中,该计算机程序在执行时,可包括如上述各方法的实施例的流程。其中,本技术所提供的各实施例中所使用的对存储器、存储、数据库或其它介质的任何引用,均可包括非易失性和/或易失性存储器。非易失性存储器可包括只读存储器(rom)、可编程rom(prom)、电可编程rom(eprom)、电可擦除可编程rom(eeprom)或闪存。易失性存储器可包括随机存取存储器(ram)或者外部高速缓冲存储器。作为说明而非局限,ram以多种形式可得,诸如静态ram(sram)、动态ram(dram)、同步dram(sdram)、双数据率sdram(ddrsdram)、增强型sdram(esdram)、同步链路(synchlink)dram(sldram)、存储器总线(rambus)直接ram(rdram)、直接存储器总线动态ram(drdram)、以及存储器总线动态ram(rdram)等。

[0142]

以上实施例的各技术特征可以进行任意的组合,为使描述简洁,未对上述实施例中的各个技术特征所有可能的组合都进行描述,然而,只要这些技术特征的组合不存在矛盾,都应当认为是本说明书记载的范围。

[0143]

以上所述实施例仅表达了本技术的几种实施方式,其描述较为具体和详细,但并

不能因此而理解为对发明专利范围的限制。应当指出的是,对于本领域的普通技术人员来说,在不脱离本技术构思的前提下,还可以做出若干变形和改进,这些都属于本技术的保护范围。因此,本技术专利的保护范围应以所附权利要求为准。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。