1.本公开涉及一种用于静电卡盘的层布置;其制造方法;以及含有所述层布置的静电卡盘。特别地,本公开涉及一种金属化层,其设置在静电卡盘中的顶部电介质层与绝缘层之间。

背景技术:

2.静电卡盘(esc)在半导体装置制造工艺中被广泛用于夹紧基板,诸如硅晶片。esc是层状结构,其中导电层被夹在陶瓷绝缘体之间,以防止它们与装置直接接触。氧化铝和氮化铝是esc中使用最多的陶瓷。导电层,通常称为“迹线”或“电极”,通常由难熔金属诸如钼和钨制成。迹线通过穿过陶瓷层的称为“通路”的层间导电管道进一步连接,以从外部电源提供电能。

3.美国专利5,671,116教导了用于制造陶瓷esc的共烧方法。在这个过程中,首先通过流延粉末来形成陶瓷带,所述粉末与各种有机和无机粘合剂混合以使它们保持在一起。然后,在生坯状态的陶瓷带顶部将导电迹线金属化。然后,将金属化的生坯带彼此上下堆叠,然后按压以将它们层压。通过将难熔金属浆料或粉末插入在陶瓷层中钻出的通孔来形成通路。然后在高温下将所得层压的生坯部件共烧,以制成整体esc主体。

4.esc的顶部陶瓷层通常称为电介质层,它与晶片直接接触,是esc中最关键的陶瓷层。它的主要功能是在晶片与下面的电极之间提供绝缘层。它的介电强度必须承受住为了夹紧晶片所施加的电场的击穿力。它还在加工时防止任何金属杂质从电极材料迁移至装置。在诸如蚀刻和沉积的加工室中,使用苛刻气体(harsh gas),诸如氟和氯,它们在性质上腐蚀性递增。在此类情况下,最重要的是陶瓷层的组合物必须不能被腐蚀性加工气体溶解并污染装置。

5.为了维持高的电介质击穿强度,陶瓷必须接近完全致密。美国专利us4678683、us5207437和us5104834全部都公开了使用二氧化硅与氧化钙和氧化镁作为液相烧结助剂以在烧结层状金属化结构时使陶瓷致密。虽然在氧化铝中的此类组合物得到致密的烧结体,但它们有一些缺陷:

6.在半导体制造过程期间,组合物被诸如氟和氯的卤素等离子气体侵蚀;并且

7.组合物的与液相形成有关的杂质含量相对较高。杂质含量高使组合物不适合于高温加工环境,因为杂质更容易通过电介质层迁移;并进入气体加工环境并且不利地到硅晶片的表面上。

8.因此,有必要开发出既耐腐蚀又抵抗杂质向加工环境中迁移的esc。

技术实现要素:

9.在第一方面中,提供了一种用于静电卡盘的层布置,其包括:

10.a.第一陶瓷层;

11.b.第二陶瓷层;

12.c.金属化层,其设置在所述第一陶瓷层与所述第二陶瓷层之间,

13.其中所述第一陶瓷层包括至少90.0wt%的以下物质:

14.(i)氧化铝、二氧化钛、zro2、y2o3、aln、si3n4、sic或其组合;或

15.(ii)掺杂有过渡金属氧化物的氧化铝;以及

16.优选地,足以使第一陶瓷层致密化至第一陶瓷层的理论最大密度(即,0%孔隙率)的至少97%、或98%、或98.5%、或99.0%的氧化钽(ta2o5)。氧化钽(ta2o5)优选在0.05wt%至10.0wt%的范围内存在。

17.在一些实施方案中,已经发现相对少量的氧化钽(例如,小于2.0wt%)(用作烧结助剂)能够生产出高密度、高纯度的陶瓷。在这些实施方案中,第一陶瓷层优选包括至少90.0wt%的氧化铝、二氧化钛、zro2、y2o3、aln、si3n4、sic或其组合。

18.在其他实施方案中,可能需要更多ta2o5(例如2.0wt%至6.0wt%或10wt%或更多)来形成ta2o5液相以使第一陶瓷层致密化。在这些实施方案中,第一陶瓷层优选包括至少90.0wt%的掺杂有过渡金属氧化物(诸如,二氧化钛)的氧化铝。

19.ta2o5在大多数环境中惰性很高,并且因此向加工环境中迁移的趋势很低。加工环境可以高于450℃、或高于550℃、或高于650℃、或高于750℃。

20.优选地,有至少92.0wt%、或至少94.0wt%、或至少96.0wt%、或至少98.0wt%、或至少99.0wt%的氧化铝、二氧化钛、zro2、y2o3、aln、si3n4、sic、过渡金属氧化物或其组合。

21.第一层可包括至少95.0wt%、或至少97.0wt%、或至少98.0wt%、或至少99.0wt%、或至少99.5wt%、或至少99.8wt%的氧化钽和氧化铝、二氧化钛、zro2、y2o3、aln、si3n4、sic、过渡金属氧化物或其组合。

22.第一陶瓷层优选包括氧化铝或aln。

23.第一陶瓷层优选包括小于或等于8.0wt%的ta2o5、或小于或等于6.0wt%或小于或等于4.0wt%的ta2o5、或小于或等于2.0wt%或小于或等于1.5wt%的ta2o5、或小于或等于1.0wt%或小于或等于0.8wt%的ta2o5、或小于或等于0.7wt%或小于或等于0.6wt%的ta2o5、或小于或等于0.5wt%或小于或等于0.4wt%。优选地,第一陶瓷层包括大于或等于0.2wt%的ta2o5、或大于或等于0.3wt%的ta2o5。所需ta2o5的量可取决于:第一陶瓷层的组合物;所需目标密度和/或目标烧结温度和时间;以及层布置将暴露的加工环境。在致密化过程中,ta2o5的水平较高可能不提供显著的附加益处;而水平较低可能不足以在目标条件下提供目标密度要求。

24.优选地,第一陶瓷层是顶部电介质层。顶部电介质层可在加工室中与晶片直接接触,并且因此电介质层的表面优选地基本上不含挥发性杂质物质(例如,cu和na)。

25.优选地,第一陶瓷层在第一陶瓷层和金属化层的界面处包括ta2o5相。

26.在一个实施方案中,在制造层布置的共烧工艺期间,将层布置加热至低于ta2o5的熔点持续一段设定的时间,导致液态ta2o5‑

氧化铝相的形成,所述相被吸引到金属化层和相邻第二陶瓷层周围的更具多孔性的区域。优选地,ta2o5能够在等于或低于1600℃下,并且更优选地在等于或低于1400℃下,在第一陶瓷层内形成液相。

27.结果,在顶部电介质层的顶表面(ta2o5缺乏相)处的ta2o5浓度低于在第一陶瓷层和金属化层的界面处的ta2o5相(例如,玻璃)的ta2o5浓度。优选地,在第一陶瓷层顶表面处的ta2o5浓度比在金属化层与第一陶瓷层之间的界面处的ta2o5相中的ta2o5浓度低20%、或

50%、或80%。ta2o5的这种分布是有利的,因为虽然ta2o5对大多数气体环境不具有反应性,但它容易与氟气反应。因此,与气体环境直接接触的表面的ta2o5较少。此外,在所使用的陶瓷氧化物是氧化铝的实施方案中,认为ta2o5形成基于氧化铝的玻璃,其可比单独ta2o5更耐氯气腐蚀。

28.在一些实施方案中,在金属化层附近的钽相的横截面积(例如,在距金属化层不多于30μm的最大点处的约300μm2或更多(例如,20μm

×

15μm)的最小样本横截面积)比在顶部电介质层表面附近的钽相的横截面积(例如,在距表面不多于30μm的最大点处的约300μm2或更多(例如,20μm

×

15μm)的最小样本横截面积)大20%、或大40%、或大80%、或大100%、或大150%、或大200%。

29.ta2o5相的熔点相对较高并且蒸气压力相对较低。ta2o5相不仅在高达1000℃或更高的温度下耐腐蚀并且不挥发,它还形成了防止更多挥发性杂质通过第一层陶瓷层迁移并进入加工室的屏障。因此,层布置具有能够在高温腐蚀环境中可靠地运行,同时在半导体生产中不污染晶片的益处。

30.特别地,在非蚀刻应用(诸如,离子注入室)中,氧化钽掺杂的氧化铝esc得到清洁得多的加工环境,因为ta2o5与其他粘合剂(诸如,氧化镁和氧化钙)相比具有更低的蒸气压力。

31.与传统的esc相比,带有ta2o5电介质顶层的esc在腐蚀性气体中的惰性性质还使esc能够在较长的时间段内维持其机械完整性。

32.在高温烧结期间形成液态ta2o5相还有助于陶瓷层与金属化层的粘合,因此避免esc中不同层的分层。

33.根据具体应用和第一陶瓷层的组合物,第一陶瓷层的厚度通常在10μm与1.0mm之间、或20μm与500μm之间、或30μm与400μm之间、或40微米与300μm之间、或50μm与200μm之间,包括其之间的所有子范围和值。当第一陶瓷层是用于离子注入工艺的esc的顶部电介质层时,则电介质层需要承受住500v至2000v的电压范围。对于用于蚀刻或沉积工艺的esc,则电介质层可能需要承受住3000v至6000v、优选地1000v至3000v的电压。

34.在一个实施方案中,顶部电介质层的击穿电压为至少60v/μm、或至少70v/μm、或至少80v/μm。

35.对于al2o3(99.5wt%)

‑

ta2o5(0.5wt%)电介质层,电介质击穿电压为约2000v/密耳或80v/μm。当加入安全裕度时,电介质层的大致厚度可能在10μm或20μm与200μm之间。与传统的高纯度电介质层(诸如,al

‑

995tm和al

‑

998tm(可购自morgan advanced ceramics,hayward,ca))相比,本文实施方案的层布置的优越的电介质击穿强度允许将更薄的电介质层用于相同的应用电压。

36.第一陶瓷层的密度优选大于陶瓷材料的理论最大密度(孔隙率为0%)的97%、更优选大于98%并且甚至更优选大于99%。另选地,第一陶瓷层的空隙率优选小于3%v/v、更优选小于2%v/v并且甚至更优选小于1%v/v。

37.第一陶瓷层的密度可以大于3.90g/cm3、或大于3.91g/cm3、或大于3.92g/cm3、或大于3.93g/cm3、或大于3.94g/cm3、或大于3.95g/cm3。

38.第二陶瓷层的密度优选低于第一陶瓷层的密度。第二陶瓷层优选包括至少95wt%并且更优选至少95wt%的氧化铝、二氧化钛、zro2、y2o3、aln、si3n4、sic或其组合。

39.形成第一层和第二层的陶瓷材料的平均粒度优选在约0.5μm与5μm之间,并且更优选在1μm与3μm之间。

40.第一陶瓷层和第二陶瓷层优选包括相同的陶瓷组分。在一个优选的实施方案中,第一陶瓷层和第二陶瓷层包括氧化铝。在此实施方案内,第二陶瓷层优选具有高氧化铝含量(例如,al

‑

998tm)。由于基本上不存在烧结助剂,较高纯度氧化铝较难烧结和致密化。因此,第二陶瓷层的密度一般低于第一陶瓷层,并且因此有利于液态ta2o5相向第二陶瓷相的迁移并进入第二陶瓷相。液态ta2o5相进入第二陶瓷相的迁移可能仅在金属化层界面附近(即,不延伸到整个第二陶瓷层)。

41.在另一个实施方案中,第一陶瓷层包括静电荷耗散材料,其包括掺杂有过渡金属氧化物的氧化铝和在0.1wt%或0.5wt%与10.0wt%之间的氧化钽(ta2o5)。基于第一陶瓷层中陶瓷材料总重量,过渡金属氧化物的存在量优选在1.0wt%至8.0wt%的范围内(优选在1.5wt%至7.5wt%的范围内或在2.0wt%至7.0wt%的范围内)。在此实施方案内,掺杂有过渡金属氧化物的氧化铝优选占第一陶瓷层的至少90wt%。

42.如us6,641,939中所公开的,氧化铝的掺杂使掺杂的氧化铝的电阻率能够受到控制,所述专利以引用的方式并入本文。

43.过渡金属氧化物可以选自由re、ti、v、fe、cr、co、mn、ni、mo和nb的氧化物组成的组。过渡金属氧化物优选为二氧化钛。

44.认为晶界相的连续性以及ta2o5‑

钛酸盐液相的润湿角控制掺杂氧化铝的电阻率。与高纯度氧化铝相比,需要向二氧化钛掺杂的氧化铝中添加更多量的ta2o5,以在等于或低于1600℃的共烧温度下形成ta2o5‑

钛酸盐液相(例如,在2.0wt%至10wt%的ta2o5的范围内)。

45.在包括过渡金属氧化物掺杂的氧化铝第一陶瓷层的实施方案中,第一陶瓷层的击穿电压优选为至少20v/μm、或至少30v/μm、或至少40v/μm。

46.在第二方面中,提供了一种静电卡盘,其包括第一方面的层布置。

47.在第三方面中,提供了一种制造用于静电卡盘的层布置的方法,其包括以下步骤:

48.a.形成第一陶瓷层或第二陶瓷层,以得到处于生坯状态的基底层;

49.b.将金属化层施加至基底层;

50.c.将第一陶瓷层或第二陶瓷层设置在金属化层上方,以形成处于生坯状态的顶层;所述第一陶瓷层(处于共烧状态)包括:

51.至少90wt%的氧化铝、二氧化钛、zro2、y2o3、aln、si3n4、sic、过渡金属氧化物或其组合;以及足以使第一陶瓷层致密化至第一陶瓷层的理论密度的至少97%、或98%、或98.5%、或99.0%的氧化钽(ta2o5)。氧化钽(ta2o5)优选在0.1wt%至10.0wt%的范围内

52.d.在足够的温度和时间下共烧各层,以形成液态ta2o5相,

53.其中,液态ta2o5相向第一陶瓷层、金属化层和第二陶瓷层之间的界面迁移。

54.在第四方面中,提供了一种制造用于静电卡盘的层布置的方法,其包括以下步骤:

55.a.形成基底层,其包括处于生坯状态的第一材料;

56.b.将难熔金属化形成材料施加至所述基底层,以形成金属化层;

57.c.将包括处于生坯状态的第二材料的顶层设置在所述金属化层上方;

58.d.在足够的温度和时间下共烧所述基底层、金属化层和顶层,以形成液态ta2o5相,

59.其中,所述液态ta2o5相向所述顶层、所述金属化层和所述基底层之间的界面迁移;并且

60.在共烧状态下,所述顶层包括第一陶瓷材料,其包括:至少90.0wt%的氧化铝、二氧化钛、zro2、y2o3、aln、si3n4、sic或其组合;以及在0.1wt%至10.0wt%范围内的氧化钽(ta2o5)。

61.其他形成层布置的方法也是可能的,例如,使用粘结剂将各层粘合在一起,而不是共烧。然而,一般来说,共烧是优选的,因为它促成了从顶层表面到金属化层的ta2o5浓度梯度,从而:

62.在金属化层处或附近产生屏障,以防止挥发性杂质向电介质层表面的迁移;

63.在电介质层与金属化层之间产生粘合层,以防止电介质层和金属化层的分层;以及

64.提供基本上不含挥发性杂质的惰性电介质层表面,其能够在气氛临界环境中(诸如,在离子注入室中)工作。

65.优选地,第二陶瓷层是基底层,并且第一陶瓷层是顶层。

66.在共烧之前,可以向布置中加入附加层(例如,加热器层)。附加层优选加入到基底层中,从而维持第一陶瓷层作为顶层。

67.金属化层与相邻陶瓷层之间的界面容易有分层和空隙形成,部分原因是热膨胀不匹配和/或空隙形成。第一陶瓷层中的液态ta2o5相迁移至金属化层界面,以在金属化层与相邻陶瓷层之间形成更可靠的粘合。

68.通常,使第一陶瓷层致密化至大于第一陶瓷层的理论最大密度的97.0wt%的温度和时间足以使液态ta2o5相改善金属化层的粘合。然而,使共烧条件维持延长的时间(例如,大于1小时或大于2小时)可具有另外的积极效果。延长的共烧时间还可导致第一陶瓷层的表面与处于生坯状态的表面相比由于ta2o5相的迁移而ta2o5的水平减少。表面层中的ta2o5水平较低(例如,与处于生坯状态的表面相比,少10%、或20%、或50%)使得表面适合于在氯(cl2和bcl3)气环境或甚至是氟气环境中应用。

69.优选地,在致密化过程期间,第二陶瓷层的密度低于第一陶瓷层的密度,因为第二陶瓷相中以及在层边界周围的较高的空隙率,促进液态ta2o5相向第二陶瓷层的迁移。

70.第一陶瓷层和第二陶瓷层可以通过任何合适的技术(包括干压或流延)来实现。在一个实施方案中,第二层是通过干压形成的,并且第一层是通过流延形成的。这种工艺的细节提供在在us20170057880中,其以引用的方式并入本文。当电介质层的厚度小于200μm并且更优选小于100μm时,优选使用流延。

71.生坯的第二陶瓷层的厚度可以有很大的变化,这主要取决于其特定的应用。然而,一般来说,它厚度的范围为约0.1mm至约5mm。优选地,生坯陶瓷层具有均匀的或至少基本均匀的厚度。

72.金属化

73.金属化层可包括难熔金属化形成材料,即在共烧期间,难熔金属化形成材料在基板上形成导电的难熔金属相。一般来说,金属化形成材料在本领域中是已知的,并且可以商业购得。金属化形成材料的熔融温度优选显著低于共烧温度(例如,低50℃或100℃)。金属化材料优选为选自由铂、钯、钨、钼、铌、钽及其合金组成的组的金属。

74.通常,金属化形成材料呈包括悬浮在有机粘合剂和溶剂中的难熔金属粒子的浆糊或油墨的形式。金属化材料还可含有一些玻璃形成组分(例如,sio2、mgco3、高岭土),其进一步有助于金属与基板的粘合。然而,因为形成的液态ta2o5相可改善金属化层与基板的粘合,所以此类添加是任选的。

75.一般来说,难熔金属粒子大小的范围为约0.1微米至约20微米。

76.难熔金属可以是其粒子可以在本发明可烧结陶瓷组合物的烧结期间烧结在一起以产生连续的导电相的任何金属。难熔金属在陶瓷组合物的烧结期间必须是固体,并且优选地,它是钨或钼。

77.金属化材料可以通过许多常规技术与陶瓷层接触。一般来说,它是以预选的静电卡盘电极图案沉积或印刷在上面和/或中间的。通常,它是丝网印刷在上面的。

78.制造

79.在制造具有多层陶瓷基板的整体主体时,生产了多个生坯陶瓷层,并且金属化材料以预选的图案接触它们或印刷在它们中的大部分(如果不是全部)上。可以根据层互相连接的需要在片材上打出通孔或直通孔,并且用通常呈浆糊的形式的金属化材料填充。然后,将这些片材以预选的通常形成三明治的方式堆叠在一起,即相互叠加。可以在一定压力和温度下对叠堆进行层压以形成层压结构,然后进行共烧,所述温度主要由其特定组合物决定,但通常低于约100℃。

80.在施加金属化涂料后,可使用等静压来装配多层生坯带和/或干压的生坯片材。典型的压力高达约103mpa(15kpsi),但可按需要使用更高的压力。等静压不仅在带之间产生良好的层压,还确保多层带结构在烧制期间的均匀收缩。

81.当将烧制的层压组件用作静电卡盘时,共烧的陶瓷部件的外表面或面部需要基本上平坦,以便确保基板晶片与电介质层的支撑表面之间有最大的表面积接触。为了提供共烧陶瓷部件的平坦度,平坦烧制层布置的方法包括以下步骤:

82.a)在具有至少一个基本上平坦表面的绝缘设定器上支撑层布置;

83.b)将具有至少一个基本上平坦表面的绝缘砝码安装或装配在层布置上,使得层布置位于绝缘设定器与绝缘砝码的基本上平坦的表面之间。

84.然后在惰性(例如,n2)或还原性(例如,h2)气体环境中将步骤(a)和(b)烧制至烧结温度。优选地,与物品相邻的设定器和/或砝码的至少一个表面被机械加工成基本上平坦。通过将与生坯物品接触的设定器和/或砝码的至少一个表面机械加工成基本上平坦,生坯层布置将在烧制期间维持其平坦度或采用设定器和/或砝码表面的平坦度。例如,在后一种情况下,当生坯层布置由于其形成工艺(诸如干压或等静压或甚至处理)不是完全平坦的或具有瑕疵,通过烧制在设定器与砝码的基本上平坦表面之间的生坯层布置,砝码所施加的压力使层布置基本上采用了设定器和/或砝码的平坦表面的平坦度。

85.本发明的结构优选被共烧以产生烧结的结构,其包括不含大于约5微米的空隙的烧结的陶瓷基板和粘合的难熔金属导电相。

86.在烧结期间,第一陶瓷层优选包括ta2o5液相,以用于生产所需密度的陶瓷基板。优选地,ta2o5液相将烧结的金属粒子粘结至相邻的陶瓷层。在烧结期间,实现陶瓷的烧结的一部分液相通过毛细管迁移到烧结难熔金属粒子之间的空隙中,得到相,通常是玻璃相,其与难熔金属的连续相混合,有助于难熔金属相与基板的粘合。烧结温度可以有很大的变化,主

要取决于特定的陶瓷组合物,但一般其高于1300℃,并且通常范围为约1350℃至约2100℃。例如,对于可烧结的液相ta2o5‑

氧化铝组合物,典型的烧结温度为约1500℃至约1600℃。

87.关于加工部件以形成静电卡盘的进一步细节可见于us20170057880,其以引用的方式并入本文。

88.为方便起见,将钽表述为氧化物形式(ta2o5),并且应当理解钽可以其他形式存在。

附图说明

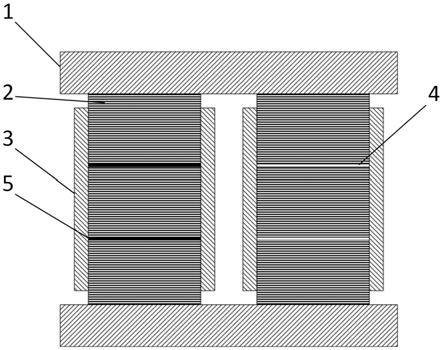

89.图1是形成静电卡盘的层布置的分解图(未按比例绘制)。

90.图2是根据实施方案的第一陶瓷层(顶部)、金属化层和第二陶瓷层的sem图像。

91.图3是图2的放大sem图像。

92.图4是腐蚀测试后al2o3‑

ta2o5组合物的重量损失(

×

10

‑

4g/cm2)的图表。

93.图5是腐蚀测试后al2o3‑

ta2o5组合物的挠曲强度(mpa)。

94.图6是层布置的横截面的sem图像。

95.图7是电介质层顶部部分的横截面的sem图像。

96.图8是电介质层中间部分的横截面的sem图像。

97.图9是电介质层底部部分的横截面的sem图像。

98.图10是突出了电介质层中钽相的存在的sem图像和eds光谱。

99.图11a

‑

c是图9的sem图像的一部分,其已经过数字成像软件处理。

具体实施方式

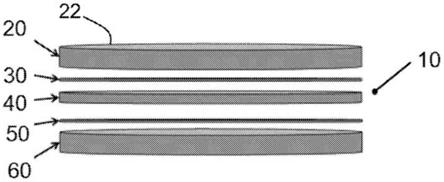

100.参考图1,有直径为300mm的静电卡盘10,其包括:由干压形成的厚度为150μm的顶部电介质层20,其具有顶表面22;电极层30(20μm),其包括钼基涂料组合物;厚度为约50μm的干压绝缘层40;加热器层(20μm)50,其包括钼基涂料组合物;和厚度为150μm的基底层。

101.电介质层20、绝缘层40和基底层60中的每一个都包括高纯度氧化铝。电介质层20包括99.5wt%的al2o3、0.5wt%的ta2o5和痕量水平的杂质。薄绝缘层40和基底层60都是由标称纯度为99.8wt%的al2o3(al

‑

998tm)的氧化铝粉形成。其他合适的氧化铝粉包括al

‑

995tm。高纯度氧化铝形成氧化铝制剂(al

‑

998tm、al

‑

995tm和e

‑

1制剂)的基础,其中氧化铝粒子的平均粒度为约1.2μm;表面积为约3.5m2/g。

102.使用喷雾干燥的氧化铝;如us20170057880第57至62段中所述的粘合剂、分散剂和其他添加剂,对陶瓷层进行干压。

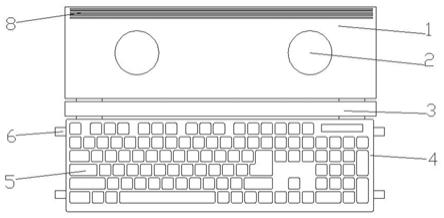

103.参考图2,共烧的层布置10包括电介质层20,该电介质层20包括分布在其中的小空隙。相对于电介质层20与金属化层30之间的界面区域80,预期电介质层20的顶部部分70具有更低比例的ta2o5。金属化层包括烧结的金属粒子和玻璃相,其中一些可能是金属化组合物的一部分并且一些可来源于电介质层中的ta2o5。与电介质层30相比,绝缘层40包括较大比例的空隙。

104.界面区域80的放大图像示出,与电介质层20的大部分相比,此区域中空隙的比例较大。

105.实施例:

106.样本

107.样本e

‑

1的组成是99.5wt%的al2o3和0.5wt%的ta2o5。其他杂质少于0.1wt%。ta2o5的平均粒度小于1.0μm,粒度分布较小(与al2o3相比)有助于ta2o5在al2o3中的均匀分散。e

‑

1的密度为3.96g/cm3。

108.样本ce

‑

1是可从morgan advanced ceramics(hayward,ca)购得的al

‑

995tm,其组成为99.5wt%的al2o3和0.5wt%其他材料(不包括ta2o5),包括玻璃形成材料。ce

‑

1的密度为3.91g/cm3。在室温、15kpsi压力下对样本(e

‑

1和ce

‑

1)进行层压,然后1575℃下、h2中共烧2小时。

109.样本e

‑

2的组成是2.0wt%的tio2、4.0wt%的ta2o5、少于0.1wt%的其他杂质和剩余为al2o3。e

‑

2的密度为3.96g/cm3。

110.样本ce

‑

2是商业组合物,其中能量色散x射线光谱(eds)分析证实存在主要的al2o3组分和次要的组分tio2、mgo、cao和sio2。ce

‑

2的密度为3.85g/cm3。

111.在室温、15kpsi压力下对样本(e

‑

2和ce

‑

2)进行层压,然后1600℃下、h2中共烧2小时。

112.耐腐蚀性和挠曲强度

113.将具有已知重量和挠曲强度的并且各自平均样本表面积为15.5cm2的样本ce1和e1在90℃下放置于具有150ml各自浓度为20%v/v的盐酸、硫酸、硝酸或氢氧化钾水溶液的teflontm测试容器中11周。然后对样本进行重新称重并重新测试挠曲强度,其中平均结果提供于图4和图5中。

114.结果表明,与样本ce

‑

1(氧化铝

‑

mgo

‑

二氧化硅)相比,样本e

‑

1(氧化铝

‑

ta2o5)的耐腐蚀性和挠曲强度改善。

115.介电性质

116.样本e

‑1117.根据astm d149,在室温下测定击穿电压。结果(表1)指示,与常规的高纯度氧化铝电介质层相比,al2o3‑

ta2o5电介质层的击穿电压远远高于其两倍,从而可以使用更薄的电介质层。

118.表1

119.[0120][0121]

据报告,样本ce

‑

1在室温下的电介质击穿电压为800v/密耳。

[0122]

还测定了在与e

‑

1和ce

‑

1相同的条件下加工的包括包括99.8wt%氧化铝(来自morgan advanced ceramics的al998 tm)的顶部电介质层的esc中的击穿电压。密度为3.92g/cm3,并且击穿电压在569v/密耳与943v/密耳之间变化,平均值为741v/密耳。

[0123]

表2

[0124]

厚度(密耳)击穿电压(v)击穿电压(v/密耳)[v/μm]7.06659951[37.5]7.06582940[37.0]7.06418917[36.1]7.080441149[45.2]平均值6926989[38.9]

[0125]

ce

‑

2的击穿电压为11v/μm。

[0126]

e

‑

2的体积电阻率是2

×

10

‑

11ωcm,相比ce

‑

2是1

×

10

‑

11ωcm。

[0127]

与现有技术(例如us6,641,939)的常规静电荷耗散材料相比,本文的层布置能够提供较大击穿电压(表2)、耐腐蚀性和密度。

[0128]

第一陶瓷层的致密化

[0129]

如先前所述对样本进行加工,不同之处在于调整了烧结温度和时间。第一陶瓷层的密度受温度和在烧结温度下维持的持续时间的影响。如表3中所示,烧结温度和时间的组合影响了致密化工艺。如果烧结温度足够高,那么时间可能是液相渗透空隙并增加致密化的限制因素。

[0130]

表3

[0131]

烧结温度(℃)时间(小时)密度(g/cm3)[%理论值*]160023.96[99.25%]153023.95[99.00%]15300.53.89[97.49%]

[0132]

*al2o3的密度取为3.99g/cm3钽在第一陶瓷层中的分布

[0133]

参考图6

‑

图9,测定了顶部电介质中在表面附近的横截面区域170处(样本(a))、在

电介质层中间的横截面区域120处(样本(b))以及在邻近金属化层130的电介质层底部的横截面区域180处(样本(c))的ta2o5浓度。在第二陶瓷层140中没有发现大量的ta2o5,但是其更可能存在于第一陶瓷层和第二陶瓷层界面处,而不是被金属静电卡盘电极图案130分开。

[0134]

使用图像处理软件工具imagejtm确定了电介质层各部件的横截面表面积。从总横截面积中排除图像中的空隙和伪影(识别为黑色)。然后用从相应的eds光谱验证的组成,使用基于钽部分色调的阈值,将图形数据转换为二元格式(白色

‑

钽部分;黑色

‑

其他),如样本b中钽相的验证所指示(图10)。然后用黑色与白色像素的比例计算电介质层顶部(a)、中间(b)和底部(c)的钽部分的横截面积比例。

[0135]

样本(c)的图像分析过程示于图11a

‑

图11c中,首先用图像处理工具对样本图像面积(图11a)进行筛选以除去空隙和伪影(图11b),然后将其用于识别相对于剩余面积(排除图11b中识别的空隙和伪影)的所识别的(图11c)钽相横截面积(白色)。在计算样本(a)和(b)中钽相的横截面积时采用了相同的处理步骤。

[0136]

使用针对(c)的在距金属化层不多于30μm的最大点处和针对(a)的在距电介质层表面不多于30μm的最大点处大约312μm2(26μm

×

12μm)的样本横截面积分析电介质层的顶部(a)、中间(b)和底部(c)部分,结果使用eds分析示于表4中。如表4所示,在电介质层的底部(c),钽的比例(相对于样本的总有效面积,即,总样本面积减去空隙和伪影所占的样本面积)最高,并且钽的比例向电介质层的顶部(a)递减。这在样本区域a(图7)、样本区域b(图8)和样本区域c(图9)的sem图像中得到了参考,其中图9中金属化层130上方的ta2o5相(有斑点的白色相)显著更多。

[0137]

表4

[0138]

电介质层位置ta相的横截面积%相对于(a)的变化顶部(a)0.29%

‑

中间(b)0.50%172%底部(c)0.73%252%

[0139]

在整个本说明书中,对“一个实施方案”、“某些实施方案”、“各种实施方案”、“一个或多个实施方案”或“实施方案”的提及意指结合实施方案描述的特定特征、结构、材料或特性包括在本公开的至少一个实施方案中。因此,在本说明书通篇各个地方出现如“在一个或多个实施方案中”、“在某些实施方案中”、“在各种实施方案中”、“在一个实施方案中”或“在实施方案中”的短语不一定是指本公开的相同实施方案。此外,在一个或多个实施方案中,可以以任何合适的方式来组合特定的特征、结构、材料或特性。

[0140]

尽管在本文中已经参考特定实施方案描述了本公开,但是应理解,这些实施方案仅是本公开的原理和应用的说明。对于本领域的技术人员显而易见的是,在不脱离本公开的精神和范围的情况下,可以对本公开进行各种修改和变化。因此,本公开旨在包括在所附权利要求书及其等同物的范围内的修改和变化。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。