1.公开的技术涉及超导器件、超导器件的制造方法以及层叠体。

背景技术:

2.作为与具有表现出超导的结构部分的超导器件相关的技术,已知有以下的技术。例如,已知有包括基底基板、载体基板和介于基底基板与载体基板之间的埋入金属化层的半导体器件。该半导体器件的制造方法包括下述工序。在载体基板的上表面形成第一导电性金属材料的上部金属化层。接着,在载体基板内形成未填充基板贯通孔直至埋入金属化层。接着,在划定未填充基板贯通孔与载体基板上及第一导电性金属材料层上的包围未填充基板贯通孔的周缘部的表面上,形成第二导电性金属材料的凸块下金属化层。凸块下金属化层与埋入金属化层和上部金属化层结合。第一导电性金属材料与第二导电性金属材料不同。接着,为了形成使未填充基板贯通孔和包围载体基板上及上部金属化层上的未填充基板贯通孔的周缘部露出的开口部,附着牺牲层而形成图案。接着,为了形成被填充的基板贯通孔,在开口部填充第三导电性金属材料。接着,去除牺牲层以形成与被填充的基板贯通孔自对准的圆柱形状的焊料凸块。

3.现有技术文献

4.专利文献

5.专利文献1:日本特表2020-520090号公报

技术实现要素:

6.发明所要解决的问题

7.公开的技术的目的在于,在超导器件中抑制伴随温度变化的应力。

8.用于解决问题的手段

9.公开的技术的超导器件具有基板、设置于所述基板的贯通孔、以及设置于所述贯通孔内的贯通电极。贯通电极具有第一部分和设置于所述第一部分与所述贯通孔的内壁面之间的第二部分,所述第二部分由包含在规定温度以下的温度下表现出超导的第一金属的材料形成。超导器件包括:接合电极,其是与所述贯通电极电连接的电极,至少一部分设置在所述贯通孔的外部,所述接合电极由包含在规定温度以下的温度下表现出超导的第二金属的材料形成;以及隔壁部,其设置在所述贯通电极与所述接合电极之间,由包含所述第一金属的材料形成。所述第一金属的熔点比所述第二金属的熔点高。

10.发明效果

11.根据公开的技术,在超导器件中,能够抑制伴随温度变化的应力。

附图说明

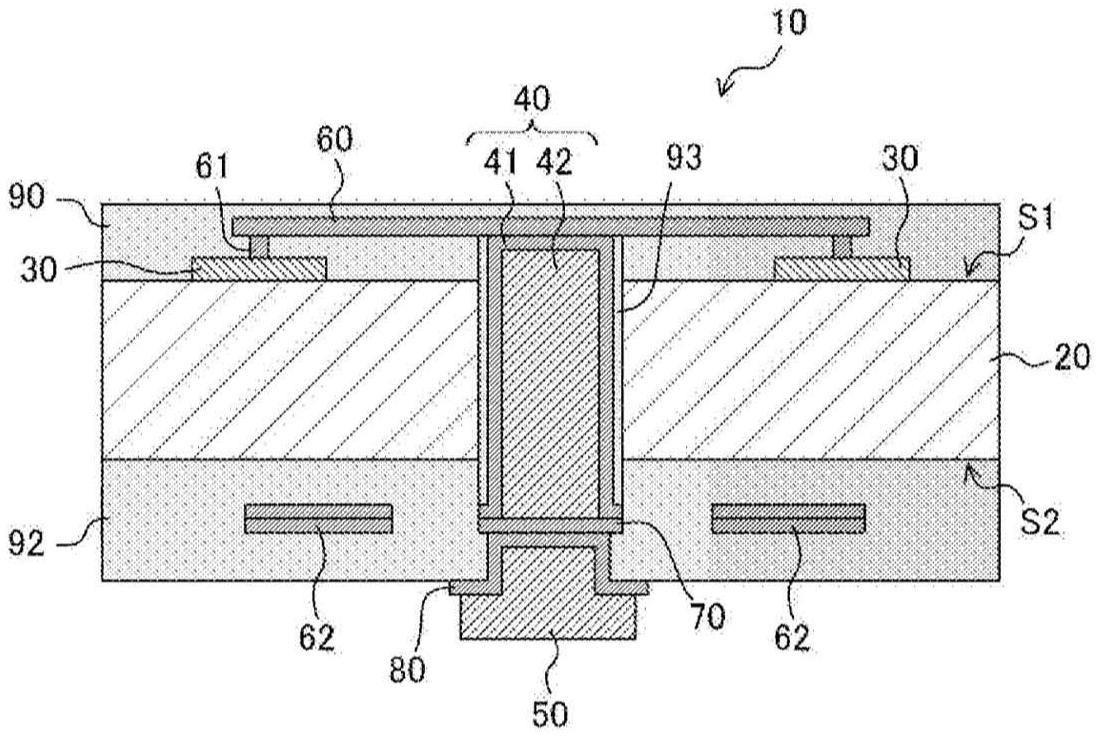

12.图1是表示公开的技术的实施方式的超导器件的结构的一例的剖视图。

13.图2示出了公开的技术的实施方式的超导量子比特元件的结构的一例的图。

14.图3a是表示公开的技术的实施方式的超导器件的制造方法的一例的剖视图。

15.图3b是表示公开的技术的实施方式的超导器件的制造方法的一例的剖视图。

16.图3c是表示公开的技术的实施方式的超导器件的制造方法的一例的剖视图。

17.图3d是表示公开的技术的实施方式的超导器件的制造方法的一例的剖视图。

18.图3e是表示公开的技术的实施方式的超导器件的制造方法的一例的剖视图。

19.图3f是表示公开的技术的实施方式的超导器件的制造方法的一例的剖视图。

20.图3g是表示公开的技术的实施方式的超导器件的制造方法的一例的剖视图。

21.图3h是表示公开的技术的实施方式的超导器件的制造方法的一例的剖视图。

22.图3i是表示公开的技术的实施方式的超导器件的制造方法的一例的剖视图。

23.图3j是表示公开的技术的实施方式的超导器件的制造方法的一例的剖视图。

24.图3k是表示公开的技术的实施方式的超导器件的制造方法的一例的剖视图。

25.图3l是表示公开的技术的实施方式的超导器件的制造方法的一例的剖视图。

26.图3m是表示公开的技术的实施方式的超导器件的制造方法的一例的剖视图。

27.图4a是表示公开的技术的实施方式的超导器件的制造方法的一例的剖视图。

28.图4b是表示公开的技术的实施方式的超导器件的制造方法的一例的剖视图。

29.图4c是表示公开的技术的实施方式的超导器件的制造方法的一例的剖视图。

30.图4d是表示公开的技术的实施方式的超导器件的制造方法的一例的剖视图。

31.图4e是表示公开的技术的实施方式的超导器件的制造方法的一例的剖视图。

32.图4f是表示公开的技术的实施方式的超导器件的制造方法的一例的剖视图。

33.图4g是表示公开的技术的实施方式的超导器件的制造方法的一例的剖视图。

34.图4h是表示公开的技术的实施方式的超导器件的制造方法的一例的剖视图。

35.图4i是表示公开的技术的实施方式的超导器件的制造方法的一例的剖视图。

36.图4j是表示公开的技术的实施方式的超导器件的制造方法的一例的剖视图。

37.图4k是表示公开的技术的实施方式的超导器件的制造方法的一例的剖视图。

38.图5是表示公开的技术的实施方式的超导器件的结构的一例的剖视图。

39.图6是表示公开的技术的实施方式的超导器件的结构的一例的剖视图。

40.图7是表示公开的技术的实施方式的超导器件的结构的一例的剖视图。

41.图8是表示公开的技术的实施方式的层叠体的结构的一例的剖视图。

42.图9是表示公开的技术的实施方式的层叠体的结构的一例的剖视图。

43.图10是表示公开的技术的实施方式的层叠体的结构的一例的剖视图。

44.图11是表示公开的技术的实施方式的层叠体的结构的一例的剖视图。

具体实施方式

45.量子计算机通过使用叠加、量子纠缠这样的量子力学现象,与以往的计算机相比具有压倒性的处理能力。作为用于实现量子计算机的器件,例如提出了使用包含超导材料的约瑟夫森元件的超导器件。约瑟夫森元件是利用了超导状态下的电流的隧道效应的开关元件。超导器件通常在几mk这样的极低温的环境下表现出超导,因此在极低温的环境下使用。

46.另一方面,认为通过将超导器件彼此或超导器件与其他器件层叠,能够实现高密

度安装。在超导器件中,考虑使用贯通电极作为用于实现三维安装的手段。具体而言,设想具备基板、贯穿基板的贯通电极、以及与贯通电极电连接的接合电极的超导器件。超导器件通过回流处理而经由接合电极层叠于其他器件。在该回流处理中,超导器件暴露于接合电极的熔点以上的温度中。在接合电极包含例如sn、pb或它们的合金的情况下,其熔点为200℃以上,回流温度设定为300℃左右。即,在超导器件中,安装时的温度与使用时的温度差为500℃以上。因此,在极低温环境下使用的超导器件中,与在常温环境下使用的一般的器件相比,伴随着贯通电极及接合电极的膨胀、收缩的体积变化变大,这些电极产生裂纹等损伤的风险高。特别是,在专利文献1所记载的贯通电极和接合电极一体地形成的构造中,由于将贯通电极和接合电极形成为一体的构造体的堆积变大,所以体积变化及与之相伴的应力变得更显著。

47.以下,参照附图说明公开的实施方式的一例。另外,在各附图中,对相同或等价的构成要素和部分标注相同的参照标号,适当省略重复的说明。

48.[第一实施方式]

[0049]

图1是表示公开的技术的第一实施方式的超导器件10的结构的一例的剖视图。超导器件10包括基板20、超导量子比特元件30、贯通电极40和接合电极50。

[0050]

基板20由绝缘体或半导体构成。通过使用硅等半导体作为基板20,容易应用现有的半导体加工技术。

[0051]

超导量子比特元件30设置在基板20的面s1侧。超导量子比特元件30是使用超导形成相干的2能级系统的元件。在本实施方式中,超导量子比特元件30构成为包含图2所示的约瑟夫森元件。约瑟夫森元件构成为包括:在规定的临界温度以下的温度下表现出超导的一对超导体31;以及夹在一对超导体31之间的厚度为数nm左右的极薄的绝缘体32。超导体31可以是例如铝,绝缘体32可以是例如氧化铝。超导量子比特元件30经由通孔61与配线60连接。通孔61及配线60分别由在规定温度以下的温度下表现出超导的高熔点金属构成。关于高熔点金属的详细情况在后面叙述。基板20的面s1被由sio2等绝缘体构成的绝缘体层90覆盖,超导量子比特元件30、通孔61及配线60埋设于绝缘体层90内。

[0052]

贯通电极40贯穿基板20。贯通电极40的一端与设置在基板20的面s1侧的配线60连接,另一端经由设置在基板20的面s1的相反侧的面s2侧的盖膜70与接合电极50连接。即,贯通电极40作为将从设置于基板20的面s1侧的超导量子比特元件30输出的量子比特传输至设置于基板20的面s2侧的接合电极50的传输路径发挥功能。

[0053]

贯通电极40构成为包含外侧部分41和内侧部分42。外侧部分41由在规定温度以下的温度下表现出超导的高熔点金属构成,包围内侧部分42。内侧部分42由在规定温度以下的温度下表现出超导的低熔点金属构成。即,在贯通电极40的内侧填充有在规定温度以下的温度下表现出超导的低熔点金属。关于低熔点金属的详细情况在后面叙述。贯通电极40的位于基板20的面s2侧的端部被盖膜70堵塞。盖膜70由在规定温度以下的温度下表现出超导的高熔点金属构成。盖膜70作为将贯通电极40与接合电极50隔开的隔壁部发挥功能。构成贯通电极40的内侧部分42的低熔点金属被构成贯通电极40的高熔点金属和构成盖膜70的高熔点金属完全包围(密封)。在基板20与贯通电极40之间,设置有由sio2等绝缘体构成的绝缘膜93。即,基板20与贯通电极40被电分离。基板20的面s2被绝缘体层92覆盖。盖膜70埋设在绝缘体层92内,贯通电极40的位于基板20的s2侧的端部到达绝缘体层92的内部。

[0054]

接合电极50具有所谓的凸块的形态,作为用于将超导器件10与其他器件接合的外部连接端子发挥功能。接合电极50被设置在基板20的面s2侧,并经由盖膜70以及基底膜80而与贯通电极40连接。在本实施方式中,接合电极50设置在贯通电极40的紧下方。接合电极50由在规定温度以下的温度下表现出超导的低熔点金属构成。接合电极50具有埋设于绝缘体层92内的部分和从绝缘体层92的表面露出的部分。基底膜80介于接合电极50与绝缘体层92之间。基底膜80作为所谓凸块下金属发挥功能,具有抑制构成接合电极50的低熔点金属向绝缘体层92内扩散的功能以及提高接合电极50与绝缘体层92的紧贴性的功能。另外,基底膜80作为将贯通电极40与接合电极50隔开的隔壁部发挥功能。基底膜80由在规定温度以下的温度下表现出超导的高熔点金属构成。

[0055]

在绝缘体层92内设置有不与超导量子比特元件30电连接的虚设配线62。虚设配线62的电位例如既可以为接地电位,也可以为浮动电位。为了取得基板20的面s1侧的配线密度与基板20的面s2侧的配线密度的平衡而根据需要设置虚设配线62。在基板20的面s1侧的配线密度与基板20的面s2侧的配线密度不均匀的情况下,在基板20产生的翘曲变得显著。通过在基板20的面s2侧适当设置虚设配线62,取得基板20的两面的配线密度的平衡,能够抑制在基板20产生的翘曲。另外,也可以在基板20的面s2侧设置与超导量子比特元件30电连接的配线或具有特定的电气功能的配线。另外,也可以在基板20的面s2侧以混合存在的方式设置虚设配线和具有特定的电气功能的配线。

[0056]

如上所述,通孔61、配线60、贯通电极40的外侧部分41、盖膜70以及基底膜80分别由在规定温度以下的温度下表现出超导的高熔点金属构成。分别构成通孔61、配线60、贯通电极40的外侧部分41、盖膜70以及基底膜80的高熔点金属优选为彼此相同的金属。另外,如上所述,贯通电极40的内侧部分42和接合电极50分别由在规定温度以下的温度下表现出超导的低熔点金属构成。分别构成贯通电极40的内侧部分42和接合电极50的低熔点金属优选为彼此相同的金属。

[0057]

在本说明书中,高熔点金属是指熔点为800℃以上的金属,低熔点金属是指熔点为300℃以下的金属。作为在规定温度以下的温度下表现出超导的高熔点金属的例子,可举出ta、nb、v、mo或以它们为主成分的合金或它们的氮化物等。作为在规定温度以下的温度下表现出超导的低熔点金属的例子,可举出sn、pb、in、ga或以它们为主成分的合金等。此外,高熔点金属是公开技术中的第一金属的一例。低熔点金属是公开技术中的低熔点金属的一例。

[0058]

优选在规定温度以下的温度下表现出超导的高熔点金属及低熔点金属与基板20的热膨胀系数之差小。例如,在基板20为si基板的情况下,作为高熔点金属,优选使用mo或ta,作为低熔点金属,优选使用ga或sn。

[0059]

此外,通过使用具有相对低的熔点的ga(具有29.8℃的熔点)或in(具有156.6℃的熔点)作为在规定温度以下的温度下表现出超导的低熔点金属,可以减小安装超导器件10时的温度与使用超导器件10时的温度之差,并且可以抑制由温度变化引起的体积变化和与之相伴的应力。

[0060]

另外,从加工的容易性的观点出发,可以选择用作在规定温度以下的温度下表现出超导的高熔点金属和低熔点金属的金属。例如,作为高熔点金属的ta和作为低熔点金属的sn均能够通过氯系的反应性干蚀刻进行图案化。

[0061]

以下,对超导器件10的制造方法进行说明。图3a~图3m是表示超导器件10的制造方法的一例的剖视图。

[0062]

首先,在例如由si等半导体构成的基板20的面s1上形成超导量子比特元件30。接着,例如通过cvd(chemical vapor deposition:化学气相沉积)法,在基板20的面s1上形成构成绝缘体层90的由sio2等绝缘体构成的绝缘体膜。超导量子比特元件30埋设于绝缘体层90内(图3a)。

[0063]

接着,在形成与超导量子比特元件30连接的通孔61之后,例如通过溅射法在绝缘体层90的表面堆积在规定温度以下的温度下表现出超导的高熔点金属(例如ta)。然后,通过将该高熔点金属图案化,形成配线60。配线60被构成绝缘体层90的由sio2等绝缘体构成的绝缘膜覆盖(图3b)。通孔61由与配线60相同的高熔点金属(例如ta)构成。

[0064]

接着,对基板20的面s2侧进行磨削,使基板20薄化。作为基板20的薄化处理的精加工,实施cmp(chemical mechanical polishing:化学机械抛光)以及药液处理。接着,例如通过cvd法在基板20的面s2上形成由sio2等绝缘体构成的绝缘体层92(图3c)。

[0065]

接下来,通过使用了例如博世工艺(bosch process)的反应性离子蚀刻,从而形成从绝缘体层92的表面起贯穿基板20而到达配线60的贯通孔45。博世工艺是通过反复进行基板20的各向同性蚀刻、保护膜(未图示)的堆积、基板20的各向异性蚀刻(底面的保护膜的除去)这3个步骤,从而以高速且高纵横比实现基板20的垂直的深挖的干式蚀刻技术。当贯通孔45到达配线60时,蚀刻停止(图3d)。

[0066]

接着,例如通过cvd法在贯通孔45的侧面形成由sio2等绝缘体构成的绝缘膜93。接着,例如通过溅射法,在基板20的面s2侧堆积与配线60相同的高熔点金属m1(例如ta)。绝缘体层92的表面、贯通孔45的侧面以及底面被高熔点金属m1覆盖。高熔点金属m1的覆盖贯通孔45的侧面及底面的部分成为贯通电极40的外侧部分41,高熔点金属m1的覆盖绝缘体层92的表面的部分成为虚设配线62的一部分。贯通电极40的外侧部分41在贯通孔45的底面与配线60连接(图3e)。

[0067]

接着,例如通过溅射法在高熔点金属m1的表面形成种子(seed)层(未图示)后,通过镀覆法在高熔点金属m1上堆积在规定温度以下的温度下表现出超导的低熔点金属m2(例如sn)。低熔点金属m2填充于贯通孔45,由此形成贯通电极40的内侧部分42(图3f)。

[0068]

接着,通过例如cmp,除去堆积在绝缘体层92上的剩余的低熔点金属m2。之后,例如通过溅射法,在基板20的面s2侧进一步堆积与配线60及贯通电极40的外侧部分41相同的高熔点金属m1(例如ta)(图3g)。

[0069]

接着,对高熔点金属m1进行图案化。由此,在基板20的面s2侧形成虚设配线62,并且形成堵塞贯通电极40的位于基板20的面s2侧的端部的盖膜70(图3h)。

[0070]

虚设配线62被构成绝缘体层92的由sio2等绝缘体构成的绝缘膜覆盖(图3i)。接着,例如通过反应性离子蚀刻,形成从绝缘体层92的表面到达盖膜70的接触孔95(图3j)。

[0071]

接下来,例如通过溅射法,在基板20的面s2侧堆积与配线60、贯通电极40的外侧部分41、盖膜70以及虚设配线62相同的高熔点金属(例如ta),并对该高熔点金属进行图案化,从而形成基底膜80。基底膜80在接触孔95的底面与盖膜70连接(图3k)。

[0072]

接着,在绝缘体层92的表面形成阻焊剂55。在阻焊剂55设置有使基底膜80露出的开口部。接着,通过镀敷法,在基底膜80上堆积与贯通电极40的内侧部分42相同的低熔点金

属(例如sn)。由此,形成接合电极50(图3l)。最后,去除阻焊剂55(图3m)。

[0073]

在上述的说明中,例示了从基板20的面s2侧形成用于形成贯通电极40的贯通孔45的情况下的制造方法,但也可以从基板20的面s1侧形成贯通孔45。以下,参照图4a~图4k对从基板20的面s1侧形成贯通孔45的情况下的制造方法进行说明。

[0074]

例如通过使用博世工艺的反应性离子蚀刻,从基板20的形成有超导量子比特元件30及绝缘体层90的面s1侧形成贯通孔45。蚀刻在贯通孔45到达面s2之前停止(图4a)。

[0075]

接下来,例如通过cvd法,在贯通孔45的侧面以及底面形成由sio2等绝缘体构成的绝缘膜93。接着,例如通过溅射法,在基板20的面s1侧堆积在规定温度以下的温度下表现出超导的高熔点金属m1(例如ta)。绝缘体层90的表面、贯通孔45的侧面以及底面被高熔点金属m1覆盖。高熔点金属m1的覆盖贯通孔45的侧面及底面的部分成为贯通电极40的外侧部分41(图4b)。

[0076]

接着,例如通过溅射法在高熔点金属m1的表面形成种子层(未图示)后,通过镀覆法在高熔点金属m1上堆积在规定温度以下的温度下表现出超导的低熔点金属m2(例如sn)。低熔点金属m2填充于贯通孔45中,由此形成贯通电极40的内侧部分42(图4c)。

[0077]

接着,通过例如cmp,除去堆积在绝缘体层90上的剩余的低熔点金属m2。之后,例如通过溅射法,在基板20的面s1侧进一步堆积与贯通电极40的外侧部分41相同的高熔点金属m1(例如ta)(图4d)。

[0078]

接着,对高熔点金属m1进行图案化。由此,形成堵塞贯通电极40的位于基板20的面s1侧的端部的盖膜70(图4e)。

[0079]

接着,在形成与超导量子比特元件30连接的通孔61之后,例如通过溅射法,在基板20的面s1侧堆积与贯通电极40的外侧部分41以及盖膜70相同的高熔点金属(例如ta)之后,对该高熔点金属进行图案化。由此,形成与超导量子比特元件30及贯通电极40电连接的配线60(图4f)。

[0080]

配线60被构成绝缘体层90的由sio2等绝缘体构成的绝缘膜覆盖。接着,对基板20的面s2侧进行磨削,使基板20薄化直至贯通电极40露出。作为基板20的薄化处理的精加工,实施cmp及药液处理。接着,例如通过cvd法在基板20的面s2上形成由sio2等绝缘体构成的绝缘体层92(图4g)。

[0081]

接着,例如通过反应性离子蚀刻,形成从绝缘体层92的表面到达贯通电极40的接触孔95(图4h)。接下来,例如通过溅射法,在基板20的面s2侧堆积与配线60、贯通电极40的外侧部分41以及盖膜70相同的高熔点金属(例如ta),并对该高熔点金属进行图案化,从而形成基底膜80。基底膜80在接触孔95的底面与贯通电极40连接(图4i)。

[0082]

接着,在绝缘体层92的表面形成阻焊剂55。在阻焊剂55设置有使基底膜80露出的开口部。接着,通过镀敷法,在基底膜80上堆积与贯通电极40的内侧部分42相同的低熔点金属(例如sn)。由此,形成接合电极50(图4j)。最后,除去阻焊剂55(图4k)。

[0083]

如上所述,根据本实施方式的超导器件10,由于具有贯穿基板20的贯通电极40,因此能够进行将超导器件10和其他器件层叠的三维安装。超导器件10经由接合电极50与其他器件接合。在超导器件10与其他器件的接合中,进行用于使接合电极50熔融的回流处理。通过回流处理中的加热,接合电极50和贯通电极40的体积有可能变化。在本实施方式的超导器件10中,接合电极50配置在贯通电极40的紧下方,将接合电极50和贯通电极40形成为一

体的结构体的体积容易变大,由体积变化引起的应力成为问题。然而,根据本实施方式的超导器件10,由高熔点金属构成的盖膜70及基底膜80作为将贯通电极40与接合电极50隔开的隔壁部发挥功能。一般而言,由于高熔点金属与低熔点金属相比热膨胀率较小,因此通过利用由高熔点金属构成的隔壁部而将贯通电极40和接合电极50隔开,从而能够将贯通电极40中的体积变化和接合电极50中的体积变化截断。由此,能够抑制伴随着贯通电极40及接合电极50的体积变化的应力。

[0084]

另外,构成贯通电极40的内侧部分42的低熔点金属被构成贯通电极40的外侧部分的高熔点金属和构成盖膜70的高熔点金属完全包围(密封)。贯通电极40的内侧部分42的伴随温度变化的体积变化被包围贯通电极40的内侧部分42的高熔点金属限制,因此能够抑制贯通电极40的伴随温度变化的体积变化。另外,在回流处理中,构成贯通电极40的内侧部分42的低熔点金属会熔融,但构成贯通电极40的外侧部分41的高熔点金属不熔融,因此能够抑制构成熔融的内侧部分42的低熔点金属向基板20中扩散。

[0085]

另外,在本实施方式的超导器件10中,配线60、贯通电极40的外侧部分41、盖膜70及基底膜80全部由相同的高熔点金属构成。由此,避免在使用异种金属的情况下的合金的形成。若形成合金,则去相干效应增大,有可能难以维持量子力学的叠加状态。

[0086]

另外,在以上的说明中,例示了由在规定温度以下的温度下表现出超导的低熔点金属构成贯通电极40的内侧部分42的方式,但并不限定于此。例如,贯通电极40的内侧部分42也可以由与基板20同种的材料或构成基板20的材料的氧化物构成。即,也可以在贯通电极40的内侧填充与基板20同种的材料或构成基板20的材料的氧化物。例如,在基板20为si基板的情况下,贯通电极40的内侧部分42也可以由多晶硅或sio2构成。构成贯通电极40的内侧部分42的、与基板20同种的材料或构成基板20的材料的氧化物被在规定温度以下的温度下表现出超导的高熔点金属包围。通过由与基板20同种的材料或构成基板20的材料的氧化物构成贯通电极40的内侧部分42,贯通电极40及基板20的伴随着温度变化的体积变化以大致相同的比例产生(即,贯通电极40及基板20的热膨胀率大致相同),所以能够抑制伴随着温度变化的应力。

[0087]

另外,贯通电极40的内侧部分42也可以由绝缘体构成。另外,对于贯通电极40,也可以由与外侧部分41相同的高熔点金属构成贯通电极40的内侧部分42。由此,与由低熔点金属构成贯通电极40的内侧部分42的情况相比,能够抑制贯通电极40的伴随着温度变化的体积变化。需要说明的是,通常高熔点金属难以通过镀覆法成膜,因此作为用于对贯通电极40的内侧进行充电的成膜法,应用溅射法或cvd法。

[0088]

另外,如图5所示,贯通电极40的内侧部分42也可以是空洞。由此,与由低熔点金属构成贯通电极40的内侧部分42的情况相比,能够抑制贯通电极40的伴随着温度变化的体积变化。在将贯通电极40的内侧部分42设为空洞的情况下,从确保机械强度的观点出发,接合电极50优选设置于在基板20的主面方向上从贯通电极40偏离的位置。另外,贯通电极40表现出超导,因此电阻不会成为问题。因此,能够仅由构成外侧部分41的薄膜的高熔点金属构成贯通电极40。

[0089]

[第二实施方式]

[0090]

图6是表示公开的技术的第二实施方式的超导器件10a的结构的一例的剖视图。根据本实施方式的超导器件10a具有对器件之间的信号传输进行中介的中介层的形态,并且

与第一实施方式的超导器件10的不同之处在于,超导器件10a不包括超导量子比特元件。超导器件10a包括基板20、贯通电极40和接合电极50。

[0091]

基板20由绝缘体或半导体构成。通过使用硅等半导体作为基板20,容易应用现有的半导体加工技术。

[0092]

贯通电极40的一端经由设置在基板20的面s1侧的盖膜70与接合电极50连接,另一端经由设置在基板20的面s2侧的盖膜70与接合电极50连接。

[0093]

贯通电极40的外侧部分41由在规定温度以下的温度下表现出超导的高熔点金属构成,包围内侧部分42。贯通电极40的内侧部分42由在规定温度以下的温度下表现出超导的低熔点金属构成。贯通电极40的两端由盖膜70封闭。盖膜70由与贯通电极40的外侧部分41相同的高熔点金属构成。盖膜70作为将贯通电极40与接合电极50隔开的隔壁部发挥功能。构成贯通电极40的内侧部分42的低熔点金属被构成贯通电极40的外侧部分41的高熔点金属和构成盖膜70的高熔点金属完全包围(密封)。

[0094]

接合电极50设置在基板20的面s1侧及面s2侧两方。接合电极50由与贯通电极40的内侧部分42相同的低熔点金属构成。基底膜80介于接合电极50与绝缘体层90、92之间。基底膜80作为所谓的凸块下金属而发挥功能,并具有抑制构成接合电极50的低熔点金属向绝缘体层90、92内扩散的功能以及提高接合电极50与绝缘体层90、92的紧贴性的功能。另外,基底膜80作为将贯通电极40与接合电极50隔开的隔壁部发挥功能。基底膜80由与贯通电极40的外侧部分41和盖膜70相同的高熔点金属构成。

[0095]

基板20的面s1侧的接合电极50与第一器件(未图示)接合,基板20的面s2侧的接合电极50与第二器件(未图示)接合。第一器件和第二器件能够经由贯通电极40进行信号传输。本实施方式的超导器件10a的制造方法可以应用用于制造第一实施方式的超导器件10的各种工艺,因此省略其描述。

[0096]

根据本实施方式的超导器件10a,与第一实施方式的超导器件10同样地,贯通电极40和接合电极50被隔壁部分隔,因此能够抑制伴随温度变化的应力。

[0097]

另外,贯通电极40的内侧部分42也可以由与基板20同种的材料或构成基板20的材料的氧化物构成。另外,贯通电极40的内侧部分42也可以由绝缘体构成。另外,贯通电极40的内侧部分42也可以由与贯通电极40的外侧部分41相同的高熔点金属构成。另外,如图7所示,贯通电极40的内侧部分42也可以是空洞。在将贯通电极40的内侧部分42设为空洞的情况下,从确保机械强度的观点出发,接合电极50优选设置于在基板20的主面方向上从贯通电极40偏离的位置。

[0098]

[第三实施方式]

[0099]

图8是表示公开的技术的第三实施方式的层叠体100的结构的一例的剖视图。层叠体100通过将上述第一实施方式的超导器件10和其他器件11层叠而构成的。其他器件11可以是例如具有读取从超导器件10输出的量子比特的功能的读取器件。超导器件10的接合电极50与设置于其他器件11的基板21的表面的焊盘25接合。

[0100]

在超导器件10与其他器件11的接合中,进行用于使接合电极50熔融的回流处理。在超导器件10中,由高熔点金属构成的盖膜70及基底膜80作为将贯通电极40与接合电极50隔开的隔壁部发挥功能,因此能够将贯通电极40中的体积变化与接合电极50中的体积变化断开。由此,能够抑制伴随着贯通电极40及接合电极50的体积变化的应力。

[0101]

此外,如图9所示,在超导器件10中,也可以在基板20的面s1侧以及面s2侧两方设置接合电极50,在基板20的面s1侧以及面s2侧两方层叠其他器件11、12。超导器件10的面s2侧的接合电极50与设置于其他器件11的基板21的表面的焊盘25接合,超导器件10的面s1侧的接合电极50与设置于其他器件12的基板22的表面的焊盘26接合。

[0102]

另外,如图10所示,超导器件10与其他器件11的接合也可以不是经由接合电极50的接合,而是基于常温接合或粘接剂的接合。在图10所示的层叠体100中,在通过常温接合或粘接剂将设置在超导器件10的基板20的面s2侧的绝缘体层92和设置在其他器件11的基板21的面s3侧的绝缘体层98接合之后,形成贯通电极40。贯通电极40与设置于其他器件11的基板21的正面的焊盘25连接。超导器件10具有设置于基板20的面s1侧的接合电极50。在超导器件10上,能够经由接合电极50进一步接合其他器件(未图示)。

[0103]

图11是示出包括上述第二实施方式的超导器件10a和其他器件11、12的层叠体的结构的一例的剖视图。超导器件10a是对其他器件11和12中的信号传输进行中介的中介层。例如,其他器件12可以具有输出量子比特的功能,其他器件11可以具有读出量子比特的功能。超导器件10a的面s2侧的接合电极50与设置于其他器件11的基板21的表面的焊盘25接合,超导器件10的面s1侧的接合电极50与设置于其他器件12的基板22的表面的焊盘26接合。

[0104]

标记说明

[0105]

10、10a超导器件

[0106]

11、12其他器件

[0107]

20、21、22基板

[0108]

30 超导量子比特元件

[0109]

40 贯通电极

[0110]

41 外侧部分

[0111]

42 内侧部分

[0112]

45 贯通孔

[0113]

50 接合电极

[0114]

60 配线

[0115]

61 通孔

[0116]

62 虚设配线

[0117]

70 盖膜

[0118]

80 基底膜

[0119]

90、92 绝缘体层

[0120]

100 层叠体

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。