1.本技术属于上电复位技术领域,尤其涉及一种上电复位检测电路、集成电路以及芯片。

背景技术:

2.在大规模集成电路系统中,都需要具备一个可靠的上电复位检测系统,其作用是实时检测芯片的供电系统是否正常。当芯片的电源电压低于监测电压点时需要提供一个复位信号,将模拟电路与数字电路复位,系统初始化;而当芯片的电源电压高于监测电压点时需要提供一个复位释放信号,允许系统开始正常工作。传统的上电复位检测系统的核心是一个电压检测电路,通过对电源电压采用分压电阻进行分压采样,然后将采样得到的电压与参考电压进行比较,然后再经过一级反相处理后得到上电复位检测信号。

3.然而,在低功耗应用系统(比如可穿戴设备)中,芯片的功耗和面积资源非常珍贵,在这种应用环境中,目前的传统结构就会占据较大的芯片面积,增加不必要的成本开销,是一个需要改进的问题。

技术实现要素:

4.为了解决上述技术问题,本技术实施例提供了一种上电复位检测电路、集成电路以及芯片,旨在解决目前的上电复位检测方案存在的分压电阻占用较大的芯片面积,导致成本增加的问题。

5.本技术实施例第一方面提供了一种上电复位检测电路,所述上电复位检测电路包括:镜像电流模块、第一nmos器件、第二nmos器件、第三nmos器件、第四nmos器件以及反相模块;所述镜像电流模块与供电端连接,用于根据供电端提供的电源生成多路镜像电流;所述第四nmos器件的漏极连接所述镜像电流模块的第一电流输出端,所述第三nmos器件的漏极和所述第三nmos器件的栅极共接于所述镜像电流模块的第二电流输入端,所述第一nmos器件的漏极、所述第一nmos器件的栅极、所述第二nmos器件的栅极以及所述第三nmos器件的源极共接,所述第二nmos器件的漏极与所述镜像电流模块的第三电流输出端共接于所述反相模块的输入端,所述第四nmos器件的栅极、所述第四nmos器件的源极、所述第一nmos器件的源极以及所述第二nmos器件的源极共接于地;所述反相模块用于对输入的电压进行反相处理后输出上电复位检测信号。

6.在一个实施例中,所述镜像电流模块包括:第一pmos器件、第二pmos器件、第三pmos器件;所述第一pmos器件的源极、所述第二pmos器件的源极、所述第三pmos器件的源极共接于所述供电端,所述第一pmos器件的栅极、所述第二pmos器件的栅极、所述第三pmos器件的栅极以及所述第三pmos器件的漏极共接作为所述镜像电流模块的第一电流输出端,所

述第一pmos器件的漏极作为所述镜像电流模块的第二电流输出端,所述第二pmos器件的漏极作为所述镜像电流模块的第三电流输出端。

7.在一个实施例中,所述第一pmos器件、所述第二pmos器件、所述第三pmos器件的宽长比相同。

8.在一个实施例中,所述第一pmos器件、所述第二pmos器件的宽长比相同。

9.在一个实施例中,所述第四nmos器件为零阈值电压mos管。

10.在一个实施例中,所述第四nmos器件的阈值电压的电压范围为-1v~0.2v。

11.在一个实施例中,所述第二nmos器件的宽长比是所述第一nmos器件的宽长比的2倍。

12.在一个实施例中,所述反相模块为施密特反相器。

13.本技术实施例第二方面还提供了一种集成电路,包括如上述任一项所述的上电复位检测电路。

14.本技术实施例第三方面还提供了一种芯片,包括如上述任一项所述的上电复位检测电路。

15.本技术实施例的有益效果:由镜像电流模块根据供电端提供的电源生成多路镜像电流,第四nmos器件的漏极接收第一路镜像电流,第三nmos器件的漏极和第三nmos器件的栅极共接接收第二路镜像电流,第一nmos器件的漏极、第一nmos器件的栅极、第二nmos器件的栅极以及第三nmos器件的源极共接,第二nmos器件的漏极、反相模块的输入端共接并接入第三路镜像电流,第四nmos器件的栅极、第四nmos器件、第一nmos器件以及第二nmos器件的源极共接于地,反相模块对输入电压进行反相处理后输出上电复位检测信号,从而无需分压电路即可实现芯片的上电复位检测。

附图说明

16.图1是本技术实施例提供的上电复位检测电路的示意图一;图2是本技术实施例提供的上电复位检测电路的示意图二;图3是本技术实施例提供的上电复位检测电路中各节点的电压波形示意图。

具体实施方式

17.为了使本技术所要解决的技术问题、技术方案及有益效果更加清楚明白,以下结合附图及实施例,对本技术进行进一步详细说明。应当理解,此处所描述的具体实施例仅仅用以解释本技术,并不用于限定本技术。

18.需要说明的是,当元件被称为“固定于”或“设置于”另一个元件,它可以直接在另一个元件上或者间接在该另一个元件上。当一个元件被称为是“连接于”另一个元件,它可以是直接连接到另一个元件或间接连接至该另一个元件上。

19.需要理解的是,术语“长度”、“宽度”、“上”、“下”、“前”、“后”、“左”、“右”、“竖直”、“水平”、“顶”、“底”“内”、“外”等指示的方位或位置关系为基于附图所示的方位或位置关系,仅是为了便于描述本技术和简化描述,而不是指示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本技术的限制。

20.此外,术语“第一”、“第二”仅用于描述目的,而不能理解为指示或暗示相对重要性

或者隐含指明所指示的技术特征的数量。由此,限定有“第一”、“第二”的特征可以明示或者隐含地包括一个或者更多个该特征。在本技术的描述中,“多个”的含义是一个或一个以上,除非另有明确具体的限定。

21.目前传统的上电复位检测系统的核心是一个电压检测电路,通过对电源电压采用分压电阻进行分压采样,然后将采样得到的电压与参考电压进行比较,然后再经过一级反相处理后得到上电复位检测信号。

22.然而,在低功耗应用系统(比如可穿戴设备)中,芯片的功耗和面积资源非常珍贵,在这种环境中上述的传统结构就会存在一个缺陷,即分压电路(例如由分压电阻和分压电阻串联形成)会占据较大的芯片面积,在电源电压为5v,要求上电复位部分模块的功耗小于100na的系统中,此时所需要的电阻至少为100mω(假定比较器消耗了一半的功耗,所以分压电阻实际消耗50na),这将浪费很大的芯片面积,增加不必要的成本开销,是一个需要改进的问题。

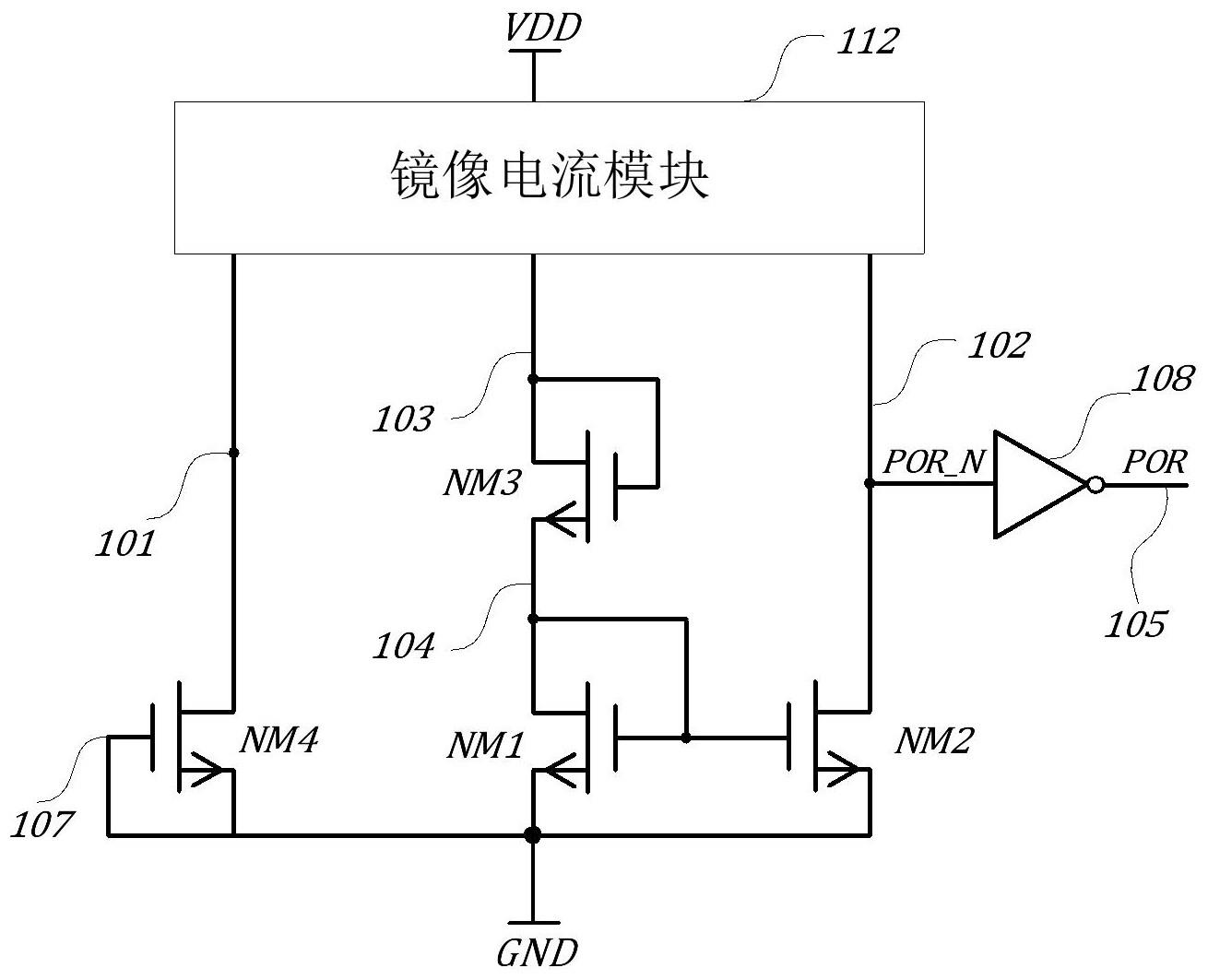

23.为了解决上述技术问题,本技术实施例提供了一种上电复位检测电路,参见图1所示,本实施例中的上电复位检测电路包括:镜像电流模块112、第一nmos器件nm1、第二nmos器件nm2、第三nmos器件nm3、第四nmos器件nm4以及反相模块108。

24.参见图1所示,镜像电流模块112与供电端vdd连接,镜像电流模块112用于根据供电端vdd提供的电源生成多路镜像电流;第四nmos器件nm4的漏极连接镜像电流模块112的第一电流输出端,第三nmos器件nm3的漏极和第三nmos器件nm3的栅极共接于镜像电流模块112的第二电流输入端,第一nmos器件nm1的漏极、第一nmos器件nm1的栅极、第二nmos器件nm2的栅极以及第三nmos器件nm3的源极共接,第二nmos器件nm2的漏极与镜像电流模块112的第三电流输出端共接于反相模块108的输入端,第四nmos器件nm4的栅极、第四nmos器件nm4的源极、第一nmos器件nm1的源极以及第二nmos器件nm2的源极共接于地gnd;反相模块108用于对输入的电压进行反相处理后输出上电复位检测信号。

25.在本实施例中,第四nmos器件nm4的栅极与源极共接于节点107,此时第四nmos器件nm4可以作为一个独立的电流源工作,其具体的电流表达式可以为ib=(1/2)*μ*c*(w/l)*v

th12

,其中,μ和c为工艺参数,μ为第四nmos器件nm4的表面迁移率,c为第四nmos器件nm4的单位面积栅氧化物的电容,w/l为第四nmos器件nm4的宽长比,v

th1

为第四nmos器件nm4的阈值电压(接近或者小于0v),ib为流过第四nmos器件nm4的电流。

26.上电复位检测电路工作时,供电端vdd接电源电压,当电源电压从0v开始上升时,电源电压的增加,会使得第四nmos器件nm4最先产生电流,由于镜像电流模块112的第一电流输出端连接第四nmos器件nm4的漏极,该电流会通过镜像电流模块112被镜像至镜像电流模块112的第二电流输出端和第三电流输出端,并由镜像电流模块112的第二电流输出端和第三电流输出端输出镜像电流。结合图1所示,由于电源电压从0v才开始上升,此时,节点103和节点104处的电流路径处于关断状态,镜像电流模块112的第二电流输出端无电流输出,第一nmos器件nm1和第二nmos器件nm2均处于截止状态。而镜像电流模块112的第三电流输出端正常输出镜像电流,从而将节点102的电压信号por_n上拉为高电平(如图3中的电压曲线211),经过反相模块108后由反相模块108对电压信号por_n进行一级反相处理得到上电复位检测信号por,此时,位于反相模块108的输出端的节点105的电压为低电平。结合图3所示,当供电端vdd的电压达到监测电压v

check

时,镜像电流模块112的第二

电流输出端输出的镜像电流使得第一nmos器件nm1、第二nmos器件nm2由截止状态转换为导通状态,节点102的电压信号por_n(如图3中的电压曲线211)又会被第二nmos器件nm2下拉变成低电平,节点102的电压信号por_n经过反相模块108反相处理后所得到的上电复位检测信号por为高电平(如图3中的电压曲线221),从而完成对供电端vdd所接入的电源的电压检测。

27.为了推导温度补偿的表达式,下面可以忽略mos管的体效应对上电复位检测电路的工作原理进行说明。

28.在忽略mos管的体效应的情况下,将第一nmos器件nm1和第三nmos器件nm3等效为阻值为2/gm的负载电阻,其中,gm为第一nmos器件nm1和第三nmos器件nm3的跨导。

29.此时,监测电压v

check

的表达式如下:;

30.w

nm3

/l

nm3

为第三nmos器件nm3的宽长比,由于工艺参数μ、μn以及阈值电压v

th1

均是温度相关的参数,μn为nmos器件的表面迁移率,cn为nmos器件的单位面积栅氧化物的电容,n用于区分不同的器件,例如,μ1表示第一nmos器件nm1的表面迁移率,c1表示第一nmos器件nm1的单位面积栅氧化物的电容,μ3表示第三nmos器件nm3的表面迁移率,c3表示第三nmos器件nm3的单位面积栅氧化物的电容,以此类推,因此,通过调整w/l与第三nmos器件nm3的宽长比w

nm3

/l

nm3

之间的倍数关系即可实现监测点(即监测电压v

check

)的温度补偿。

31.在一个实施例中,参见图2所示,镜像电流模块112包括:第一pmos器件pm1、第二pmos器件pm2、第三pmos器件pm3;第一pmos器件pm1的源极、第二pmos器件pm2的源极、第三pmos器件pm3的源极共接于供电端vdd,第一pmos器件pm1的栅极、第二pmos器件pm2的栅极、第三pmos器件pm3的栅极以及第三pmos器件pm3的漏极共接作为镜像电流模块112的第一电流输出端,第一pmos器件pm1的漏极作为镜像电流模块112的第二电流输出端,第二pmos器件pm2的漏极作为镜像电流模块112的第三电流输出端。

32.在本实施例中,第一pmos器件pm1的栅极、第二pmos器件pm2的栅极以及第三pmos器件pm3的栅极共接节点vbp,从而将流过第三pmos器件pm3的电流镜像到第一pmos器件pm1和第二pmos器件pm2。第一pmos器件的漏极和栅极共接于节点101,此时节点101作为镜像电流模块112的第一电流输出端,第一pmos器件pm1的漏极作为镜像电流模块112的第二电流输出端,第二pmos器件pm2的漏极作为镜像电流模块112的第三电流输出端。

33.当供电端vdd的电压达到监测电压v

check

时,第一pmos器件、第一nmos器件nm1、第二nmos器件nm2由截止状态转换为导通状态,因为,i

nm2

=2i

nm1

=2i

pm2

,所以节点102的电压信号por_n(如图3中的电压曲线211)又会被第二nmos器件nm2下拉变成低电平,节点102的电压信号por_n经过反相模块108反相处理后所得到的上电复位检测信号por为高电平(如图3中的电压曲线221),从而完成对供电端vdd所接入的电源的电压检测。

34.在一个实施例中,第一pmos器件pm1、第二pmos器件pm2、第三pmos器件pm3的宽长比相同。

35.在本实施例中,第一pmos器件pm1、第二pmos器件pm2、第三pmos器件pm3均为标准

的pmos器件。由于第一pmos器件pm1、第二pmos器件pm2、第三pmos器件pm3的宽长比相同,所以在上电复位检测电路正常工作的情况下,第一pmos器件pm1、第二pmos器件pm2、第三pmos器件pm3具有同样的电流能力。

36.在一个实施例中,第一pmos器件pm1、第二pmos器件pm2的宽长比相同。

37.在一个实施例中,第一nmos器件nm1、第二nmos器件nm2、第三nmos器件nm3均为标准的nmos器件。

38.在一个实施例中,第四nmos器件nm4为零阈值电压mos管。

39.在本实施例中,第四nmos器件nm4为零阈值电压mos管,零阈值电压mos管的阈值电压接近或者小于0v。

40.在一个实施例中,第四nmos器件nm4的阈值电压的电压范围为-1v~0.2v。

41.在本实施例中,第四nmos器件nm4可以为一种零阈值电压mos管,其阈值电压接近或者小于0v,并且第四nmos器件nm4的栅极与源极共接于节点107,此时第四nmos器件nm4可以作为一个独立的电流源工作。

42.在一个实施例中,第二nmos器件nm2的宽长比是第一nmos器件nm1的宽长比的2倍。

43.在本实施例中,由于第二nmos器件nm2的宽长比是第一nmos器件nm1的宽长比的2倍,所以在上电复位检测电路正常工作的情况下,第二nmos器件nm2的电流能力是第一nmos器件nm1的电流能力的2倍。

44.由于w

pm1

/l

pm1

=w

pm2

/l

pm2

,w

nm2

/l

nm2

=2*w

nm1

/l

nm1

,当器件导通时,i

pm1

=i

pm2

,i

nm2

=2i

nm1

,w

pm1

/l

pm1

为第一pmos器件pm1的宽长比,w

pm2

/l

pm2

为第二pmos器件pm2的宽长比,w

nm2

/l

nm2

为第二nmos器件nm2的宽长比,w

nm1

/l

nm1

为第一nmos器件nm1的宽长比,i

pm1

为流过第一pmos器件pm1的电流,i

pm2

为流过第二pmos器件pm2的电流,i

nm1

为流过第一nmos器件nm1的电流,i

nm2

为流过第二nmos器件nm2的电流。

45.结合图3对上电复位检测电路的工作原理进行说明,当供电端vdd的电压曲线如图3中曲线201所示,节点102的电压信号por_n的电压曲线如图3中的曲线211所示,节点105的上电复位检测信号por的电压曲线如图3中的曲线221所示。

46.供电端vdd的电源电压从零开始上升时,随着电源电压的增加,第四nmos器件nm4会最先产生电流,此电流会通过第三pmos器件pm3被镜像到第一pmos器件pm1和第二pmos器件pm2,但此时103与104路径处于关断状态,所以第一pmos器件pm1与第一nmos器件nm1、第二nmos器件nm2均处于截止状态,而第二pmos器件pm2处于导通状态,节点102的电压信号por_n上拉为高电平(如图3中的电压曲线211),经过反相模块108后由反相模块108对电压信号por_n进行一级反相处理得到上电复位检测信号por,此时,反相模块108的输出端的节点105的电压为低电平。

47.等供电端vdd的电压达到监测电压v

check

时,第一pmos器件pm1、第一nmos器件nm1、第二nmos器件nm2由截止状态转换为导通状态,因为,i

nm2

=2i

nm1

=2i

pm2

,i

nm2

为流过第二nmos器件nm2的电流,i

nm1

为流过第一nmos器件nm1的电流,i

pm2

为流过第二pmos器件pm2的电流,所以节点102的电压信号por_n(如图3中的电压曲线211)又会被第二nmos器件nm2下拉变成低电平,节点102的电压信号por_n经过反相模块108反相处理后所得到的上电复位检测信号por为高电平(如图3中的电压曲线221),从而完成对供电端vdd所接入的电源的电压检测。

48.在一个实施例中,反相模块108为施密特反相器。

49.在本实施例中,反相模块108可以为标准的施密特反相器,可以用于对输入的信号进行信号整形,达到防止误触发的目的。

50.本技术实施例还提供了一种集成电路,包括如上述任一项所述的上电复位检测电路。

51.本技术实施例中的集成电路所采用的上电复位检测电路的结构很简单,只用几只mos器件就可以完成电压检测功能,也省掉了很大面积的分压电阻。与此同时,本技术实施例中所采用的电路结构依靠自身的结构特性兼具温度补偿的特性,而传统结构的方案还需要额外的带隙基准电压源(bandgap)提供一个零温度系数的参考电压vref来完成温度的补偿。相对而言,本技术实施例中所采用的电路结构在极低功耗应用的芯片中,不但节省了很大面积的电阻,而且还节省了一个bandgap所带来的成本开销,使得芯片的电路规模和复杂度大大降低。

52.本技术实施例还提供了一种芯片,包括如上述任一项所述的上电复位检测电路。

53.在本实施例中,采用上述实施例中的上电复位检测电路,可以很容易实现功耗小于100na的上电复位检测系统,该上电复位检测电路所需要的芯片面积很小几乎可以忽略,具有温度补偿的效果,最终的检测精度可以做到

±

100mv左右,非常适合应用在一些低功耗的芯片中(比如可穿戴领域中的低功耗芯片)。

54.本技术实施例的有益效果:由镜像电流模块根据供电端提供的电源生成多路镜像电流,第四nmos器件的漏极接收第一路镜像电流,第三nmos器件的漏极和第三nmos器件的栅极共接接收第二路镜像电流,第一nmos器件的漏极、第一nmos器件的栅极、第二nmos器件的栅极以及第三nmos器件的源极共接,第二nmos器件的漏极、反相模块的输入端共接并接入第三路镜像电流,第四nmos器件的栅极、第四nmos器件、第一nmos器件以及第二nmos器件的源极共接于地,反相模块对输入电压进行反相处理后输出上电复位检测信号,从而无需分压电路即可实现芯片的上电复位检测。

55.所属领域的技术人员可以清楚地了解到,为了描述的方便和简洁,仅以上述各功能单元、模块的划分进行举例说明,实际应用中,可以根据需要而将上述功能分配由不同的功能单元、模块完成,即将所述装置的内部结构划分成不同的功能单元或模块,以完成以上描述的全部或者部分功能。实施例中的各功能单元、模块可以集成在一个处理单元中,也可以是各个单元单独物理存在,也可以两个或两个以上单元集成在一个单元中。

56.另外,各功能单元、模块的具体名称也只是为了便于相互区分,并不用于限制本技术的保护范围。上述系统中单元、模块的具体工作过程,可以参考前述方法实施例中的对应过程,在此不再赘述。

57.在上述实施例中,对各个实施例的描述都各有侧重,某个实施例中没有详述或记载的部分,可以参见其它实施例的相关描述。

58.另外,在本技术各个实施例中的各功能单元可以集成在一个处理单元中,也可以是各个单元单独物理存在,也可以两个或两个以上单元集成在一个单元中。

59.以上所述实施例仅用以说明本技术的技术方案,而非对其限制;尽管参照前述实施例对本技术进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分技术特征进行等同替换;而这些修改

或者替换,并不使相应技术方案的本质脱离本技术各实施例技术方案的精神和范围,均应包含在本技术的保护范围之内。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。