1.本发明涉及一种包含多个高通滤波器的带通滤波器。

背景技术:

2.作为通信装置中使用的电子部件之一,存在带通滤波器。带通滤波器例如能够通过将高通滤波器和低通滤波器串联连接而构成,其中,该高通滤波器在带通滤波器的通带的低频侧形成衰减极点(attenuationpole),该低通滤波器在带通滤波器的通带的高频侧形成衰减极点。

3.中国专利申请公开第111164890a号说明书公开了一种将高通滤波器和低通滤波器串联连接得到的带通滤波器。高通滤波器和低通滤波器各自包含电感器。

4.近年来,市场要求小型移动通信设备的小型化、省空间化,还要求该通信设备中使用的带通滤波器的小型化。作为适于小型化的带通滤波器,已知一种使用包含层叠的多个电介质层和多个导体层的层叠体构成的带通滤波器。

5.在高通滤波器和低通滤波器一体构成于层叠体的情况下,如果层叠体小型化,则在高通滤波器的电感器与低通滤波器的电感器之间产生的非预期的磁耦合有时会过强。由此导致有时无法实现期望的特性。对此,中国专利申请公开第111164890a号说明书公开了一种技术,通过使两个电感器各自的磁通方向正交,来使两个电感器彼此不会发生磁耦合。

6.带通滤波器要求在阻带下具有足够大的通过衰减量。作为增大靠通带低频侧的阻带中的通过衰减量的方法,可以考虑设置多个高通滤波器。另外,在小型的带通滤波器中,为了防止多个高通滤波器的多个电感器彼此发生磁耦合,可以考虑使多个电感器各自的磁通的方向彼此不同。但是,实际上制造产品时,有时无法充分地增大阻带中的通过衰减量。

技术实现要素:

7.本发明的目的在于,提供一种在通带的低频侧能够增大通过衰减量的带通滤波器。

8.本发明的带通滤波器是使规定的通带内的频率的信号选择性地通过的带通滤波器。本发明的带通滤波器包括:第一端口;第二端口;在电路结构上,在第一端口与第二端口之间从第一端口一侧起依次设置的第一高通滤波器、第二高通滤波器和第三高通滤波器;和在电路结构上被设置于第二高通滤波器与第三高通滤波器之间的第一低通滤波器。第一至第三高通滤波器各自在通带的低频侧形成衰减极点。由第二高通滤波器形成的衰减极点的频率比由第一和第三高通滤波器各自形成的衰减极点的频率高。

9.在本发明的带通滤波器中,在电路结构上,在第一高通滤波器与第二高通滤波器之间可以没有设置低通滤波器。

10.另外,在本发明的带通滤波器中,由第一高通滤波器形成的衰减极点的频率与由第三高通滤波器形成的衰减极点的频率可以彼此不同。

11.另外,在本发明的带通滤波器中,可以还包括层叠体,层叠体包含层叠的多个电介

质层。第一端口、第二端口、第一高通滤波器、第二高通滤波器、第三高通滤波器以及第一低通滤波器可以与层叠体构成为一体。该情况下,第三高通滤波器可以在层叠体内与不第一高通滤波器相邻。另外,第二高通滤波器可以在层叠体内被配置于第一高通滤波器与第三高通滤波器之间。另外,第一低通滤波器可以在层叠体内被配置于第一高通滤波器与第三高通滤波器之间。

12.另外,在本发明的带通滤波器包括层叠体的情况下,第一高通滤波器至第三高通滤波器可以在层叠体内不物理上共地。该情况下,本发明的带通滤波器可以还包括被配置于层叠体的外表面的第一接地端子、第二接地端子和第三接地端子。第一高通滤波器可以与第一接地端子电连接。第二高通滤波器可以与第二接地端子电连接。第三高通滤波器可以与第三接地端子电连接。另外,该情况下,第一高通滤波器可以包含第一电感器。第二高通滤波器可以包含第二电感器。第三高通滤波器可以包含第三电感器。第一至第三电感器可以在层叠体内不彼此电连接。

13.另外,在本发明的带通滤波器包括层叠体的情况下,第一高通滤波器可以包含绕第一轴线卷绕的第一电感器。第二高通滤波器可以包含绕第二轴线卷绕的第二电感器。第三高通滤波器可以包含绕第三轴线卷绕的第三电感器。第一轴线和第二轴线可以在彼此不同的方向上延伸。第二轴线和第三轴线可以在彼此不同的方向上延伸。第一轴线、第二轴线和第三轴线各自可以与多个电介质层的层叠方向正交。第一低通滤波器可以包含绕第四轴线卷绕的第四电感器,第四轴线可以在与第一轴线、第二轴线和第三轴线中的一个或两个轴线不同的方向上延伸。

14.本发明的带通滤波器包括在电路结构上在第一端口与第二端口之间从第一端口一侧起依次设置的第一高通滤波器、第二高通滤波器和第三高通滤波器。由第二高通滤波器形成的衰减极点的频率比由第一和第三高通滤波器各自形成的衰减极点的频率高。由此,根据本发明,在通带的低频侧能够增大通过衰减量。

15.本发明的其他目的、特征和益处将通过以下的说明变得足够清楚。

附图说明

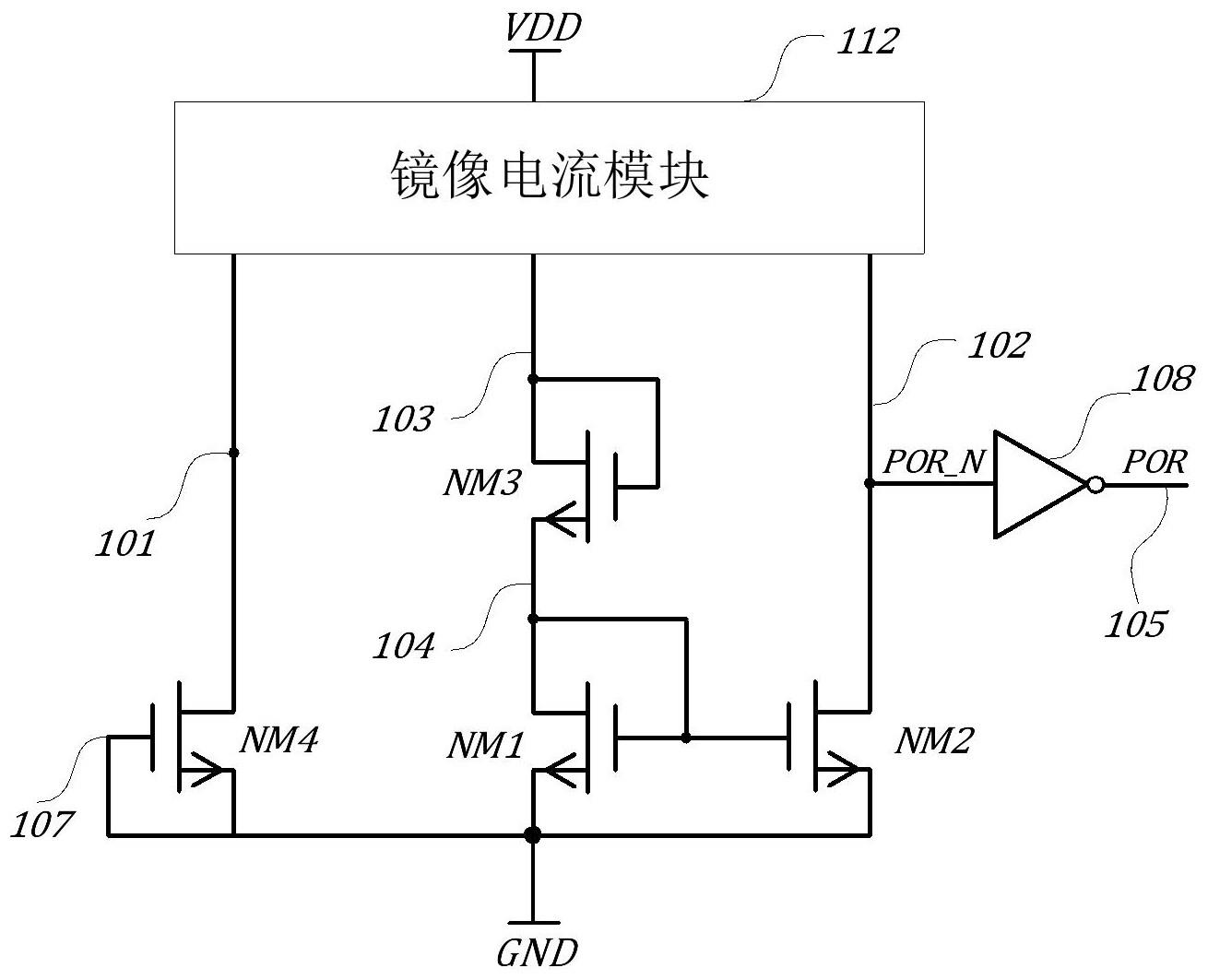

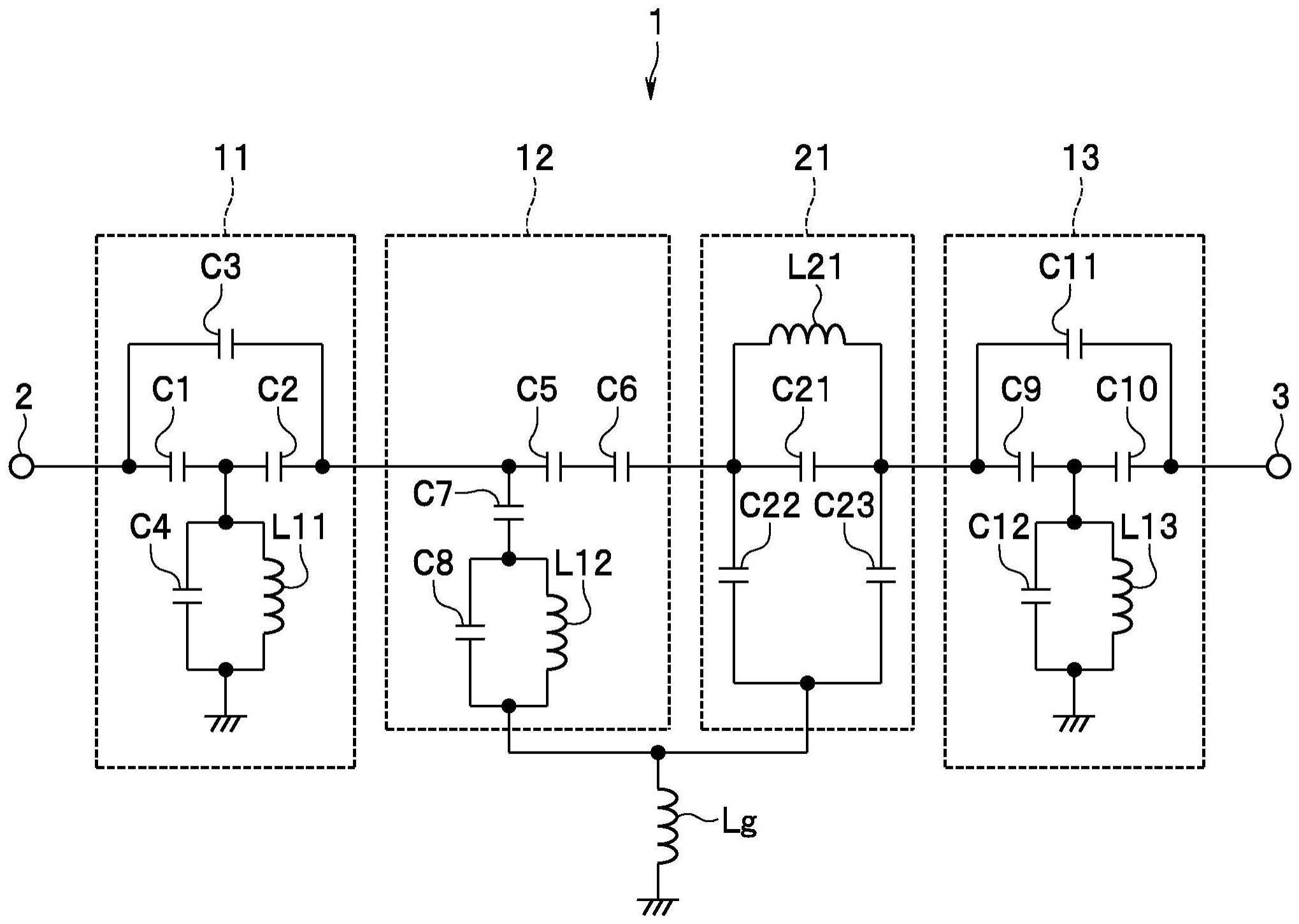

16.图1是表示本发明一实施方式的带通滤波器的电路结构的电路图。

17.图2是表示本发明一实施方式的带通滤波器的外观的立体图。

18.图3a至图3c是表示本发明一实施方式的带通滤波器的层叠体中的第一层至第三层电介质层的图案形成面的说明图。

19.图4a至图4c是表示本发明一实施方式的带通滤波器的层叠体中的第四层至第六层电介质层的图案形成面的说明图。

20.图5a至图5c是表示本发明一实施方式的带通滤波器的层叠体中的第七层至第九层电介质层的图案形成面的说明图。

21.图6a是表示本发明一实施方式的带通滤波器的层叠体中的第十层至第十八层电介质层的图案形成面的说明图。

22.图6b是表示本发明一实施方式的带通滤波器的层叠体中的第十九层电介质层的图案形成面的说明图。

23.图6c是表示本发明一实施方式的带通滤波器的层叠体中的第二十层电介质层的

图案形成面的说明图。

24.图7a和图7b是表示本发明一实施方式的带通滤波器的层叠体中的第二十一层和第二十二层电介质层的图案形成面的说明图。

25.图8是表示本发明一实施方式的带通滤波器的层叠体的内部的立体图。

26.图9是表示本发明一实施方式的带通滤波器的层叠体的内部的平面图。

27.图10是表示本发明一实施方式的带通滤波器的通过衰减特性之一例的特性图。

28.图11是表示第一实施例的模型的通过衰减特性的特性图。

29.图12是表示第二实施例的模型的通过衰减特性的特性图。

30.图13是表示比较例的模型的通过衰减特性的特性图。

31.图14是表示变形例的模型的通过衰减特性的特性图。

具体实施方式

32.以下,参照附图对本发明的实施方式进行详细说明。首先,参照图1对本发明一实施方式的带通滤波器1的结构的概略进行说明。本实施方式的带通滤波器1使规定的通带内的频率的信号选择性地通过。

33.带通滤波器1具备第一端口2、第二端口3、第一高通滤波器11、第二高通滤波器12、第三高通滤波器13和低通滤波器21。第一和第二端口2、3各自是用于输入或输出信号的端口。即,在信号输入到第一端口2的情况下,从第二端口3输出信号。在信号输入到第二端口3的情况下,从第一端口2输出信号。

34.第一至第三高通滤波器11、12、13在电路结构上,在第一端口2与第二端口3之间从第一端口2一侧起依次设置。低通滤波器21设置于第二高通滤波器12与第三高通滤波器13之间。在带通滤波器1中,在电路结构上,在第一高通滤波器11与第二高通滤波器12之间没有设置低通滤波器。此外,在本技术中,“电路结构上”这样的表述指其不是物理结构上的配置而是电路图上的配置。

35.第一至第三高通滤波器11~13各自在带通滤波器1的通过衰减特性中,在带通滤波器1的通带的低频侧形成衰减极点。由第二高通滤波器12形成的衰减极点的频率比由第一和第三高通滤波器11、13各自形成的衰减极点的频率高。另外,由第一高通滤波器11形成的衰减极点的频率与由第三高通滤波器13形成的衰减极点的频率彼此不同。

36.低通滤波器21在带通滤波器1的通过衰减特性中在带通滤波器1的通带的高频侧形成衰减极点。

37.关于带通滤波器1的通过衰减特性和由第一至第三高通滤波器11~13各自形成的衰减极点,将在后文进行详细说明。

38.接着,参照图1对第一高通滤波器11、第二高通滤波器12、第三高通滤波器13以及低通滤波器21的结构之一例进行说明。

39.第一高通滤波器11包含第一电感器l11和电容器c1、c2、c3、c4。电容器c1的一端与第一端口2连接。电容器c2的一端与电容器c1的另一端连接。电容器c3的一端与电容器c1的一端连接。电容器c3的另一端与电容器c2的另一端连接。

40.第一电感器l11的一端被连接在电容器c1与电容器c2的连接点上。第一电感器l11的另一端接地。电容器c4与第一电感器l11并联连接。

41.第二高通滤波器12包含第二电感器l12和电容器c5、c6、c7、c8。电容器c5的一端与第一高通滤波器11的电容器c2的另一端连接。电容器c6的一端与电容器c5的另一端连接。

42.电容器c7的一端被连接在电容器c2与电容器c5的连接点上。第二电感器l12的一端与电容器c7的另一端连接。第二电感器l12的另一端接地。电容器c8与第二电感器l12并联连接。

43.低通滤波器21包含第四电感器l21和电容器c21、c22、c23。电容器c21的一端与第二高通滤波器12的电容器c6的另一端连接。第四电感器l21与电容器c21并联连接。

44.电容器c22的一端与电容器c21的一端连接。电容器c23的一端与电容器c21的另一端连接。电容器c22、c23各自的另一端接地。

45.图1中,lg表示将第二电感器l12和电容器c22、c23分别与大地(gnd)连接的路径的电感成分。

46.第三高通滤波器13包含第三电感器l13和电容器c9、c10、c11、c12。电容器c9的一端与低通滤波器21的电容器c21的另一端连接。电容器c10的一端与电容器c9的另一端连接。电容器c10的另一端与第二端口3连接。电容器c11的一端与电容器c9的一端连接。电容器c11的另一端与电容器c10的另一端连接。

47.第三电感器l13的一端被连接在电容器c9与电容器c10的连接点上。第三电感器l13的另一端接地。电容器c12与第三电感器l13并联连接。

48.接着,参照图2对带通滤波器1的其他结构进行说明。图2是表示带通滤波器1的外观的立体图。

49.带通滤波器1还具备包含层叠的多个电介质层和多个导体层的层叠体50。第一端口2、第二端口3、第一至第三高通滤波器11~13以及低通滤波器21与层叠体50构成为一体。

50.层叠体50具有位于多个电介质层的层叠方向t的两端的底面50a和顶面50b,以及将底面50a与顶面50b连接的四个侧面50c~50f。侧面50c、50d彼此朝向相反侧,侧面50e、50f也彼此朝向相反侧。侧面50c~50f相对于顶面50b和底面50a垂直。

51.在此,如图2所示地定义x方向、y方向、z方向。x方向、y方向、z方向彼此正交。在本实施方式中,将与层叠方向t平行的一个方向设为z方向。另外,将与x方向相反的方向设为-x方向,将与y方向相反的方向设为-y方向,将与z方向相反的方向设为-z方向。

52.如图2所示,底面50a位于层叠体50中的-z方向的端部。顶面50b位于层叠体50中的z方向的端部。底面50a和顶面50b各自的形状为在x方向上较长的矩形形状。侧面50c位于层叠体50中的-x方向的端部。侧面50d位于层叠体50中的x方向的端部。侧面50e位于层叠体50中的-y方向的端部。侧面50f位于层叠体50中的y方向的端部。

53.带通滤波器1还具备设置于层叠体50的底面50a的端子111、112、113、114、115、116。端子111、112、113在离侧面50e比离侧面50f近的位置在x方向上依次排列。端子114、115、116在离侧面50f比离侧面50e近的位置在-x方向上依次排列。

54.端子116对应于第一端口2,端子114对应于第二端口3。因此,第一和第二端口2、3设置于层叠体50的底面50a。端子111~113、115各自接地。端子111对应于本发明中的“第一接地端子”。端子112、115对应于本发明中的“第二接地端子”。端子113对应于本发明中的“第三接地端子”。端子111~113、115配置于层叠体50的外表面。

55.接着,参照图3a至图7b对构成层叠体50的多个电介质层和多个导体层之一例进行

说明。在该例中,层叠体50具有层叠的二十二层电介质层。以下,将该二十二层电介质层从下到上依次称为第一层至第二十二层电介质层。另外,用附图标记51~72表示第一层至第二十二层电介质层。

56.图3a至图6c中,多个圆表示多个通孔(全通导孔)。在电介质层51~70的每一个形成有多个通孔。多个通孔分别通过在通孔用的孔内填充导体膏而形成。多个通孔各自与端子、导体层或其他通孔连接。

57.图3a表示第一层电介质层51的图案形成面。在电介质层51的图案形成面上形成有端子111~116。另外,图3a中,用附图标记51t1表示与端子111连接的特定的通孔,用附图标记51t9表示与端子112连接的2个特定的通孔,用附图标记51t5表示与端子113连接的特定的通孔,用附图标记51t3表示与端子115连接的2个特定的通孔。

58.图3b表示第二层电介质层52的图案形成面。在电介质层52的图案形成面上形成有导体层521、522、523、524。导体层521具有彼此位于相反侧的第一端和第二端。形成于电介质层51的特定的通孔51t1与导体层521的第一端的附近部分连接。形成于电介质层51的2个特定的通孔51t3与导体层524连接。形成于电介质层51的特定的通孔51t5与导体层522连接。

59.另外,图3b中,用附图标记52t1表示与导体层521的第二端的附近部分连接的特定的通孔,用附图标记52t5表示与导体层522连接的特定的通孔。另外,用附图标记52t9表示与形成于电介质层51的2个特定的通孔51t9连接的2个特定的通孔。

60.图3c表示第三层电介质层53的图案形成面。在电介质层53的图案形成面上形成有导体层531、532。形成于电介质层52的特定的通孔52t3、52t9与导体层532连接。

61.另外,图3c中,分别用附图标记53t1、53t5表示与形成于电介质层52的特定的通孔52t1、52t5连接的2个特定的通孔。另外,用附图标记53t3表示与导体层532连接的特定的通孔。

62.图4a表示第四层电介质层54的图案形成面。在电介质层54的图案形成面上形成有导体层541、542、543、544、545。另外,图4a中,分别用附图标记54t1、54t3、54t5表示与形成于电介质层53的特定的通孔53t1、53t3、53t5连接的三个特定的通孔。

63.图4b表示第五层电介质层55的图案形成面。在电介质层55的图案形成面上形成有导体层551、552。另外,图4b中,分别用附图标记55t1、55t3、55t5表示与形成于电介质层54的特定的通孔54t1、54t3、54t5连接的三个特定的通孔。另外,用附图标记55t7表示与导体层552连接的特定的通孔。

64.图4c表示第六层电介质层56的图案形成面。在电介质层56的图案形成面上形成有导体层561、562、563。另外,图4c中,分别用附图标记56t1、56t3、56t5、56t7表示与形成于电介质层55的特定的通孔55t1、55t3、55t5、55t7连接的四个特定的通孔。另外,分别用附图标记56t2、56t8表示与导体层561、563连接的2个特定的通孔。

65.图5a表示第七层电介质层57的图案形成面。在电介质层57的图案形成面上形成有导体层571、572、573、574、575。形成于电介质层56的通孔56t3、56t5分别与导体层573、575连接。

66.另外,图5a中,分别用附图标记57t1、57t2、57t7、57t8表示与形成于电介质层56的特定的通孔56t1、56t2、56t7、56t8连接的四个特定的通孔。另外,用附图标记57t3表示与导

体层573连接的2个特定的通孔,用附图标记57t4表示与导体层574连接的2个特定的通孔,用附图标记57t5表示与导体层575连接的2个特定的通孔,用附图标记57t6表示与导体层572连接的2个特定的通孔。

67.图5b表示第八层电介质层58的图案形成面。在电介质层58上形成有特定的通孔58t1、58t2、58t3、58t4、58t5、58t6、58t7、58t8。形成于电介质层57的特定的通孔57t1~57t8分别与特定的通孔58t1~58t8连接。

68.图5c表示第九层电介质层59的图案形成面。在电介质层59的图案形成面上形成有导体层591。另外,在电介质层59上形成有特定的通孔59t1、59t2、59t3、59t4、59t5、59t6、59t7、59t8。形成于电介质层58的特定的通孔58t1~58t8分别与特定的通孔59t1~59t8连接。

69.图6a表示第十层至第十八层电介质层60~68各自的图案形成面。在电介质层60~68的每一个形成有特定的通孔60t1、60t2、60t3、60t4、60t5、60t6、60t7、60t8。形成于电介质层59的特定的通孔59t1~59t8分别与形成于电介质层60的特定的通孔60t1~60t8连接。另外,在电介质层60~68中,上下相邻的相同附图标记的通孔彼此相互连接。

70.图6b表示第十九层电介质层69的图案形成面。在电介质层69上形成有特定的通孔69t1、69t2、69t3、69t4、69t5、69t6、69t7、69t8。形成于电介质层68的特定的通孔60t1~60t8分别与特定的通孔69t1~69t8连接。

71.图6c表示第二十层电介质层70的图案形成面。在电介质层70的图案形成面上形成有电感器用导体层701、702、703、704。导体层701~704各自具有彼此位于相反侧的第一端和第二端。形成于电介质层69的特定的通孔69t1与导体层701的第一端的附近部分连接。形成于电介质层69的特定的通孔69t2与导体层701的第二端的附近部分连接。形成于电介质层69的2个特定的通孔69t3与导体层702的第一端的附近部分连接。形成于电介质层69的2个特定的通孔69t4与导体层702的第二端的附近部分连接。形成于电介质层69的2个特定的通孔69t5与导体层703的第一端的附近部分连接。形成于电介质层69的2个特定的通孔69t6与导体层703的第二端的附近部分连接。形成于电介质层69的特定的通孔69t7与导体层704的第一端的附近部分连接。形成于电介质层69的特定的通孔69t8与导体层704的第二端的附近部分连接。

72.另外,图6c中,用附图标记70t1表示与导体层701的第一端的附近部分连接的特定的通孔,用附图标记70t2表示与导体层701的第二端的附近部分连接的特定的通孔,用附图标记70t3表示与导体层702的第一端的附近部分连接的2个特定的通孔,用附图标记70t4表示与导体层702的第二端的附近部分连接的2个特定的通孔,用附图标记70t5表示与导体层703的第一端的附近部分连接的2个特定的通孔,用附图标记70t6表示与导体层703的第二端的附近部分连接的2个特定的通孔,用附图标记70t7表示与导体层704的第一端的附近部分连接的特定的通孔,用附图标记70t8表示与导体层704的第二端的附近部分连接的2个特定的通孔。

73.图7a表示第二十一层电介质层71的图案形成面。在电介质层71的图案形成面上形成有电感器用导体层711、712、713、714。导体层711~714各自具有彼此位于相反侧的第一端和第二端。形成于电介质层70的特定的通孔70t1与导体层711的第一端的附近部分连接。形成于电介质层70的特定的通孔70t2与导体层711的第二端的附近部分连接。形成于电介

质层70的2个特定的通孔70t3与导体层712的第一端的附近部分连接。形成于电介质层70的2个特定的通孔70t4与导体层712的第二端的附近部分连接。形成于电介质层70的2个特定的通孔70t5与导体层713的第一端的附近部分连接。形成于电介质层70的2个特定的通孔70t6与导体层713的第二端的附近部分连接。形成于电介质层70的特定的通孔70t7与导体层714的第一端的附近部分连接。形成于电介质层70的特定的通孔70t8与导体层714的第二端的附近部分连接。

74.图7b表示第二十二层电介质层72的图案形成面。在电介质层72的图案形成面上形成有由导体层构成的标记721。

75.图2所示的层叠体50以第一层电介质层51的图案形成面成为层叠体50的底面50a、第二十二层电介质层72的与图案形成面相反的一侧的面成为层叠体50的顶面50b的方式,由第一层至第二十二层电介质层51~72层叠而构成。

76.标注了附图标记的多个特定的通孔以外的图3a至图4c所示的多个通孔的每一个,在将第一层至第二十二层电介质层51~72层叠时,与在层叠方向t上重叠的导体层或在层叠方向t上重叠的其他通孔连接。另外,在多个特定的通孔以外的图3a至图4c所示的多个通孔之中,位于端子内或导体层内的通孔与该端子或该导体层连接。

77.图8表示由第一层至第二十二层电介质层51~72层叠而构成的层叠体50的内部。如图8所示,在层叠体50的内部,层叠有图3a至图7a所示的多个导体层和多个通孔。此外,图8中省略了标记721。

78.以下,对图1所示的带通滤波器1的电路的构成要素与图3a至图7a所示的层叠体50的内部的构成要素的对应关系进行说明。首先,对第一高通滤波器11的构成要素进行说明。第一电感器l11由电感器用导体层701、711和特定的通孔52t1、53t1、54t1、55t1、56t1、56t2、57t1、57t2、58t1、58t2、59t1、59t2、60t1、60t2、69t1、69t2、70t1、70t2构成。

79.电容器c1由导体层561、571和这些导体层之间的电介质层56构成。电容器c2由导体层551、561和这些导体层之间的电介质层55构成。电容器c3由导体层541、551和这些导体层之间的电介质层54构成。电容器c4由导体层521、561和这些导体层之间的电介质层52~55构成。

80.接着,对第二高通滤波器12的构成要素进行说明。第二电感器l12由电感器用导体层702、712和特定的通孔57t3、57t4、58t3、58t4、59t3、59t4、60t3、60t4、69t3、69t4、70t3、70t4构成。

81.电容器c5由导体层551、591和这些导体层之间的电介质层55~58构成。电容器c6由导体层552、591和这些导体层之间的电介质层55~58构成。电容器c7由导体层542、551、562和这些导体层之间的电介质层54、55构成。电容器c8由导体层532、542和这些导体层之间的电介质层53构成。

82.接着,对第三高通滤波器13的构成要素进行说明。第三电感器l13由电感器用导体层703、713和特定的通孔57t5、57t6、58t5、58t6、59t5、59t6、60t5、60t6、69t5、69t6、70t5、70t6构成。

83.电容器c9由导体层563、572和这些导体层之间的电介质层56构成。电容器c10由导体层531、543和这些导体层之间的电介质层53构成。电容器c11由导体层543、563和这些导体层之间的电介质层54、55构成。电容器c12由导体层522、531和这些导体层之间的电介质

层52构成。

84.接着,对低通滤波器21的构成要素进行说明。第四电感器l21由电感器用导体层704、714和特定的通孔55t7、56t7、56t8、57t7、57t8、58t7、58t8、59t7、59t8、60t7、60t8、69t7、69t8、70t7、70t8构成。

85.电容器c21由导体层545、552和这些导体层之间的电介质层54构成。电容器c22由导体层532、544和这些导体层之间的电介质层53构成。电容器c23由导体层523、532、545和这些导体层之间的电介质层52、53构成。

86.图1所示的电感成分lg包含导体层524和特定的通孔51t3、51t9、52t3、52t9各自的电感成分。

87.接着,参照图1至图9对本实施方式的带通滤波器1的结构上的特征进行说明。图9是表示层叠体50的内部的平面图。

88.首先,对关于第一至第三高通滤波器11~13以及低通滤波器21的配置的特征进行说明。如图9所示,第三高通滤波器13在层叠体50内不与第一高通滤波器11相邻。在本实施方式中,第一高通滤波器11被配置在离侧面50c比离侧面50d近的位置。第三高通滤波器13被配置在离侧面50d比离侧面50c近的位置。

89.第二高通滤波器12在层叠体50内被配置于第一高通滤波器11与第三高通滤波器13之间。另外,低通滤波器21在层叠体50内被配置于第一高通滤波器11与第三高通滤波器13之间。在本实施方式中,第二高通滤波器12在离侧面50f比离侧面50e近的位置,被配置于第一高通滤波器11与第三高通滤波器13之间。低通滤波器21在离侧面50e比离侧面50f近的位置,被配置于第一高通滤波器11与第三高通滤波器13之间。

90.接着,对第一至第四电感器l11~l13、l21的结构上的特征进行说明。在此,将通过串联连接2个以上的通孔而构成的构造物称为通孔列。层叠体50包含通孔列t1、t2、t3、t4、t5、t6、t7、t8。通孔列t1由特定的通孔52t1、53t1、54t1、55t1、56t1、57t1、58t1、59t1、60t1、69t1构成。通孔列t2由特定的通孔56t2、57t2、58t2、59t2、60t2、69t2构成。

91.2个通孔列t3由特定的通孔57t3、58t3、59t3、60t3、69t3构成。2个通孔列t4由特定的通孔57t4、58t4、59t4、60t4、69t4构成。2个通孔列t5由特定的通孔57t5、58t5、59t5、60t5、69t5构成。2个通孔列t6由特定的通孔57t6、58t6、59t6、60t6、69t6构成。

92.通孔列t7由特定的通孔55t7、56t7、57t7、58t7、59t7、60t7、69t7构成。通孔列t8由特定的通孔56t8、57t8、58t8、59t8、60t8、69t8构成。

93.第一电感器l11包含电感器用导体层701、711、通孔列t1、t2以及特定的通孔70t1、70t2。通孔列t1与电感器用导体层701的第一端的附近部分连接。通孔列t2与电感器用导体层701的第二端的附近部分连接。

94.第二电感器l12包含电感器用导体层702、712、2个通孔列t3、2个通孔列t4以及特定的通孔70t3、70t4。2个通孔列t3在电感器用导体层702的第一端的附近部分并联连接。2个通孔列t4在电感器用导体层702的第二端的附近部分并联连接。

95.第三电感器l13包含电感器用导体层703、713、2个通孔列t5、2个通孔列t6以及特定的通孔70t5、70t6。2个通孔列t5在电感器用导体层703的第一端的附近部分并联连接。2个通孔列t6在电感器用导体层703的第二端的附近部分并联连接。

96.第四电感器l21包含电感器用导体层704、714、通孔列t7、t8以及特定的通孔70t7、

70t8。通孔列t7与电感器用导体层704的第一端的附近部分连接。通孔列t8与电感器用导体层704的第二端的附近部分连接。

97.第一电感器l11绕第一轴线a1卷绕。第二电感器l12绕第二轴线a2卷绕。第三电感器l13绕第三轴线a3卷绕。第四电感器l21绕第四轴线a4卷绕。

98.第一轴线a1和第二轴线a2在彼此不同的方向上延伸。在图9所示的例子中,第一轴线a1在与x方向平行的方向上延伸,第二轴线a2在与y方向平行的方向上延伸。此外,只要满足第一轴线a1和第二轴线a2在彼此不同的方向上延伸这一条件,则第一和第二轴线a1、a2的至少一个也可以在相对于x方向和y方向分别倾斜的方向上延伸。

99.第二轴线a2和第三轴线a3在彼此不同的方向上延伸。在图9所示的例子中,第三轴线a3在与x方向平行的方向上延伸。此外,只要满足第二轴线a2和第三轴线a3在彼此不同的方向上延伸这一条件,则第二和第三轴线a2、a3的至少一个也可以在相对于x方向和y方向分别倾斜的方向上延伸。

100.第四轴线a4在与第一至第三轴线a1~a3中的一个或两个不同的方向上延伸。在图8和图9所示的例子中,第四轴线a4在与y方向平行的方向上延伸。因此,第四轴线a4在相对于第二轴线a2平行、但与第一和第三轴线a1、a3不同的方向上延伸。

101.此外,在图8和图9所示的例子中,第一轴线a1和第三轴线a3均在与x方向平行的方向上延伸。但是,第一轴线a1和第三轴线a3也可以在彼此不同的方向上延伸。另外,在图8和图9所示的例子中,第二轴线a2和第四轴线a4均在与y方向平行的方向上延伸。但是,第二轴线a2和第四轴线a4也可以在彼此不同的方向上延伸。

102.另外,在图8和图9所示的例子中,第一至第四轴线a1~a4均与层叠方向t正交。此外,第一至第四轴线a1~a4中的至少一个也可以与层叠方向t平行。

103.接着,对关于第一至第三高通滤波器11~13与大地的连接的特征进行说明。第一高通滤波器11与端子111电连接。即,第一电感器l11的通孔列t1与构成电容器c4的导体层521连接。导体层521经由特定的通孔51t1与端子111连接。

104.第二高通滤波器12与端子112、115电连接。即,第二电感器l12的2个通孔列t3经由导体层573以及特定的通孔53t3、54t3、55t3、56t3与构成电容器c8的导体层532连接。导体层532经由特定的通孔51t9、52t9与端子112连接,并且经由2个特定的通孔51t3、导体层524以及2个特定的通孔52t3与端子115连接。

105.第三高通滤波器13与端子113电连接。即,第三电感器l13的2个通孔列t5经由导体层575以及特定的通孔52t5、53t5、54t5、55t5、56t5与构成电容器c12的导体层522连接。导体层522经由特定的通孔51t5与端子113连接。

106.与大地连接的端子111~113、115在层叠体50的底面50a上彼此隔开间隔。并且,端子111~113、115在层叠体50内不彼此电连接。因此,第一至第三高通滤波器11~13在层叠体50内不物理上共地(共用大地)。

107.此外,在本实施方式中,第二高通滤波器12和低通滤波器21均与端子111、115电连接。导体层532除了构成第二高通滤波器12的电容器c8外,还构成低通滤波器21的电容器c22、c23。如前述,导体层532与端子111、115连接。

108.另外,在本实施方式中,如上所述,第一至第三电感器l11~l13各自的大地侧的端部与彼此不同的端子电连接,并且在层叠体50内不彼此电连接。另外,如图1所示,在第一至

第三电感器l11~l13中的一个电感器的与大地相反的一侧的端部,和第一至第三电感器l11~l13中的另一个电感器的与大地相反的一侧的端部之间,存在多个电容器。因此,第一至第三电感器l11~l13各自的与大地相反的一侧的端部在层叠体50内不彼此电连接。由此,第一至第三电感器l11~l13在层叠体50内不彼此电连接。

109.接着,参照图10对带通滤波器1的特性之一例进行说明。图10是表示带通滤波器1的通过衰减特性之一例的特性图。图10中,横轴表示频率,纵轴表示衰减量。

110.如图10所示,关于带通滤波器1,在带通滤波器1的通过衰减特性中,在带通滤波器1的通带的低频侧形成有三个衰减极点81、82、83。衰减极点81是由第一高通滤波器11形成的衰减极点。衰减极点82是由第二高通滤波器12形成的衰减极点。衰减极点83是由第三高通滤波器13形成的衰减极点。如图10所示,衰减极点82形成于通带的附近,衰减极点81、83形成于比衰减极点82更靠低频侧的频段。即,衰减极点82的频率比衰减极点81、83各自的频率高。

111.另外,在图10所示的例子中,衰减极点81的频率与衰减极点83的频率彼此不同。在图10所示的例子中,特别是,衰减极点83的频率比衰减极点81的频率高。

112.接着,对本实施方式的带通滤波器1的作用和效果进行说明。在本实施方式中,第一高通滤波器11形成衰减极点81,第二高通滤波器12形成衰减极点82,第三高通滤波器13形成衰减极点83。

113.在此,关注带通滤波器中在物理上相邻的2个谐振电路。通常,如果带通滤波器小型化,则2个谐振电路的间隔变小,因此2个谐振电路容易彼此发生磁耦合。在这2个谐振电路在带通滤波器的通过衰减特性中形成相邻的2个衰减极点的情况下,如果2个谐振电路发生磁场耦合,则在带通滤波器的通过衰减特性中,2个衰减极点之间的通过衰减量会减小。

114.在本实施方式中,第二高通滤波器12在电路结构上被配置于第一高通滤波器11与第三高通滤波器13之间。因此,如果由第二高通滤波器12形成的衰减极点存在于由第一高通滤波器11形成的衰减极点与由第三高通滤波器13形成的衰减极点之间,且第二高通滤波器12与第一高通滤波器11和第三高通滤波器13的双方发生磁耦合,则在带通滤波器1的通过衰减特性中,由第一高通滤波器11形成的衰减极点与由第二高通滤波器12形成的衰减极点之间的通过衰减量、以及由第二高通滤波器12形成的衰减极点与由第三高通滤波器13形成的衰减极点之间的通过衰减量会减小。其结果是,在通带的低频侧的较宽的频率区域中,通过衰减量会减小。

115.对此,在本实施方式中,由第二高通滤波器12形成的衰减极点82不存在于由第一高通滤波器11形成的衰减极点81与由第三高通滤波器13形成的衰减极点83之间,衰减极点82的频率比衰减极点81、83各自的频率高。由此,根据本实施方式,能够抑制通过衰减量在通带的低频侧的较宽的频率区域中减小,其结果是,能够在通带的低频侧增大通过衰减量。

116.此外,衰减极点81的频率与衰减极点83的频率彼此不同。衰减极点83的频率可以比衰减极点81的频率高,也可以低。在衰减极点83的频率比衰减极点81的频率高的情况下,衰减极点82、83对应于前述的在带通滤波器的通过衰减特性中相邻的2个衰减极点。在本实施方式中,低通滤波器21在电路结构上被设置于第二高通滤波器12与第三高通滤波器13之间。由此,根据本实施方式,能够延长从第二高通滤波器12至第三高通滤波器13的路径,抑制或防止第二高通滤波器12与第三高通滤波器13之间的磁耦合。其结果是,根据本实施方

式,在带通滤波器1的通过衰减特性中,能够抑制衰减极点82与衰减极点83之间的通过衰减量减小。

117.另外,在本实施方式中,第三高通滤波器13在层叠体50内不与第一高通滤波器11相邻。由此,根据本实施方式,能够抑制或防止第一高通滤波器11与第三高通滤波器13之间的磁耦合。其结果是,根据本实施方式,在带通滤波器1的通过衰减特性中,能够抑制衰减极点81与衰减极点83之间的通过衰减量减小。

118.另外,在本实施方式中,第一至第三高通滤波器11~13在层叠体50内不物理上共地。由此,根据本实施方式,能够防止第一至第三高通滤波器11~13经由层叠体50内的大地而发生磁耦合。由此也同样地,根据本实施方式,在通带的低频侧能够抑制通过衰减量减小。

119.另外,在本实施方式中,第一至第三电感器l11~l13在层叠体50内不彼此电连接。由此,根据本实施方式,能够防止第一至第三电感器l11~l13经由层叠体50内的导体(导体层和通孔)而发生磁耦合。由此也同样地,根据本实施方式,在通带的低频侧能够抑制通过衰减量减小。

120.在此,将被电感器用导体层701和通孔列t1、t2包围的区域称为第一电感器l11的开口部。另外,将被电感器用导体层702和通孔列t3、t4包围的区域称为第二电感器l12的开口部。另外,将被电感器用导体层703和通孔列t5、t6包围的区域称为第三电感器l13的开口部。

121.在本实施方式中,第一电感器l11绕第一轴线a1卷绕,第二电感器l12绕第二轴线a2卷绕,第三电感器l13绕第三轴线a3卷绕。如前述,第一轴线a1和第二轴线a2在彼此不同的方向上延伸。由此,根据本实施方式,与第一轴线a1和第二轴线a2在相同方向上延伸且第一电感器l11的开口部和第二电感器l12的开口部彼此相对的情况相比,能够抑制第一电感器l11与第二电感器l12之间的磁耦合。同样,在本实施方式中,第二轴线a2和第三轴线a3在彼此不同的方向上延伸。由此,根据本实施方式,与第二轴线a2和第三轴线a3在相同的方向上延伸且第二电感器l12的开口部和第三电感器l13的开口部彼此相对的情况相比,能够抑制第二电感器l12与第三电感器l13之间的磁耦合。由此,根据本实施方式,在通带的低频侧能够抑制通过衰减量减小。

122.接着,通过模拟调查了由第一至第三高通滤波器11~13各自形成的衰减极点的频率对带通滤波器1的通过衰减特性带来的影响,对模拟的结果进行说明。在模拟中使用了第一实施例的模型、第二实施例的模型以及比较例的模型。第一实施例的模型和第二实施例的模型均是本实施方式的带通滤波器1的模型。比较例的模型是比较例的带通滤波器的模型。比较例的带通滤波器的电路结构与本实施方式的带通滤波器1的电路结构相同。

123.模拟中使用的模型均是组合了结构的模型和电路的模型而得到的模型。结构的模型是分别由两个电感器用导体层和多个通孔构成的第一至第四电感器l11~l13、l21(参照图8)的模型。电路的模型是分别由理想的电容器构成的电容器c1~c12、c21~c23的模型。

124.在以下的说明中,将由第一高通滤波器11形成的衰减极点称为第一衰减极点91,将由第二高通滤波器12形成的衰减极点称为第二衰减极点92,将由第三高通滤波器13形成的衰减极点称为第三衰减极点93。在第一实施例的模型中,以频率按照第一衰减极点91、第三衰减极点93和第二衰减极点92的顺序变高的方式设计了第一至第三高通滤波器11~13。

在第二实施例的模型中,以频率按照第三衰减极点93、第一衰减极点91和第二衰减极点92的顺序变高的方式设计了第一至第三高通滤波器11~13。在比较例的模型中,以频率按照第三衰减极点93、第二衰减极点92和第一衰减极点91的顺序变高的方式设计了第一至第三高通滤波器11~13。

125.第一和第二实施例的模型满足由第二高通滤波器12形成的衰减极点的频率比由第一和第三高通滤波器11、13各自形成的衰减极点的频率高这一本实施方式的带通滤波器1的条件。另一方面,比较例的模型不满足上述条件。

126.在模拟中,对第一实施例的模型、第二实施例的模型和比较例的模型分别调查了通过衰减特性。图11表示第一实施例的模型的通过衰减特性。图12表示第二实施例的模型的通过衰减特性。图13表示比较例的模型的通过衰减特性。图11至图13中,横轴表示频率,纵轴表示衰减量。在此,将图11至图13所示的衰减量的绝对值称为通过衰减量。根据图11至图13可以理解,第一和第二实施例的模型与比较例的模型相比,在通带的低频侧,通过衰减量增大。

127.另外,对于通过衰减量,要求其例如在4.5ghz以下的频率区域为60db以上。第一实施例的模型和第二实施例的模型满足上述的要求,但比较例的模型不满足上述的要求。

128.基于模拟的结果可以理解,根据本实施方式,通过满足前述的带通滤波器1的条件,能够在通带的低频侧增大通过衰减量。

129.[变形例]

[0130]

接着,对本实施方式的带通滤波器1的变形例进行说明。在变形例中,由第一高通滤波器11形成的衰减极点的频率与由第三高通滤波器13形成的衰减极点的频率实质上相同。

[0131]

在此,对变形例的模型的通过衰减特性进行说明。变形例的模型是本实施方式的带通滤波器1的变形例的模型,与前述的模拟相同,是组合了结构的模型和电路的模型而得到的模型。图14表示变形例的模型的通过衰减特性。图14中,横轴表示频率,纵轴表示衰减量。图14中,附图标记92表示由第二高通滤波器12形成的衰减极点(第二衰减极点92),附图标记94表示由第一和第三高通滤波器11、13形成的一个衰减极点。如图14所示,在变形例中,在通带的低频侧,通过衰减量变得足够大。

[0132]

此外,本发明不限定于上述实施方式,能够进行各种变更。例如,只要满足要保护的技术方案的条件,则本发明中的高通滤波器和低通滤波器各自的结构以及高通滤波器和低通滤波器各自的数量就不限于实施方式所示的例子,是任意的。

[0133]

另外,第四轴线a4也可以在与第二轴线a2不同的方向上延伸。在该情况下,第四轴线a4也可以相对于第一和第三轴线a1、a3分别平行。

[0134]

基于以上的说明可知,能够实施本发明的各种方式和变形例。因此,在要求保护的技术方案的等同范围内,即使采用上述最佳方式以外的方式也能够实施本发明。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。