1.本公开涉及半导体技术领域,特别是涉及一种半导体结构及其制备方法。

背景技术:

2.dram(dynamic random access memory,动态随机存取存储器),具有集成度高、功耗低、价格便宜等优点,所以在大容量存储器中普遍采用。

3.然而,随着半导体的高度集成以及摩尔定律向10nm至20nm之间级别的演进,要求有源区的排布更加密集,存储单元的尺寸越来越小,尤其是在关键尺寸小于15nm的dram制造过程中,减小位线之间的寄生电容变得越来越困难。因此,亟需一种半导体结构及其制备方法,在半导体尺寸收缩的同时减小寄生电容,以提高存储器件的性能。

技术实现要素:

4.基于此,本公开提供一种半导体结构及其制备方法,能够减小位线间的寄生电容,进而提高半导体器件的整体性能。

5.根据本公开的各种实施例,一方面提供一种半导体结构,包括衬底和第一位线立柱;第一位线立柱位于衬底上,其包括沿衬底的厚度方向依次叠置的第一介电层、第一绝缘层及第一接触层,第一绝缘层与衬底相邻;其中,第一绝缘层具有第一预设厚度,且第一预设厚度关联于第一介电层、第一绝缘层及第一接触层的厚度和;第一绝缘层的顶面沿第一方向的长度与第一绝缘层的底面沿第一方向的长度比为第一目标值;第一方向、第一绝缘层的顶面和底面均与厚度方向垂直。

6.于上述实施例中的半导体结构中,第一位线立柱中的第一绝缘层具有第一预设厚度,且第一预设厚度与第一介电层、第一绝缘层及第一接触层的厚度和相关,即当第一介电层、第一绝缘层及第一接触层的厚度和不变时,通过增大第一介电层和第一接触层的厚度,能够使得第一预设厚度减小。在相关技术中,由于多层结构层叠的复杂性以及刻蚀工艺精度的限制,会导致在刻蚀形成第一位线立柱时,使得第一位线立柱中越靠近衬底的部分层结构,其侧壁刻蚀越不完全,因此,会导致第一绝缘层的侧壁并不能够完全垂直于第一方向,即水平方向;且由于靠近衬底的部分刻蚀不完全,会使得第一绝缘层的底面沿第一方向的长度远大于其顶面沿第一方向的长度,以致第一绝缘层的底面以及靠近底面的位置沿第一方向的尺寸较大,占据了第一位线立柱侧壁方向的空间,使其与相邻的位线立柱之间的距离在靠近衬底的部分变得较小,增大了寄生电容,影响了器件的整体性能。本公开通过控制第一绝缘层的厚度,即第一预设厚度,来控制第一绝缘层侧壁的垂直程度,当第一预设厚度在第一介电层、第一绝缘层及第一接触层的厚度和中占据的比例更小时,第一绝缘层的侧壁更容易垂直于第一方向,同时第一绝缘层的顶面沿第一方向的长度与其底面沿第一方向的长度的差值更小,长度比被控制在第一目标值,第一位线立柱的垂直程度更好、性能更优。另外,第一绝缘层的垂直程度更好,也能够为第一绝缘层的侧壁方向留出更多的空间,使得第一位线立柱与其相邻的位线立柱之间的间距增大,进而减小寄生电容,进一步提升

存储结构的整体性能。

7.在其中一些实施例中,第一预设厚度与第一介电层的厚度、第一接触层的厚度均成负相关;其中,第一预设厚度的范围为[1/6t,1/4t];其中,t为第一介电层、第一绝缘层及第一接触层的厚度和。

[0008]

在其中一些实施例中,第一预设厚度的范围为[3nm,10nm]。

[0009]

在其中一些实施例中,第一目标值的范围为[0.8,1]。

[0010]

在其中一些实施例中,半导体结构还包括第一位线侧墙,其位于第一位线立柱的外侧壁上,第一位线侧墙沿第一方向的长度关联于第一绝缘层的底面沿第一方向的长度。

[0011]

在其中一些实施例中,第一位线侧墙沿第一方向的长度与第一绝缘层的底面沿第一方向的长度成负相关。

[0012]

在其中一些实施例中,衬底内包括沿第一方向交替排布的有源区和隔离结构,且衬底包括沿第一方向交替排布的凹槽及凸出部,第一位线立柱位于凸出部的顶面,且与其正下方的隔离结构连接;半导体结构还包括第二位线立柱,其部分位于凹槽内且与凹槽暴露的有源区连接。

[0013]

在其中一些实施例中,第一位线立柱还包括沿衬底的厚度方向依次叠置的第一阻挡层、第一导电层及第一位线盖层,第一接触层与第一阻挡层相邻;其中,第一位线盖层的厚度范围为[10nm,30nm]。

[0014]

在其中一些实施例中,第二位线立柱包括沿厚度方向依次叠置的位线插塞、第二阻挡层、第二导电层及第二位线盖层;其中,位线插塞与凹槽暴露的有源区连接,第二位线盖层的厚度范围为[10nm,30nm]。

[0015]

本公开的另一方面还提供一种半导体结构的制备方法,包括:提供衬底;于衬底上形成第一位线立柱,第一位线立柱包括沿衬底的厚度方向依次叠置的第一介电层、第一绝缘层及第一接触层,第一绝缘层与衬底相邻;其中,第一绝缘层具有第一预设厚度,且第一预设厚度关联于第一介电层、第一绝缘层及第一接触层的厚度和;第一绝缘层的顶面沿第一方向的长度与第一绝缘层的底面沿第一方向的长度比具有第一目标值;第一方向、第一绝缘层的顶面和底面均与厚度方向垂直。

[0016]

于上述实施例中的半导体结构的制备方法中,通过于沿衬底的厚度方向形成依次叠置的第一介电层、第一绝缘层及第一接触层,且将第一预设厚度设置为关联于第一介电层、第一绝缘层及第一接触层的厚度和、第一绝缘层的顶面沿第一方向的长度与第一绝缘层的底面沿第一方向的长度比具有第一目标值,能够使得第一绝缘层的侧壁与衬底表面的夹角更接近于90

°

,并且能够增大第一位线立柱与相邻位线立柱之间的空间,以减小寄生电容。本公开克服了相关技术中第一绝缘层的侧壁并不能够完全垂直于第一方向且第一位线立柱与相邻的位线立柱之间的距离在靠近衬底的部分较小的问题,通过控制第一绝缘层的厚度,即第一预设厚度,来控制第一绝缘层侧壁的垂直程度,当第一预设厚度在第一介电层、第一绝缘层及第一接触层的厚度和中占据的比例更小时,第一绝缘层的侧壁更容易垂直于第一方向,同时第一绝缘层的顶面沿第一方向的长度与其底面沿第一方向的长度的比值被控制在第一目标值,第一位线立柱的垂直程度更好、性能更优;还使得第一位线立柱与其相邻的位线立柱之间的间距增大,进而减小寄生电容以提高器件性能。

[0017]

在其中一些实施例中,衬底内包括沿第一方向交替排布的有源区和隔离结构,且

衬底包括沿第一方向交替排布的凹槽及凸出部,第一介电层位于凸出部上,第一位线立柱位于凸出部的顶面,且与其正下方的隔离结构连接;形成第一位线立柱,包括:于衬底上依次形成沿厚度方向叠置的绝缘材料层、插塞材料层、阻挡材料层、导电材料层及盖层材料层,绝缘材料层位于凸出部上的第一介电层上,插塞材料层至少填满凹槽;刻蚀导电材料层及盖层材料层,以形成沿厚度方向依次叠置的第一导电层及第一位线盖层;刻蚀绝缘材料层、插塞材料层及阻挡材料层,以形成第一位线立柱,第一位线立柱包括沿厚度方向依次叠置的第一介电层、第一绝缘层、第一接触层、第一阻挡层、第一导电层及第一位线盖层。

[0018]

在其中一些实施例中,形成第一绝缘层、第一接触层及第一阻挡层,包括:于第一预设工艺环境下刻蚀绝缘材料层、插塞材料层及阻挡材料层,剩余的绝缘材料层形成第一绝缘层,剩余的插塞材料层位于第一绝缘层顶面的部分形成第一接触层,剩余的插塞材料层位于凹槽内及凹槽顶面的部分形成中间插塞层,剩余的阻挡材料层位于第一接触层顶面的部分形成第一阻挡层,剩余的阻挡材料层位于中间插塞层顶面的部分形成第二阻挡层。

[0019]

在其中一些实施例中,第一预设工艺环境包括第一工艺气体及第一预设压力;其中,第一工艺气体选自氯气、三氟化氮、氮气、惰性气体和其组合,第一预设压力范围为[4mt,6mt]。

[0020]

在其中一些实施例中,形成第一导电层及第一位线盖层,包括:于第二预设工艺环境下刻蚀盖层材料层,并于第三预设工艺环境下刻蚀导电材料层,剩余的导电材料层位于第一阻挡层顶面的部分形成第一导电层,剩余的导电材料层位于第二阻挡层顶面的部分形成第二导电层,剩余的盖层材料层位于第一导电层顶面的部分形成第一位线盖层,剩余的盖层材料层位于第二导电层顶面的部分形成第二位线盖层。

[0021]

在其中一些实施例中,形成第一位线立柱之后,还包括:于第四预设工艺环境下对中间插塞层进行处理,形成沿第一方向间隔排布的位线插塞,以形成第二位线立柱,第二位线立柱包括沿厚度方向依次叠置的位线插塞、第二阻挡层、第二导电层以及第二位线盖层。

[0022]

在其中一些实施例中,第二预设工艺环境包括第二工艺气体及第二预设压力;其中,第二工艺气体选自四氟化碳、三氟甲烷、氧气、氮气、惰性气体和其组合,第二预设压力范围为[13mt,17mt]。

[0023]

在其中一些实施例中,第三预设工艺环境包括第三工艺气体及第三预设压力;其中,第三工艺气体选自氯气、三氟化氮、氧气、氮气、惰性气体和其组合,第三预设压力范围为[4mt,6mt]。

[0024]

在其中一些实施例中,第四预设工艺环境包括第四工艺气体及第四预设压力;其中,第四工艺气体选自溴化氢、氧气、惰性气体和其组合,第四预设压力范围为[18mt,22mt]。

附图说明

[0025]

为了更清楚地说明本公开实施例中的技术方案,下面将对实施例描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本公开实施例的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

[0026]

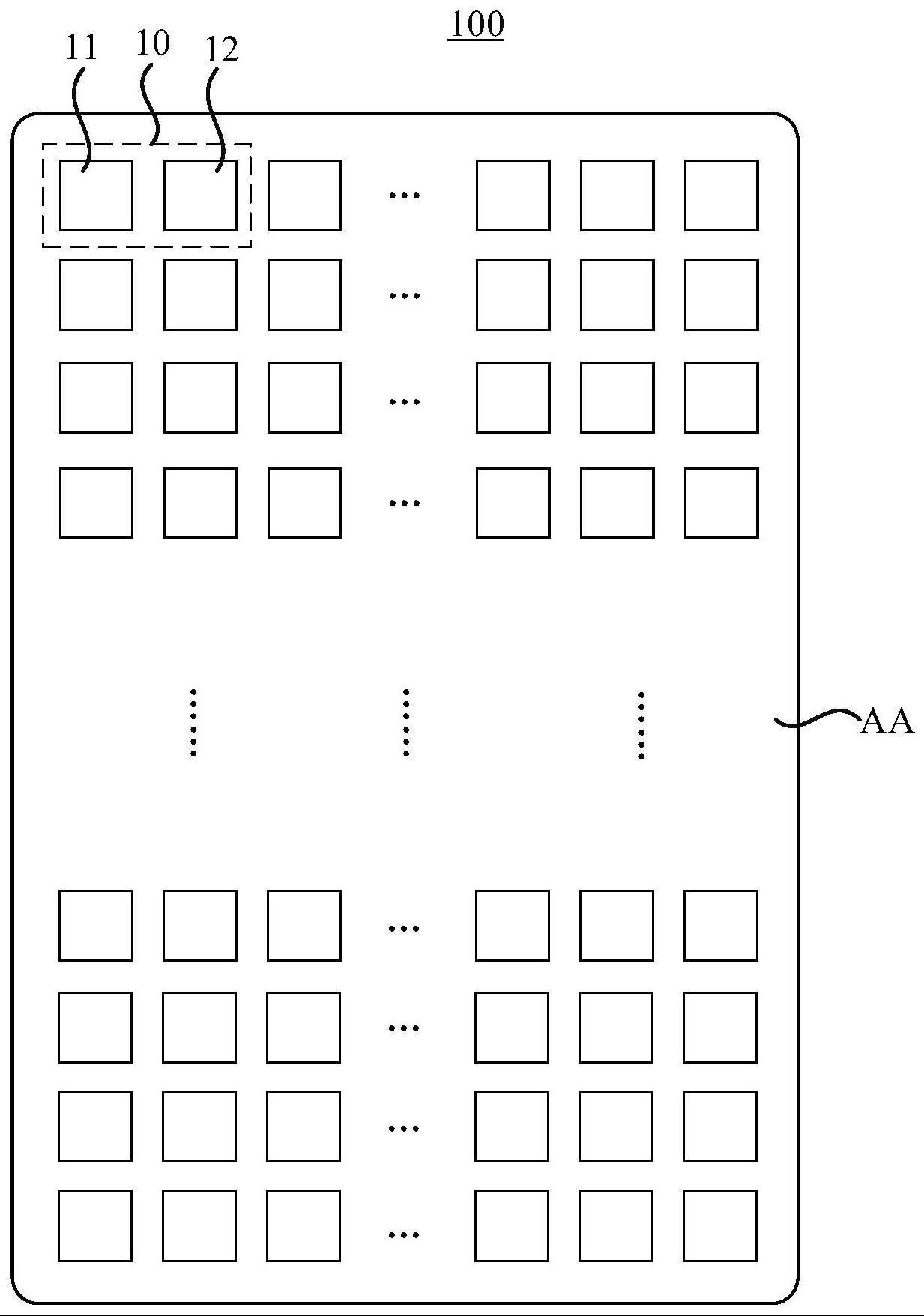

图1显示为本公开一实施例中提供的一种半导体结构的截面示意图;

图2显示为本公开一实施例中提供的一种相关技术中半导体结构的截面示意图;图3显示为本公开另一实施例中提供的一种半导体结构的截面示意图;图4显示为本公开一实施例中提供的一种电容插塞-有源区接触面积与第一预设厚度关系的曲线示意图;图5显示为本公开一实施例中提供的一种半导体结构的制备方法的流程示意图;图6显示为本公开一实施例中提供的一种于衬底内形成初始隔离材料层的截面结构示意图;图7显示为本公开一实施例中提供的一种在图6所示的结构上形成中间隔离材料层的截面结构示意图;图8显示为本公开一实施例中提供的一种在图7所示的结构上形成隔离结构、第一介电层、绝缘材料层及插塞材料层的截面结构示意图;图9显示为本公开一实施例中提供的一种在图8所示的结构上形成阻挡材料层、导电材料层及盖层材料层的截面结构示意图;图10显示为本公开一实施例中提供的一种在图9所示的结构上形成第一掩膜层及第二掩膜层的截面结构示意图;图11显示为本公开一实施例中提供的一种在图10所示的结构上形成第一位线盖层及第二位线盖层的截面结构示意图;图12显示为本公开一实施例中提供的一种在图11所示的结构上形成第一导电层及第二导电层的截面结构示意图;图13显示为本公开一实施例中提供的一种在图12所示的结构上形成第一绝缘层、第一接触层、第一阻挡层、第二阻挡层及中间插塞层的截面结构示意图;图14显示为本公开一实施例中提供的一种在图13所示的结构上形成位线插塞的截面结构示意图;图15显示为本公开一实施例中提供的一种在图14所示的结构上形成第一介质层及第四介质层的截面结构示意图;图16显示为本公开一实施例中提供的一种在图15所示的结构上形成第二介质层及第五介质层的截面结构示意图;图17显示为本公开一实施例中提供的一种在图16所示的结构上形成第三介质层、第六介质层及第一隔离层的截面结构示意图;图18显示为本公开一实施例中提供的一种在图17所示的结构上形成第二隔离层及第三隔离层的截面结构示意图;图19显示为本公开一实施例中提供的一种在图15所示的结构上形成第三介质层及第六介质层的截面结构示意图;图20显示为本公开一实施例中提供的一种在图19所示的结构上形成电容插塞沟槽的截面结构示意图。

[0027]

附图标记说明:10、衬底;101、有源区;102、隔离结构;1021、初始隔离材料层;1022、中间隔离材料层;10a、凹槽;10b、凸出部;111、绝缘材料层;112、插塞材料层;113、阻挡材料层;114、导电材料层;115、盖层材料层;121、第一掩膜层;122、第二掩膜层;13、第一位线立柱;131、第一

介电层;132、第一绝缘层;133、第一接触层;134、第一阻挡层;135、第一导电层;136、第一位线盖层;14、第二位线立柱;141、位线插塞;1411、中间插塞层;142、第二阻挡层;143、第二导电层;144、第二位线盖层;15、第一位线侧墙;151、第一介质层;152、第二介质层;153、第三介质层;16、第二位线侧墙;161、第四介质层;162、第五介质层;1621、第五子介质层;163、第六介质层;1631、第六子介质层;17、第一隔离层;18、第二隔离层;19、第三隔离层;20、电容插塞沟槽;21、电容插塞;30、有源层;31、第一位线结构;311、介电层;312、绝缘层;313/321、接触层;314/322、阻挡层;315/323、导电层;316/324、盖层;32、第二位线结构;33、位线侧墙;331、第一子侧墙;332、第二子侧墙;333、第三子侧墙。

具体实施方式

[0028]

为了便于理解本公开,下面将参阅相关附图对本公开进行更全面的描述。附图中给出了本公开的首选实施例。但是,本公开可以以许多不同的形式来实现,并不限于本文所描述的实施例。相反地,提供这些实施例的目的是使对本公开的公开内容更加透彻全面。除非另有定义,本文所使用的所有的技术和科学术语与属于本公开的技术领域的技术人员通常理解的含义相同。本文中在本公开的说明书中所使用的术语只是为了描述具体的实施例的目的,不是旨在于限制本公开。

[0029]

应当明白,当元件或层被称为“在...上”、“与...相邻”、“连接到”或“耦合到”其它元件或层时,其可以直接地在其它元件或层上、与之相邻、连接或耦合到其它元件或层,或者可以存在居间的元件或层。相反,当元件被称为“直接在...上”、“与...直接相邻”、“直接连接到”或“直接耦合到”其它元件或层时,则不存在居间的元件或层。空间关系术语例如“在...下”、“在...下面”、“下面的”、“在...之下”、“在...之上”、“上面的”等,在这里可以用于描述图中所示的一个元件或特征与其它元件或特征的关系。

[0030]

应当明白,除了图中所示的取向以外,空间关系术语还包括使用和操作中的器件的不同取向。例如,如果附图中的器件翻转,描述为“在其它元件下面”或“在其之下”或“在其下”元件或特征将取向为在其它元件或特征“上”。因此,示例性术语“在...下面”和“在...下”可包括上和下两个取向。此外,器件也可以包括另外地取向(譬如,旋转90度或其它取向),并且在此使用的空间描述语相应地被解释。在此使用时,单数形式的“一”、“一个”和“所述/该”也可以包括复数形式,除非上下文清楚指出另外的方式。还应明白,当术语“组成”和/或“包括”在该说明书中使用时,可以确定所述特征、整数、步骤、操作、元件和/或部件的存在,但不排除一个或更多其它的特征、整数、步骤、操作、元件、部件和/或组的存在或添加。同时,在此使用时,术语“和/或”包括相关所列项目的任何及所有组合。

[0031]

需要说明的是,本实施例中所提供的图示仅以示意方式说明本公开的基本构想,虽图示中仅显示与本公开中有关的组件而非按照实际实施时的组件数目、形状及尺寸绘制,其实际实施时各组件的型态、数量及比例可为一种随意的改变,且其组件布局型态也可能更为复杂。

[0032]

存储器是用来存储程序和各种数据信息的记忆部件,按存储器的使用类型可分为rom(read-only memory,只读存储器)和ram(random access memory,随机存取存储器),根据存储单元的工作原理不同,ram分为sram(static ram,静态随机存取存储器)和dram,dram与sram相比具有集成度高、功耗低、价格便宜等优点,所以在大容量存储器中普遍采

用。dram中的基本存储单元由两个元件组成,即晶体管和电容器,晶体管用于对电容器充电或放电,充电或放电均通过字线和位线完成。

[0033]

随着半导体的高度集成,以及摩尔定律向1xnm级别,即10nm至20nm之间的演进,要求有源区的排布更加密集。随着动态随机存取存储器技术的发展,存储单元的尺寸越来越小,存储器中结构的工艺难度越来越大,并且器件中寄生电容较大的问题较为常见。基于上述技术问题,本公开提供一种半导体结构及其制备方法,能够减小位线间的寄生电容,进而提高半导体器件的整体性能。

[0034]

需要说明的是,本公开中衬底的厚度方向可以为oy方向,第一方向可以为ox方向。

[0035]

作为示例,请参阅图1,本公开一方面提供一种半导体结构,包括衬底(未图示)和第一位线立柱13;第一位线立柱13位于衬底上,其包括沿衬底10的厚度方向(例如oy方向)依次叠置的第一介电层131、第一绝缘层132及第一接触层133,第一绝缘层132与衬底10相邻;其中,第一绝缘层132具有第一预设厚度,且第一预设厚度关联于第一介电层131、第一绝缘层132及第一接触层133的厚度和;第一绝缘层132的顶面沿第一方向(例如ox方向)的长度与第一绝缘层132的底面沿第一方向(例如ox方向)的长度比为第一目标值;第一方向(例如ox方向)、第一绝缘层132的顶面和底面均与厚度方向(例如oy方向)垂直。

[0036]

于上述实施例中的半导体结构中,第一位线立柱13中的第一绝缘层132具有第一预设厚度,且第一预设厚度与第一介电层131、第一绝缘层132及第一接触层133的厚度和相关,即当第一介电层131、第一绝缘层132及第一接触层133的厚度和不变时,通过增大第一介电层131和第一接触层133的厚度,能够使得第一预设厚度减小。在相关技术中,由于多层结构层叠的复杂性以及刻蚀工艺精度的限制,会导致在刻蚀形成第一位线立柱13时,使得第一位线立柱13中越靠近衬底的部分层结构,其侧壁刻蚀越不完全,因此,会导致第一绝缘层132的侧壁并不能够完全垂直于第一方向(例如ox方向),即水平方向;且由于靠近衬底的部分刻蚀不完全,会使得第一绝缘层132的底面沿第一方向(例如ox方向)的长度远大于其顶面沿第一方向(例如ox方向)的长度,以致第一绝缘层132的底面以及靠近底面的位置沿第一方向(例如ox方向)的尺寸较大,占据了第一位线立柱13侧壁方向的空间,使其与相邻的位线立柱之间的距离在靠近衬底的部分变得较小,增大了寄生电容,影响了器件的整体性能。本公开通过控制第一绝缘层132的厚度,即第一预设厚度,来控制第一绝缘层132侧壁的垂直程度,当第一预设厚度在第一介电层131、第一绝缘层132及第一接触层133的厚度和中占据的比例更小时,第一绝缘层132的侧壁更容易垂直于第一方向(例如ox方向),同时第一绝缘层132的顶面沿第一方向(例如ox方向)的长度与其底面沿第一方向(例如ox方向)的长度的差值更小,长度比被控制在第一目标值,第一位线立柱13的垂直程度更好、性能更优。另外,第一绝缘层132的垂直程度更好,也能够为第一绝缘层132的侧壁方向留出更多的空间,使得第一位线立柱13与其相邻的位线立柱之间的间距增大,进而减小寄生电容,进一步提升存储结构的整体性能。

[0037]

作为示例,请参阅图1及图2,图2为相关技术中现有的第一位线结构31与第二位线结构32的截面示意图,第一位线结构31与衬底(未图示)内的隔离绝缘区(未图示)相连,第二位线结构32与衬底内的有源层30相连,第一位线结构31包括沿远离衬底表面的方向依次叠置的介电层311、绝缘层312、接触层313、阻挡层314、导电层315和盖层316,第二位线结构32包括沿远离衬底表面的方向依次叠置的接触层321、阻挡层322、导电层323和盖层324。相

关技术中普遍由于多层结构层叠的复杂性以及刻蚀工艺精度的限制,绝缘层312的侧壁并不能够完全垂直于第一方向(例如ox方向),即水平方向;且由于靠近衬底的部分刻蚀不完全,会使得绝缘层312的底面沿第一方向(例如ox方向)的长度范围为[21.8nm,22.0nm],从而导致相关技术中的绝缘层312普遍大于甚至远大于其顶面沿第一方向(例如ox方向)的长度范围[9.0nm,9.2nm],占据了第一位线结构31侧壁方向的空间,其顶面沿第一方向(例如ox方向)的长度比与其底面沿第一方向(例如ox方向)的长度比范围为[0.4,0.6],使其与相邻的第二位线结构32之间的距离在靠近衬底的部分变得较小,增大了附近区域的寄生电容。而本公开提供的半导体结构中,由于控制了第一绝缘层132的厚度,使得第一绝缘层132的侧壁垂直于第一方向(例如ox方向)的程度得到改善,且由于靠近衬底的部分刻蚀完全,第一绝缘层132的底面沿第一方向(例如ox方向)的长度范围为[9.8nm,10.0nm],具体地,第一绝缘层132的底面沿第一方向(例如ox方向)的长度可以为9.8nm、9.83nm、9.86nm、9.9nm、9.95nm或10.0nm等等,尺寸接近于其顶面沿第一方向(例如ox方向)的长度范围[8.5nm,8.7nm],具体地,其顶面沿第一方向(例如ox方向)的长度可以为8.5nm、8.53nm、8.6nm、8.63nm、8.66nm或8.7nm等等,第一位线立柱13与第二位线立柱14之间的空间更大,且第一位线立柱13顶面沿第一方向(例如ox方向)的长度比与其底面沿第一方向(例如ox方向)的长度比具有第一目标值,第一目标值的范围为[0.8,1],使得第一位线立柱13的垂直程度更好;具体地,第一目标值可以为0.8、0.85、0.9、0.95或1等等。

[0038]

作为示例,请继续参阅图1,第一预设厚度与第一介电层的厚度、第一接触层的厚度均成负相关,具体地,在本公开中,第一预设厚度越薄,第一接触层的厚度和第一介电层的厚度就越厚,因此,第一预设厚度占上述三者的比例就越小,能够使得三者作为一个整体的侧壁表面垂直程度更好;其中,第一预设厚度的范围为[1/6t,1/4t];其中,t为第一介电层131、第一绝缘层132及第一接触层133的厚度和。具体地,第一预设厚度可以为1/6t、1/5t或1/4t等等、。当第一介电层131、第一绝缘层132及第一接触层133的厚度和不变时,通过增大第一介电层131和第一接触层133的厚度,能够使得第一预设厚度减小,即使得第一预设厚度占上述厚度和的比例减小,因此刻蚀难度更小,能够得到侧壁与第一方向(例如ox方向)垂直程度更好的第一绝缘层132,从而减小寄生电容并提高感测裕度。

[0039]

作为示例,请继续参阅图1,半导体结构还包括第一位线侧墙15,其位于第一位线立柱13的外侧壁上,第一位线侧墙15沿第一方向(例如ox方向)的长度关联于第一绝缘层132的底面沿第一方向(例如ox方向)的长度。当第一绝缘层132的底面沿第一方向(例如ox方向)的长度减小时,能够为其附近相邻的第一位线侧墙15提供空间,使其沿第一方向(例如ox方向)的尺寸增大。

[0040]

作为示例,请继续参阅图1,第一位线侧墙15沿第一方向(例如ox方向)的长度与第一绝缘层132的底面沿第一方向(例如ox方向)的长度成负相关。因此,当第一绝缘层132的底面沿第一方向(例如ox方向)的长度减小时,能够使得第一位线侧墙15增厚,从而更好地为第一位线立柱13和第二位线立柱14提供隔离作用,以减小两者之间的寄生电容。

[0041]

作为示例,请继续参阅图1,第一位线侧墙15包括沿远离第一位线立柱13的方向依次排布的第一介质层151、第二介质层152及第三介质层153;其中,第一介质层151与所述第三介质层153的材料相同,且与第二介质层152的材料不同。第一位线侧墙15位于第一位线立柱13和第二位线立柱14之间的空隙内,能够将两者进行隔离,以减小寄生电容。

[0042]

作为示例,请继续参阅图1及图2,由于当第一绝缘层132的底面沿第一方向(例如ox方向)的长度减小,为第一位线侧墙15沿第一方向(例如ox方向)的长度的增大提供了空间,因此,第一位线侧墙15能够随着第一绝缘层132底面尺寸的减小而变厚。具体地,可以将第二介质层152与第三介质层153沿第一方向(例如ox方向)的长度增大,以更好地提供隔离,减小寄生电容。

[0043]

作为示例,请参阅图3,衬底10内包括沿第一方向(例如ox方向)交替排布的有源区101和隔离结构102,且衬底10包括沿第一方向(例如ox方向)交替排布的凹槽10a及凸出部10b,第一位线立柱13位于凸出部10b的顶面,且与其正下方的隔离结构102连接;半导体结构还包括第二位线立柱14,其部分位于凹槽10a内且与凹槽10a暴露的有源区101连接,即第二位线立柱14为存储器实际工作过程中所使用的位线立柱,第二位线立柱14与第一位线立柱13间隔排布,彼此相邻,在半导体尺寸逐渐微缩的情况下,两者之间的寄生电容会增大,通过本公开中第一绝缘层132的尺寸及结构设置,能够增大两者之间的间隔,因此能够减小寄生电容并改善感测裕度的问题。

[0044]

作为示例,请参阅图1及图3,第一位线立柱13还包括沿衬底10的厚度方向(例如oy方向)依次叠置的第一阻挡层134、第一导电层135及第一位线盖层136,第一接触层133与第一阻挡层134相邻;其中,第一位线盖层136的厚度范围为[10nm,30nm]。具体地,第一位线盖层136的厚度可以为10nm、15nm、20nm、25nm或30nm等等。将第一位线盖层136设置在上述厚度范围内,能够改善第一位线立柱13易倾斜甚至倒塌的问题,提高第一位线立柱13的稳定性能,进而提升存储器的整体性能。

[0045]

作为示例,请继续参阅图1及图3,第二位线立柱14包括沿厚度方向(例如oy方向)依次叠置的位线插塞141、第二阻挡层142、第二导电层143及第二位线盖层144;其中,位线插塞141与凹槽10a暴露的有源区101连接,第二位线盖层144的厚度范围为[10nm,30nm]。具体地,第二位线盖层144的厚度可以为10nm、15nm、20nm、25nm或30nm等等。第二位线盖层144的厚度可以与第一位线盖层136的厚度相同,将第二位线盖层144设置在上述厚度范围内,能够改善第二位线立柱14易倾斜甚至倒塌的问题,提高第二位线立柱14的稳定性能。

[0046]

作为示例,请继续参阅图3,半导体结构还包括电容插塞21,其位于沿所述第一方向(例如ox方向)相邻的所述第一位线立柱13和所述第二位线立柱14之间,且与其正下方的有源区101连接。电容插塞21用于将电容结构与有源区101相连,以构成存储单元。

[0047]

作为示例,请继续参阅图3,半导体结构还包括电容接触层(未图示),其位于所述电容插塞21沿所述厚度方向(例如oy方向)远离所述衬底10的一侧,电容接触层沿所述厚度方向(例如oy方向)远离所述衬底10的一侧还设置有电容结构(未图示),电容结构与第二位线立柱14共同用于构成存储单元。

[0048]

作为示例,请继续参阅图1,第一预设厚度的范围为[3nm,10nm]。具体地,第一预设厚度可以为3nm、4nm、5nm、8nm或10nm等等。

[0049]

作为示例,请参阅图3及图4,图4显示为在第一绝缘层132的形貌不同的三种情况下,第一位线立柱13中第一预设厚度的变化对电容插塞21与有源区101接触面积的影响,三条曲线由上到下分别表示位线中靠近底部的侧壁垂直程度逐渐变差的结构,即在三条曲线中,第一绝缘层侧壁的垂直程度由上到下依次变差,从而使得第一绝缘层所占用的空间从上到下依次变大,占用电容插塞21的空间越来越大。因此,最下方的曲线所表示的结构占用

的电容插塞21的空间最大,导致电容插塞21与其下方有源区101的接触面积最小,接触效果最差。从图4中还可以看出,在同一条曲线中,第一预设厚度大于8nm时,电容插塞21与有源区101的接触面积减小趋势越来越快,与预设接触面积差距越来越大。因此,将第一预设厚度设置为[3nm,10nm],能够将电容插塞21与有源区101的接触面积稳定在一个预设值附近,从而提高半导体结构的导电性能及接触性能。

[0050]

作为示例,请参阅图5,本公开的另一方面还提供一种半导体结构的制备方法,包括:步骤s2:提供衬底;步骤s4:于衬底上形成第一位线立柱,第一位线立柱包括沿衬底的厚度方向依次叠置的第一介电层、第一绝缘层及第一接触层,第一绝缘层与衬底相邻;其中,第一绝缘层具有第一预设厚度,且第一预设厚度关联于第一介电层、第一绝缘层及第一接触层的厚度和;第一绝缘层的顶面沿第一方向的长度与第一绝缘层的底面沿第一方向的长度比具有第一目标值;第一方向、第一绝缘层的顶面和底面均与厚度方向垂直。

[0051]

于上述实施例中的半导体结构的制备方法中,于沿衬底的厚度方向形成依次叠置的第一介电层、第一绝缘层及第一接触层,且将第一预设厚度设置为关联于第一介电层、第一绝缘层及第一接触层的厚度和、第一绝缘层的顶面沿第一方向的长度与第一绝缘层的底面沿第一方向的长度比具有第一目标值,能够使得第一绝缘层的侧壁与衬底表面的夹角更接近于90

°

,并且能够增大第一位线立柱与相邻位线立柱之间的空间,以减小寄生电容。本公开克服了相关技术中第一绝缘层的侧壁并不能够完全垂直于第一方向且第一位线立柱与相邻的位线立柱之间的距离在靠近衬底的部分较小的问题,通过控制第一绝缘层的厚度,即第一预设厚度,来控制第一绝缘层侧壁的垂直程度,当第一预设厚度在第一介电层、第一绝缘层及第一接触层的厚度和中占据的比例更小时,第一绝缘层的侧壁更容易垂直于第一方向,同时第一绝缘层的顶面沿第一方向的长度与其底面沿第一方向的长度的比值被控制在第一目标值,第一位线立柱的垂直程度更好、性能更优;还使得第一位线立柱与其相邻的位线立柱之间的间距增大,进而减小寄生电容以提高器件性能。

[0052]

作为示例,请参阅图6-图8,步骤s4中包括:步骤s41:于衬底10内形成包括沿第一方向(例如ox方向)交替排布的有源区101和隔离结构102,且衬底10包括沿第一方向(例如ox方向)交替排布的凹槽10a及凸出部10b,第一介电层131位于凸出部10b上,第一位线立柱13位于凸出部10b的顶面,且与其正下方的隔离结构102连接。

[0053]

作为示例,请参阅图6,步骤s41中包括:步骤s411:于衬底10内形成沿第一方向(例如ox方向)间隔排布的初始隔离材料层1021,初始隔离材料层1021用于定义有源区101的位置。

[0054]

在步骤s411中,初始隔离材料层1021还覆盖衬底10的顶面,其材料可以包括氧化硅或其他绝缘材料中的一种或多种。

[0055]

作为示例,请继续参阅图6,衬底10可以采用半导体材料、绝缘材料、导体材料或者它们的任意组合构成。衬底10可以为单层结构,也可以为多层结构。例如,衬底10可以是诸如硅(si)衬底、硅锗(sige)衬底、硅锗碳(sigec)衬底、碳化硅(sic)衬底、砷化镓(gaas)衬底、砷化铟(inas)衬底、磷化铟(inp)衬底或其它的iii/v半导体衬底或ii/vi半导体衬底。

或者,还例如,衬底10可以是包括诸如si/sige、si/sic、绝缘体上硅(soi)或绝缘体上硅锗的层状衬底。本领域的技术人员可以根据衬底10上形成的晶体管类型选择衬底10的类型,因此,衬底10的类型不应限制本公开的保护范围。

[0056]

作为示例,请参阅图7,步骤s41中还包括:步骤s412:对初始隔离材料层1021的顶面进行平坦化处理,以形成中间隔离材料层1022。

[0057]

在步骤s412中,平坦化处理工艺可以采用化学机械抛光(chemical mechanical polishing,简称cmp)、反刻、物理抛光等工艺中的一种或多种。

[0058]

作为示例,请参阅图8,步骤s41中包括:步骤s413:于衬底10表面形成沿第一方向(例如ox方向)交替排布的凹槽10a及凸出部10b,中间隔离材料层1022位于凸出部10b顶面的部分为第一介电层131。

[0059]

在步骤s413中,凹槽10a至少暴露出有源区101的顶面,第一介电层131至少与隔离结构102的顶面相连。

[0060]

作为示例,请参阅图8-图13,形成第一位线立柱13,包括:步骤s42:于衬底10上依次形成沿厚度方向(例如oy方向)叠置的绝缘材料层111、插塞材料层112、阻挡材料层113、导电材料层114及盖层材料层115,绝缘材料层111位于凸出部10b上的第一介电层131上,插塞材料层112至少填满凹槽10a;步骤s43:刻蚀导电材料层114及盖层材料层115,以形成沿厚度方向(例如oy方向)依次叠置的第一导电层135及第一位线盖层136;步骤s44:刻蚀绝缘材料层111、插塞材料层112及阻挡材料层113,以形成第一位线立柱13,第一位线立柱13包括沿厚度方向(例如oy方向)依次叠置的第一介电层131、第一绝缘层132、第一接触层133、第一阻挡层134、第一导电层135及第一位线盖层136。

[0061]

作为示例,请参阅图8及图9,在步骤s42中,绝缘材料层111的材料可以包括氮化硅,插塞材料层112的材料可以包括多晶硅,阻挡材料层113的材料可以选自钽、氮化钽、钛、氮化钛和其组合,导电材料层114的材料可以选自钨、钽、钼、金、银和其组合,盖层材料层115可以包括氮化硅。

[0062]

作为示例,请参阅图10、图11及图12,在步骤s43中形成第一导电层135及第一位线盖层136,包括:步骤s431:于第二预设工艺环境下刻蚀盖层材料层115,并于第三预设工艺环境下刻蚀导电材料层114,剩余的导电材料层114位于第一阻挡层134顶面的部分形成第一导电层135,剩余的导电材料层114位于第二阻挡层142顶面的部分形成第二导电层143,剩余的盖层材料层115位于第一导电层135顶面的部分形成第一位线盖层136,剩余的盖层材料层115位于第二导电层143顶面的部分形成第二位线盖层144。

[0063]

作为示例,请参阅图10,步骤s431包括:步骤s4311:盖层材料层115的表面形成间隔排布的第一掩膜层121及第二掩膜层122,第二掩膜层122位于第一掩膜层121的顶面。

[0064]

在步骤s4311中,第一掩膜层121的材料可以为无定形碳层(amorphous carbon layer,简称acl),第二掩膜层122的材料可以为氮氧化硅;形成第一掩膜层121及第二掩膜层122的过程可以通过沉积、图形化刻蚀等,且通过第五预设工艺环境刻蚀形成,第五预设

工艺环境包括第五工艺气体及第五预设压力,其中,第五工艺气体选自羰基硫(cos)、氧气、氮气和其组合,第五预设压力范围为[4mt,6mt];具体地,羰基硫(cos)的流量范围为[50sccm,70sccm],氧气的流量范围为[140sccm,160sccm],氮气的流量范围为[70sccm,90sccm]。

[0065]

步骤s4312:于第二预设工艺环境下刻蚀盖层材料层115。

[0066]

步骤s4313:于第三预设工艺环境下刻蚀导电材料层114。

[0067]

作为示例,第五预设工艺环境中,第五预设压力可以为4mt、4.5mt、5mt或6mt等等;羰基硫(cos)的流量可以为50sccm、60sccm、65sccm或70sccm等等,氧气的流量可以为140sccm、145sccm、150sccm或160sccm等等,氮气的流量可以为70sccm、75sccm、80sccm或90sccm等等。

[0068]

作为示例,请参阅图11,第二预设工艺环境包括第二工艺气体及第二预设压力;其中,第二工艺气体选自四氟化碳(cf4)、三氟甲烷(chf3)、氧气、氮气、惰性气体和其组合,第二预设压力范围为[13mt,17mt];具体地,四氟化碳的流量范围为[70sccm,80sccm],三氟甲烷的流量范围为[220sccm,230sccm],氧气的流量范围为[30sccm,40sccm],氩气的流量范围为[140sccm,160sccm]。

[0069]

作为示例,第二预设工艺环境中,第二预设压力可以为13mt、14mt、15mt或17mt等等;四氟化碳的流量可以为70sccm、72sccm、75sccm或80sccm等等,三氟甲烷的流量可以为220sccm、222sccm、225sccm或230sccm等等,氧气的流量可以为30sccm、32sccm、36sccm或40sccm等等,氩气的流量可以为140sccm、145sccm、150sccm或160sccm等等。

[0070]

作为示例,请参阅图12,第三预设工艺环境包括第三工艺气体及第三预设压力;其中,第三工艺气体选自氯气、三氟化氮、氧气、氮气、惰性气体和其组合,第三预设压力范围为[4mt,6mt];具体地,氯气的流量范围为[19sccm,23sccm],三氟化氮的流量范围为[11sccm,12sccm],氧气的流量范围为[20sccm,22sccm],氩气的流量范围为[18sccm,22sccm],氮气的流量范围为[110sccm,114sccm]。

[0071]

作为示例,第三预设工艺环境中,第三预设压力可以为3mt、4mt、4.5mt或5mt等等;氯气的流量可以为19sccm、20sccm、21sccm或23sccm等等,三氟化氮的流量可以为11sccm、11.2sccm、11.5sccm或12sccm等等,氧气的流量可以为20sccm、21sccm、21.5sccm或22sccm等等,氩气的流量可以为18sccm、19sccm、20sccm或22sccm等等,氮气的流量可以为110sccm、112sccm或114sccm等等。

[0072]

作为示例,请参阅图13,步骤s44中形成第一绝缘层132、第一接触层133及第一阻挡层134,包括:步骤s441:于第一预设工艺环境下刻蚀绝缘材料层111、插塞材料层112及阻挡材料层113,剩余的绝缘材料层111形成第一绝缘层132,剩余的插塞材料层112位于第一绝缘层132顶面的部分形成第一接触层133,剩余的插塞材料层112位于凹槽10a内及凹槽10a顶面的部分形成中间插塞层1411,剩余的阻挡材料层113位于第一接触层133顶面的部分形成第一阻挡层134,剩余的阻挡材料层113位于中间插塞层1411顶面的部分形成第二阻挡层142。

[0073]

作为示例,请参阅图13,在步骤s441中,通过于第一预设工艺环境下刻蚀绝缘材料层111、插塞材料层112及阻挡材料层113,将绝缘材料层111、插塞材料层112及阻挡材料层

113的侧壁形貌设置于垂直衬底10表面,由于控制了绝缘材料层111、插塞材料层112的厚度,因此,在进行垂直刻蚀时,第一接触层133和第一绝缘层132的侧壁能够更好地垂直于第一方向(例如ox方向),且第一绝缘层132的顶面及底面沿第一方向(例如ox方向)的长度差值减小,保证了第一位线立柱13的垂直程度的同时,还能够减小寄生电容。

[0074]

作为示例,请继续参阅图13,第一预设工艺环境包括第一工艺气体及第一预设压力;其中,第一工艺气体选自氯气、三氟化氮、氮气、惰性气体和其组合,第一预设压力范围为[4mt,6mt];具体地,氯气的流量范围为[25sccm,35sccm],三氟化氮的流量范围为[8sccm,10sccm],氦气的流量范围为[160sccm,180sccm],氮气的流量范围为[180sccm,200sccm]。

[0075]

作为示例,第一预设工艺环境中,第一预设压力可以为4mt、5mt、5.5mt或6mt等等;氯气的流量可以为25sccm、28sccm、30sccm或35sccm等等,三氟化氮的流量可以为8sccm、9sccm、9.5sccm或10sccm等等,氦气的流量可以为160sccm、165sccm、170sccm或180sccm等等,氮气的流量可以为180sccm、190sccm或200sccm等等。

[0076]

作为示例,请参阅图14,形成第一位线立柱13之后,还包括:步骤s5:于第四预设工艺环境下对中间插塞层1411进行处理,形成沿第一方向(例如ox方向)间隔排布的位线插塞141,以形成第二位线立柱14,第二位线立柱14包括沿厚度方向(例如oy方向)依次叠置的位线插塞141、第二阻挡层142、第二导电层143以及第二位线盖层144。

[0077]

作为示例,请继续参阅图14,第四预设工艺环境包括第四工艺气体及第四预设压力;其中,第四工艺气体选自溴化氢(hbr)、氧气、惰性气体和其组合,第四预设压力范围为[18mt,22mt];具体地,溴化氢的流量范围为[460sccm,500sccm],氧气的流量范围为[16sccm,20sccm],氦气的流量范围为[2500sccm,3500sccm]。

[0078]

作为示例,第四预设工艺环境中,第四预设压力可以为18mt、19mt、20mt或22mt等等;溴化氢的流量可以为460sccm、470sccm、480sccm或500sccm等等,氧气的流量可以为16sccm、18sccm、19sccm或20sccm等等,氦气的流量可以为2500sccm、2800sccm、3000sccm或3500sccm等等。

[0079]

作为示例,请参阅图3、图15-图20,形成所述第一位线立柱13及所述第二位线立柱14之后,还包括:步骤s6:于所述第一位线立柱13的外侧壁上形成第一位线侧墙15,以及于所述第二位线立柱14的外侧壁上形成第二位线侧墙16;步骤s7:于沿所述第一方向(例如ox方向)相邻的所述第一位线立柱13及所述第二位线立柱14之间形成电容插塞21,所述电容插塞21与所述有源区101连接。

[0080]

作为示例,请参阅图15,步骤s6中包括:步骤s61:于第一位线立柱13的侧壁表面形成第一介质层151,并同时于凹槽10a内壁表面形成依次叠置的第四介质层161、第五子介质层1621及第六子介质层1631,第四介质层161还覆盖第二位线立柱14的侧壁表面,第一介质层151及第四介质层161还覆盖第一位线立柱13与第二位线立柱14之间暴露出的衬底10的表面。

[0081]

在步骤s61中,第一介质层151、第四介质层161及第六子介质层1631的材料相同,均可以为氮化硅,第五子介质层1621的材料可以为氧化硅。

[0082]

作为示例,请参阅图16,步骤s6中还包括:

步骤s62:于第一介质层151的表面形成第二介质层152并于第四介质层161的表面形成第五介质层162,第五介质层162还包括第五子介质层1621。

[0083]

在步骤s62中,第五介质层162的材料与第五子介质层1621相同,均为氧化硅。

[0084]

作为示例,请参阅图17,步骤s6中还包括:步骤s63:于第二介质层152的表面、第一位线立柱13的顶面形成第三介质层153并于第五介质层162的表面、第二位线立柱14的顶面形成第六介质层163,第六介质层163还包括第六子介质层1631。

[0085]

步骤s64:于第三介质层153的表面、第六介质层163的表面以及第一位线立柱13与第二位线立柱14之间的衬底10表面形成第一隔离层17。

[0086]

在步骤s63中,第六介质层163的材料与第六子介质层1631相同,均为氮化硅。

[0087]

在步骤s64中,第一隔离层17的材料可以为氧化硅。

[0088]

作为示例,请参阅图18,步骤s64之后还可以包括:步骤s65:于第一位线立柱13与第二位线立柱14之间的空隙内形成第二隔离层18,第二隔离层18还覆盖第一位线立柱13与第二位线立柱14的表面,并于第二隔离层18的表面形成第三隔离层19。

[0089]

在步骤s65中,第二隔离层18与第三隔离层19的材料可以为任意绝缘材料中的一种或多种。

[0090]

作为示例,请参阅图19及图20,步骤s63之后还可以包括:步骤s64’:于第一位线立柱13及第二位线立柱14之间的衬底10表面形成电容插塞沟槽20,电容插塞沟槽20的底面高于凹槽的底面,且与有源区101连接。

[0091]

在步骤s64’中,电容插塞沟槽20的形成工艺可以包括干法刻蚀或湿法刻蚀。

[0092]

作为示例,请参阅图3,步骤s64’之后还可以包括:步骤s65’:至少于电容插塞沟槽20内形成电容插塞21,并于电容插塞21的顶面形成电容接触层(未图示)。

[0093]

于上述实施例中的半导体结构及其制备方法中,通过控制第一绝缘层的厚度,即第一预设厚度,来控制第一绝缘层侧壁的垂直程度,同时第一绝缘层的顶面沿第一方向的长度与其底面沿第一方向的长度的差值更小,长度比被控制在第一目标值,第一位线立柱的垂直程度更好、性能更优。另外,第一绝缘层的垂直程度更好,也能够为第一绝缘层的侧壁方向留出更多的空间,使得第一位线侧墙的厚度增大,进而减小寄生电容,并扩大了工艺窗口,进一步提升存储结构的整体性能。本公开还减小了第一位线盖层与第二位线盖层的厚度,以改善位线立柱易倾斜的问题,提高其稳定性。

[0094]

请注意,上述实施例仅出于说明性目的而不意味对本公开的限制。

[0095]

本说明书中的各个实施例均采用递进的方式描述,每个实施例重点说明的都是与其他实施例的不同之处,各个实施例之间相同相似的部分互相参见即可。

[0096]

以上实施例的各技术特征可以进行任意的组合,为使描述简洁,未对上述实施例中的各个技术特征所有可能的组合都进行描述,然而,只要这些技术特征的组合不存在矛盾,都应当认为是本说明书记载的范围。

[0097]

以上实施例仅表达了本公开的几种实施方式,其描述较为具体和详细,但并不能因此而理解为对公开专利范围的限制。应当指出的是,对于本领域的普通技术人员来说,在

不脱离本公开构思的前提下,还可以做出若干变形和改进,这些都属于本公开的保护范围。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。