技术特征:

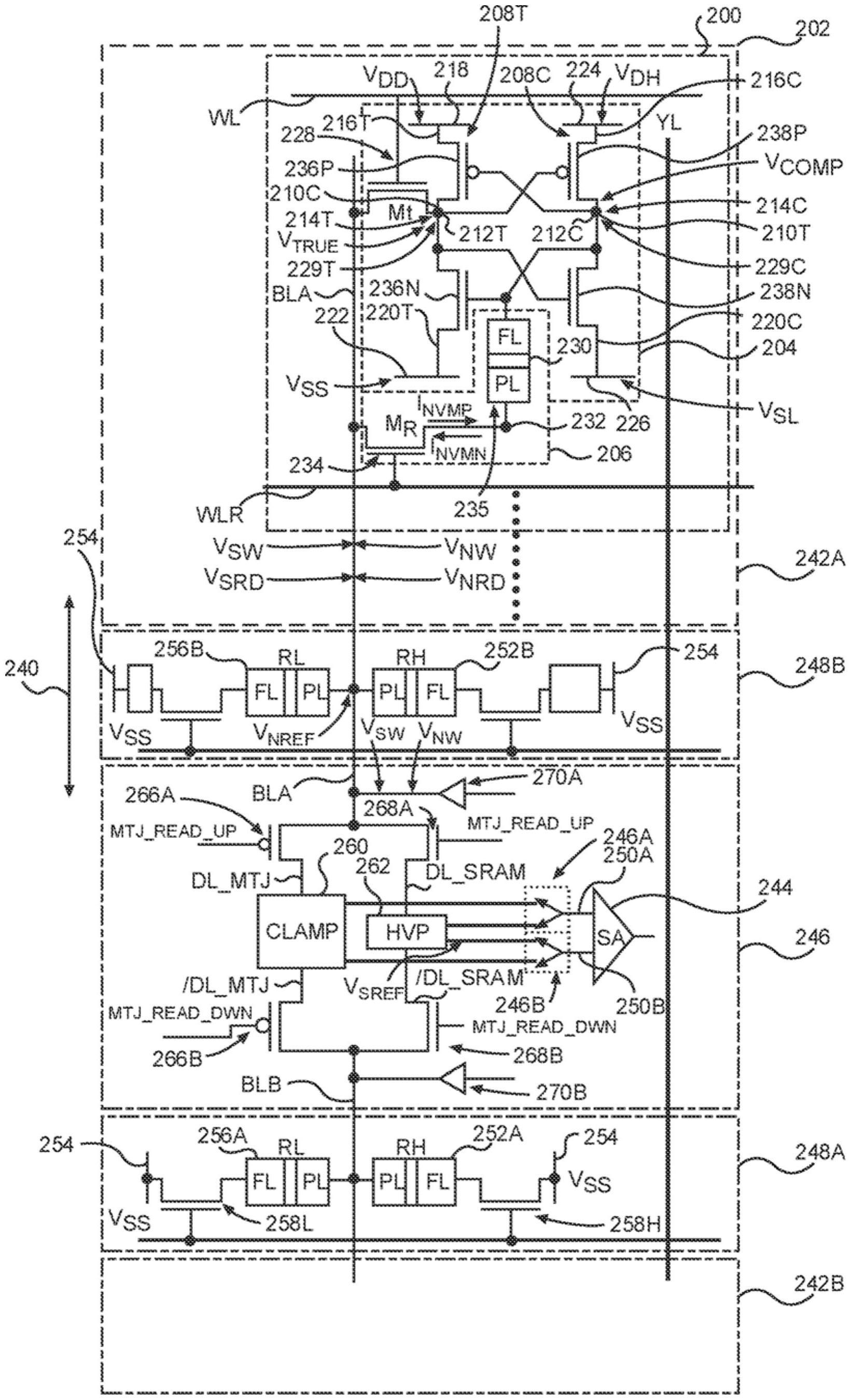

1.一种存储器位单元电路,包括:位线;静态随机存取存储器(sram)位单元电路,包括:存储电路,包括:真反相器电路,包括:真输入节点;真输出节点,包括真存储节点;真功率节点,被耦合到电源电压轨;以及真接地节点,被耦合到接地电压轨;以及互补反相器电路,包括:互补输入节点,被耦合到所述真反相器电路的所述真输出节点;互补输出节点,包括耦合到所述真反相器电路的所述真输入节点的互补存储节点;互补功率节点,被耦合到高电压轨;以及互补接地节点,被耦合到低电压轨;以及第一存取电路,被耦合到所述真输出节点和所述位线;以及非易失性存储器(nvm)位单元电路,包括:nvm器件,被耦合在所述互补输出节点与第一节点之间;以及第二存取电路,被耦合到所述第一节点和所述位线。2.根据权利要求1所述的存储器位单元电路,其中所述sram位单元电路被配置为:响应于所述第一存取电路将所述位线耦合到所述真输出节点并且sram写入电压被提供给所述位线,将真sram数据存储在所述真输出节点上,并且将互补sram数据存储在所述互补输出节点上。3.根据权利要求1所述的存储器位单元电路,其中所述nvm器件是磁性随机存取存储器(mram)器件,所述磁性随机存取存储器(mram)器件被配置为:响应于所述第二存取电路将所述第一节点耦合到所述位线,基于在所述位线与所述互补存储节点之间在第一方向上传导第一电流或在所述位线与所述互补存储节点之间在第二方向上传导第二电流,存储第一二进制nvm数据。4.根据权利要求3所述的存储器位单元电路,其中:所述电源电压轨被配置为接收电源电压;所述接地电压轨被配置为接收接地电压;所述高电压轨被配置为接收比所述电源电压高的电压;所述低电压轨被配置为接收比所述接地电压低的电压;并且响应于所述第二存取电路将所述第一节点耦合到所述位线,所述互补反相器电路被配置为传导所述第一方向上的所述第一电流和所述第二方向上的所述第二电流中的一者通过所述nvm器件。5.一种存储器位单元阵列电路,包括:第一位线;第一多个存储器位单元电路,各自耦合到所述第一位线,每个存储器位单元电路包括:静态随机存取存储器(sram)位单元电路,被配置为:响应于接收到电源电压,将真sram

数据存储在真存储节点上,并且将互补sram数据存储在互补存储节点上,所述sram位单元电路包括耦合到所述真存储节点和所述第一位线的第一存取电路;以及非易失性存储器(nvm)位单元电路,被配置为存储nvm数据,所述nvm位单元电路包括:nvm器件,被耦合到所述sram位单元电路的所述互补存储节点和第一节点;以及第二存取电路,被耦合到所述第一节点和所述第一位线;以及阵列存取电路,被耦合到所述第一位线,所述阵列存取电路被配置为:基于所述第一位线上的第一sram读取电压,确定存储在所述第一多个存储器位单元电路中的存储器位单元电路的所述sram位单元电路中的所述真sram数据;以及基于所述第一位线上的第一nvm读取电压,确定存储在所述第一多个存储器位单元电路中的所述存储器位单元电路的所述nvm位单元电路中的第一nvm数据。6.根据权利要求5所述的存储器位单元阵列电路,所述阵列存取电路还包括耦合到所述第一位线的感测放大器电路,其中:所述感测放大器电路被配置为将所述第一位线上的所述第一sram读取电压与sram参考电压进行比较,所述sram参考电压是介于所述电源电压与接地电压之间的电压;并且所述感测放大器电路还被配置为将所述第一位线上的所述第一nvm读取电压与nvm参考电压进行比较。7.根据权利要求6所述的存储器位单元阵列电路,其中:所述nvm器件被配置为:响应于第一电流而包括高电阻状态,并且响应于第二电流而包括低电阻状态;并且所述存储器位单元电路还包括被配置为提供所述nvm参考电压的nvm参考电路,所述nvm参考电路耦合到第二位线并且包括:第一高电阻(hr)nvm器件,被耦合到所述第二位线和接地电压节点,并且被配置为包括所述高电阻状态;以及第一低电阻(lr)nvm器件,被耦合在所述第二位线与所述接地电压节点之间,并且被配置为包括所述低电阻状态。8.根据权利要求7所述的存储器位单元阵列电路,所述阵列存取电路还包括:所述感测放大器电路,包括第一输入和第二输入;钳位电路,被配置为:响应于所述第一多个存储器位单元电路中的所述存储器位单元电路中的所述nvm位单元电路的读取操作,将所述第一位线耦合到所述感测放大器电路的所述第一输入,并且将所述第二位线耦合到所述感测放大器电路的所述第二输入;以及半v

dd

预充电(hvp)电路,被配置为:响应于所述第一多个存储器位单元电路中的所述存储器位单元电路中的所述sram位单元电路的读取操作,将所述第一位线耦合到所述感测放大器电路的所述第一输入,并且将所述sram参考电压耦合到所述感测放大器电路的所述第二输入。9.根据权利要求8所述的存储器位单元阵列电路,还包括:第二多个存储器位单元电路,被耦合到所述第二位线;以及第二nvm参考电路,被配置为在所述第一位线上提供所述nvm参考电压;其中所述阵列存取电路还被配置为确定存储在所述第二多个存储器位单元电路中的一个存储器位单元电路中的第二nvm数据。

10.根据权利要求9所述的存储器位单元阵列电路,其中:所述第二nvm参考电路包括:第二hr nvm器件,被耦合到所述第一位线和所述接地电压节点,所述第二hr nvm器件被配置为包括所述高电阻状态;以及第二lr nvm器件,被耦合到所述第一位线和所述接地电压节点,所述第二lr nvm器件被配置为包括所述低电阻状态。11.根据权利要求9所述的存储器位单元阵列电路,其中被配置为确定存储在所述第二多个存储器位单元电路中的一个存储器位单元电路中的第二真sram数据的所述阵列存取电路还被配置为:将所述感测放大器电路的所述第二输入上的第二sram读取电压与所述感测放大器电路的所述第一输入上的所述sram参考电压进行比较。12.根据权利要求9所述的存储器位单元阵列电路,所述阵列存取电路还包括:第一写入驱动器,被耦合到所述第一位线;以及第二写入驱动器,被耦合到所述第二位线;其中:所述第一写入驱动器被配置为将第一真sram数据写入到所述第一多个存储器位单元电路中的所述存储器位单元电路的所述sram位单元电路中;并且所述第二写入驱动器被配置为将第二真sram数据写入到所述第二多个存储器位单元电路中的所述一个存储器位单元电路的sram位单元电路中。13.根据权利要求5所述的存储器位单元阵列电路,被集成到射频(rf)前端模块中。14.根据权利要求5所述的存储器位单元阵列电路,被集成到选自由以下各项组成的组的设备中:机顶盒;娱乐单元;导航设备;通信设备;固定位置数据单元;移动位置数据单元;全球定位系统(gps)设备;移动电话;蜂窝电话;智能电话;会话发起协议(sip)电话;平板电脑;平板手机;服务器;计算机;便携式计算机;移动计算设备;可穿戴计算设备;台式计算机;个人数字助理(pda);显示器;计算机显示器;电视;调谐器;收音机;卫星收音机;音乐播放器;数字音乐播放器;便携式音乐播放器;数字视频播放器;视频播放器;数字视频盘(dvd)播放器;便携式数字视频播放器;汽车;车辆组件;以及商用无人机。15.一种在存储器位单元阵列电路中访问存储器位单元电路中存储的数据的方法,包括:通过阵列存取电路,基于第一位线上的电压,访问静态随机存取存储器(sram)位单元电路中的真sram数据和非易失性存储器(nvm)位单元电路中的nvm数据中的一者。16.根据权利要求15所述的方法,其中所述存储器位单元阵列电路包括:第一多个存储器位单元电路,各自耦合到所述第一位线,每个存储器位单元电路包括:sram位单元电路,被配置为:响应于接收到电源电压,将真sram数据存储在真存储节点上,并且将互补sram数据存储在互补存储节点上;以及nvm位单元电路,被配置为存储nvm数据;并且所述阵列存取电路,被耦合到所述第一位线。17.根据权利要求16所述的方法,其中访问所述sram位单元电路中的所述真sram数据和所述nvm位单元电路中的所述nvm数据中的所述一者还包括:在sram写入操作中,基于所述第一位线上的sram写入数据电压,将所述真sram数据存储在所述存储器位单元电路的所

述sram位单元电路的所述真存储节点上,并且将所述互补sram数据存储在所述存储器位单元电路的所述sram位单元电路的所述互补存储节点上。18.根据权利要求17所述的方法,其中:所述阵列存取电路还包括耦合到所述第一位线的第一写入驱动器;以及将所述真sram数据存储在所述存储器位单元电路的所述sram位单元电路的所述真存储节点上还包括:通过所述第一写入驱动器,向所述第一位线提供所述sram写入数据电压。19.根据权利要求16所述的方法,其中访问所述存储器位单元电路中存储的数据还包括:在sram读取操作中,基于所述第一位线上的第一sram读取电压,确定存储在所述存储器位单元电路的所述sram位单元电路的所述真存储节点上的所述真sram数据。20.根据权利要求19所述的方法,其中:所述阵列存取电路还包括:感测放大器电路,包括第一输入和第二输入;以及半v

dd

预充电(hvp)电路,将所述第一位线耦合到所述感测放大器电路的所述第一输入,并且将sram参考电压提供给所述感测放大器电路的所述第二输入;以及确定存储在所述存储器位单元电路的所述sram位单元电路的所述真存储节点上的所述真sram数据还包括:通过所述hvp电路,将所述第一位线预充电到所述电源电压的一半;激活第一存取电路,以将所述sram位单元电路的所述真存储节点耦合到所述第一位线,从而将与所述真sram数据相对应的所述第一sram读取电压提供给所述第一位线;以及通过所述感测放大器电路,将所述感测放大器电路的所述第一输入上的所述第一sram读取电压与所述感测放大器电路的所述第二输入上的所述sram参考电压进行比较。21.根据权利要求16所述的方法,其中在nvm写入操作中,访问所述sram位单元电路中的所述真sram数据和所述nvm位单元电路中的所述nvm数据中的所述一者还包括:基于所述第一位线上的第一nvm写入电压,将所述nvm数据存储在所述存储器位单元电路的所述nvm位单元电路中。22.根据权利要求21所述的方法,其中:所述阵列存取电路还包括耦合到所述第一位线的第一写入驱动器;所述sram位单元电路还包括真反相器电路,所述真反相器电路与包括所述互补存储节点的互补反相器电路交叉耦合;所述nvm位单元电路还包括:nvm器件,被耦合到所述sram位单元电路的所述互补存储节点以及第一节点;以及第二存取电路,被耦合到所述第一节点和所述第一位线;以及将所述nvm数据存储在所述nvm位单元电路中还包括:将所述电源电压和接地电压提供给所述真反相器电路;将比所述电源电压高的较高电压和比所述接地电压低的较低电压提供给所述互补反相器电路;通过所述第一写入驱动器,将所述第一nvm写入电压提供给所述第一位线;以及激活所述第二存取电路,以将所述第一位线耦合到所述第一节点。23.根据权利要求22所述的方法,其中将所述nvm数据存储在所述nvm位单元电路中还

包括:将与所述nvm数据相对应的所述互补sram数据存储在所述sram位单元电路的所述互补存储节点上。24.根据权利要求16所述的方法,其中访问所述sram位单元电路中的所述真sram数据和所述nvm位单元电路中的所述nvm数据中的所述一者还包括:响应于nvm读取操作,基于所述第一位线上的第一nvm读取电压,确定存储在所述存储器位单元电路的所述nvm位单元电路中的所述nvm数据。25.根据权利要求24所述的方法,其中确定存储在所述nvm位单元电路中的所述nvm数据还包括:将所述第一位线上的所述第一nvm读取电压与第一参考电压进行比较。26.根据权利要求16所述的方法,其中:所述存储器位单元阵列电路还包括:第二位线,被耦合到所述阵列存取电路;以及nvm参考电路,被耦合到所述第二位线,所述nvm参考电路被配置为提供nvm参考电压;所述nvm位单元电路还包括:nvm器件,被耦合到所述sram位单元电路的所述互补存储节点以及第一节点;以及存取电路,被耦合到所述第一节点和所述第一位线;所述阵列存取电路还包括:感测放大器电路,包括第一输入和第二输入;以及钳位电路,被耦合到所述第一位线、所述第二位线、所述感测放大器电路的所述第一输入和所述感测放大器电路的所述第二输入;以及确定存储在所述nvm位单元电路中的所述nvm数据包括:通过所述钳位电路,将小于所述电源电压的中间电压提供给所述第一位线;通过所述钳位电路,将所述第二位线上的所述中间电压提供给所述nvm参考电路以生成所述nvm参考电压;激活所述存取电路,以将所述nvm器件耦合到所述第一位线以将基于所述nvm数据的第一nvm读取电压提供给所述第一位线;通过所述钳位电路,将所述第一位线耦合到所述感测放大器电路的所述第一输入,并且将所述第二位线耦合到所述感测放大器电路的所述第二输入;以及通过所述感测放大器电路,将所述第一输入上的所述第一nvm读取电压与所述第二输入上的所述nvm参考电压进行比较。27.一种操作存储器位单元阵列电路的方法,包括:响应于激活静态随机存取存储器(sram)位单元电路中的电源电压,驱动第一电流通过第一多个存储器位单元电路中的每个存储器位单元电路的非易失性存储器(nvm)位单元电路,以将所述nvm位单元电路设置为第一电阻状态;以及响应于所述电源电压的去激活的指示:对于所述第一多个存储器位单元电路中的每个存储器位单元电路:读取所述sram位单元电路的真存储节点上的真sram数据;响应于确定所述sram位单元电路中的所述真sram数据对应于所述nvm位单元电路的第二电阻状态,驱动第二电流通过所述nvm位单元电路,以将所述nvm位单元电路设置为所述第二电阻态;以及

响应于确定所述sram位单元电路中的所述真sram数据对应于所述nvm位单元电路的所述第一电阻状态,使所述nvm位单元电路留在所述第一电阻状态,其中在所述第一多个存储器位单元电路中,每个存储器位单元电路包括:所述sram位单元电路,被配置为:响应于接收到所述电源电压,将所述真sram数据存储在所述真存储节点上,并且将互补sram数据存储在互补存储节点上;并且所述nvm位单元电路被配置为独立于所述sram位单元电路接收所述电源电压而存储nvm数据。

技术总结

公开了一种被包括在存储器位单元阵列电路中的示例性存储器位单元电路,该存储器位单元电路包括耦合到SRAM位单元电路和NVM位单元电路的位线,SRAM位单元电路和NVM位单元电路具有减小的面积和减小的功耗。SRAM位单元电路包括交叉耦合的真反相器和互补反相器以及耦合到位线的第一存取电路。NVM位单元电路包括通过第二存取电路耦合到位线的NVM器件,并且耦合到SRAM位单元电路。存储在SRAM位单元电路和NVM位单元电路中的数据基于位线上的电压而被访问。真SRAM数据根据位线上的SRAM读取电压来确定,并且NVM位单元电路中的NVM数据根据位线上的第一NVM读取电压来确定。线上的第一NVM读取电压来确定。线上的第一NVM读取电压来确定。

技术研发人员:K

受保护的技术使用者:高通股份有限公司

技术研发日:2021.09.30

技术公布日:2023/8/5

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。