1.本说明书的技术领域涉及半导体元件以及装置。

背景技术:

2.以gan为代表的iii族氮化物半导体具备高的击穿电场和高熔点。因此,iii族氮化物半导体有望作为代替gaas系半导体的高输出、高频、高温用的半导体器件的材料。因此,正在研究开发使用iii族氮化物半导体的hemt元件等。

3.例如,在专利文献1中,公开了一种通过极化结使电子及空穴同时产生的技术(参照专利文献1的图4等)。另外,在专利文献2中,公开了一种依次形成gan层、algan层、gan层、p型gan层的技术(专利文献2的第[0034]段)。由此,公开了一种将p型gan层的价带的上端的能量ev提高至费米能级ef,产生二维空穴气的技术。

[0004]

专利文献1:日本特开2007-134607号公报

[0005]

专利文献2:wo2011/162243

[0006]

半导体元件一般要求优异的电气特性。作为这样的电气特性,例如,可举出高的耐压性、低的导通电阻、短的响应时间、对大电流的应对性、漏电流的抑制。

技术实现要素:

[0007]

本说明书的技术要解决的课题是提供耐压性优异的半导体元件以及装置。

[0008]

第一方式的半导体元件具有:第一半导体层;比第一半导体层靠上层的第二半导体层;比第二半导体层靠上层的第三半导体层;比第三半导体层靠上层的第四半导体层;第二半导体层或第三半导体层之上的源极电极及漏极电极;第四半导体层之上的栅极电极;栅极电极与第四半导体层接触的栅极电极接触区域;源极电极与第二半导体层或第三半导体层接触的源极电极接触区域;漏极电极与第二半导体层或第三半导体层接触的漏极电极接触区域;以及从第四半导体层到达第二半导体层的第一凹部及第二凹部。第一半导体层、第二半导体层、第三半导体层及第四半导体层为iii族氮化物半导体层。第二半导体层的带隙大于第一半导体层及第三半导体层的带隙。第一半导体层、第二半导体层及第三半导体层为未掺杂的半导体层。第四半导体层为p型半导体层。源极电极形成在第一凹部之上。漏极电极形成在第二凹部之上。漏极电极接触区域与第三半导体层之间的距离大于源极电极接触区域与第三半导体层之间的距离。

[0009]

在该半导体元件中,漏极电极接触区域与第三半导体层之间的距离大于源极电极接触区域与第三半导体层之间的距离。缓和了在漏极电极接触区域与第三半导体层之间产生的电场。因此,该半导体元件具有优异的耐压性。

[0010]

在本说明书中,提供至少一个以上的电气特性优异的半导体元件以及装置。

附图说明

[0011]

图1是第一实施方式的半导体元件的俯视图。

[0012]

图2是表示第一实施方式的半导体元件的层叠构造的图。

[0013]

图3是表示第一实施方式的半导体元件的元件功能区域的电极的接触区域的图。

[0014]

图4是第一实施方式的半导体元件的源极接触电极及漏极接触电极的周边的放大图。

[0015]

图5是表示第一实施方式的半导体元件的源极电极露出区域的周边的截面构造的图(其1)。

[0016]

图6是表示第一实施方式的半导体元件的漏极电极露出区域的周边的截面构造的图。

[0017]

图7是表示第一实施方式的半导体元件的栅极电极露出区域的周边的截面构造的图。

[0018]

图8是表示第一实施方式的半导体元件的源极电极露出区域的周边的截面构造的图(其2)。

[0019]

图9是表示第一实施方式的半导体元件的源极电极接触区域及漏极电极接触区域与绝缘层之间的位置关系的图。

[0020]

图10是表示第一实施方式的半导体元件的栅极电极的配线的图。

[0021]

图11是表示第一实施方式的半导体元件的源极电极的配线的图。

[0022]

图12是表示第一实施方式的半导体元件的源极电极及漏极电极的层叠构造的图。

[0023]

图13是表示第一实施方式的半导体元件的栅极电极的层叠构造的图。

[0024]

图14是表示第一实施方式的半导体元件的二维电子气及二维空穴气的图。

[0025]

图15是表示第一实施方式的半导体元件的带构造的图。

[0026]

图16是示意性地表示对第一实施方式的半导体元件的栅极电极施加了反偏压的情况下的电场的示意图。

[0027]

图17是用于对第一实施方式的半导体元件的制造方法进行说明的图(其1)。

[0028]

图18是用于对第一实施方式的半导体元件的制造方法进行说明的图(其2)。

[0029]

图19是用于对第一实施方式的半导体元件的制造方法进行说明的图(其3)。

[0030]

图20是第二实施方式的半导体元件的俯视图。

[0031]

图21是表示第三实施方式的半导体元件的层叠构造的图。

[0032]

图22是表示第四实施方式的半导体元件的栅极焊盘电极的周边的图。

[0033]

图23是表示第四实施方式的半导体元件的漏极电极露出区域的周边的截面构造的图。

34.图24是第四实施方式的变形例中的半导体元件的俯视图。

[0035]

图25是第四实施方式的变形例中的半导体元件中的栅极焊盘电极的周边的放大图。

[0036]

图26是表示第八实施方式的半导体元件的层叠构造的图。

[0037]

图27是表示第八实施方式的半导体元件的电极形成区域的图。

[0038]

图28是表示第八实施方式的变形例中的半导体元件的电极形成区域的图。

[0039]

图29是表示第八实施方式的变形例中的半导体元件的层叠构造的图(其1)。

[0040]

图30是表示第八实施方式的变形例中的半导体元件的层叠构造的图(其2)。

[0041]

图31是表示第八实施方式的变形例中的半导体元件的层叠构造的图(其3)。

[0042]

图32是表示栅极电极接触区域gc1包围源极电极接触区域sc1的情况下的fet的图。

[0043]

图33是表示栅极电极接触区域gc1处于源极电极接触区域sc1与漏极电极接触区域dc1之间的情况下的fet的图。

[0044]

图34是表示对fet的漏极电极施加了0.1v时的栅极电压和漏极电流之间的关系的图表。

[0045]

图35是表示fet的栅极电压和漏极电流之间的关系的图表。

[0046]

图36是表示fet的漏极电压和漏极电流之间的关系的图表。

[0047]

图37是表示fet中的关断时的漏极电压和漏极电流之间的关系的图表。

[0048]

图38是表示fet中的关断时的漏极电压和栅极电流之间的关系的图表。

[0049]

图39是在fet的评价中使用的电路图。

[0050]

图40是表示fet的评价中的输出值的图表。

[0051]

图41是表示fet的上升时间tr及下降时间tf的定义的图。

[0052]

图42是表示fet的特性的表。

[0053]

图43是表示fet中的第二未掺杂gan层(第三半导体层)与mg掺杂pgan层(第四半导体层)的接合面积和半导体元件的耐压之间的关系的图表。

[0054]

图44是表示fet的栅极长度和响应时间之间的关系的图表。

[0055]

图45是表示fet中的除极化超结区域psj1以外的第三半导体层与第四半导体层的接合面积和响应时间之间的关系的图表。

[0056]

图46是表示fet中的位错密度和接合面积之间的关系的图表。

[0057]

图47是汇总了图46的数据的表。

[0058]

图48是表示fet中的位错密度和源极漏极间距离之间的关系的图表。

[0059]

图49是汇总了图48的数据的表。

[0060]

图50是表示fet中的位错密度和响应时间之间的关系的图表。

[0061]

图51是汇总了图50的数据的表。

[0062]

图52是表示fet中的极化超结长度lpsj和标准化导通电阻之间的关系的图表。

[0063]

图53是表示fet中的源极漏极间距离和标准化导通电阻之间的关系的图表。

[0064]

图54是表示fet中的位错密度和半导体元件的特性之间的关系的表。

[0065]

图55是表示fet的芯片尺寸和漏极电压vd为2v时的电流值之间的关系的表。

[0066]

图56是表示fet的有源区域面积和漏极电压vd为2v时的电流值之间的关系的图表。

[0067]

图57是表示改变了fet中的极化超结长度lpsj和源极接触电极s1c与漏极接触电极d1c之间的距离lsd时的fet的耐压性的表。

[0068]

图58是表示未改变fet中的极化超结长度lpsj、和源极接触电极s1c与漏极接触电极d1c之间的距离lsd时的fet的耐压性的表。

[0069]

图59是表示fet中的极化超结长度lpsj与fet的耐压性之间的关系的图表。

[0070]

图60是表示fet中的漏极电极接触区域dc1和极化超结面之间的距离与耐压性之间的关系的图表。

[0071]

图61是表示fet中的极化超结长度lpsj和半导体元件的耐压性之间的关系的图

表。

[0072]

图62是表示fet的漏极电压和漏极电流之间的关系的图表。

[0073]

图63是表示fet的漏极电压为0.1v时的栅极电压和漏极电流之间的关系的图表。

[0074]

图64是表示fet的关断时的漏极电压和漏极电流之间的关系的图表。

[0075]

图65是表示fet的关断时的漏极电压和栅极电流之间的关系的图表。

[0076]

图66是表示极化超结长度lpsj为20μm的肖特基势垒二极管的反向恢复时间特性的图表。

[0077]

图67是表示肖特基势垒二极管的正向特性的图表。

[0078]

图68是表示肖特基势垒二极管的反向特性的图表。

[0079]

图69是表示改变了极化超结长度lpsj和阳极电极接触区域ac1与阴极电极接触区域cc1之间的距离lac时的肖特基势垒二极管的耐压性的表。

具体实施方式

[0080]

以下,举半导体元件及其制造方法以及装置为例,对具体实施方式进行说明。但是,本说明书的技术并不限定于这些实施方式。在本说明书中,未掺杂的半导体层是指未有意地掺入杂质的半导体层。附图中的各层的厚度之比不一定反映实际的厚度之比。

[0081]

(第一实施方式)

[0082]

1.半导体元件的构造

[0083]

1-1.半导体元件的区域

[0084]

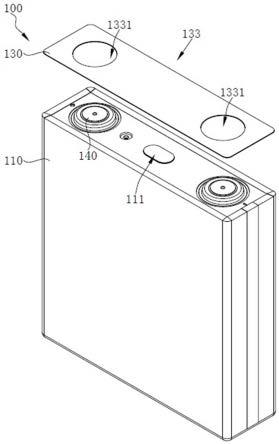

图1是第一实施方式的半导体元件100的俯视图。半导体元件100为场效应晶体管(field effect transistor:fet)。如图1所示,半导体元件100具有元件功能区域fr1、源极电极露出区域sr1、漏极电极露出区域dr1及栅极电极露出区域gr1、gr2。

[0085]

元件功能区域fr1是发挥作为元件的功能的区域。如后述那样,元件功能区域fr1为电流实际流过半导体的区域。元件功能区域fr1被聚酰亚胺等绝缘体覆盖。因此,在元件功能区域fr1中,半导体或金属不露出。

[0086]

源极电极露出区域sr1是源极电极露出的区域。源极电极露出区域sr1是用于与外部电极电连接的焊盘电极露出的区域。源极电极露出区域sr1具有端部sr1a、端部sr1b及中央部sr1c。端部sr1a及端部sr1b在元件功能区域fr1侧向远离中央部sr1c的方向延伸。随着接近元件功能区域fr1及漏极电极露出区域dr1,源极电极露出区域sr1扩大。

[0087]

漏极电极露出区域dr1是漏极电极露出的区域。漏极电极露出区域dr1是用于与外部电极电连接的焊盘电极露出的区域。

[0088]

栅极电极露出区域gr1、gr2是栅极电极露出的区域。栅极电极露出区域gr1、gr2是用于与外部电极电连接的焊盘电极露出的区域。

[0089]

源极电极露出区域sr1、漏极电极露出区域dr1及栅极电极露出区域gr1、gr2隔着绝缘层而形成在半导体之上。因此,在上述的源极电极露出区域sr1、漏极电极露出区域dr1及栅极电极露出区域gri、gr2中,源极电极、漏极电极及栅极电极不与半导体接触。

[0090]

源极电极露出区域sr1以将元件功能区域fr1夹在中间的状态与漏极电极露出区域dr1对置配置。将源极电极露出区域sr1与栅极电极露出区域gr1、gr2合起来的区域配置成带状。漏极电极露出区域dr1配置成带状。

[0091]

栅极电极露出区域gr1、gr2形成在源极电极露出区域sr1侧。栅极电极露出区域gr1、gr2以将元件功能区域fr1夹在中间的状态与漏极电极露出区域dr1对置配置。在栅极电极露出区域gr1与栅极电极露出区域gr2之间配置有源极电极露出区域sr1。栅极电极露出区域gr1面对着源极电极露出区域sr1的端部sr1a及中央部sr1c。栅极电极露出区域gr2面对着源极电极露出区域sr1的端部sr1b及中央部sr1c。

[0092]

源极电极露出区域sr1的端部sr1a位于栅极电极露出区域gr1与元件功能区域fr1之间。源极电极露出区域sr1的端部sr1b位于栅极电极露出区域gr2与元件功能区域fr1之间。在面对元件功能区域fr1的位置,源极电极露出区域sr1的宽度与漏极电极露出区域dr1的宽度几乎相等。

[0093]

1-2.元件功能区域

[0094]

1-2-1.截面构造

[0095]

图2是表示第一实施方式的半导体元件100的层叠构造的图。图2是表示图1的ii-ii截面的图。如图2所示,半导体元件100具有蓝宝石基板sub1、缓冲层bf1、第一半导体层110、第二半导体层120、第三半导体层130、第四半导体层140、源极电极s1、漏极电极d1、栅极电极g1及聚酰亚胺层pi1。

[0096]

蓝宝石基板sub1是支承半导体层的支承基板。蓝宝石基板sub1例如也可以是供半导体层从 c面生长的生长基板。蓝宝石基板sub1的厚度例如为50μm以上且500μm以下。

[0097]

缓冲层bf1形成在蓝宝石基板sub1之上。缓冲层bf1例如是低温gan缓冲层。缓冲层bf1例如也可以是低温aln缓冲层。缓冲层bf1的膜厚例如为20nm以上且50nm以下。

[0098]

第一半导体层110形成在比缓冲层bf1靠上层。第一半导体层110例如是gan层。第一半导体层110未有意地掺入杂质。第一半导体层110的膜厚例如为300nm以上且5000nm以下。

[0099]

第二半导体层120形成在比第一半导体层110靠上层。第二半导体层120与第一半导体层110直接接触。第二半导体层120例如是algan层。第二半导体层120的al组成例如是0.1以上且0.5以下。第二半导体层120的带隙大于第一半导体层110及第三半导体层130的带隙。第二半导体层120未有意地掺入杂质。第二半导体层120的膜厚例如为20nm以上且150nm以下。

[0100]

第三半导体层130形成在比第二半导体层120靠上层。第三半导体层130与第二半导体层120直接接触。第三半导体层130例如是gan层。第三半导体层130未有意地掺入杂质。第三半导体层130被凹部x1和凹部x2夹着而划分。另外,第三半导体层130包围源极电极s1的形成区域亦即凹部x1的周围。第三半导体层130的膜厚例如为20nm以上且150nm以下。

[0101]

第四半导体层140形成在比第三半导体层130靠上层。第四半导体层140与第三半导体层130直接接触。第四半导体层140例如是p型gan层。第四半导体层140被掺杂了p型杂质。p型杂质例如为mg。第四半导体层140的杂质浓度例如为1

×

10

17

cm-3

以上且3

×

10

20

cm-3

以下。越靠近栅极电极g1,第四半导体层140的杂质浓度越高。第四半导体层140的膜厚例如为20nm以上且150nm以下。

[0102]

源极电极s1形成在第二半导体层120之上。源极电极s1与第二半导体层120直接接触。在源极电极s1的形成部位形成有凹部x1。凹部x1从第四半导体层140到达第二半导体层120的中途。第二半导体层120在凹部x1的底部露出。源极电极s1形成在凹部x1之上。

[0103]

漏极电极d1形成在第二半导体层120之上。漏极电极d1与第二半导体层120直接接触。在漏极电极d1的形成部位形成有凹部x2。凹部x2从第四半导体层140到达第二半导体层120的中途。第二半导体层120在凹部x2的底部露出。漏极电极d1形成在凹部x2之上。

[0104]

栅极电极g1形成在第四半导体层140之上。栅极电极g1与第四半导体层140直接接触。

[0105]

聚酰亚胺层pi1覆盖半导体层的表面。另外,聚酰亚胺层pi1覆盖元件功能区域fr1的各电极。

[0106]

像这样,第一半导体层110、第二半导体层120、第三半导体层130及第四半导体层140为iii族氮化物半导体层。第一半导体层110、第二半导体层120及第三半导体层130为未掺杂的半导体层。第四半导体层140为p型半导体层。

[0107]

第三半导体层130具有凹部x3和与第四半导体层140接触的区域。凹部x3从第四半导体层140到达第三半导体层130的中途。凹部x3中的第三半导体层130的膜厚比与第四半导体层140接触的第三半导体层130的膜厚薄。

[0108]

凹部x1与凹部x2不相连。如后述那样,凹部x1为棒状形状,凹部x2为梳齿形状。而且,在凹部x1与凹部x2之间配置有第三半导体层130。

[0109]

1-2-2.平面构造

[0110]

图3是表示第一实施方式的半导体元件100的元件功能区域fr1的电极的接触区域的图。在图3中,示出将元件功能区域fr1中的电极的接触区域投影到第二半导体层120的情况下的区域。半导体元件100具有源极电极接触区域sc1、漏极电极接触区域dc1及栅极电极接触区域gc1。

[0111]

源极电极接触区域sc1为源极电极s1与第二半导体层120接触的区域。漏极电极接触区域dc1为漏极电极d1与第二半导体层120接触的区域。栅极电极接触区域gc1为栅极电极g1与第四半导体层140接触的区域。

[0112]

源极电极接触区域sc1例如为第一电极接触区域。漏极电极接触区域dc1例如为第二电极接触区域。栅极电极接触区域gc1例如为第三电极接触区域。

[0113]

对于源极电极接触区域sc1、漏极电极接触区域dc1及栅极电极接触区域gc1而言,在投影到蓝宝石基板sub1、第一半导体层110及第二半导体层120中的任一个的情况下,均相互不重叠。

[0114]

源极电极接触区域sc1具有棒状形状。栅极电极接触区域gc1非接触地包围源极电极接触区域sc1的周围。严格来说,栅极电极接触区域gc1处于第四半导体层140之上,源极电极接触区域sc1处于第二半导体层120之上。

[0115]

将栅极电极g1与第四半导体层140接触的栅极电极接触区域gc1投影到第二半导体层120而得的区域非接触地包围源极电极s1与第二半导体层120接触的源极电极接触区域sc1的周围。在将栅极电极接触区域gc1及源极电极接触区域sc1投影到蓝宝石基板sub1或第一半导体层110的情况下,栅极电极接触区域gc1非接触地包围源极电极接触区域sc1的周围。

[0116]

漏极电极接触区域dc1具有梳齿形状。源极电极接触区域sc1及栅极电极接触区域gc1以被夹在漏极电极接触区域dc1的梳齿与梳齿之间的位置的状态配置。即,源极电极接触区域sc1的棒状形状配置在漏极电极接触区域dc1的梳齿形状之间。

[0117]

第一半导体层110与第二半导体层120接触的接触面的形状为长方形。将源极电极接触区域sc1的棒状形状投影到该接触面而得的区域的长度方向配置为与该长方形的短边平行的方向。如图2及图3所示,在与源极电极接触区域sc1的棒状形状的长度方向垂直的截面中,源极电极接触区域sc1与漏极电极接触区域dc1交替配置。

[0118]

如图3所示,源极接触电极s1c具有前端部分的弧状部s1c1和前端部分以外的棒状部s1c2。源极接触电极s1c的棒状部s1c2被夹在弧状部s1c1与弧状部s1c1之间。

[0119]

漏极接触电极d1c具有前端部分的弧状部d1c1和前端部分以外的棒状部d1c2。漏极接触电极d1c的棒状部d1c2未被夹在弧状部d1c1与弧状部d1c1之间。

[0120]

栅极接触电极g1c具有前端部分的弧状部g1c1和前端部分以外的带状部g1c2。栅极接触电极g1c的弧状部g1c1位于带状部g1c2与带状部g1c2之间。栅极接触电极g1c的弧状部g1c1及带状部g1c2为环状形状。

[0121]

如图1所示,源极电极接触区域sc1的棒状部分的数量比漏极电极接触区域dc1的梳齿形状的棒状部分的数量多1条。像这样,位于半导体元件100的最外侧的电极接触区域是源极电极接触区域sc1,而不是漏极电极接触区域dc1。

[0122]

图4是表示第一实施方式的半导体元件100的源极接触电极s1c及漏极接触电极d1c的周边的放大图。

[0123]

1-2-3.极化超结区域

[0124]

如图2所示,半导体元件100具有极化超结区域psj1。极化超结区域psj1为具有第一半导体层110、第二半导体层120及第三半导体层130而不具有第四半导体层140的区域。即,极化超结区域psj1是形成有第三半导体层130并且未形成有第四半导体层140的区域中的位于栅极电极接触区域gc1与漏极电极接触区域dc1之间的区域。

[0125]

像这样,极化超结区域psj1不具有p型半导体层。极化超结区域psj1位于被栅极电极接触区域gc1与漏极电极接触区域dc1夹着的区域。极化超结长度lpsj为连接从源极电极接触区域sc1至漏极电极接触区域dc1的最短距离的方向上的极化超结区域psj1的长度。

[0126]

1-3.源极电极露出区域

[0127]

图5是表示第一实施方式的半导体元件100的源极电极露出区域sr1的周边的截面构造的图(其1)。图5是表示图1的v-v截面的图。如图5所示,在第一半导体层110之上形成有绝缘层il1。而且,在绝缘层il1之上形成有源极电极s1。另外,在栅极电极g1的栅极配线电极g1w与源极电极s1的源极配线电极s1w之间形成有聚酰亚胺层pi1。聚酰亚胺层pi1将栅极电极g1与源极电极s1绝缘。在源极电极露出区域sr1中,源极电极s1与半导体未电连接。

[0128]

在第一半导体层110中,沿着源极电极露出区域sr1的至少一部分形成有槽u1。由于具有槽u1,因此能够将第一半导体层110与源极电极s1之间的距离取得大。即,提高了第一半导体层110与源极电极s1之间的绝缘性。

[0129]

源极电极s1具有源极接触电极s1c、源极配线电极s1w及源极焊盘电极s1p。源极接触电极s1c与第二半导体层120直接接触。源极配线电极s1w连结源极接触电极s1c与源极焊盘电极s1p。源极焊盘电极s1p是用于与外部电源电连接的电极。

[0130]

1-4.漏极电极露出区域

[0131]

图6是表示第一实施方式的半导体元件100的漏极电极露出区域dr1的周边的截面构造的图。图6是表示图1的vi-vi截面的图。如图6所示,在第一半导体层110之上形成有绝

缘层il1。而且,在绝缘层il1之上形成有漏极电极d1。另外,聚酰亚胺层pi1填埋漏极电极d1与绝缘层il1之间的间隙。在漏极电极露出区域dr1中,漏极电极d1与半导体未电连接。

[0132]

在第一半导体层110中,沿着漏极电极露出区域dr1的至少一部分形成有槽u2。由于具有槽u2,因此能够将第一半导体层110与漏极电极d1之间的距离取得大。即,提高了第一半导体层110与漏极电极d1之间的绝缘性。

[0133]

漏极电极d1具有漏极接触电极d1c、漏极配线电极d1w及漏极焊盘电极d1p。漏极接触电极d1c与第二半导体层120直接接触。漏极配线电极d1w连结漏极接触电极d1c与漏极焊盘电极d1p。漏极焊盘电极d1p为用于与外部电源电连接的电极。

[0134]

1-5.栅极电极露出区域

[0135]

图7是表示第一实施方式的半导体元件100的栅极电极露出区域gr1的周边的截面构造的图。图7是表示图1的vii-vii截面的图。如图7所示,在第一半导体层110之上形成有绝缘层il1。而且,在绝缘层il1之上形成有栅极电极g1。在栅极电极露出区域gr1中,栅极电极g1与半导体未电连接。

[0136]

栅极电极g1具有栅极接触电极g1c、栅极配线电极g1w及栅极焊盘电极g1p。栅极接触电极g1c与第四半导体层140直接接触。栅极配线电极g1w连结栅极接触电极g1c与栅极焊盘电极g1p。栅极焊盘电极g1p为用于与外部电源电连接的电极。

[0137]

1-6.绝缘膜的形成区域

[0138]

图8是表示第一实施方式的半导体元件100的源极电极露出区域sr1的周边的截面构造的图(其2)。图8是表示图1的viii-viii截面的图。如图8所示,漏极电极d1的漏极接触电极d1c向源极焊盘电极s1p侧延伸。在漏极电极d1的漏极接触电极d1c向源极焊盘电极s1p侧延伸的延长线上,绝缘层il1不与第一半导体层110及第二半导体层120接触。不过,绝缘层il1形成在第一半导体层110之上,在槽u1的底部与第一半导体层110接触。

[0139]

图9是表示第一实施方式的半导体元件100的源极电极接触区域sc1及漏极电极接触区域dc1与绝缘层il1之间的位置关系的图。图9是提取绝缘层il1与源极电极接触区域sc1及漏极电极接触区域dc1而绘制的俯视图。

[0140]

如图9所示,绝缘层il1具有朝向源极电极接触区域sc1及栅极电极接触区域gc1突出的突出部il1a。如图5所示,突出部il1a配置于栅极配线电极g1w与第一半导体层110之间的位置中的源极电极接触区域sc1的长度方向的延长线上的位置。

[0141]

如图5及图9所示,绝缘层il1在突出部il1a的位置与第二半导体层120接触。如图8及图9所示,绝缘层il1在突出部il1a以外的位置不与第二半导体层120接触。如图5所示,绝缘层il1的突出部il1a与第二半导体层120、第三半导体层130、第四半导体层140、栅极接触电极g1c及栅极配线电极g1w接触。

[0142]

1-7.电极的配线构造

[0143]

图10是表示第一实施方式的半导体元件100的栅极电极g1的配线的图。栅极电极接触区域gc1的栅极电极g1与栅极配线电极gw2连结。栅极配线电极gw2沿与源极电极接触区域sc1的长度方向平行的方向形成。栅极配线电极gw1经由栅极配线电极gw2而与多个栅极接触电极g1c电连接。栅极配线电极gw1及栅极配线电极gw2是栅极配线电极g1w的一部分。

[0144]

图11是表示第一实施方式的半导体元件100的源极电极s1的配线的图。源极接触

电极s1c与源极配线电极sw2连结。源极配线电极sw2沿与源极电极接触区域sc1的长度方向平行的方向形成。源极配线电极sw1经由源极配线电极sw2而与多个源极接触电极s1c电连接。源极配线电极sw1及源极配线电极sw2为源极配线电极s1w的一部分。

[0145]

如图11所示,将源极电极s1的源极配线电极s1w投影到第二半导体层120而得的区域不与将漏极电极d1的漏极配线电极d1w投影到第二半导体层120而得的区域重叠。

[0146]

如图10及图11所示,将源极配线电极sw2投影到第二半导体层120而得的区域与将栅极配线电极gw2投影到第二半导体层120而得的区域重叠。

[0147]

将源极电极s1的源极配线电极s1w投影到第二半导体层120而得的区域与将栅极电极g1的栅极配线电极g1w投影到第二半导体层120而得的区域部分地重叠。将漏极电极d1的漏极配线电极d1w投影到第二半导体层120而得的区域不与将栅极电极g1的栅极配线电极g1w投影到第二半导体层120而得的区域重叠。

[0148]

1-8.电极的层叠构造

[0149]

1-8-1.源极电极及漏极电极

[0150]

如上述那样,源极电极s1及漏极电极d1形成在第二半导体层120之上。在第二半导体层120为algan层的情况下,源极电极s1及漏极电极d1与algan层接触。

[0151]

图12是表示第一实施方式的半导体元件100的源极电极s1及漏极电极d1的层叠构造的图。源极电极s1具有从第二半导体层120侧起依次形成的第一金属层s1a1、第二金属层s1a2、第三金属层s1a3、第四金属层s1a4、第五金属层s1a5、第六金属层s1a6。在第三金属层s1a3与第四金属层s1a4之间也可以存在其他金属层。

[0152]

第一金属层s1a1例如为v。第二金属层s1a2例如为al。第三金属层s1a3例如为ti。第四金属层s1a4例如为ti。第五金属层s1a5例如为au。第六金属层s1a6例如为au。上述为例示,也可以使用上述以外的金属或合金。

[0153]

第一金属层s1a1的膜厚例如为5nm以上且60nm以下。第二金属层s1a2的膜厚例如为20nm以上且400nm以下。第三金属层s1a3的膜厚例如为5nm以上且60nm以下。第四金属层s1a4的膜厚例如为5nm以上且60nm以下。第五金属层s1a5的膜厚例如为50nm以上且400nm以下。第六金属层s1a6的膜厚例如为1000nm以上且15000nm以下。上述为例示,也可以使用上述以外的数值。

[0154]

从第一金属层s1a1至第五金属层s1a5的金属层例如相当于源极接触电极s1c。第六金属层s1a6例如相当于源极配线电极s1w。

[0155]

漏极电极d1具有从第二半导体层120侧起依次形成的第一金属层d1a1、第二金属层d1a2、第三金属层d1a3、第四金属层d1a4、第五金属层d1a5、第六金属层d1a6。这些金属层中的金属的种类及膜厚与源极电极s1相同。当然,这些金属层中的金属的种类及膜厚也可以与源极电极s1不同。

[0156]

1-8-2.栅极电极

[0157]

图13是表示第一实施方式的半导体元件100的栅极电极g1的层叠构造的图。栅极电极g1具有从第四半导体层140侧起依次形成的第一金属层g1a1、第二金属层g1a2、第三金属层g1a3、第四金属层g1a4。

[0158]

第一金属层g1a1例如为ni。第二金属层g1a2例如为au。第三金属层g1a3例如为ni。第四金属层g1a4例如为au。上述为例示,也可以使用上述以外的金属或合金。

[0159]

第一金属层g1a1的膜厚例如为5nm以上且100nm以下。第二金属层g1a2的膜厚例如为5nm以上且300nm以下。第三金属层g1a3的膜厚例如为5nm以上且100nm以下。第四金属层g1a4的膜厚例如为50nm以上且400nm以下。上述为例示,也可以使用上述以外的数值。

[0160]

从第一金属层g1a1至第三金属层g1a3的金属层例如相当于栅极接触电极g1c。第四金属层g1a4例如相当于栅极配线电极g1w。另外,也可以是从第一金属层g1a1至第四金属层g1a4的金属层相当于栅极接触电极g1c,并在其之上存在栅极配线电极g1w。

[0161]

2.半导体元件的工作原理

[0162]

2-1.二维电子气及二维空穴气

[0163]

图14是表示第一实施方式的半导体元件100的二维电子气及二维空穴气的图。图15是表示第一实施方式的半导体元件100的带构造的图。

[0164]

如图14所示,第一半导体层110与第二半导体层120形成异质结。由此,产生压电极化及自发极化,在第一半导体层110侧的第二半导体层120感应出正的固定电荷。另外,第二半导体层120与第三半导体层130异质结。由此,产生压电极化及自发极化,在第三半导体层130侧的第二半导体层120感应出负的固定电荷。

[0165]

由此,如图14及图15所示,在第二半导体层120侧的第一半导体层110的内部产生二维电子气(2deg),在第二半导体层120侧的第三半导体层130的内部产生二维空穴气(2dhg)。

[0166]

另外,p型的第四半导体层140与第三半导体层130接触。因此,拉高第三半导体层130中的第二半导体层120侧的价带的上端的能量。因此,促进了二维空穴气(2dhg)的产生。

[0167]

这样一来,如图14及图15所示,在异质界面产生二维电子气(2deg)及二维空穴气(2dhg)。

[0168]

2-2.阈值电压

[0169]

在对栅极电极g1施加的栅极电压为阈值电压vth以上的情况下,如上述那样产生压电极化及自发极化。而且,产生二维电子气(2deg)及二维空穴气(2dhg)。在该状态下,在源极电极s1与漏极电极d1之间有电流流动。阈值电压vth例如为-5v左右。

[0170]

在对栅极电极g1施加的栅极电压小于阈值电压vth的情况下,不产生压电极化及自发极化。因此,在源极电极s1与漏极电极d1之间几乎没有电流流动。实际上,在源极电极s1与漏极电极d1之间有微小的漏电流流动。

[0171]

若使栅极电压不足阈值电压vth,则空穴被从第四半导体层140抽出。因此,不从栅极电极g1向第三半导体层130供给正电荷,二维电子气(2deg)及二维空穴气(2dhg)几乎同时消失。

[0172]

漏极电流按照漏极电极d1、第二半导体层120、第一半导体层110的二维电子气(2deg)、第二半导体层120、源极电极s1的路径流动。二维空穴气(2dhg)仅在半导体元件100的导断时与二维电子气(2deg)一同产生,并不会为了使电流流过半导体元件100而直接利用。

[0173]

3.半导体元件的电气特性

[0174]

这里,对半导体元件100的构造与半导体元件100的电气特性之间的关系进行说明。

[0175]

图16是示意性地表示对第一实施方式的半导体元件100的栅极电极g1施加了反偏

压的情况下的电场的示意图。图16的横轴表示半导体元件100的位置。图16的纵轴为电场。在施加了反偏压时,半导体元件100中的空穴被抽出。因此,二维电子气(2deg)及二维空穴气(2dhg)消失。而且,第一半导体层110、第二半导体层120及第三半导体层130耗尽。其结果是:电场的强度在图16中的极化超结区域psj1的宽度方向上一样。这里,图16所示的电场的面积相当于电压。

[0176]

即使在半导体元件100的源极电极s1与漏极电极d1之间施加了高电压,也能够通过对栅极电极施加反偏压来如图16那样使电场在空间上广泛分布。即,该半导体元件100能够抑制局部形成强的电场。因此,半导体元件100的耐压性高。

[0177]

在本说明书中,fet的耐压是指在施加了-10v的栅极电压vg的关断状态下、在施加了漏极电压vd时漏极电流id达到1

×

10-4

a的漏极电压vd的值。在本实施方式中,半导体元件100在常温下的额定电流为几a~几十a左右。上述的漏极电流id为比该额定电流低5个数量级左右的值。

[0178]

3-1.极化超结区域

[0179]

若存在极化超结区域psj1,则能够使极化超结区域psj1耗尽。即使对栅极电极g1施加较大的反偏压,也遍及极化超结区域psj1地形成一样的电场分布。另一方面,在现有的fet中,大多在栅极附近形成强的电场。因此,与同样的条件下的现有的fet相比,形成在栅极电极g1附近的电场强度足够小。像这样,在半导体元件100中,缓和了向栅极附近的电场集中。因此,处于极化超结区域psj1的长度亦即极化超结长度lpsj越长、则半导体元件100的耐压性越高的趋势。

[0180]

另一方面,若极化超结长度lpsj较短,则源极电极s1与漏极电极d1之间的距离较短。因此,处于极化超结长度lpsj越短、则半导体元件100的导通电阻越低的趋势。

[0181]

3-2.栅极长度

[0182]

栅极长度lg为第四半导体层140在连接从源极电极接触区域sc1至漏极电极接触区域dc1的最短距离的方向上的长度。处于栅极长度lg越短、则响应时间越短的趋势。在栅极长度lg较短的情况下,栅极长度lg方向的耗尽层区域较短。由于耗尽层区域变窄,因此栅极电荷电容可以较小。即,在使半导体元件100进行开关动作时,栅极电极g1向耗尽层区域供给或排出的电荷量较少即可。由此,半导体元件100的开关速度提高。

[0183]

3-3.栅极宽度

[0184]

栅极宽度为第四半导体层140在与连接从源极电极接触区域sc1至漏极电极接触区域dc1的最短距离的方向正交的方向上的长度。即,栅极宽度是栅极电极接触区域gc1包围源极电极接触区域sc1的周围的长度。由于多个源极电极接触区域sc1离散配置,因此,实际上,栅极宽度为多个栅极电极接触区域gc1包围多个源极电极接触区域sc1的周围的长度之和。

[0185]

栅极宽度越长,越能够增大供电流流过半导体元件100的区域。因此,处于栅极宽度越长、则漏极电压vd为2v时的电流值越大的趋势。在第一实施方式中,为了增加该栅极宽度,将源极电极接触区域sc1设为棒状形状,并将漏极电极接触区域dc1设为梳齿形状。

[0186]

此外,由于漏极电流在源极电极s1与漏极电极d1之间流动,因此能够采用增加源极宽度或漏极宽度的构思。漏极电流被认为取决于源极宽度和漏极宽度中的较短的一方而被限制。源极宽度为源极电极接触区域sc1的外周长度。漏极宽度为漏极电极接触区域dc1

的外周长度。不过,源极宽度或漏极宽度也可以减去源极电极接触区域sc1与漏极电极接触区域dc1未面对的区域的长度。

[0187]

3-4.绝缘层的突出部

[0188]

如图5所示,第二半导体层120在绝缘层il1的突出部il1a的周边与绝缘层il1接触。如图8所示,第二半导体层120在除绝缘层il1的突出部il1a的周边以外的部位与聚酰亚胺层pii接触。聚酰亚胺层pi1适于形成比绝缘层il1厚的膜。因此,聚酰亚胺层pi1将半导体层周围的更多的区域绝缘。

[0189]

如图5所示,在栅极配线电极g1w的正下方的区域中,绝缘层il1将半导体层与其周围的材料绝缘。如图8所示,在除栅极配线电极g1w的正下方以外的区域中,聚酰亚胺层pi1将半导体层与其周围的材料绝缘。

[0190]

这里,假设在除栅极配线电极g1w的正下方以外的区域中,绝缘层il1将半导体层与其周围的材料绝缘。对漏极电极接触区域dc1施加高电位。因此,存在从漏极电极接触区域dc1向源极电极接触区域sc1或栅极电极接触区域gc1经由绝缘层il1的表面产生漏电流的担忧。在本实施方式中,在除栅极配线电极g1w的正下方以外的区域中,聚酰亚胺层pi1将半导体层与其周围的材料绝缘,因此经由绝缘层il1的表面的漏电流被抑制。

[0191]

如图5所示,在突出部il1a的部位,从蓝宝石基板sub侧起依次层叠有第一半导体层110、第二半导体层120、第三半导体层130、第四半导体层140、绝缘层il1及栅极配线电极g1w。若绝缘层il1为氧化物,则该层叠构造成为mos构造。在该突出部il1a的部位和栅极接触电极g1c与第四半导体层140直接接触的部位,用于耗尽极化超结区域psj1的栅极电压不同。

[0192]

在第一实施方式的半导体元件100中,第二半导体层120与绝缘层il1的接触部位限定于突出部il1a的周边。并且,将栅极电极接触区域gc1投影到第二半导体层120而得的区域包围源极电极接触区域sc1的周围。因此,漏电流被抑制。

[0193]

4.半导体元件的制造方法

[0194]

4-1.半导体层形成工序

[0195]

如图17所示,在蓝宝石基板sub1之上依次生长出缓冲层bf1、第一半导体层110、第二半导体层120、第三半导体层130、第四半导体层140。因此,例如,利用mocvd法即可。或者也可以利用其他气相生长法、液相生长法等。

[0196]

4-2.凹部形成工序

[0197]

如图18所示,形成凹部x1、x2、x3。因此,只要利用icp等干式蚀刻即可。蚀刻气体例如为cl2、bcl3、sicf4等氯系气体。在干式蚀刻时,使用光致抗蚀剂等即可。凹部x1为形成源极电极s1的区域。凹部x2为形成漏极电极d1的区域。凹部x3为成为极化超结区域psj1的区域。

[0198]

在凹部x1及凹部x2的底部露出第二半导体层120。在凹部x3的底部露出第三半导体层130。因此,首先,在露出至第三半导体层130之后仅对形成凹部x1、x2的区域再次进行蚀刻来使第二半导体层120露出即可。或者,也可以实施分开的两个工序。这里,凹部x1、x2的深度为相同程度,但凹部x1、x2不相连。凹部x1为棒状的形状,凹部x2为梳齿形状。

[0199]

另外,在元件功能区域fr1外侧的区域中,形成槽u1及槽u2来使第一半导体层110露出。由此,在除存在源极电极接触区域sc1、漏极电极接触区域dc1、栅极电极接触区域

gc1、极化超结区域psj1的区域以外的区域,不形成电流的路径。即,半导体元件100的有源区域被限定。

[0200]

4-3.绝缘层形成工序

[0201]

在第一半导体层110的槽u1及槽u2之上形成绝缘层il1。因此,例如利用cvd法即可。

[0202]

4-4.电极形成工序

[0203]

如图19所示,形成源极电极s1、漏极电极d1及栅极电极g1。源极电极s1及漏极电极d1由于电极的层叠构造相同,因此在同一工序中实施即可。栅极电极g1的层叠构造与源极电极s1及漏极电极d1不同,因此在不同工序中实施。为了形成上述的电极,利用溅射、ald法、eb蒸镀法等成膜技术即可。通过该工序,绝缘层il1配置在源极电极s1、漏极电极d1及栅极电极g1与第一半导体层110之间。

[0204]

4-5.保护层形成工序

[0205]

接下来,用聚酰亚胺覆盖露出的半导体层的表面。将聚酰亚胺的前体亦即聚酰胺酸涂布于半导体的露出部分。之后,在250℃以上且500℃以下加热晶片,形成聚酰亚胺层p11。

[0206]

4-6.元件分离工序

[0207]

然后,从晶片切出半导体元件100,制造各自独立的半导体元件100。

[0208]

4-7.其他工序

[0209]

也可以适当实施形成配线电极或焊盘电极的工序、热处理工序等其他工序。通过以上工序来得到半导体元件100。

[0210]

5.第一实施方式的效果

[0211]

5-1.源极电极接触区域以及漏极电极接触区域

[0212]

源极电极接触区域sc1为棒状形状。漏极电极接触区域dc1为梳齿形状。而且,在漏极电极接触区域dc1的梳齿之间配置有源极电极接触区域sc1的棒状形状。源极电极接触区域sc1的外周部与漏极电极接触区域dc1的外周部构成的路径长。电流流过被夹在源极电极接触区域sc1与漏极电极接触区域dc1之间的区域的半导体层。因此,该半导体元件100能够流过大电流。

[0213]

5-2.栅极电极接触区域

[0214]

在半导体元件100中,将栅极电极g1与第四半导体层140接触的栅极电极接触区域gc1投影到第二半导体层120而得的区域非接触地包围将源极电极s1与第二半导体层120接触的源极电极接触区域sc1投影到第二半导体层120而得的区域的周围。因此,在漏极电极d1与第二半导体层120接触的漏极电极接触区域dc1和源极电极接触区域sc1之间一定存在栅极电极接触区域gc1。因此,半导体元件100能够抑制关断时的漏电流。

[0215]

5-3.极化超结区域

[0216]

半导体元件100具有极化超结区域psj1。通过具有极化超结区域psj1,能够扩大耗尽区域。因此,半导体元件100具备高的耐压性。

[0217]

5-4.栅极长度

[0218]

半导体元件100具有比较长的栅极长度lg。由于栅极长度lg比较长,因此能够扩大耗尽区域。

[0219]

6.变形例

[0220]

6-1.装置

[0221]

第一实施方式的技术能够应用于具有半导体元件100的装置。作为这样的装置,例如可举出封装体、模块、发射器、通信器、电力输送器等。

[0222]

6-2.半导体层

[0223]

在第一实施方式中,第二半导体层120为a1gan。第二半导体层120也可以是al

x

inyga

(1-x-y)

n(x>0)。第一半导体层110及第三半导体层130也可以是al

x

inyga

(1-x-y)

n(x≥0)。不过,第一半导体层110及第三半导体层130的带隙小于第二半导体层120的带隙。另外,第一半导体层110及第三半导体层130的组成也可以不相同。

[0224]

6-3.源极电极接触区域及漏极电极接触区域

[0225]

在第一实施方式中,源极电极接触区域sc1具有棒状形状,漏极电极接触区域dc1具有梳齿形状。也可以取而代之,源极电极接触区域sc1具有梳齿形状,漏极电极接触区域dc1具有棒状形状。

[0226]

因此,源极电极接触区域sc1和漏极电极接触区域dc1中的一方具有棒状形状。源极电极接触区域sc1和漏极电极接触区域dc1中的另一方具有梳齿形状。源极电极接触区域sc1和漏极电极接触区域dc1中的一方的棒状形状配置在源极电极接触区域sc1和漏极电极接触区域dc1中的另一方的梳齿形状之间。

[0227]

6-4.电极接触区域的形状

[0228]

源极电极接触区域sc1的棒状形状的前端部分为圆弧形状。但是,前端部分并不局限于圆弧。棒状形状的前端部分为弧状的弧状部。棒状形状的除前端部分以外的部分为直线形状的棒状部。

[0229]

6-5.源极接触电极及漏极接触电极

[0230]

源极接触电极s1c及漏极接触电极d1c与第二半导体层120直接接触。这是因为凹部x1、x2到达第二半导体层120的中途。但是,若凹部x1、x2的底部十分接近第二半导体层120,则不需要源极接触电极s1c及漏极接触电极d1c与第二半导体层120直接接触。在该情况下,凹部x1、x2到达第三半导体层130的中途。而且,源极接触电极s1c及漏极接触电极d1c与非常薄的第三半导体层130接触。第三半导体层130的非常薄的部分的厚度例如为10nm以下。此时,第三半导体层130在凹部x1、x2的部位较薄,在除凹部x1、x2以外的部位比在凹部x1、x2的部位厚。即使在该情况下,半导体元件也能够在源极漏极间流过足够大的电流。

[0231]

因此,源极电极s1及漏极电极d1形成在第二半导体层120或第三半导体层130之上。源极电极接触区域sc1为源极电极s1与第二半导体层120或第三半导体层130接触的区域。漏极电极接触区域dc1为漏极电极d1与第二半导体层120或第三半导体层130接触的区域。

[0232]

6-6.栅极电极接触区域

[0233]

栅极电极接触区域gc1可以包围漏极电极接触区域dc1。在该情况下,关断时的漏电流也被抑制。在该情况下,将栅极电极接触区域gc1投影到第二半导体层120而得的区域包围将源极电极接触区域sc1或漏极电极接触区域dc1投影到第二半导体层120而得的区域的周围。

[0234]

6-7.配线电极

[0235]

也可以交换源极电极s1与漏极电极d1的位置关系。在该情况下,将源极配线电极s1w投影到第二半导体层120而得的区域和将漏极配线电极d1w投影到第二半导体层120而得的区域这两个区域中的一方与将栅极配线电极g1w投影到第二半导体层120而得的区域部分地重叠,将源极配线电极s1w投影到第二半导体层120而得的区域和将漏极配线电极d1w投影到第二半导体层120而得的区域这两个区域中的另一方不与将栅极配线电极g1w投影到第二半导体层120而得的区域重叠。

[0236]

另外,在将源极配线电极s1w投影到第二半导体层120而得的区域和将漏极配线电极d1w投影到第二半导体层120而得的区域这两个区域中的一方与将栅极配线电极g1w投影到第二半导体层120而得的区域部分地重叠的部位,源极配线电极s1w或漏极配线电极d1w与第一半导体层110之间的距离大于栅极配线电极g1w与第一半导体层110之间的距离。

[0237]

6-8.保护膜

[0238]

保护半导体层的保护膜可以是除聚酰亚胺以外的绝缘层。绝缘层具有无机电介质膜和有机电介质膜中的至少一方即可。例如,绝缘层具有sio2、si

x

ny、sion、al2o3、aln、alon、zro2、zrn、zron、ta2o3、tan、taon、hfo2、hfn2、hfon、tio2、tin、tion、聚酰亚胺中的任一种以上。

[0239]

6-9.组合

[0240]

可以将上述的变形例自由组合。

[0241]

(第二实施方式)

[0242]

对第二实施方式进行说明。

[0243]

1.半导体元件

[0244]

图20是第二实施方式的半导体元件200的俯视图。源极电极s1与第二半导体层120接触的源极电极接触区域sc1为棒状形状。漏极电极d1与第二半导体层120接触的漏极电极接触区域dc1为梳齿形状。源极电极接触区域sc1的棒状形状配置在漏极电极接触区域dc1的梳齿形状之间。

[0245]

在半导体元件200中,距离lpsj2为距离lpsj1以上。距离lpsj1为源极电极接触区域sc1的除前端部分以外的棒状部分中的极化超结长度。距离lpsj2为源极电极接触区域1的前端部分中的极化超结长度。

[0246]

像这样,棒状形状的前端部分中的连接从源极电极接触区域sc1至漏极电极接触区域dc1的最短距离的方向的极化超结区域psj2的长度为棒状形状的除前端部分以外的部分中的连接从源极电极接触区域sc1至漏极电极接触区域dc1的最短距离的方向的极化超结区域psj1的长度以上。

[0247]

棒状形状的前端部分中的连接从源极电极接触区域sc1至漏极电极接触区域dc1的最短距离的方向的极化超结区域psj2的长度相对于棒状形状的除前端部分以外的部分中的连接从源极电极接触区域sc1至漏极电极接触区域dc1的最短距离的方向的极化超结区域psj1的长度为1.05以上且3以下即可。

[0248]

在半导体元件200中,距离lsd2为距离lsd1以上。距离lsd1为源极电极接触区域sc1的除前端部分以外的棒状部分中的源极电极接触区域sc1与漏极电极接触区域dc1之间的距离。距离lsd2为源极电极接触区域sc1的前端部分中的源极电极接触区域sc1与漏极电极接触区域dc1之间的距离。

[0249]

即,棒状形状的前端部分中的源极电极接触区域sc1与漏极电极接触区域dc1之间的距离为棒状形状的除前端部分以外的部分中的源极电极接触区域sc1与漏极电极接触区域dc1之间的距离以上。

[0250]

棒状形状的前端部分为弧状的弧状部。棒状形状的除前端部分以外的部分为直线形状的棒状部。

[0251]

2.第二实施方式的效果

[0252]

源极电极s1的源极电极接触区域sc1的前端部分与除前端部分以外的棒状部分相比,电场易变强。在第二实施方式的半导体元件200中,在其前端部分中,加长了极化超结区域psj的极化超结长度lpsj2的长度。另外,因同样的理由增大了距离lsd2。因此,半导体元件200具备更高的耐压性。

[0253]

3.变形例

[0254]

3-1.源极电极接触区域及漏极电极接触区域

[0255]

也可以是源极电极接触区域sc1具有梳齿形状,漏极电极接触区域dc1具有棒状形状。源极电极接触区域sc1的梳齿形状具有棒状形状。即使在该情况下,棒状形状的前端部分中的源极电极接触区域sc1与漏极电极接触区域dc1之间的距离也为棒状形状的除前端部分以外的部分中的源极电极接触区域sc1与漏极电极接触区域dc1之间的距离以上。

[0256]

3-2.弧状部

[0257]

弧状部例如为圆弧形状。但是,弧状部也可以是除圆弧以外的弧状形状。

[0258]

3-3.组合

[0259]

可以自由组合上述的变形例。

[0260]

(第三实施方式)

[0261]

对第三实施方式进行说明。

[0262]

1.半导体元件

[0263]

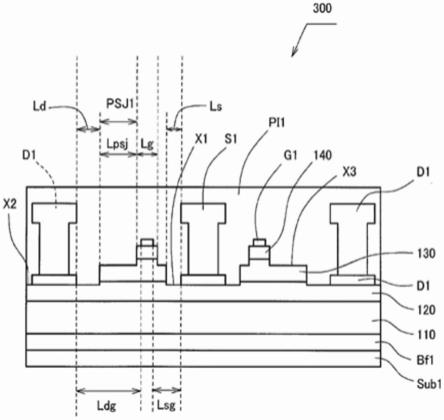

图21是表示第三实施方式的半导体元件300的层叠构造的图。源极电极s1形成在凹部x1之上。漏极电极d1形成在凹部x2之上。

[0264]

这里,漏极电极接触区域dc1与第三半导体层130之间的距离ld大于源极电极接触区域sc1与第三半导体层130之间的距离ls。漏极电极接触区域dc1与第三半导体层130之间的距离ld例如为1μm以上且10μm以下。

[0265]

另外,在将源极电极接触区域sc1、漏极电极接触区域dc1及栅极电极接触区域gc1投影到第二半导体层120的情况下,投影了漏极电极接触区域dc1的区域与投影了栅极电极接触区域gc1的区域之间的距离ldg大于投影了源极电极接触区域sc1的区域与投影了栅极电极接触区域gc1的区域之间的距离lsg。

[0266]

2.第三实施方式的效果

[0267]

在半导体元件300工作时,漏极电极d1与栅极电极g1之间的电位差(电压)有时充分大于源极电极s1与栅极电极g1之间的电位差(电压)。因此,在第三实施方式中,使漏极电极接触区域dc1与栅极电极接触区域gc1之间的距离ldg充分大于源极电极接触区域sc1与栅极电极接触区域gc1之间的距离lsg。对漏极电极d1施加绝对值高的电位,因此漏极栅极间的电场强度强于源极栅极间的电场强度。因此,使距离ldg充分大于距离lsg。

[0268]

(第四实施方式)

[0269]

对第四实施方式进行说明。

[0270]

1.半导体元件

[0271]

图22是表示第四实施方式的半导体元件400的栅极焊盘电极的周边的图。

[0272]

源极电极s2具有源极接触电极s2c、源极配线电极s2w及源极焊盘电极s2p。源极接触电极s2c与第二半导体层120直接接触。源极配线电极s2w连结源极接触电极s2c与源极焊盘电极s2p。源极焊盘电极s2p是用于与外部电源电连接的电极。

[0273]

栅极电极g2具有栅极接触电极g2c、栅极配线电极g2w及栅极焊盘电极g2p。栅极接触电极g2c与第四半导体层140直接接触。栅极配线电极g2w连结栅极接触电极g2c与栅极焊盘电极g2p。栅极焊盘电极g2p是用于与外部电源电连接的电极。

[0274]

源极配线电极s2w在与源极焊盘电极s2p的连结部位具有弯曲为弧状的弯曲部s2r。栅极配线电极g2w在与栅极焊盘电极g2p的连结部位具有弯曲为弧状的弯曲部g2r。

[0275]

2.绝缘层

[0276]

图23是表示第四实施方式的半导体元件400的漏极电极露出区域的周边的截面构造的图。如图23所示,半导体元件400除了具有绝缘层il1之外,还具有绝缘层il2、绝缘层il3及绝缘层il4。绝缘层il2位于绝缘层il1之上。绝缘层il3位于绝缘层il2之上。绝缘层il4位于绝缘层il3之上。

[0277]

绝缘层il1及绝缘层il2的材质为无机电介质膜。无机电介质膜例如为sio2。另外,绝缘层il3及绝缘层il4的材质为有机电介质膜。有机电介质膜例如为聚酰亚胺。在sio2等硬的膜之上形成有机电介质膜即可。

[0278]

绝缘层il2及绝缘层il3填埋绝缘层il1与第二半导体层120之间的间隙。绝缘层il2填埋半导体层的侧面及表面。另外,绝缘层il2填埋源极电极s1、漏极电极d1及栅极电极g1的接触电极。绝缘层il4为最上层。

[0279]

3.第四实施方式的效果

[0280]

半导体元件400具备高的耐压性。因此,在使用时,有时对半导体元件400施加高电压。像这样,即使在施加了高电压的情况下,也可抑制在弯曲部s2r及弯曲部g2r的周围形成强的电场。另外,认为还缓和绝缘层内的内部应力。

[0281]

4.变形例

[0282]

4-1.漏极电极

[0283]

在漏极电极中,漏极配线电极具有在与漏极焊盘电极的连结部位弯曲为弧状的弯曲部即可。

[0284]

4-2.焊盘电极的数量

[0285]

图24是第四实施方式的变形例中的半导体元件的俯视图。如图24所示,栅极焊盘电极g2p以被夹在源极焊盘电极s2p与源极焊盘电极s2p之间的状态配置。另外,半导体元件也可以具有多个源极焊盘电极s2p。即,栅极电极g2、源极电极s2及漏极电极d2中的至少一个也可以具有多个焊盘电极。

[0286]

图25是表示第四实施方式的变形例中的半导体元件中的栅极焊盘电极的周边的放大图。如图25所示,在连结源极焊盘电极s2p与源极焊盘电极s2p的连结部s2i也形成有弯曲形状s2i1。

[0287]

4-3.焊盘电极的形状

[0288]

源极焊盘电极s2p、栅极焊盘电极g2p及漏极焊盘电极中的至少一个的角可以为弯曲形状。

[0289]

4-4.绝缘层

[0290]

绝缘层具有无机电介质膜和有机电介质膜中的至少一方即可。例如,绝缘层具有sio2、si

x

ny、sion、al2o3、aln、alon、zro2、zrn、zron、ta2o3、tan、taon、hfo2、hfn2、hfon、tio2、tin、tion、聚酰亚胺中的任一种以上。

[0291]

4-5.组合

[0292]

可以自由组合上述的变形例。

[0293]

(第五实施方式)

[0294]

对第五实施方式进行说明。

[0295]

1.半导体元件

[0296]

半导体元件的基本构造与第一实施方式同样。

[0297]

第二半导体层120中的位错密度例如为1

×

106cm-2

以上且1

×

10

10

cm-2

以下。位错密度为5

×

109cm-2

以下即可。另外,第一半导体层110中的位错密度例如为1

×

106cm-2

以上且1

×

10

10

cm-2

以下。位错密度为5

×

109cm-2

以下即可。

[0298]

第二半导体层120与第三半导体层130之间的接触面积在栅极宽度方向的每1μm为10μm2以上且200μm2以下。

[0299]

栅极长度lg为0.1μm以上且6μm以下。另外,栅极长度lg也可以为0.3μm以上且5μm以下。并且,栅极长度lg也可以为1μm以上且4μm以下。

[0300]

第二半导体层120与第三半导体层130之间的接触面积和耐压满足下式(1)

[0301]

101x-810≤y≤235x 585.........(1)

[0302]

x:栅极宽度方向的每1μm的第二半导体层与第三半导体层之间的接触面积

[0303]

y:耐压。

[0304]

2.半导体元件的电气特性

[0305]

第五实施方式的半导体元件中的300v开关下的上升时间(tr)及下降时间(tf)均为3ns以上且30ns以下。

[0306]

第五实施方式的半导体元件的耐压为1500v以上且20000v以下。另外,半导体元件的耐压也可以为3000v以上且10000v以下。

[0307]

3.位错密度

[0308]

为了降低半导体层的位错密度,使用利用溅射形成aln缓冲层的方法、在基板形成凹凸形状的方法、利用vpe形成几十μm以上的厚膜的方法等即可。

[0309]

(第六实施方式)

[0310]

对第六实施方式进行说明。

[0311]

1.半导体元件

[0312]

半导体元件的基本构造与第一实施方式同样。

[0313]

极化超结长度lpsj为1μm以上且50μm以下。极化超结长度lpsj也可以为2μm以上且40μm以下。极化超结长度lpsj还可以为3μm以上且30μm以下。

[0314]

栅极长度lg为0.1μm以上且6μm以下。另外,栅极长度lg也可以为0.3μm以上且5μm以下。并且,栅极长度lg还可以为1μm以上且4μm以下。

[0315]

2.半导体元件的电气特性

[0316]

第六实施方式的半导体元件中的300v开关下的上升时间(tr)及下降时间(tf)均为3ns以上且30ns以下。上升时间(tr)及下降时间(tf)也可以为4ns以上且20ns以下。上升时间(tr)及下降时间(tf)还可以为5ns以上且10ns以下。

[0317]

第六实施方式的半导体元件中的标准化导通电阻为1mω

·

cm2以上且20mω

·

cm2以下。标准化导通电阻也可以为2mω

·

cm2以上且17mω

·

cm2以下。标准化导通电阻还可以为3mω

·

cm2以上且15mω

·

cm2以下。

[0318]

(第七实施方式)

[0319]

对第七实施方式进行说明。

[0320]

1.半导体元件

[0321]

半导体元件的基本构造与第一实施方式同样。

[0322]

有源区域面积为2.2mm2以上且100mm2以下。有源区域面积也可以为2.5mm2以上且90mm2以下。有源区域面积还可以为3mm2以上且80mm2以下。

[0323]

有源区域面积是电流实际流过第一半导体层110的面积。有源区域面积为从第二半导体层120中的第三半导体层130侧的面积减去源极电极接触区域sc1及漏极电极接触区域dc1的面积和夹在最外侧的源极电极接触区域sc1与第二半导体层120的外周部之间的区域的面积而得的面积。

[0324]

栅极长度lg为0.1μm以上且6μm以下。另外,栅极长度lg也可以为0.3μm以上且5μm以下。并且,栅极长度lg还可以为1μm以上且4μm以下。

[0325]

栅极宽度为300mm以上且12000mm以下。栅极宽度也可以为350mm以上且11000mm以下。栅极宽度还可以为400mm以上且10000mm以下。

[0326]

半导体元件的外周长度为13mm以上且520mm以下。半导体元件的外周长度也可以为15mm以上且500mm以下。半导体元件的外周长度还可以为20mm以上且480mm以下。外周长度为半导体元件的蓝宝石基板sub1的4条边的长度之和。

[0327]

2.半导体元件的电气特性

[0328]

第七实施方式的半导体元件中的300v开关下的上升时间(tr)及下降时间(tf)均为3ns以上且30ns以下。

[0329]

第七实施方式的半导体元件中的漏极电压vd为2v时的电流值是30a以上且1200a以下。漏极电压vd为2v时的电流值是在导通状态下非电流饱和区域的区域的电流值。

[0330]

(第八实施方式)

[0331]

1.肖特基势垒二极管

[0332]

图26是表示第八实施方式的半导体元件500的层叠构造的图。半导体元件500为肖特基势垒二极管。半导体元件500具有蓝宝石基板sub2、缓冲层bf2、第一半导体层510、第二半导体层520、第三半导体层530、第四半导体层540、阴极电极c1及阳极电极a1。

[0333]

缓冲层bf2形成在蓝宝石基板sub2之上。第一半导体层510形成在缓冲层bf2之上。第二半导体层520形成在第一半导体层510之上。第三半导体层530形成在第二半导体层520之上。第四半导体层540形成在第三半导体层530之上。

[0334]

第一半导体层510、第二半导体层520、第三半导体层530及第四半导体层540为iii族氮化物半导体层。第二半导体层520的带隙大于第一半导体层510及第三半导体层530的

带隙。第一半导体层510、第二半导体层520及第三半导体层530为未掺杂的半导体层。第四半导体层540为p型半导体层。

[0335]

阴极电极c1形成在第二半导体层520之上。凹部y1从第四半导体层540到达第二半导体层520的中途。阴极电极c1形成在凹部y1之上。

[0336]

阳极电极a1形成在第四半导体层540之上。凹部y2从第四半导体层540到达第一半导体层510的中途。阳极电极a1形成为从凹部y2的底面遍及至第四半导体层540。因此,阳极电极a1与第一半导体层510、第二半导体层520、第三半导体层530及第四半导体层540接触。阳极电极a1与第一半导体层510的底面及侧面、第二半导体层520及第三半导体层530的侧面、第四半导体层540的侧面及上表面接触。

[0337]

图27是表示第八实施方式的半导体元件500的电极形成区域的图。如图27所示,半导体元件500具有阴极电极c1与第二半导体层520接触的阴极电极接触区域cc1和阳极电极a1与第四半导体层540接触的阳极电极接触区域ac1。

[0338]

阴极电极c1与第二半导体层520接触的阴极电极接触区域cc1具有梳齿形状。阳极电极a1与第一半导体层510及第四半导体层540接触的阳极电极接触区域ac1具有棒状形状。将阳极电极接触区域ac1投影到第一半导体层510而得的区域的棒状形状配置于将阴极电极接触区域cc1投影到第一半导体层510而得的区域的梳齿形状之间的位置。

[0339]

极化超结区域是形成有第三半导体层530并且未形成有第四半导体层540的区域中的位于阳极电极接触区域ac1与阴极电极接触区域cc1之间的区域。

[0340]

2.耐压

[0341]

在本说明书中肖特基势垒二极管的耐压是指在阳极电极a1与阴极电极c1之间施加了反向的电压va时阳极电流ia达到1

×

10-4

a的阳极电压va的值。

[0342]

3.变形例

[0343]

3-1.电极接触区域的形状

[0344]

也可以是阴极电极接触区域cc1具有棒状形状,阳极电极接触区域ac1具有梳齿形状。即,可以是阴极电极接触区域cc1和阳极电极接触区域ac1中的一方具有梳齿形状,阴极电极接触区域cc1和阳极电极接触区域ac1中的另一方具有棒状形状。

[0345]

图28是表示第八实施方式的变形例中的半导体元件的电极形成区域的图。阴极电极c1与第二半导体层520接触的阴极电极接触区域cc1具有梳齿形状。阳极电极a1与第一半导体层510及第四半导体层540接触的阳极电极接触区域ac1具有梳齿形状。配置为将阴极电极接触区域cc1投影到第一半导体层510而得的区域的梳齿形状与将阳极电极接触区域ac1投影到第一半导体层510而得的区域的梳齿形状相互不同。

[0346]

阴极电极接触区域cc1和阳极电极接触区域ac1中的一方的棒状形状(包括梳齿形状的前端的棒状部分)配置在阴极电极接触区域cc1和阳极电极接触区域ac1中的另一方的梳齿形状之间即可。

[0347]

3-2.阳极电极的接触区域

[0348]

图29是表示第八实施方式的变形例中的半导体元件600的层叠构造的图(其1)。半导体元件600具有蓝宝石基板sub2、缓冲层bf2、第一半导体层510、第二半导体层520、第三半导体层530、第四半导体层540、阴极电极c1及阳极电极a1。阳极电极a1形成在凹部y3之上。凹部y3从第四半导体层540到达第二半导体层520的中途。在半导体元件600中,阳极电

极a1不与第一半导体层510接触。

[0349]

图30是表示第八实施方式的变形例中的半导体元件700的层叠构造的图(其2)。半导体元件700具有蓝宝石基板sub2、缓冲层bf2、第一半导体层510、第二半导体层520、第三半导体层530、第四半导体层540、阴极电极c1、阳极电极a1及绝缘层750。

[0350]

绝缘层750覆盖第二半导体层520的一部分、第三半导体层530的侧面及第四半导体层540的一部分。绝缘层750位于第三半导体层530的侧面、第四半导体层540的侧面以及阳极电极a1之间。阳极电极a1与第二半导体层520及第四半导体层540接触,不与第三半导体层530接触。

[0351]

像这样,阳极电极a1与第一半导体层510或第二半导体层520接触即可。

[0352]

3-3.阴极电极的接触区域

[0353]

图31是表示第八实施方式的变形例中的半导体元件800的层叠构造的图(其3)。如图31所示,阴极电极c2与第一半导体层510的底面及侧面和第二半导体层520的侧面及上表面接触。

[0354]

3-4.极化超结区域

[0355]

棒状形状的前端部分中的连接从阴极电极接触区域cc1至阳极电极接触区域ac1的最短距离的方向的极化超结区域的长度为棒状形状的除前端部分以外的部分中的连接从阴极电极接触区域cc1至阳极电极接触区域ac1的最短距离的方向的极化超结区域的长度以上。

[0356]

3-5.阴极电极与第三半导体层之间的距离

[0357]

阴极电极接触区域cc1与第三半导体层530之间的距离为1μm以上且10μm以下。

[0358]

3-6.组合

[0359]

可以自由组合上述的变形例。

[0360]

(实施方式的组合)

[0361]

针对从第一实施方式至第八实施方式,存在可以包含变形例在内地自由组合的情况。

[0362]

(评价试验)

[0363]

1.实验1

[0364]

1-1.fet的制作

[0365]

制造了图32及图33所示那样的简单构造的fet。图32是表示栅极电极接触区域gc1包围源极电极接触区域sc1的情况下的fet的图。图33是表示栅极电极接触区域gc1处于源极电极接触区域sc1与漏极电极接触区域dc1之间的情况下的fet的图。在图33中,栅极电极接触区域gc1未包围源极电极接触区域sc1。

[0366]

像这样,制造了栅极电极接触区域gc1包围源极电极接触区域sc1的fet和栅极电极接触区域gc1未包围源极电极接触区域sc1的fet。而且,比较了这些fet的漏电流。

[0367]

1-2.实验结果(漏电流)

[0368]

图34是表示对fet的漏极电极施加了0.1v时的栅极电压和漏极电流之间的关系的图表。图34的横轴为栅极电压。图34的纵轴为漏极电流。

[0369]

图35是表示fet的栅极电压和漏极电流之间的关系的图表。图35的横轴为栅极电压。图35的纵轴为漏极电流。如图35所示,在栅极电极g1包围源极电极s1的情况下,fet在栅

极电压为-5v以上时工作。即使栅极电压小于-5v,也流动有关断漏电流。关断漏电流为1

×

10-9

a/mm左右。

[0370]

如图35所示,在栅极电极g1不包围源极电极s1的情况下,fet在栅极电压为-4.5v以上时工作。在栅极电压小于-4.5v的情况下,;流动有1.0

×

10-6

a/mm左右的关断漏电流。像这样,栅极电极g1包围源极电极s1的周围,从而关断漏电流变小2个数量级左右。

[0371]

图36是表示fet的漏极电压和漏极电流之间的关系的图表。图36的横轴为漏极电压。图36的纵轴为漏极电流。图36示出了栅极电极g1包围源极电极s1的周围的fet的漏极电流。在图36中,示出改变了栅极电压时的漏极电流。如图36所示,越增大栅极电压,则漏极电流越大。

[0372]

图37是表示fet中的关断时的漏极电压和漏极电流之间的关系的图表。图37的横轴为漏极电压。图37的纵轴为漏极电流。此时的栅极电压为-10v。图37示出栅极电极g1包围源极电极s1的周围的fet的漏极电流。如图37所示,在关断时,流动有1

×

10-9

a/mm左右的漏电流。另外,漏极电压越大,则漏极电流越稍稍变大。

[0373]

图38是表示fet中的关断时的漏极电压和栅极电流之间的关系的图表。图38的横轴为漏极电压。图38的纵轴为栅极电流。此时的栅极电压为-10v。图38示出栅极电极g1包围源极电极s1的周围的fet的栅极电流。如图38所示,在关断时,流过1

×

10-9

a/mm左右的漏电流。另外,漏极电压越大,则栅极电流越稍稍变大。

[0374]

如以上那样,在实际制造出的fet中,漏电流被抑制。此外,图35~图38中的电流值按照栅极宽度进行了标准化。

[0375]

2.实验2

[0376]

2-1.fet的制作

[0377]

制作了与第一实施方式的半导体元件100相同的fet。在c面蓝宝石基板之上利用mocvd法依次层叠了氏温gan缓冲层、第一未掺杂gan层、algan层、第二未掺杂gan层、mg掺杂pgan层。低温gan缓冲层、第一未掺杂gan层、algan层、第二未掺杂gan层、mg掺杂pgan层的膜厚分别为30nm、1.0μm、47nm、80nm、53nm。低温gan缓冲层的成膜温度为530℃。第一未掺杂gan层、algan层、第一未掺杂gan层的成膜温度为1100℃。使mg掺杂pgan层的mg浓度从5.0

×

10

19

cm-3

上升至2.0

×

10

20

cm-3

,提高了mg掺杂gan层的表面附近的mg浓度。

[0378]

作为栅极电极,从半导体层侧起依次层叠有ni、au。作为源极电极、漏极电极,从半导体层侧起依次层叠有ti、al、ni、au。

[0379]

作为半导体层的位错密度,使用了三个种类。第一元件的位错密度为5.0

×

108cm-2

。第二元件的位错密度为2.3

×

109cm-2

。第三元件的位错密度为9.0

×

109cm-2

。

[0380]

2-2.评价方法

[0381]

图39是在fet的评价中使用的电路图。图40是表示fet的评价中的输出值的图表。漏极电压vd为300v。

[0382]

图41是表示fet的上升时间tr及下降时间tf的定义的图。上升时间tr是指漏极电压vd从最大值的90%下降至10%所花费的时间。下降时间tf是指漏极电压vd从最大值的10%上升至90%所花费的时间。如图40所示,伴随漏极电压vd下降,漏极电流id增加。如图40所示,由于漏极电流id小幅振动,所以代替漏极电流id而将漏极电压vd作为上升时间tr及下降时间tf的基准。

[0383]

2-3.实验结果(响应时间)

[0384]

图42是表示fet的特性的表。在实施例1~6中,上升时间为22ns以下。在比较例1中,上升时间为42ns。在实施例1~6中,栅极长度为4μm,而在比较例1中,栅极长度为8μm。

[0385]

图43是表示fet中的第二未掺杂gan层(第三半导体层)与mg掺杂pgan层(第四半导体层)的接合面积和半导体元件的耐压之间的关系的图表。图43的横轴为栅极宽度方向每1μm的第二未掺杂gan层(第三半导体层)的面积。图43的纵轴为半导体元件的耐压。

[0386]

如图43所示,在上述的式(1)成立的区域中,耐压为1500v以上。

[0387]

101x-810≤y≤235x 585.........(1)

[0388]

x:栅极宽度方向的每1μm的第二半导体层与第三半导体层之间的接触面积

[0389]

y:耐压

[0390]

图44是表示fet的栅极长度和响应时间之间的关系的图表。图44的横轴为栅极长度。图44的横轴为响应时间。如图44所示,处于栅极长度越短、则响应时间越短的趋势。在栅极长度为6μm以下的情况下,上升时间tr及下降时间tf为30ns以下。在栅极长度为4μm以下的情况下,上升时间tr及下降时间tf为20ns以下。

[0391]

图45是表示fet中的除极化超结区域psj1以外的第三半导体层130与第四半导体层140的接合面积和响应时间之间的关系的图表。图45的横轴为第三半导体层130与第四半导体层140的接合面积。图45的纵轴为响应时间。如图45所示,处于第三半导体层130与第四半导体层140的接合面积越小、则响应时间越短的趋势。

[0392]

图46是表示fet中的位错密度和接合面积之间的关系的图表。图46的横轴为位错密度。图46的纵轴为第三半导体层130与第四半导体层140的接合面积。如图46所示,为了具有大的耐压性,需要增大第三半导体层130与第四半导体层140的接合面积。另外,位错密度越高,则需要取越大的接合面积。

[0393]

图47是汇总了图46的数据的表。

[0394]

图48是表示fet中的位错密度和源极漏极间距离之间的关系的图表。图48的横轴为位错密度。图48的纵轴为源极漏极间距离。如图48所示,为了具有大的耐压性,需要增大源极漏极间距离。另外,位错密度越高,则需要将源极漏极间距离取得越大。

[0395]

图49是汇总了图48的数据的表。

[0396]

图50是表示fet中的位错密度和响应时间之间的关系的图表。图50的横轴为位错密度。图50的纵轴为响应时间。如图50所示,处于位错密度越低、则上升时间tr及下降时间tf均越短的趋势。特别地,通过位错密度的下降,上升时间tr的改善效果较好。

[0397]

图51是汇总了图50的数据的表。如图50及图51所示,在位错密度为5

×

108cm-2

以下的情况下,上升时间tr为16ns以下。在位错密度为5

×

108cm-2

以下的情况下,下降时间tf为10ns以下。

[0398]

2-4.实验结果(导通电阻)

[0399]

图52是表示fet中的极化超结长度lpsj和标准化导通电阻之间的关系的图表。图52的横轴为极化超结长度。图52的纵轴为标准化导通电阻。如图52所示,极化超结长度lpsj越长,则标准化导通电阻越上升。另外,在极化超结长度lpsj为50μm以下的情况下,标准化导通电阻为20mω

·

cm2以下。在极化超结长度lpsj为2μm的情况下,标准化导通电阻为1mω

·

cm2左右。

[0400]

图53是表示fet中的源极漏极间距离和标准化导通电阻之间的关系的图表。图53的横轴为源极漏极间距离。图53的纵轴为标准化导通电阻。如图53所示,源极漏极间距离越长,则标准化导通电阻越上升。另外,在源极漏极间距离为60μm以下的情况下,标准化导通电阻为20mω

·

cm2以下。在源极漏极间距离为11μm的情况下,标准化导通电阻为1mω

·

cm2左右。

[0401]

2-5.实验结果(位错密度)

[0402]

图54是表示fet中的位错密度和半导体元件的特性之间的关系的表。如图54所示,位错密度越低,则x射线摇摆曲线的半高宽的值越小。另外,位错密度越低,则薄层电阻(sheet resistance)越小。并且,位错密度越低,则二维空穴气的迁移率越大。薄层电阻受二维电子气的迁移率影响。因此,认为因位错密度变低、结晶性提高而导致二维电子气的迁移率变大。另一方面,二维空穴气的浓度几乎不取决于位错密度。

[0403]

2-6.实验结果(有源区域)

[0404]

图55是表示fet的芯片尺寸和漏极电压vd为2v时的电流值之间的关系的表。如图55所示,芯片尺寸越大,则芯片外周长度、芯片面积、有源区域面积越大。有源区域面积是在导通状态下电流实际流过的半导体的区域。有源区域面积为从元件功能区域fr1的面积减去源极电极及漏极电极与半导体层接触的区域的面积和夹在最外侧的源极电极接触区域与第二半导体层的外周部之间的区域的面积而得的面积。

[0405]

另外,芯片尺寸越大,则栅极宽度也越大。栅极宽度是指栅极电极g1包围源极电极s1的线的合计长度。

[0406]

图56是表示fet的有源区域面积和漏极电压vd为2v时的电流值之间的关系的图表。图56的横轴为有源区域面积。图56的纵轴为漏极电压vd为2v时的电流值。如图56所示,在有源区域面积为2.2mm2以上的情况下,漏极电压vd为2v时的电流值为30a以上。在有源区域面积为5.0mm2以上的情况下,漏极电压vd为2v时的电流值为100a以上。

[0407]

3.实验3

[0408]

3-1.fet的制作

[0409]

制作了与第二实施方式的半导体元件200同样的fet。除极化超结长度lpsj以外的方面与实验2同样。

[0410]

3-2.实验结果(极化超结长度)

[0411]

图57是表示在改变了fet中的极化超结长度lpsj和源极接触电极s1c与漏极接触电极d1c之间的距离lsd时的fet的耐压性的表。在图57中,示出改变了前端部分中的极化超结长度lpsj的最小值和除前端部分以外的部分中的极化超结长度lpsj的最小值的情况。

[0412]

图58是表示未改变fet中的极化超结长度lpsj和源极接触电极s1c与漏极接触电极d1c之间的距离lsd时的fet的耐压性的表。在图58中,前端部分中的极化超结长度lpsj与除前端部分以外的部分中的极化超结长度lpsj相同。

[0413]

图59是表示fet中的极化超结长度lpsj和fet的耐压性之间的关系的图表。图59的横轴为极化超结长度lpsj。图59的纵轴为fet的耐压性。如图59所示,fet的耐压性与极化超结长度lpsj大致成比例。

[0414]

像这样,fet的耐压取决于极化超结长度lpsj的最小值。

[0415]

4.实验4

[0416]

4-1.fet的制作

[0417]

制作了与第三实施方式的半导体元件300同样的fet。除电极与半导体层之间的距离以外的方面与实验2同样。

[0418]

4-2.实验结果(电极与半导体层之间的距离)

[0419]

图60是表示fet中的漏极电极接触区域dc1与极化超结面之间的距离和耐压性之间的关系的图表。图60的横轴为漏极电极接触区域dc1与极化超结面之间的距离。图60的纵轴为耐电压。如图60所示,即使在漏极电极接触区域dc1与第三半导体层130之间的距离短到10μm以下的情况下,半导体元件的耐压性也十分高。

[0420]

图61是表示fet中的极化超结长度lpsj和半导体元件的耐压性之间的关系的图表。图61的横轴为极化超结长度lpsj。图61的纵轴为半导体元件的耐压。如图61所示,极化超结长度lpsj越长,则半导体元件的耐压性越高。在某种程度上,半导体元件的耐压与极化超结长度lpsj成比例。

[0421]

5.实验5

[0422]

5-1.fet的制作

[0423]

制作了与第四实施方式的半导体元件400同样的fet。除焊盘电极以外与实验2同样。

[0424]

5-2.实验结果(焊盘电极)

[0425]

图62是表示fet的漏极电压与漏极电流之间的关系的图表。图62的横轴为漏极电压。图62的纵轴为漏极电流。如图62所示,处于若使栅极电压上升、则漏极电流变大的趋势。在漏极电压约为15v以上时,漏极电流饱和。

[0426]

图63是表示fet的漏极电压为0.1v时的栅极电压和漏极电流之间的关系的图表。图63的横轴为栅极电压。图63的纵轴为漏极电流。

[0427]

图64是表示fet关断时的漏极电压和漏极电流之间的关系的图表。图64的横轴为漏极电压。图64的纵轴为漏极电流。栅极电压为-10v。

[0428]

图65是表示fet关断时的漏极电压和栅极电流之间的关系的图表。图65的横轴为漏极电压。图65的纵轴为栅极电流。栅极电压为-10v。

[0429]

图62~图65中的电流值按照栅极宽度进行了标准化。

[0430]

6.实验6

[0431]

6-1.肖特基势垒二极管的制造

[0432]

制造了与第八实施方式同样的肖特基势垒二极管。该半导体层的层叠构造及制造条件与实验1同样。制造出改变了极化超结长度lpsj的元件。

[0433]

6-2.实验结果(反向恢复电流)

[0434]

图66是表示极化超结长度lpsj为20μm的肖特基势垒二极管的反向恢复时间特性的图表。图66的横轴为时间。图66的纵轴为阳极电流。反向恢复时间为21.8ns。反向恢复电流的峰值为5.0a。

[0435]

6-3.实验结果(正向特性)

[0436]

图67是表示肖特基势垒二极管的正向特性的图表。图67的横轴为阳极电压。图67的纵轴为阳极电流。如图67所示,具有极化超结长度lpsj越短、则阳极电流越大的趋势。即,具有极化超结长度lpsj越短、则标准化导通电阻越小的趋势。

[0437]

6-4.实验结果(反向特性)

[0438]

图68是表示肖特基势垒二极管的反向特性的图表。图68的横轴为阴极电压。图68的纵轴为阳极电流。如图68所示,极化超结长度lpsj越短,则耐压性越低。在极化超结长度lpsj为15μm、20μm、25μm、30μm、40μm的情况下,耐压性分别约为2000v、2600v、3000v、超过3000v、超过3000v。

[0439]

6-5.实验结果(极化超结长度)

[0440]

图69是表示改变了极化超结长度lpsj和阳极电极接触区域ac1与阴极电极接触区域cc1之间的距离lac时的肖特基势垒二极管的耐压性的表。在图69中,示出改变了前端部分中的极化超结长度lpsj的最小值和除前端部分以外的部分中的极化超结长度lpsj的最小值的情况。

[0441]

通过将前端部分的极化超结长度lpsj及距离lac设为除前端部分以外的极化超结长度lpsj及距离lac以上,从而肖特基势垒二极管的耐压提高。

[0442]

(附注)

[0443]

1.第一

[0444]

第一方式的半导体元件具有:第一半导体层;比第一半导体层靠上层的第二半导体层;比第二半导体层靠上层的第三半导体层;比第三半导体层靠上层的第四半导体层;第二半导体层或第三半导体层之上的源极电极及漏极电极;第四半导体层之上的栅极电极;栅极电极与第四半导体层接触的栅极电极接触区域;源极电极与第二半导体层或第三半导体层接触的源极电极接触区域;以及漏极电极与第二半导体层或第三半导体层接触的漏极电极接触区域。第一半导体层、第二半导体层、第三半导体层及第四半导体层为iii族氮化物半导体层。第二半导体层的带隙大于第一半导体层及第三半导体层的带隙。第一半导体层、第二半导体层及第三半导体层为未掺杂的半导体层。第四半导体层为p型半导体层。将栅极电极接触区域投影到第二半导体层而得的区域包围将源极电极接触区域或漏极电极接触区域投影到第二半导体层而得的区域的周围。

[0445]

在第二方式的半导体元件中,源极电极接触区域和漏极电极接触区域中的一方具有棒状形状。源极电极接触区域和漏极电极接触区域中的另一方具有梳齿形状。源极电极接触区域和漏极电极接触区域中的一方的棒状形状配置在源极电极接触区域和漏极电极接触区域中的另一方的梳齿形状之间。

[0446]

在第三方式的半导体元件中,源极电极具有源极配线电极。漏极电极具有漏极配线电极。将源极配线电极投影到第二半导体层而得的区域不与将漏极配线电极投影到第二半导体层而得的区域重叠。

[0447]

在第四方式的半导体元件中,源极电极具有源极配线电极。漏极电极具有漏极配线电极。栅极电极具有栅极配线电极。将源极配线电极投影到第二半导体层而得的区域和将漏极配线电极投影到第二半导体层而得的区域这两个区域中的一方与将栅极配线电极投影到第二半导体层而得的区域部分地重叠。将源极配线电极投影到第二半导体层而得的区域和将漏极配线电极投影到第二半导体层而得的区域这两个区域中的另一方不与将栅极配线电极投影到第二半导体层而得的区域重叠。

[0448]

在第五方式的半导体元件中,在将源极配线电极投影到第二半导体层而得的区域和将漏极配线电极投影到第二半导体层而得的区域这两个区域中的一方与将栅极配线电

极投影到第二半导体层而得的区域部分地重叠的部位,源极配线电极或漏极配线电极与第一半导体层之间的距离大于栅极配线电极与第一半导体层之间的距离。

[0449]

在第六方式的半导体元件中,第一半导体层与第二半导体层直接接触。第一半导体层与第二半导体层接触的接触面的形状为长方形。棒状形状的长度方向配置为与长方形的短边平行的方向。

[0450]

第七方式的装置具有上述的半导体元件。

[0451]

2.第二

[0452]

第一方式的半导体元件具有:第一半导体层;比第一半导体层靠上层的第二半导体层;比第二半导体层靠上层的第三半导体层;比第三半导体层靠上层的第四半导体层;第二半导体层或第三半导体层之上的源极电极及漏极电极;第四半导体层之上的栅极电极;栅极电极与第四半导体层接触的栅极电极接触区域;源极电极与第二半导体层或第三半导体层接触的源极电极接触区域;以及漏极电极与第二半导体层或第三半导体层接触的漏极电极接触区域。第一半导体层、第二半导体层、第三半导体层及第四半导体层为iii族氮化物半导体层。第二半导体层的带隙大于第一半导体层及第三半导体层的带隙。第一半导体层、第二半导体层及第三半导体层为未掺杂的半导体层。第四半导体层为p型半导体层。源极电极接触区域和漏极电极接触区域中的一方具有棒状形状。源极电极接触区域和漏极电极接触区域中的另一方具有梳齿形状。源极电极接触区域和漏极电极接触区域中的一方的棒状形状配置在源极电极接触区域和漏极电极接触区域中的另一方的梳齿形状之间。

[0453]

在第二方式的半导体元件中,将栅极电极接触区域投影到第二半导体层而得的区域包围将源极电极接触区域或漏极电极接触区域投影到第二半导体层而得的区域的周围。

[0454]

在第三方式的半导体元件中,源极电极具有源极配线电极。漏极电极具有漏极配线电极。将源极配线电极投影到第二半导体层而得的区域不与将漏极配线电极投影到第二半导体层而得的区域重叠。

[0455]

在第四方式的半导体元件中,源极电极具有源极配线电极。漏极电极具有漏极配线电极。栅极电极具有栅极配线电极。将源极配线电极投影到第二半导体层而得的区域和将漏极配线电极投影到第二半导体层而得的区域这两个区域中的一方与将栅极配线电极投影到第二半导体层而得的区域部分地重叠。将源极配线电极投影到第二半导体层而得的区域和将漏极配线电极投影到第二半导体层而得的区域这两个区域中的另一方不与将栅极配线电极投影到第二半导体层而得的区域重叠。

[0456]

在第五方式的半导体元件中,在将源极配线电极投影到第二半导体层而得的区域和将漏极配线电极投影到第二半导体层而得的区域这两个区域中的一方与将栅极配线电极投影到第二半导体层而得的区域部分地重叠的部位,源极配线电极或漏极配线电极与第一半导体层之间的距离大于栅极配线电极与第一半导体层之间的距离。

[0457]

在第六方式的半导体元件中,第一半导体层与第二半导体层直接接触。第一半导体层与第二半导体层接触的接触面的形状为长方形。棒状形状的长度方向配置为与长方形的短边平行的方向。

[0458]

第七方式的装置具有上述的半导体元件。

[0459]

3.第三

[0460]

第一方式的半导体元件具有:第一半导体层;比第一半导体层靠上层的第二半导

体层;比第二半导体层靠上层的第三半导体层;比第三半导体层靠上层的第四半导体层;第二半导体层或第三半导体层之上的源极电极及漏极电极;第四半导体层之上的栅极电极;栅极电极与第四半导体层接触的栅极电极接触区域;源极电极与第二半导体层或第三半导体层接触的源极电极接触区域;以及漏极电极与第二半导体层或第三半导体层接触的漏极电极接触区域。第一半导体层、第二半导体层、第三半导体层及第四半导体层为iii族氮化物半导体层。第二半导体层的带隙大于第一半导体层及第三半导体层的带隙。第一半导体层、第二半导体层及第三半导体层为未掺杂的半导体层。第四半导体层为p型半导体层。源极电极接触区域和漏极电极接触区域中的一方具有棒状形状。源极电极接触区域和漏极电极接触区域中的另一方具有梳齿形状。源极电极接触区域和漏极电极接触区域中的一方的棒状形状配置在源极电极接触区域和漏极电极接触区域中的另一方的梳齿形状之间。该半导体元件具有极化超结区域,该极化超结区域是形成有第三半导体层并且未形成有第四半导体层的区域中的位于栅极电极接触区域与漏极电极接触区域之间的区域。棒状形状的前端部分中的连接从源极电极接触区域至漏极电极接触区域的最短距离的方向的极化超结区域的长度为棒状形状的除前端部分以外的部分中的连接从源极电极接触区域至漏极电极接触区域的最短距离的方向的极化超结区域的长度以上。

[0461]

在第二方式的半导体元件中,棒状形状的前端部分为弧状的弧状部。棒状形状的除前端部分以外的部分为直线形状的棒状部。

[0462]

在第三方式的半导体元件中,棒状形状的前端部分中的连接从源极电极接触区域至漏极电极接触区域的最短距离的方向的极化超结区域的长度相对于棒状形状的除前端部分以外的部分中的连接从源极电极接触区域至漏极电极接触区域的最短距离的方向的极化超结区域的长度为1.05以上。

[0463]

在第四方式的半导体元件中,棒状形状的前端部分中的源极电极接触区域与漏极电极接触区域之间的距离为棒状形状的除前端部分以外的部分中的源极电极接触区域与漏极电极接触区域之间的距离以上。

[0464]

第五方式的半导体元件具有:第一半导体层;比第一半导体层靠上层的第二半导体层;比第二半导体层靠上层的第三半导体层;比第三半导体层靠上层的第四半导体层;第二半导体层之上的阴极电极;第四半导体层之上的阳极电极;阴极电极与第二半导体层接触的阴极电极接触区域;以及阳极电极与第四半导体层接触的阳极电极接触区域。第一半导体层、第二半导体层、第三半导体层及第四半导体层为iii族氮化物半导体层。第二半导体层的带隙大于第一半导体层及第三半导体层的带隙。第一半导体层、第二半导体层及第三半导体层为未掺杂的半导体层。第四半导体层为p型半导体层。阳极电极与第二半导体层或第一半导体层接触。阴极电极接触区域和阳极电极接触区域中的一方具有棒状形状。阴极电极接触区域和阳极电极接触区域中的另一方具有梳齿形状。阴极电极接触区域和阳极电极接触区域中的一方的棒状形状配置在阴极电极接触区域和阳极电极接触区域中的另一方的梳齿形状之间。该半导体元件具有极化超结区域,该极化超结区域是形成有第三半导体层并且未形成有第四半导体层的区域中的位于阴极电极接触区域与阳极电极接触区域之间的区域。棒状形状的前端部分中的连接从阴极电极接触区域至阳极电极接触区域的最短距离的方向的极化超结区域的长度为棒状形状的除前端部分以外的部分中的连接从阴极电极接触区域至阳极电极接触区域的最短距离的方向的极化超结区域的长度以上。

[0465]

第六方式的半导体元件具有从第四半导体层到达第二半导体层的第一凹部。阴极电极至少形成在第一凹部之上。

[0466]

在第七方式的半导体元件中,阴极电极与第一半导体层的侧面及第二半导体层的侧面接触。

[0467]

第八方式的半导体元件具有阳极电极与第四半导体层接触的阳极电极接触区域和从第四半导体层到达第一半导体层的第二凹部。阳极电极形成在第二凹部之上并且与第一半导体层或第二半导体层接触。

[0468]

第九方式的半导体元件在第三半导体层及第四半导体层与阳极电极之间具有绝缘层。

[0469]

第十方式的装置具有上述的半导体元件。

[0470]

4.第四

[0471]

第一方式的半导体元件具有:第一半导体层;比第一半导体层靠上层的第二半导体层;比第二半导体层靠上层的第三半导体层;比第三半导体层靠上层的第四半导体层;第二半导体层或第三半导体层之上的源极电极及漏极电极;第四半导体层之上的栅极电极;栅极电极与第四半导体层接触的栅极电极接触区域;源极电极与第二半导体层或第三半导体层接触的源极电极接触区域;漏极电极与第二半导体层或第三半导体层接触的漏极电极接触区域;以及从第四半导体层到达第二半导体层的第一凹部及第二凹部。第一半导体层、第二半导体层、第三半导体层及第四半导体层为iii族氮化物半导体层。第二半导体层的带隙大于第一半导体层及第三半导体层的带隙。第一半导体层、第二半导体层及第三半导体层为未掺杂的半导体层。第四半导体层为p型半导体层。源极电极形成在第一凹部之上。漏极电极形成在第二凹部之上。漏极电极接触区域与第三半导体层之间的距离大于源极电极接触区域与第三半导体层之间的距离。

[0472]

在第二方式的半导体元件中,漏极电极接触区域与第三半导体层之间的距离为10μm以下。

[0473]

在第三方式的半导体元件中,在将源极电极接触区域、漏极电极接触区域及栅极电极接触区域投影到第二半导体层的情况下,投影了漏极电极接触区域的区域与投影了栅极电极接触区域的区域之间的距离大于投影了源极电极接触区域的区域与投影了栅极电极接触区域的区域之间的距离。

[0474]

第四方式的半导体元件具有:第一半导体层;比第一半导体层靠上层的第二半导体层;比第二半导体层靠上层的第三半导体层;比第三半导体层靠上层的第四半导体层;第二半导体层之上的阴极电极;第四半导体层之上的阳极电极;以及阴极电极与第二半导体层接触的阴极电极接触区域。第一半导体层、第二半导体层、第三半导体层及第四半导体层为iii族氮化物半导体层。第二半导体层的带隙大于第一半导体层及第三半导体层的带隙。第一半导体层、第二半导体层及第三半导体层为未掺杂的半导体层。第四半导体层为p型半导体层。阴极电极接触区域与第三半导体层之间的距离为10μm以下。

[0475]

第五方式的半导体元件具有从第四半导体层到达第二半导体层的第一凹部。阴极电极至少形成在第一凹部之上。

[0476]

在第六方式的半导体元件中,阴极电极与第一半导体层的侧面及第二半导体层的侧面接触。

[0477]

第七方式的半导体元件具有:阳极电极与第四半导体层接触的阳极电极接触区域;和从第四半导体层到达第一半导体层的第二凹部。阳极电极形成在第二凹部之上并且与第一半导体层或第二半导体层接触。

[0478]

第八方式的半导体元件在第三半导体层及第四半导体层与阳极电极之间具有绝缘层。

[0479]

第九方式的装置具有上述的半导体元件。

[0480]

5.第五

[0481]

第一方式的半导体元件具有:第一半导体层;比第一半导体层靠上层的第二半导体层;比第二半导体层靠上层的第三半导体层;比第三半导体层靠上层的第四半导体层;第二半导体层或第三半导体层之上的源极电极及漏极电极;以及第四半导体层之上的栅极电极。第一半导体层、第二半导体层、第三半导体层及第四半导体层为iii族氮化物半导体层。第二半导体层的带隙大于第一半导体层及第三半导体层的带隙。第一半导体层、第二半导体层及第三半导体层为未掺杂的半导体层。第四半导体层为p型半导体层。栅极电极、源极电极及漏极电极中的至少一个具有接触电极、配线电极及焊盘电极。配线电极连结接触电极与焊盘电极。配线电极具有弯曲为弧状的弯曲部。

[0482]

在第二方式的半导体元件中,栅极电极、源极电极及漏极电极中的至少一个具有多个焊盘电极。

[0483]

在第三方式的半导体元件中,栅极电极、源极电极及漏极电极具有接触电极、配线电极及焊盘电极。该半导体元件在栅极电极的配线电极与源极电极的配线电极之间具有绝缘层。绝缘层具有第一绝缘层和第一绝缘层之上的第二绝缘层。

[0484]

在第四方式的半导体元件中,绝缘层具有无机电介质膜和有机电介质膜中的至少一方。

[0485]

在第五方式的半导体元件中,第一半导体层与第二半导体层直接接触。第一半导体层与第二半导体层接触的接触面的形状为长方形。

[0486]

第六方式的装置具有上述的半导体元件。

[0487]

6.第六

[0488]

第一方式的半导体元件具有:第一半导体层;比第一半导体层靠上层的第二半导体层;比第二半导体层靠上层的第三半导体层;比第三半导体层靠上层的第四半导体层;第二半导体层或第三半导体层之上的源极电极及漏极电极;以及第四半导体层之上的栅极电极。第一半导体层、第二半导体层、第三半导体层及第四半导体层为iii族氮化物半导体层。第二半导体层的带隙大于第一半导体层及第三半导体层的带隙。第一半导体层、第二半导体层及第三半导体层为未掺杂的半导体层。第四半导体层为p型半导体层。位错密度为1

×

106cm-2

以上且1

×

10

10

cm-2

以下。第二半导体层与第三半导体层之间的接触面积在栅极宽度方向的每1μm为10μm2以上且200μm2以下。

[0489]

在第二方式的半导体元件中,位错密度为5

×

109cm-2

以下。

[0490]

在第三方式的半导体元件中,第二半导体层与第三半导体层之间的接触面积和耐压满足下式

[0491]

101x-810≤y≤235x 585

[0492]

x:栅极宽度方向的每1μm的第二半导体层与第三半导体层之间的接触面积

[0493]

y:耐压。

[0494]

在第四方式的半导体元件中,连接从源极电极接触区域至漏极电极接触区域的最短距离的方向上的第四半导体层的长度亦即栅极长度为6μm以下。300v开关下的上升时间及下降时间均为30ns以下。

[0495]

第五方式的半导体元件具有上述的半导体元件。

[0496]

7.第七

[0497]

第一方式的半导体元件具有:第一半导体层;比第一半导体层靠上层的第二半导体层;比第二半导体层靠上层的第三半导体层;比第三半导体层靠上层的第四半导体层;第二半导体层或第三半导体层之上的源极电极及漏极电极;第四半导体层之上的栅极电极;源极电极与第二半导体层或第三半导体层接触的源极电极接触区域;以及漏极电极与第二半导体层或第三半导体层接触的漏极电极接触区域。第一半导体层、第二半导体层、第三半导体层及第四半导体层为iii族氮化物半导体层。第二半导体层的带隙大于第一半导体层及第三半导体层的带隙。第一半导体层、第二半导体层及第三半导体层为未掺杂的半导体层。第四半导体层为p型半导体层。该半导体元件具有极化超结区域,该极化超结区域是形成有第三半导体层并且未形成有第四半导体层的区域中的位于栅极电极接触区域与漏极电极接触区域之间的区域。连接从源极电极接触区域至漏极电极接触区域的最短距离的方向上的极化超结区域的长度亦即极化超结长度为50μm以下。连接从源极电极接触区域至漏极电极接触区域的最短距离的方向上的第四半导体层的长度亦即栅极长度为6μm以下。

[0498]

在第二方式的半导体元件中,标准化导通电阻为20mω

·

cm2以下。

[0499]

在第三方式的半导体元件中,300v开关下的上升时间及下降时间均为30ns以下。

[0500]

第四方式的装置具有上述的半导体元件。

[0501]

8.第八

[0502]

第一方式的半导体元件具有:第一半导体层;比第一半导体层靠上层的第二半导体层;比第二半导体层靠上层的第三半导体层;比第三半导体层靠上层的第四半导体层;第二半导体层或第三半导体层之上的源极电极及漏极电极;第四半导体层之上的栅极电极;源极电极与第二半导体层或第三半导体层接触的源极电极接触区域;以及漏极电极与第二半导体层或第三半导体层接触的漏极电极接触区域。第一半导体层、第二半导体层、第三半导体层及第四半导体层为iii族氮化物半导体层。第二半导体层的带隙大于第一半导体层及第三半导体层的带隙。第一半导体层、第二半导体层及第三半导体层为未掺杂的半导体层。第四半导体层为p型半导体层。从第二半导体层中的第三半导体层侧的面积减去源极电极接触区域及漏极电极接触区域的面积和夹在最外侧的源极电极接触区域与第二半导体层的外周部之间的区域的面积而得的有源区域面积为2.2mm2以上。

[0503]

在第二方式的半导体元件中,连接从源极电极接触区域至漏极电极接触区域的最短距离的方向上的第四半导体层的长度亦即栅极长度为6μm以下。

[0504]

在第三方式的半导体元件中,栅极宽度为300mm以上。

[0505]

在第四方式的半导体元件中,半导体元件的外周长度为13mm以上。

[0506]

在第五方式的半导体元件中,上升时间及下降时间均为30ns以下。

[0507]

在第六方式的半导体元件中,源极电极具有露出于元件外部的源极焊盘电极。漏极电极具有露出于元件外部的漏极焊盘电极。将源极焊盘电极及漏极焊盘电极投影到第二

半导体层而得的区域不与第二半导体层的形成区域重叠。

[0508]

第七方式的半导体元件具有上述的半导体元件。

[0509]

附图标记说明

[0510]

100...半导体元件;sub1...蓝宝石基板;bf1...缓冲层;110...第一半导体层;120...第二半导体层;130...第三半导体层;140...第四半导体层;s1...源极电极;sc1...源极电极接触区域;d1...漏极电极;dc1...漏极电极接触区域;g1...栅极电极;gc1...栅极电极接触区域。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。