一种基于risc-v架构的加密和解密装置

技术领域

1.本发明属于密码安全技术领域,更具体地,涉及一种基于risc-v架构的加密和解密装置。

背景技术:

2.无线链路传输加密主要用于实现无线通信的链路层加密保护,确保无线链路传输数据的安全。无线链路传输加密具有模块化、低功耗、小型化的特点,通常采用fpga和cpu架构,cpu完成配置和管理功能,fpga完成业务处理和加密功能。随着无线通信技术的发展,无线通信业务类型呈现多样化等发展趋势,对链路加密设备功能提出了更多的要求,要求能够支持单播、组播、点对点/点对多点、入网认证等多种密码功能,传统基于fpga的链路加密处理机制缺乏通用处理器的灵活性,设计、编程和调试复杂。

3.risc-v是一种基于精简指令集原则的开源指令集架构,具有架构简单、模块化设计、易于移植、完全开源等特点,目前广泛应用于物联网、数据中心、边缘计算等场景。基于risc-v架构的无线链路加密的装置和方法,结合rsic-v和fpga特点,基于risc-v处理器的灵活性,满足业务多样化的密码应用需求;基于fpga高性能,满足业务高带宽的加密需求,从而更好的满足无线通信的链路密码服务保障应用需求。

技术实现要素:

4.针对现有技术的缺陷,本发明的目的在于提供一种基于risc-v架构的加密和解密装置,旨在解决传统基于fpga的链路加密处理机制缺乏通用处理器的灵活性,设计、编程和调试复杂的问题。

5.为实现上述目的,第一方面,本发明提供了一种基于risc-v架构的链路加密装置,所述加密装置包括:内网侧预处理模块、risc-v处理器模块、算法处理模块及外网侧预处理模块;

6.所述内网侧预处理模块,对外连接至内网侧rapid io接口,对内通过axi stream接口连接至risc-v处理器,用于对明文数据进行初步判定,据此对数据进行组包和crc校验后,将数据包发送给risc-v处理器;

7.所述risc-v处理器包括:业务处理模块和控制管理模块;

8.所述业务处理模块,提供axi stream接口分别连接内网侧预处理模块、外网侧预处理模块和算法处理模块,提供axi ram接口连接至控制管理模块,用于通过解析从内网接收到的数据包中的字段并区分报文类型,将控制报文转发至控制管理模块,将数据报文转发给算法处理模块,将已加密业务数据解析后,将已加密业务数据转发至外网侧预处理模块;

9.所述控制管理模块,提供axi ram接口连接至业务处理模块,用于对控制报文进行协议解析和处理后,转发至算法处理模块,接收到算法处理模块返回的控制数据后,按照控制协议进行协议处理后,将数据通过业务处理模块发送至外网侧预处理模块;

10.所述算法处理模块,提供axi stream接口连接至业务处理模块,用于对控制数据进行加密和完整性保护,发回至控制管理模块,对业务数据加密处理后,将已加密数据发送至业务处理模块;

11.所述外网侧预处理模块,对外连接至外网侧rapid io接口,对内通过axi stream接口连接至risc-v处理器,用于完成基本信息判定后,据此对数据进行分片和crc计算,再将密文数据发送至外网侧用户接口。

12.优选地,整个加密装置基于fpga可编程逻辑器件实现,并采用fpga的ip核方式例化1个32位risc-v处理器。

13.优选地,所述内网侧预处理模块从rapid io接口接收到明文数据后,根据报文帧长度将多个rapid io接口帧数据进行组包,完成crc校验,校验通过后,通过axi stream接口将报文转发至risc-v中的业务逻辑处理模块对报文类型进行解析和处理,报文类型指示为数据报文时,将该报文转发至算法处理模块进行加密处理,并将加密后的密文数据通过axi stream转发至外网侧预处理模块。

14.优选地,所述外网侧预处理模块对报文进行crc计算并填充crc计算结果,并按照rapid io帧格式进行分片处理后通过rapid io接口发送至外网接口,从而完成业务加密处理。

15.优选地,所述加密装置支持rc4、aes加密算法。

16.为实现上述目的,第二方面,本发明提供了一种基于risc-v架构的链路解密装置,所述解密装置包括:外网侧预处理模块、risc-v处理器模块、算法处理模块及内网侧预处理模块;

17.所述外网侧预处理模块,对外连接至外网侧rapid io接口,对内通过axi stream接口连接至risc-v处理器,用于对密文数据进行初步判定,据此对数据进行组包和crc校验后,将数据包发送给risc-v处理器;

18.所述risc-v处理器包括:业务处理模块和控制管理模块;

19.所述业务处理模块,提供axi stream接口分别连接内网侧预处理模块、外网侧预处理模块和算法处理模块,提供axi ram接口连接至控制管理模块,用于通过解析从外网接收到的数据包中的字段并区分报文类型,将控制报文转发至控制管理模块,将数据报文转发给算法处理模块,将已解密业务数据解析后,将已解密业务数据转发至内网侧预处理模块;

20.所述控制管理模块,提供axi ram接口连接至业务处理模块,用于对控制报文进行协议解析和处理后,转发至算法处理模块,接收到算法处理模块返回的控制数据后,按照控制协议进行协议处理后,将数据通过业务处理模块发送至内网侧预处理模块;

21.所述算法处理模块,提供axi stream接口连接至业务处理模块,用于对控制数据进行解密保护,发回至控制管理模块,对业务数据解密处理后,将已解密数据发送至业务处理模块;

22.所述内网侧预处理模块,对外连接至内网侧rapid io接口,对内通过axi stream接口连接至risc-v处理器,用于完成基本信息判定后,据此对数据进行分片和crc计算,再将明文数据发送至内网侧用户接口。

23.优选地,整个装置基于fpga可编程逻辑器件实现,并采用fpga的ip核方式例化1个

32位risc-v处理器。

24.优选地,所述外网侧预处理模块从rapid io接口接收到密文数据后,根据报文帧长度将多个rapid io接口帧数据进行组包,完成crc校验,校验通过后,通过axi stream接口将报文转发至rsic-v中的业务逻辑处理模块对报文类型进行解析和处理,报文类型指示为数据报文时,将该报文转发至算法处理模块进行解密处理,并将解密后的明文数据通过axi stream转发至内网侧预处理模块。

25.优选地,所述内网侧预处理模块对报文进行crc计算并填充crc计算结果,并按照rapid io帧格式进行分片处理后通过rapid io接口发送至内网接口,从而完成业务解密处理。

26.优选地,所述解密装置支持rc4、aes解密算法。

27.总体而言,通过本发明所构思的以上技术方案与现有技术相比,具有以下有益效果:

28.本发明提出一种基于risc-v架构的加密和解密装置,结合fpga高性能和risc-v处理器灵活编程等特点,由risc-v处理器完成复杂业务逻辑解析和灵活编程处理,由fpga完成数据面加速处理和算法处理,兼具高性能、低功耗以及灵活性等特点;采用控制和业务转发分离的结构,业务数据通过内网预处理模块、业务逻辑处理模块、算法处理模块以及外网处理模块进行转发处理,提供高速的业务转发处理能力;控制数据主要通过控制管理模块进行处理,提供灵活业务逻辑处理能力,能够更好适应和满足各种无线通信业务的链路传输加密保障需求。

附图说明

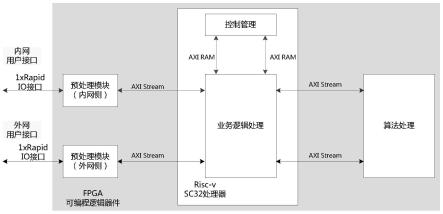

29.图1为本发明提供的加解密装置整体结构示意图。

30.图2为本发明提供的加密装置业务数据转发处理流向示意图。

31.图3为本发明提供的加密装置控制数据转发处理流向示意图。

具体实施方式

32.为了使本发明的目的、技术方案及优点更加清楚明白,以下结合附图及实施例,对本发明进行进一步详细说明。应当理解,此处所描述的具体实施例仅用以解释本发明,并不用于限定本发明。

33.如图1所示,本发明提供了一种基于risc-v架构的链路加密装置,所述加密装置包括:内网侧预处理模块、risc-v处理器模块、算法处理模块及外网侧预处理模块。

34.所述内网侧预处理模块,对外连接至内网侧rapid io接口,对内通过axi stream接口连接至risc-v处理器,用于对明文数据进行初步判定,据此对数据进行组包和crc校验后,将数据包发送给risc-v处理器。

35.优选地,所述内网侧预处理模块从rapid io接口接收到明文数据后,根据报文帧长度将多个rapid io接口帧数据进行组包,完成crc校验,校验通过后,通过axi stream接口将报文转发至risc-v中的业务逻辑处理模块对报文类型进行解析和处理,报文类型指示为数据报文时,将该报文转发至算法处理模块进行加密处理,并将加密后的密文数据通过axi stream转发至外网侧预处理模块。

36.所述risc-v处理器包括:业务处理模块和控制管理模块。

37.所述业务处理模块,提供axi stream接口分别连接内网侧预处理模块、外网侧预处理模块和算法处理模块,提供axi ram接口连接至控制管理模块,用于通过解析从内网接收到的数据包中的字段并区分报文类型,将控制报文转发至控制管理模块,将数据报文转发给算法处理模块,将已加密业务数据解析后,将已加密业务数据转发至外网侧预处理模块。

38.所述控制管理模块,提供axi ram接口连接至业务处理模块,用于对控制报文进行协议解析和处理后,转发至算法处理模块,接收到算法处理模块返回的控制数据后,按照控制协议进行协议处理后,将数据通过业务处理模块发送至外网侧预处理模块。

39.所述算法处理模块,提供axi stream接口连接至业务处理模块,用于对控制数据进行加密和完整性保护,发回至控制管理模块,对业务数据加密处理后,将已加密数据发送至业务处理模块。

40.优选地,所述加密装置支持rc4、aes加密算法。

41.所述外网侧预处理模块,对外连接至外网侧rapid io接口,对内通过axi stream接口连接至risc-v处理器,用于完成基本信息判定后,据此对数据进行分片和crc计算,再将密文数据发送至外网侧用户接口。

42.优选地,所述外网侧预处理模块对报文进行crc计算并填充crc计算结果,并按照rapid io帧格式进行分片处理后通过rapid io接口发送至外网接口,从而完成业务加密处理。

43.优选地,整个加密装置基于fpga可编程逻辑器件实现,并采用fpga的ip核方式例化1个32位risc-v处理器。

44.如图2所示,实线箭头表示数据接口通信关系,虚线箭头表示特征数据处理流向。加密装置的业务数据转发流向主要涉及预处理模块、业务逻辑处理模块以及算法处理模块等处理。以内网用户接口数据至外网用户接口数据加密转发流向为例,其数据转发过程如下:

45.(1)内网用户接口通过rapid io将用户业务数据发送至无线通信链路加密装置的内网侧预处理模块。

46.(2)内网侧预处理模块将待加密数据接收后,完成基本信息判定(如长度、包头等信息)等工作后,据此对数据进行分片、crc校验等处理后,将数据发送至业务逻辑处理模块。

47.(3)业务处理模块完成业务数据解析后,将待加密数据转发至算法处理模块进行加密处理。

48.(4)算法处理模块完成加密处理后,将已加密数据发送至业务处理模块。

49.(5)业务处理模块完成业务数据解析后,将接收的已加密数据转发至外网侧预处理模块。

50.(6)外网侧预处理模块将已加密数据接收后,完成基本信息判定(如长度、包头等信息)等工作后,据此对数据进行组包、crc计算等处理后,将数据发送至外网侧用户接口。

51.如图3所示,实线箭头表示数据接口通信关系,虚线箭头表示特征数据处理流向。加密装置的控制数据转发流向主要涉及预处理模块、业务逻辑处理模块、控制管理模块以

及算法处理模块等处理。以内网用户接口数据至外网用户接口控制数据转发流向为例,其数据转发过程如下:

52.(1)内网用户接口通过rapid io将控制数据发送至无线通信链路加密装置的内网侧预处理模块。

53.(2)内网侧预处理模块将待控制数据接收后,完成基本信息判定(如长度、包头等信息)等工作后,据此对数据进行分片、crc校验等处理后,将数据发送至业务逻辑处理模块。

54.(3)业务处理模块完成业务数据解析后,将控制数据转发至控制管理模块进行处理。

55.(4)控制管理模块完成对控制协议解析、处理后,将控制数据发送给算法处理模块,进行加密和完整性保护等处理。

56.(5)算法处理模块接收到控制数据后,进行加密和完整性保护处理后,将控制数据发回至控制管理模块。

57.(6)控制管理模块接收到已进行加密和完整性保护的控制数据后,按照控制协议进行协议处理后,将数据通过业务处理模块发送至外网侧预处理模块。

58.(7)外网侧预处理模块将已加密和完整性保护的控制数据接收后,完成基本信息判定(如长度、包头等信息)等工作后,据此对数据进行组包、crc计算等处理后,将控制数据发送至外网侧用户接口。

59.如图1所示,本发明提供了一种基于risc-v架构的链路解密装置,所述解密装置包括:外网侧预处理模块、risc-v处理器模块、算法处理模块及内网侧预处理模块。

60.所述外网侧预处理模块,对外连接至外网侧rapid io接口,对内通过axi stream接口连接至risc-v处理器,用于对密文数据进行初步判定,据此对数据进行组包和crc校验后,将数据包发送给risc-v处理器。

61.优选地,所述外网侧预处理模块从rapid io接口接收到密文数据后,根据报文帧长度将多个rapid io接口帧数据进行组包,完成crc校验,校验通过后,通过axi stream接口将报文转发至rsic-v中的业务逻辑处理模块对报文类型进行解析和处理,报文类型指示为数据报文时,将该报文转发至算法处理模块进行解密处理,并将解密后的明文数据通过axi stream转发至内网侧预处理模块。

62.所述risc-v处理器包括:业务处理模块和控制管理模块。

63.所述业务处理模块,提供axi stream接口分别连接内网侧预处理模块、外网侧预处理模块和算法处理模块,提供axi ram接口连接至控制管理模块,用于通过解析从外网接收到的数据包中的字段并区分报文类型,将控制报文转发至控制管理模块,将数据报文转发给算法处理模块,将已解密业务数据解析后,将已解密业务数据转发至内网侧预处理模块。

64.所述控制管理模块,提供axi ram接口连接至业务处理模块,用于对控制报文进行协议解析和处理后,转发至算法处理模块,接收到算法处理模块返回的控制数据后,按照控制协议进行协议处理后,将数据通过业务处理模块发送至内网侧预处理模块。

65.所述算法处理模块,提供axi stream接口连接至业务处理模块,用于对控制数据进行解密保护,发回至控制管理模块,对业务数据解密处理后,将已解密数据发送至业务处

理模块。

66.优选地,所述解密装置支持rc4、aes解密算法。

67.所述内网侧预处理模块,对外连接至内网侧rapid io接口,对内通过axi stream接口连接至risc-v处理器,用于完成基本信息判定后,据此对数据进行分片和crc计算,再将明文数据发送至内网侧用户接口。

68.优选地,所述内网侧预处理模块对报文进行crc计算并填充crc计算结果,并按照rapid io帧格式进行分片处理后通过rapid io接口发送至内网接口,从而完成业务解密处理。

69.优选地,整个装置基于fpga可编程逻辑器件实现,并采用fpga的ip核方式例化1个32位risc-v处理器。

70.本领域的技术人员容易理解,以上所述仅为本发明的较佳实施例而已,并不用以限制本发明,凡在本发明的精神和原则之内所作的任何修改、等同替换和改进等,均应包含在本发明的保护范围之内。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。