技术特征:

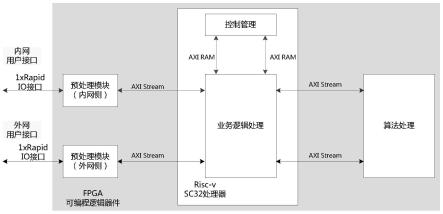

1.一种基于risc-v架构的链路加密装置,其特征在于,所述加密装置包括:内网侧预处理模块、risc-v处理器模块、算法处理模块及外网侧预处理模块;所述内网侧预处理模块,对外连接至内网侧rapid io接口,对内通过axi stream接口连接至risc-v处理器,用于对明文数据进行初步判定,据此对数据进行组包和crc校验后,将数据包发送给risc-v处理器;所述risc-v处理器包括:业务处理模块和控制管理模块;所述业务处理模块,提供axi stream接口分别连接内网侧预处理模块、外网侧预处理模块和算法处理模块,提供axi ram接口连接至控制管理模块,用于通过解析从内网接收到的数据包中的字段并区分报文类型,将控制报文转发至控制管理模块,将数据报文转发给算法处理模块,将已加密业务数据解析后,将已加密业务数据转发至外网侧预处理模块;所述控制管理模块,提供axi ram接口连接至业务处理模块,用于对控制报文进行协议解析和处理后,转发至算法处理模块,接收到算法处理模块返回的控制数据后,按照控制协议进行协议处理后,将数据通过业务处理模块发送至外网侧预处理模块;所述算法处理模块,提供axi stream接口连接至业务处理模块,用于对控制数据进行加密和完整性保护,发回至控制管理模块,对业务数据加密处理后,将已加密数据发送至业务处理模块;所述外网侧预处理模块,对外连接至外网侧rapid io接口,对内通过axi stream接口连接至risc-v处理器,用于完成基本信息判定后,据此对数据进行分片和crc计算,再将密文数据发送至外网侧用户接口。2.如权利要求1所述的加密装置,其特征在于,整个加密装置基于fpga可编程逻辑器件实现,并采用fpga的ip核方式例化1个32位risc-v处理器。3.如权利要求1所述的链路加密装置,其特征在于,所述内网侧预处理模块从rapid io接口接收到明文数据后,根据报文帧长度将多个rapid io接口帧数据进行组包,完成crc校验,校验通过后,通过axi stream接口将报文转发至risc-v中的业务逻辑处理模块对报文类型进行解析和处理,报文类型指示为数据报文时,将该报文转发至算法处理模块进行加密处理,并将加密后的密文数据通过axi stream转发至外网侧预处理模块。4.如权利要求1所述的加密装置,其特征在于,所述外网侧预处理模块对报文进行crc计算并填充crc计算结果,并按照rapid io帧格式进行分片处理后通过rapid io接口发送至外网接口,从而完成业务加密处理。5.如权利要求1所述的加密装置,其特征在于,所述加密装置支持rc4、aes加密算法。6.一种基于risc-v架构的链路解密装置,其特征在于,所述解密装置包括:外网侧预处理模块、risc-v处理器模块、算法处理模块及内网侧预处理模块;所述外网侧预处理模块,对外连接至外网侧rapid io接口,对内通过axi stream接口连接至risc-v处理器,用于对密文数据进行初步判定,据此对数据进行组包和crc校验后,将数据包发送给risc-v处理器;所述risc-v处理器包括:业务处理模块和控制管理模块;所述业务处理模块,提供axi stream接口分别连接内网侧预处理模块、外网侧预处理模块和算法处理模块,提供axi ram接口连接至控制管理模块,用于通过解析从外网接收到的数据包中的字段并区分报文类型,将控制报文转发至控制管理模块,将数据报文转发给

算法处理模块,将已解密业务数据解析后,将已解密业务数据转发至内网侧预处理模块;所述控制管理模块,提供axi ram接口连接至业务处理模块,用于对控制报文进行协议解析和处理后,转发至算法处理模块,接收到算法处理模块返回的控制数据后,按照控制协议进行协议处理后,将数据通过业务处理模块发送至内网侧预处理模块;所述算法处理模块,提供axi stream接口连接至业务处理模块,用于对控制数据进行解密保护,发回至控制管理模块,对业务数据解密处理后,将已解密数据发送至业务处理模块;所述内网侧预处理模块,对外连接至内网侧rapid io接口,对内通过axi stream接口连接至risc-v处理器,用于完成基本信息判定后,据此对数据进行分片和crc计算,再将明文数据发送至内网侧用户接口。7.如权利要求6所述的解密装置,其特征在于,整个装置基于fpga可编程逻辑器件实现,并采用fpga的ip核方式例化1个32位risc-v处理器。8.如权利要求6所述的解密装置,其特征在于,所述外网侧预处理模块从rapid io接口接收到密文数据后,根据报文帧长度将多个rapid io接口帧数据进行组包,完成crc校验,校验通过后,通过axi stream接口将报文转发至rsic-v中的业务逻辑处理模块对报文类型进行解析和处理,报文类型指示为数据报文时,将该报文转发至算法处理模块进行解密处理,并将解密后的明文数据通过axi stream转发至内网侧预处理模块。9.如权利要求6所述的解密装置,其特征在于,所述内网侧预处理模块对报文进行crc计算并填充crc计算结果,并按照rapid io帧格式进行分片处理后通过rapid io接口发送至内网接口,从而完成业务解密处理。10.如权利要求6所述的解密装置,其特征在于,所述解密装置支持rc4、aes解密算法。

技术总结

本发明公开了一种基于RISC-V架构的加密和解密装置,属于密码安全技术领域。本发明结合FPGA高性能和Risc-v处理器灵活编程等特点,由Risc-v处理器完成复杂业务逻辑解析和灵活编程处理,由FPGA完成数据面加速处理和算法处理,兼具高性能、低功耗以及灵活性等特点;采用控制和业务转发分离的结构,业务数据通过内网预处理模块、业务逻辑处理模块、算法处理模块以及外网处理模块进行转发处理,提供高速的业务转发处理能力;控制数据主要通过控制管理模块进行处理,提供灵活业务逻辑处理能力,能够更好适应和满足各种无线通信业务的链路传输加密保障需求。加密保障需求。加密保障需求。

技术研发人员:郑波 袁国材 潘鹏 王珒 叶耀文 祁小龙 闵清 金文 陈昊 项勃 张磊 沈洁萍

受保护的技术使用者:武汉船舶通信研究所(中国船舶重工集团公司第七二二研究所)

技术研发日:2022.11.23

技术公布日:2023/3/10

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。