1.本发明涉及一种半导体装置。

背景技术:

2.半导体装置包含功率器件,被用作电力转换装置。功率器件是开关元件。开关元件是例如igbt(insulated gate bipolar transistor:绝缘栅双极型晶体管)、功率mosfet(metal oxide semiconductor field effect transistor:金属氧化物半导体场效应晶体管)。半导体装置包括半导体芯片、以及绝缘电路基板,该半导体芯片包含功率器件。绝缘电路基板包括绝缘板、以及形成于绝缘板的正面且接合了半导体芯片的电路图案。另外,在绝缘电路基板上,半导体芯片与电路图案之间、半导体芯片与多个电路图案之间通过键合线电连接而形成期望的电路。另外,外部连接端子(引线框架)相对于电路图案而电连接。这样的半导体芯片、绝缘电路基板、键合线、外部连接端子的一部分被收纳于壳体并在壳体内填充密封部件(例如,参照专利文献1)。

3.现有技术文献

4.专利文献

5.专利文献1:国际公开第2016/084622号

技术实现要素:

6.技术问题

7.上述半导体装置所包含的作为开关元件的半导体芯片有时会产生振荡现象。特别地,在开关元件以宽带隙半导体为主要成分而构成时,容易更显著地产生振荡现象。若产生振荡现象,则导致半导体装置的可靠性降低。

8.本发明是鉴于这样的问题而做成的,其目的在于,提供一种减少振荡现象的产生的半导体装置。

9.技术方案

10.根据本发明的一个观点,提供一种半导体装置,所述半导体装置具备:多个第一半导体芯片,其在正面具备第一控制电极和第一输出电极,并且在背面具备第一输入电极;多个第二半导体芯片,其在正面具备第二控制电极和第二输出电极,并且在背面具备第二输入电极;第一输入电路图案,其供所述多个第一半导体芯片的所述第一输入电极配置;第一控制电路图案,其与所述第一控制电极电连接;第二输入电路图案,其供所述多个第二半导体芯片的所述第二输入电极配置;以及第二控制电路图案,其与所述第二控制电极电连接,所述第一控制电路图案经由第一电阻元件而配置在控制端子与所述第一控制电极之间,所述第二控制电路图案经由第二电阻元件而配置在所述控制端子与所述第二控制电极之间,至少一个所述第一输出电极与至少一个所述第二输出电极通过第一基板间布线部件而电连接。

11.技术效果

12.根据公开的技术,能够降低振荡现象的产生,并且能够抑制半导体装置的可靠性的降低。

附图说明

13.图1是第一实施方式的半导体装置的俯视图。

14.图2是第一实施方式的半导体装置所包含的电阻芯片的图。

15.图3是示出第一实施方式的半导体装置的控制侧的布线结构的图。

16.图4是示出第一实施方式的半导体装置的输出侧的布线结构的图。

17.图5是示出第一实施方式的半导体装置的等效电路的图。

18.图6是第一实施方式的变形例的半导体装置的主要部分俯视图。

19.图7是参考例的半导体装置的主要部分俯视图。

20.图8是第二实施方式的半导体装置的俯视图。

21.图9是示出第二实施方式的半导体装置的控制侧的布线结构的图。

22.图10是示出第二实施方式的半导体装置的等效电路的图。

23.符号说明

24.1、10 半导体装置

25.2、5、20a~20f 绝缘电路基板

26.3、6、21a~21f 绝缘板

27.3a~3d 第一边~第四边

28.4a~4e、4a1、7a~7e、22a1~22a8、22b1~22b8、22c1~22c8、22d1~22d8、22e1、22e2、22f1、22f2 电路图案

29.6a~6d 第五边~第八边

30.8a、8b 引线框架

31.8a1、8b1 布线部

32.8a2、8a3、8b2、8b3 脚部

33.9a1~9h1、9a2~9h2、9j、9k、40、40a~40d、41、42 引线

34.25 基底基板

35.30、31 半导体芯片

36.30a 控制电极

37.30b 输出电极

38.32 电阻芯片

39.32a、32d 电阻部

40.32b 正面电极

41.32c 背面电极

42.32e、32f 电极

具体实施方式

43.以下,参照附图,对实施方式进行说明。应予说明,在以下说明中,在图中的半导体装置中,“正面”和“上表面”是表示朝向上侧( z方向)的x-y面。同样地,在图中的半导体装

置中,“上”是表示上侧( z方向)的方向。在图中的半导体装置中,“背面”和“下表面”是表示朝向下侧(-z方向)的x-y面。同样地,在图中的半导体装置中,“下”是表示下侧(-z方向)的方向。根据需要,在其他附图中也表示相同的方向性。“正面”、“上表面”、“上”、“背面”、“下表面”、“下”、“侧面”仅仅是便于确定相对位置关系的表达而已,并不限定本发明的技术思想。例如,“上”和“下”不必须表示相对于地面的铅垂方向。即,“上”和“下”的方向不限于重力方向。另外,在以下说明中,“主要成分”表示包含80vol%以上的情况。

44.[第一实施方式]

[0045]

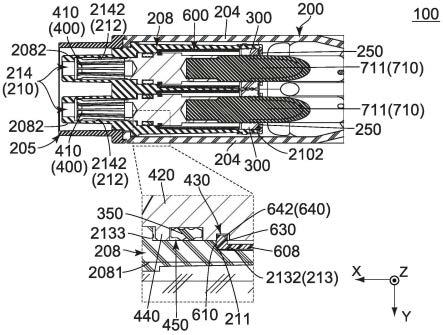

利用图1和图2对第一实施方式的半导体装置进行说明。图1是第一实施方式的半导体装置的俯视图。图2是第一实施方式的半导体装置所包括的电阻芯片的图。应予说明,图2的(a)表示纵型电阻芯片,图2的(b)表示横型电阻芯片。另外,图2的上侧是纵型电阻芯片、横型电阻芯片各自的俯视图,图2的下侧是上侧的图的单点划线x-x处的截面图。半导体装置1包括绝缘电路基板2、绝缘电路基板5、引线框架8a(控制端子)、引线框架8b、半导体芯片30、半导体芯片31以及电阻芯片32。半导体装置1如此构成一个臂。因此,半导体装置1可以包含上述那样的臂作为上臂,还包括相同结构的臂作为下臂。另外,绝缘电路基板2、5、半导体芯片30、31以及电阻芯片32之间通过引线而适当地电连接。

[0046]

半导体装置1相邻地配置有绝缘电路基板2、5。即,绝缘电路基板2、5如后所述那样,绝缘板3、6的第一边3a、第五边6a以及第三边3c、第七边6c形成同一平面,另外,绝缘板3的第二边3b和绝缘板6的第八边6d对置。应予说明,半导体装置1也可以在金属制的基底基板上经由焊料而配置绝缘电路基板2、5。另外,半导体装置1也可以利用壳体以使基底基板的背面露出的方式收纳基底基板上的绝缘电路基板2、5,另外,也可以利用密封部件来密封壳体内。或者,半导体装置1也可以不使用壳体,而利用密封部件以使基底基板的背面露出的方式密封基底基板上的绝缘电路基板2、5。

[0047]

如图1所示,绝缘电路基板2、5构成为,相对于第二边3b和第八边6d而彼此形成线对称。这样的绝缘电路基板2、5包括绝缘板3、6、形成于绝缘板3、6的正面的电路图案4a~4e、7a~7e、以及形成于绝缘板3、6的背面的金属板(省略图示)。应予说明,绝缘板3、6以及金属板在俯视下为矩形形状。特别地,绝缘板3、6依次被第一边~第四边3a~3d、第五边~第八边6a~6d包围。另外,绝缘板3、6以及金属板的角部可以被倒角为r形状、c形状。在俯视下,金属板的尺寸比绝缘板3、6的尺寸小,并且形成在绝缘板3、6的内侧。

[0048]

绝缘板3、6以导热性良好的陶瓷为主要成分而构成。该陶瓷由例如以氧化铝、氮化铝或氮化硅为主要成分的材料构成。另外,绝缘板3、6的厚度为0.2mm以上且2.5mm以下。

[0049]

金属板以导热性优良的金属为主要成分而构成。这样的金属是例如铜、铝或至少包括其中一种的合金。另外,金属板的厚度为0.1mm以上且5.0mm以下。为了提高耐腐蚀性,也可以对金属板的表面进行镀覆处理。此时,使用的镀覆材料列举出例如镍、镍-磷合金、镍-硼合金。

[0050]

电路图案4a~4e、7a~7e在俯视下分别呈尺寸不同的矩形形状。这样的电路图案4a~4e、7a~7e以导电性优良的金属为主要成分而构成。这样的金属列举出例如铜、铝或至少包括其中一种的合金。另外,电路图案4a~4e、7a~7e的厚度为0.1mm以上且5.0mm以下。为了提高耐腐蚀性,也可以对电路图案4a~4e、7a~7e的表面进行镀覆处理。此时,所使用的镀覆材料列举出例如镍、镍-磷合金、镍-硼合金。电路图案4a~4e、7a~7e通过在绝缘板

3、6的正面形成金属层,并对该金属层进行蚀刻等处理而获得。或者,也可以使预先从金属层切出的电路图案4a~4e、7a~7e压接在绝缘板3、6的正面而获得。应予说明,图1所示的电路图案4a~4e、7a~7e的形状、个数为一例。另外,被电路图案4d、7d、4e、7e所示的虚线包围的区域表示引线框架(外部连接端子)的接合部位。

[0051]

电路图案4a在绝缘板3的正面的第一边3a侧,沿着第二边3b而形成。电路图案4b在绝缘板3的正面的第一边3a侧,相对于电路图案4a而形成在第四边3d侧。即,电路图案4a、4b沿第一边3a而形成一列。

[0052]

电路图案7a在绝缘板6的正面的第五边6a侧,沿着第八边6d而形成。另外,电路图案7a与电路图案4a对置。电路图案7b在绝缘板6的正面的第五边6a侧,相对于电路图案7a而形成在第六边6b侧。即,电路图案7a、7b沿着第五边6a而形成一列。

[0053]

电路图案4c、7c在第三边3c、第七边6c侧与电路图案4a、4b、7a、7b相邻,并从第二边3b、第六边6b向第四边3d、第八边6d延伸而形成。电路图案4d、7d在第三边3c、第七边6c侧与电路图案4c、7c相邻,并从第二边3b、第六边6b向第四边3d、第八边6d延伸而形成。电路图案4e、7e在第三边3c、第七边6c侧与电路图案4d、7d相邻,并且沿着第三边3c、第七边6c从第二边3b、第六边6b向第四边3d、第八边6d延伸而形成。

[0054]

作为具有这样的结构的绝缘电路基板2、5,可以使用例如dcb(direct copper bonding:直接铜键合衬底)基板、amb(active metal brazed:活性金属钎焊)基板。绝缘电路基板2、5能够使由半导体芯片30、31产生的热量经由电路图案4d、7d、绝缘板3、6以及金属板而向外侧传导。

[0055]

半导体芯片30、31以硅为主要成分而构成。另外,半导体芯片30、31也可以以宽带隙半导体为主要成分而构成。宽带隙半导体列举出例如碳化硅、氮化镓。半导体芯片30是开关元件。开关元件是例如igbt、功率mosfet。这样的半导体芯片30在背面具备漏极或集电极作为输入电极(主电极)。另外,半导体芯片30在正面分别具备控制电极30a(栅极)、以及作为主电极的输出电极30b(源极或发射极)。对于上述半导体芯片30而言,其背面侧沿第一边3a、第五边6a和第三边3c、第七边6c通过接合材料(省略图示)而在电路图案4d、7d上接合有多个(例如两个)。应予说明,在图1中,半导体芯片30以使控制电极30a分别对置的方式设置在电路图案4d、7d上。或者,半导体芯片30也可以以使控制电极30a分别朝向第一边3a、第五边6a侧的方式设置。或者,半导体芯片30也可以以使控制电极30a分别朝向绝缘板3、6的第二边3b、第六边6b和第四边3d、第八边6d侧的方式设置。

[0056]

应予说明,接合材料是焊料或金属烧结体。焊料使用无铅焊料。无铅焊料以例如包含锡、银、铜、锌、锑、铟、铋中的至少两种的合金为主要成分。此外,焊料中也可以含有添加物。金属烧结体的材料以银或银合金为主要成分。另外,这样的接合材料也可以用于后述的半导体芯片31相对于电路图案4d、7d的接合。

[0057]

半导体芯片31包括二极管元件。二极管元件是例如sbd(schottky barrier diode:肖特基二极管)、pin(p-intrinsic-n)二极管的fwd(free wheeling diode:续流二极管)。这样的半导体芯片31在背面具备阴极作为背面负电极,在正面具备阳极作为正面正电极。对于上述半导体芯片31而言,其背面侧以与第一边3a、第五边6a和第三边3c、第七边6c平行且沿着半导体芯片30的方式通过接合材料(省略图示)而在电路图案4d、7d上接合多个(例如两个)。应予说明,也可以配置将开关元件和二极管元件作为一个半导体芯片的rc

(reverse conducting:反向导通)-igbt元件来代替半导体芯片30、31。

[0058]

电阻芯片32相对于电路图案4a、7a分别经由接合材料而接合于内侧。应予说明,接合材料如上所述。另外,在图2的(a)的下半部分(截面图),示出使电阻芯片32与电路图案4a接合的情况。如图2的(a)所示,在此使用的电阻芯片32为纵型,在俯视下呈矩形形状。这样的电阻芯片32具备电阻部32a、以及分别形成于电阻部32a的正面和背面的正面电极32b和背面电极32c。电阻部32a包含将后述的正面电极32b与背面电极32c连接的电阻材料。电阻部32a的厚度为0.1mm以上且5.0mm以下。电阻部32a的俯视下的一边的长度为0.1mm以上且10.0mm以下。另外,正面电极32b和背面电极32c以导电性优良的金属为主要成分而构成。这样的金属列举出例如铜、铝或至少包括其中一种的合金。正面电极32b和背面电极32c的厚度为0.1mm以上且5.0mm以下。在俯视下,正面电极32b和背面电极32c的尺寸比电阻部32a的尺寸小,并且形成在电阻部32a的内侧。

[0059]

另外,在图2的(b)中示出了横型的电阻芯片32。另外,在图2的(b)的下半部分(截面图),示出使电阻芯片32与电路图案4a、4b接合的情况。横型的电阻芯片32在立方体状的电阻部32d的两侧部分别形成有电极32e、32f。电阻部32d具备立方体状的陶瓷、设置在该陶瓷的正面的电阻膜、以及形成在电阻膜上的保护膜。电极32e、32f覆盖该陶瓷的两端,并且分别与电阻膜连接。应予说明,后面会对使用横型的电阻芯片32的情况进行描述。

[0060]

引线框架8a的一端侧与外部的控制装置等电连接,另一端侧与绝缘电路基板2、5连接。引线框架8a可以是控制端子。引线框架8a具备布线部8a1、以及与布线部8a1接合的脚部8a2、8a3。布线部8a1呈例如直线状。另外,布线部8a1的一端侧(图1中右侧)可以包括与外部的控制装置电连接的控制端子。在布线部8a1的另一端侧(图1中左侧)分别连接有脚部8a2、8a3。脚部8a2与电路图案4a的第二边3b侧接合。脚部8a3与电路图案7a的第八边6d侧接合。脚部8a2、8a3相对于电路图案4a、7a的接合能够使用上述的接合材料。或者,也可以通过超声波接合来接合。引线框架8a以导电性优良的金属为主要成分而构成。这样的金属列举出例如铜、铝或至少包括其中一种的合金。为了提高耐腐蚀性,也可以对引线框架8a的表面进行镀覆处理。此时,使用的镀覆材料列举出例如镍、镍-磷合金、镍-硼合金。因此,施加于引线框架8a的布线部8a1的一端侧的控制电流在布线部8a1流通,向脚部8a2、8a3分流而分别流向电路图案4a、7a。应予说明,不限于该情况,也可以相对于引线框架8a而另行具备控制端子。例如,也可以在布线部8a1的一端侧(图1中右侧)电连接有控制端子。即,从外部的控制装置施加的控制电流可以经由控制端子和引线框架8a、或者经由具备控制端子的引线框架8a而分别流向电路图案4a、7a。

[0061]

引线框架8b的一端侧与外部的控制装置等电连接,另一端侧与绝缘电路基板2、5连接。引线框架8b可以是感测端子。引线框架8b具备布线部8b1、以及与布线部8b1接合的脚部8b2、8b3。布线部8b1呈例如直线状。另外,布线部8b1的一端侧(图1中右侧)可以包括与外部的控制装置电连接的控制端子。在布线部8b1的另一端侧(图1中左侧)分别连接有脚部8b2、8b3。脚部8b2与电路图案4c的第二边3b侧接合。脚部8b3与电路图案7c的第八边6d侧接合。脚部8b2、8b3相对于电路图案4c、7c的接合能够使用上述接合材料。或者,也可以通过超声波接合来接合。引线框架8b可以由与引线框架8a相同的材料构成。因此,从绝缘电路基板2、5各自的半导体芯片30的输出电极30b(源极)输出的感测电流经由引线9d1、9e1、9d2、9e2以及电路图案4c、7c而在脚部8b2、8b3流通,进而在布线部8b1流通,从而向外部的控制装置

等输出。应予说明,不限于该情况,也可以相对于引线框架8b而另行具备具备感测端子。例如,在布线部8b1的一端侧(图1中右侧)也可以电连接有感测端子。

[0062]

针对这样的绝缘电路基板2、5、半导体芯片30、31以及电阻芯片32而布线有引线9a1~9h1、9a2~9h2、9j。首先,对控制用的布线进行说明。引线9a1、9a2将电阻芯片32的正面电极与电路图案4b、7b直接连接。另外,引线9b1、9c1、9b2、9c2将电路图案4b、7b与半导体芯片30的控制电极30a直接连接。这样的控制用的引线9a1~9c1、9a2~9c2的直径为例如25μm以上且400μm以下。

[0063]

接下来,对感测用的引线进行说明。感测用的引线9d1、9e1、9d2、9e2将半导体芯片30的输出电极30b与电路图案4c、7c直接连接。这样的检测用的引线9d1、9e1、9d2、9e2的直径为例如25μm以上且400μm以下。这些检测用的引线9d1、9e1、9d2、9e2可以是与控制用的引线9a1~9c1、9a2~9c2相同的直径。

[0064]

对主电流用的布线进行说明。引线9f1、9g1、9f2、9g2将半导体芯片30的输出电极30b、半导体芯片31的正面正电极以及电路图案4e、7e直接连接。主电流用的引线9f1、9g1、9f2、9g2的直径为100μm以上且600μm以下。

[0065]

另外,在绝缘电路基板2、5内,引线9h1、9h2将半导体芯片30的输出电极30b之间直接连接。此外,引线9j横跨绝缘电路基板2、5而将绝缘电路基板2、5各自的半导体芯片30的输出电极30b之间直接连接。这些引线9h1、9h2、9j的直径为25μm以上且400μm以下。这些引线9h1、9h2、9j可以是与控制用的引线9a1~9c1、9a2~9c2相同的直径。

[0066]

接下来,利用图3和图4,对从半导体装置1的引线框架8a(布线部8a1)起到绝缘电路基板2、5的半导体芯片30的控制电极30a为止的控制(栅极)侧的布线结构、以及从半导体芯片30的输出电极30b起到输出端子为止的输出(源极)侧的布线结构进行说明。图3是示出第一实施方式的半导体装置的控制侧的布线结构的图,图4是示出第一实施方式的半导体装置的输出侧的布线结构的图。应予说明,在图4中,相对于半导体装置1所包括的半导体芯片30的输出侧的布线结构,还一并示出控制侧的布线结构以及后述的半导体装置1的等效电路。

[0067]

应予说明,图3中的电阻rx是从通电时的控制端子起,通过引线框架8a的布线部8a1而分支到脚部8a2、8a3为止的电阻(布线电阻)。即,电阻rx是引线框架8a的电阻。另外,图4中的电阻rz是通电时的输出端子的布线电阻。应予说明,在图4中,省略了从输出端子起到配置有输出端子的电路图案为止的布线的图示。电阻ra是将绝缘电路基板2所包括的电路图案4a、引线9a1、电路图案4b的布线电阻以及电阻芯片32的电阻相加而得的电阻。另外,电阻rb是将绝缘电路基板5所包括的电路图案7a、引线9a2、电路图案7b的布线电阻以及电阻芯片32的电阻相加而得的电阻。应予说明,电阻芯片32的电阻值比各布线电阻大。

[0068]

电阻ra1和电阻ra2是从电路图案4b起到绝缘电路基板2的半导体芯片30的控制电极30a为止的布线电阻。即,电阻ra1是引线9b1的布线电阻。同样地,电阻ra2是引线9c1的布线电阻。

[0069]

电阻ra3和电阻ra4是从绝缘电路基板2的不同的半导体芯片30的输出电极30b起到绝缘电路基板2的电路图案4e为止的布线电阻。即,电阻ra3和电阻ra4是引线9f1、9g1的布线电阻。电阻ra5是从电路图案4e起到省略图示的输出端子为止的布线电阻。

[0070]

电阻rb1和电阻rb2是从电路图案7b起到绝缘电路基板5的半导体芯片30的控制电

极30a为止的通电时的布线电阻。即,电阻rb1是引线9b2的布线电阻。电阻ra2是引线9c2的布线电阻。

[0071]

电阻rb3和电阻rb4是从绝缘电路基板5的不同的半导体芯片30的输出电极30b起到绝缘电路基板5的电路图案7e为止的布线电阻。即,电阻rb3和电阻rb4是引线9f2、9g2的布线电阻。电阻rb5是从电路图案7e起到省略图示的输出端子为止的布线电阻。

[0072]

另外,分别设置于绝缘电路基板2、5的电阻芯片32的电阻使用比从引线框架8a起到电阻芯片32为止的电阻rx(以及输出端子的电阻rz)大且比电阻ra1~ra5、rb1~rb5大的电阻。这样的电阻芯片32的电阻优选为10ω以上且100ω以下,更优选为30ω以上且50ω以下。

[0073]

在这样的半导体装置1中,首先,对没有电阻芯片32的情况进行说明。在该情况下,考虑为了导通(或关断)而使针对引线框架8a的控制电压成为导通(或关断)之时。在该情况下,由于因从控制端子起的路径的不同而引起的布线电阻以及电感的差,所以在多个半导体芯片30的上升时间(或下降时间)上出现差。由此,在多个半导体芯片30中从输出电极30b(源极)输出的电压产生时间差。该电流经由感测用的引线9d1、9e1、9d2、9e2、电路图案4c、7c、引线框架8b,成为紊乱的电压而被向外部的控制装置输出。由此,有可能导致产生振荡现象,并使绝缘电路基板2、5的半导体芯片30引起误动作。

[0074]

另一方面,半导体装置1的绝缘电路基板2、5分别设置有电阻芯片32。在该情况下,从控制端子起的布线电阻以及电感的相对差(各个半导体芯片30的布线电阻或者电感相对于标准的布线电阻或者电感的相对比)小。在上述情况下,在使针对引线框架8a的控制电压成为导通(或关断)时,能够抑制多个半导体芯片30的上升时间(或下降时间)的差。由此,输出电极30b(源极)的电压不会紊乱。因此,能够向外部的控制装置输出稳定的电压。因此,在配置于后述的不同的绝缘电路基板2、5的半导体芯片30的输出电极30b间的电位被均匀化的情况下,通过配置电阻芯片32,抑制振荡现象以及由其引起的误动作的产生。

[0075]

接下来,利用图5和图1对半导体装置1所包括的等效电路进行说明。图5是示出第一实施方式的半导体装置的等效电路的图。应予说明,在图5中,作为半导体芯片30,示出功率mosfet的情况。另外,图5中的上方对应于绝缘电路基板2,图5中的下方对应于绝缘电路基板5。

[0076]

在绝缘电路基板2的电路图案4d并联连接有半导体芯片30的背面的输入电极(漏极)以及半导体芯片31的背面负电极。另外,半导体芯片30的输出电极30b(源极)以及半导体芯片31的正面正电极经由引线9f1、9g1而与电路图案4e连接。此外,半导体芯片30的输出电极30b之间通过引线9h1而直接连接。

[0077]

在绝缘电路基板5的电路图案7d并联连接有半导体芯片30的背面的输入电极(漏极)以及半导体芯片31的背面负电极。另外,半导体芯片30的正面的输出电极(源极)以及半导体芯片31的正面正电极经由引线9f2、9g2而与电路图案7e连接。此外,半导体芯片30的输出电极30b之间通过引线9h2而直接连接。

[0078]

此外,在半导体装置1中,绝缘电路基板2的半导体芯片30的输出电极30b与绝缘电路基板5的半导体芯片30的输出电极30b通过引线9j而直接连接。

[0079]

在这样的半导体装置1中,首先,对不设置引线9h1、9h2、9j的情况进行说明。在该情况下,认为设置于绝缘电路基板2的两个半导体芯片30的输出电极30b(源极)间的电感值

根据路径而变大。另外,同样地,认为设置于绝缘电路基板5的两个半导体芯片30的输出电极30b间的电感值也根据路径而变大。在这样的情况下,半导体装置1有时在导通(或关断)时半导体芯片30的控制电极30a-输出电极30b(栅极-源极)间的电位紊乱而导致振荡。

[0080]

特别地,绝缘电路基板2的半导体芯片30与绝缘电路基板5的半导体芯片30之间并联连接。绝缘电路基板2的半导体芯片30的输出电极30b和绝缘电路基板5的半导体芯片30的输出电极30b电连接于半导体装置1所包括的引线框架8b或输出端子(省略图示)。因此,绝缘电路基板2的半导体芯片30的输出电极30b与绝缘电路基板5的半导体芯片30的输出电极30b之间的布线长度比配置于相同的绝缘电路基板2(或绝缘电路基板5)的半导体芯片30的输出电极30b间的布线长度长。因此,配置于不同的绝缘电路基板2、5的半导体芯片30的输出电极30b间经由大的电感而连接。因此,有时会产生半导体芯片30的振荡现象。

[0081]

另一方面,对半导体装置1利用引线9j将绝缘电路基板2的半导体芯片30的输出电极30b与绝缘电路基板5的半导体芯片30的输出电极30b连接的情况进行说明。通过利用引线9j将分别配置于这些不同的绝缘电路基板2、5的半导体芯片30的输出电极30b间直接连接,从而使它们之间的电位均匀化。由此,能够从输出电极30b(源极)向外部的控制装置输出稳定的电压。因此,如利用图3说明的那样,在半导体芯片30的控制电极30a的布线电阻以及电感的偏差小的情况下,利用引线9j将分别配置于不同的绝缘电路基板2、5的半导体芯片30的输出电极30b间连接,从而抑制振荡现象以及由其引起的误动作的产生。

[0082]

在半导体装置1中,在绝缘电路基板2、5分别设置有电阻芯片32,并且未利用引线9j将绝缘电路基板2的半导体芯片30的输出电极30b与绝缘电路基板5的半导体芯片30的输出电极30b连接的情况下,进行如下考虑。利用电阻芯片32,能够减小配置在绝缘电路基板2内的半导体芯片30的控制电极30a以及配置在绝缘电路基板5内的半导体芯片30的控制电极30a中的、从各控制端子起的布线电阻以及电感的相对差。另一方面,在分别配置于不同的绝缘电路基板2、5的半导体芯片30的控制电极30a,有时因电阻芯片32的电阻值的偏差而产生从控制端子起的布线电阻以及电感的相对差。

[0083]

因此,在绝缘电路基板2、5分别设置有电阻芯片32的情况下,通过利用引线9j将分别配置于不同的绝缘电路基板2、5的半导体芯片30的输出电极30b之间连接,从而使不同的绝缘电路基板2、5的输出电位均匀化。通过如此地操作,能够抑制振荡现象以及由其引起的误动作的产生。

[0084]

此外,对设置引线9h1、9h2的情况进行说明。利用引线9h1将绝缘电路基板2的半导体芯片30的输出电极30b之间直接连接,从而使输出电极30b间的电位均匀化,抑制了电感值的增加。另外,同样地,利用引线9h2将绝缘电路基板5的半导体芯片30的输出电极30b之间直接连接,从而使输出电极30b间的电位均匀化,进而,抑制了振荡现象以及由其引起的误动作的产生。

[0085]

如此,在半导体装置1中,通过利用引线9h1、9h2、9j来连接,从而能够降低绝缘电路基板2的半导体芯片30的输出电极30b之间的电感值、绝缘电路基板5的半导体芯片30的输出电极30b之间的电感值、以及绝缘电路基板2的半导体芯片30的输出电极30b与绝缘电路基板5的半导体芯片30的输出电极30b之间的电感值。其结果是,能够降低半导体装置1的半导体芯片30的振荡现象。

[0086]

上述半导体装置1具备半导体芯片30、以及分别设置有半导体芯片30的绝缘电路

基板2、5。半导体芯片30在正面具备控制电极30a和输出电极30b,在背面具备输入电极。绝缘电路基板2、5包括绝缘板3、6、形成于绝缘板的正面并且配置有半导体芯片30的输入电极的电路图案4d、7d(输入电路图案)以及与控制电极30a电连接的电路图案4b、7b(控制电路图案)。此时,在半导体装置1中,电路图案4b、7b经由电阻芯片32而在电路图案4b、7b与控制电极30a之间分别施加控制电压,通过引线9j(第一基板间布线部件),将绝缘电路基板2的半导体芯片30的输出电极30b与绝缘电路基板5的半导体芯片30的输出电极30b电连接。

[0087]

半导体装置1利用电阻芯片32来减小从控制端子起到控制电极30a为止的布线电阻以及电感的相对差。在使针对控制电极30a的控制电压成为导通(或关断)时,能够抑制多个半导体芯片30的上升时间(或下降时间)的差。由此,输出电极30b(源极)的电压不会紊乱。因此,能够向外部的控制装置输出稳定的电压。此外,半导体装置1利用引线9j使配置于不同的绝缘电路基板2、5的半导体芯片30的输出电极30b间的电位均匀化。由此,能够从输出电极30b(源极)向外部的控制装置稳定地输出电压。因此,半导体装置1能够抑制振荡现象以及由其引起的误动作的产生,并且能够抑制可靠性的降低。此外,半导体装置1通过在同一绝缘电路基板2、5利用引线9h1、9h2将半导体芯片30的输出电极30b之间直接连接,从而使输出电极30b间的电位均匀化,抑制电感值的增加。因此,能够进一步抑制半导体装置1的振荡现象以及由其引起的误操作的产生。

[0088]

在图1的半导体装置1中,只不过示例出使用绝缘电路基板2、5的情况。只要构成图5所示的等效电路,电路图案4a~4e、7a~7e也可以不是必须形成于绝缘板3、6。另外,图1的半导体装置1的电阻芯片32的配置是一个例子而已,不限于该情况。在以下的变形例中,利用图6,对与图1的半导体装置1相同地有助于抑制振荡现象的电阻芯片32以及配置有电阻芯片32的电路图案的其他方式进行说明。图6是第一实施方式的变形例的半导体装置的主要部件俯视图。应予说明,图6的(a)示出变形例1-1中的电阻芯片32的周围。另外,图6的(b)示出后述的变形例1-2中的电阻芯片32的周围。

[0089]

另外,在图6中,示出绝缘电路基板2的第一边3a侧。在图6中,示出在图1的绝缘电路基板2中去除了电路图案4c的情况。与此相对的绝缘电路基板5的电路图案也构成为,在与图1相同地相对于绝缘电路基板2配置时,相对于第二边3b和第八边6d而与图6的绝缘电路基板2的电路图案呈线对称。另外,此时的绝缘电路基板5也被去除了电路图案7c。

[0090]

(变形例1-1)

[0091]

在图6的(a)的绝缘电路基板2中,形成有电路图案4a1来代替图1的电路图案4a、4b。电路图案4a1具备与电路图案4a、4b相同的宽度,在第一边3a侧从第二边3b向第四边3d延伸而形成。另外,在电路图案4a1的第二边3b侧设置有电阻芯片32。在电阻芯片32的正面电极直接连接有引线框架8a。另外,引线9b1、9c1分别将电路图案4a1与半导体芯片30的控制电极30a直接连接。即,电阻芯片32的背面电极与半导体芯片30的控制电极30a电连接。

[0092]

这样的绝缘电路基板2在引线框架8a与半导体芯片30的控制电极30a之间包含电阻芯片32、电路图案4a1以及引线9b1、9c1。若与图1的绝缘电路基板2相比,能够减少一个电路图案。能够比图1的绝缘电路基板2更容易形成,并且能够削减制造成本。在该情况下,也能够与图1的半导体装置1相同地抑制振荡现象的产生,并且能够抑制半导体装置1的可靠性的降低。

[0093]

(变形例1-2)

[0094]

在图6的(b)的绝缘电路基板2中,在图1的绝缘电路基板2,横跨电路图案4a、4b的间隙而设置有横型的电阻芯片32来代替纵型的电阻芯片32(图2的(b))。此时,电阻芯片32的一个端部与电路图案4a的端部(第四边3d侧)直接连接,电阻芯片32的另一个端部与电路图案4b的端部(第二边3b侧)直接连接(参照图2的(b)的下半部分(截面图))。即,电阻芯片32的另一个电极与半导体芯片30的控制电极30a电连接,电阻芯片32的一个电极与引线框架8a电连接。与图1的半导体装置1同样地,能够抑制振荡现象的产生,并且能够抑制半导体装置1的可靠性的降低。

[0095]

(参考例)

[0096]

在此,利用图7对针对图1、图6的参考例进行说明。图7是参考例的半导体装置的主要部分俯视图。参考例的绝缘电路基板2在图1的绝缘电路基板2中去除了电路图案4b、4c。另外,在参考例的绝缘电路基板2中,从图1的绝缘电路基板2中去除电路图案4b。因此,利用引线9k通过针脚接合将电阻芯片32的正面电极与半导体芯片30的控制电极30a之间直接连接。然而,在该情况下,导致从电阻芯片32起到各半导体芯片30的控制电极30a为止的布线长不同。与这样的布线长的不同相对应地,导致从电阻芯片32起到各半导体芯片30为止的布线电阻以及电感不同。因此,与图1和图6的情况相比,不能可靠地抑制振荡现象。因此,针对半导体芯片30的控制电极30a,优选不通过引线从电阻芯片32直接连接,而是经由电路图案分别连接。

[0097]

[第二实施方式]

[0098]

接下来,利用图8对第二实施方式进行说明。图8是第二实施方式的半导体装置的俯视图。在图8中,设置有与第一实施方式相同的半导体芯片30、31。其中,示出了第二实施方式的半导体芯片30是功率mosfet的情况。另外,除引线40a~40d、41、42以外,都作为引线40而进行说明。另外,图8中的图案中的被四边形包围的区域表示引线框架所连接的部位。

[0099]

半导体装置10具备基底基板25、利用上述接合材料而与基底基板25的正面接合的绝缘电路基板20a~20d、半导体芯片30、31以及引线40、40a~40d、41、42。半导体装置10也可以将它们收纳于壳体并利用密封部件来密封壳体内。或者,半导体装置10也可以不使用壳体,而利用密封部件以使基底基板的背面露出的方式密封基底基板上的绝缘电路基板20a~20d。应予说明,半导体装置10利用绝缘电路基板20a、20b构成上臂,并且利用绝缘电路基板20c、20d构成下臂。

[0100]

基底基板25以导热性优良的金属为主要成分而构成。这样的金属是例如铜、铝或至少包括其中一种的合金。另外,金属板的厚度为5.0mm以上且10.0mm以下。如图8所示,基底基板25在俯视下是绝缘电路基板20a~20d能够以两行两列的方式配置并且绝缘电路基板20e、20f能够在基底基板25的右侧的短边与绝缘电路基板20a、20b之间排列的面积。为了提高耐腐蚀性,也可以对基底基板25的表面进行镀覆处理。此时,所使用的镀覆材料列举出例如镍、镍-磷合金、镍-硼合金。

[0101]

绝缘电路基板20a~20f包括绝缘板21a~21f、形成于绝缘板21a~21f的正面的电路图案22a1~22a8、22b1~22b8、22c1~22c8、22d1~22d8、22e1~22e2、22f1~22f2、以及形成于绝缘板21a~21f的背面的金属板(省略图示)。应予说明,绝缘板21a~21f以及金属板的角部也可以被倒角为r形状、c形状。金属板的尺寸在俯视下比绝缘板21a~21f的尺寸小,并且形成于绝缘板21a~21f的内侧。

[0102]

绝缘板21a~21f以导热性良好的陶瓷为主要成分而构成。该陶瓷由例如以氧化铝、氮化铝或氮化硅为主要成分的材料构成。另外,绝缘板21a~21f的厚度为0.2mm以上且2.5mm以下。

[0103]

金属板以导热性优良的金属为主要成分而构成。这样的金属是例如铜、铝或至少包括其中一种的合金。另外,金属板的厚度为0.1mm以上且5.0mm以下。为了提高耐腐蚀性,也可以对金属板的表面进行镀覆处理。此时,使用的镀覆材料列举出例如镍、镍-磷合金、镍-硼合金。

[0104]

电路图案22a1~22a8、22b1~22b8、22c1~22c8、22d1~22d8、22e1~22e2、22f1~22f2在俯视下分别呈尺寸不同的矩形形状。这样的电路图案22a1~22a8、22b1~22b8、22c1~22c8、22d1~22d8、22e1~22e2、22f1~22f2以导电性优良的金属为主要成分而构成。这样的金属列举出例如铜、铝或至少包括其中一种的合金。另外,电路图案22a1~22a8、22b1~22b8、22c1~22c8、22d1~22d8、22e1~22e2、22f1~22f2的厚度为0.1mm以上且5.0mm以下。为了提高耐腐蚀性,也可以对电路图案22a1~22a8、22b1~22b8、22c1~22c8、22d1~22d8、22e1~22e2、22f1~22f2的表面进行镀覆处理。此时,所使用的镀覆材料列举出例如镍、镍-磷合金、镍-硼合金。电路图案22a1~22a8、22b1~22b8、22c1~22c8、22d1~22d8、22e1~22e2、22f1~22f2的绝缘板21a~21f以与第一实施方式相同的方式形成。

[0105]

电路图案22a6、22b6沿绝缘板21a、21b的图中右侧的短边的中央部而形成。电路图案22a8、22b8沿绝缘板21a、21b的图中左侧的短边的中央部而形成。电路图案22a7、22b7的图中右侧包围电路图案22a6、22b6的周围的一半左右,并向图中左侧延伸。另外,在电路图案22a7、22b7的图中左侧,包围电路图案22a8、22b8的除图中左侧的边以外的周围。

[0106]

另外,如图8所示,电路图案22a1、22a5、22b1、22b5在绝缘板21a、21b的图中右侧的角部形成为l字状。如图8所示,电路图案22a2、22a4、22b2、22b4以与电路图案22a8、22b8的短边平行的方式直线状地形成在绝缘板21a、21b的外周缘。电路图案22a3、22b3沿绝缘板21a、21b的图中左侧而形成为u字状。

[0107]

电路图案22c6、22d6沿绝缘板21c、21d的图中左侧的短边的中央部而形成。电路图案22c8、22d8沿绝缘板21c、21d的图中右侧的短边的中央部而形成。电路图案22c7、22d7的图中左侧包围电路图案22c6、22d6的周围的一半左右,并向图中右侧延伸。另外,电路图案22c7、22d7的图中右侧包围电路图案22c8、22d8的除图中右侧的边以外的周围。

[0108]

另外,如图8所示,电路图案22c1、22c5、22d1、22d5在绝缘板21c、21d的图中左侧的角部形成为l字状。如图8所示,电路图案22c2、22c4、22d2、22d4以与电路图案22c8、22d8的短边平行的方式直线状地形成在绝缘板21c、21d的外周缘。电路图案22c3、22d3沿绝缘板21c、21d的图中右侧而形成为u字状。电路图案22e1、22e2、22f1、22f2在绝缘板21e、21f的正面,在俯视下形成为上下各一半。

[0109]

作为具有这样的结构的绝缘电路基板20a~20f,可以使用例如dcb基板、amb基板。绝缘电路基板20a~20d能够使由半导体芯片30、31产生的热量经由电路图案22a7、22b7、22c7、22d7、绝缘板21a~21d以及金属板而向外侧传导。

[0110]

半导体芯片30、31和电阻芯片32是如第一实施方式中所说明的那样。应予说明,电阻芯片32使用纵型。半导体芯片30的背面的输入电极与绝缘电路基板20a~20d的电路图案22a7、22b7、22c7、22d7接合。半导体芯片31的背面负电极与绝缘电路基板20a~20d的电路

图案22a7、22b7、22c7、22d7接合。电阻芯片32的背面电极与绝缘电路基板20a~20d的电路图案22a6、22b6、22c6、22d6接合。

[0111]

省略图示的引线框架由与第一实施方式相同的材质构成。引线框架分别与绝缘电路基板20a~20f所示的四边形的区域接合。即,作为g2、g1端子的引线框架分别与绝缘电路基板20e、20f的电路图案22e1、22f1接合。另外,作为s2、s1端子的引线框架分别与绝缘电路基板20e、20f的电路图案22e2、22f2接合。另外,作为d1端子的引线框架与绝缘电路基板20a、20b的电路图案22a7、22b7接合。作为s2端子的引线框架与绝缘电路基板20c、20d的电路图案22c8、22d8接合。作为d2s1端子的引线框架与绝缘电路基板20c、20d的电路图案22c7、22d7接合。

[0112]

控制用的引线40将电路图案22e1、22a1直接连接。控制用的引线40将电路图案22a1、22a2、22c2、22c1直接连接。控制用的引线40将电路图案22c1、22c6以及电阻芯片32直接连接。控制用的引线40将电路图案22c6以及绝缘电路基板20c的半导体芯片30的控制电极30a直接连接。此外,控制用的引线40将电路图案22c1、22c5、22d1以及电阻芯片32直接连接。

[0113]

另外,控制用的引线40将电路图案22f1、22b5直接连接。控制用的引线40将电路图案22b5和电阻芯片32直接连接。控制用的引线40将电路图案22b6与绝缘电路基板20b的半导体芯片30的控制电极30a直接连接。此外,控制用的引线40将绝缘电路基板20b的电阻芯片32与绝缘电路基板20a的电阻芯片32直接连接。控制用的引线40将电路图案22b6与绝缘电路基板20b的半导体芯片30的控制电极30a直接连接。这样的控制用的引线40的直径为例如25μm以上且400μm以下。

[0114]

主电流用的引线40将绝缘电路基板20a的半导体芯片30的输出电极30b、半导体芯片31的正面正电极、以及电路图案22a8直接连接。主电流用的引线40将电路图案22a8、22c7直接连接。主电流用的引线40将绝缘电路基板20c的半导体芯片30的输出电极30b、半导体芯片31的正面正电极以及电路图案22c8直接连接。

[0115]

主电流用的引线40将绝缘电路基板20b的半导体芯片30的输出电极30b、半导体芯片31的正面正电极以及电路图案22b8直接连接。主电流用的引线40将电路图案22b8、22d7直接连接。主电流用的引线40将绝缘电路基板20d的半导体芯片30的输出电极30b、半导体芯片31的正面正电极以及电路图案22d8直接连接。主电流用的引线40的直径为100μm以上且600μm以下。

[0116]

检测用的引线40将电路图案22f2、22b1、22b2、22b3、22b4与电路图案22b8直接连接。另外,检测用的引线40将电路图案22b3、22a3、22a8直接连接。另外,检测用的引线40将电路图案22e2、22a5、22a4、22c3、22c4直接连接。检测用的引线40将电路图案22c3、22c8直接连接。检测用的引线40将电路图案22c3、22d3、22d8、22d4直接连接。这样的检测用的引线40的直径为例如25μm以上且400μm以下。这些检测用的引线40可以是与控制用的引线40相同的直径。

[0117]

此外,在绝缘电路基板20a~20d,引线40a~40d将半导体芯片30的输出电极30b之间直接连接。另外,引线41将绝缘电路基板20a的半导体芯片31的正面正电极与绝缘电路基板20b的半导体芯片31的正面正电极直接连接。引线42将绝缘电路基板20c的半导体芯片31的正面正电极与绝缘电路基板20d的半导体芯片31的正面正电极直接连接。应予说明,引线

40a~40d、41、42的直径为例如25μm以上且400μm以下。另外,引线40a~40d、41、42各自不限于一条,也可以是多条。这些引线40a~40d、41、42可以是与控制用的引线40相同的直径。

[0118]

接下来,利用图9,对从半导体装置10的g1、g2端子的引线框架起到绝缘电路基板20a~20d的半导体芯片30的控制电极30a为止的布线结构进行说明。图9是示出第二实施方式的半导体装置的控制侧的布线结构的图。

[0119]

应予说明,图9中的电阻rx、ry是通电时的分别从g1、g2端子的引线框架起到电路图案22f1、22e1为止的电阻(布线电阻)。即,电阻rx、ry是g1、g2端子的引线框架各自的电阻。电阻ra是将绝缘电路基板20f所包括的电路图案22f1、引线40、电路图案22b5、引线40的布线电阻以及绝缘电路基板20b的电阻芯片32的电阻相加而得的电阻。电阻rb是将绝缘电路基板20f所包括的电路图案22f1、引线40、电路图案22b5、(电路图案22b5、22b6、22a6间的)引线40的布线电阻以及绝缘电路基板20a的电阻芯片32的电阻相加而得的电阻。

[0120]

电阻rc是将电路图案22e1、引线40、电路图案22a1、引线40、电路图案22a2、引线40、电路图案22c2、引线40、电路图案22c1、引线40的布线电阻以及绝缘电路基板20c的电阻芯片32的电阻相加而得的电阻。电阻rd是将电路图案22e1、引线40、电路图案22a1、引线40、电路图案22a2、引线40、电路图案22c2、引线40、电路图案22c1、引线40、电路图案22c5、引线40、电路图案22d1、引线40的布线电阻以及绝缘电路基板20d的电阻芯片32的电阻相加而得的电阻。

[0121]

电阻ra1、ra2是分别从电路图案22a6起到绝缘电路基板20a的半导体芯片30的控制电极30a为止的布线电阻。即,电阻ra1、ra2是引线40的布线电阻。电阻rb1、rb2是分别从电路图案22b6起到绝缘电路基板20b的半导体芯片30的控制电极30a为止的布线电阻。即,电阻rb1、rb2是引线40的布线电阻。

[0122]

电阻rc1、rc2是分别从电路图案22c6起到绝缘电路基板20c的半导体芯片30的控制电极30a为止的布线电阻。即,电阻rc1、rc2是引线40的布线电阻。电阻rd1、rd2是分别从电路图案22d6起到绝缘电路基板20d的半导体芯片30的控制电极30a为止的布线电阻。即,电阻rc1、rc2是引线40的布线电阻。

[0123]

另外,分别设置于绝缘电路基板20a~20d的电阻芯片32的电阻ra~rd使用比从各引线框架起到电阻芯片32为止的电阻rx、ry大且比电阻ra1、ra2、rb1、rb2、rc1、rc2、rd1、rd2大的电阻。具体的电阻值与第一实施方式相同。

[0124]

因此,与第一实施方式同样地,利用电阻芯片32,使从g1、g2端子起的布线电阻以及电感的相对差变小。在使针对g1、g2端子的引线框架的控制电压成为导通(或关断)时,能够抑制多个半导体芯片30的上升时间(或下降时间)的差。由此,输出电极30b(源极)的电压不会紊乱。因此,能够向外部的控制装置输出稳定的电压。因此,在使配置于后述的不同的绝缘电路基板20a~20d的半导体芯片30的输出电极30b间的电位均匀化的情况下,通过配置电阻芯片32,能够抑制振荡现象以及由其引起的误动作的产生。

[0125]

接下来,利用图10以及图8,对这样的半导体装置10所包括的等效电路进行说明。图10是示出第二实施方式的半导体装置的等效电路的图。应予说明,在图10中,如上所述,作为半导体芯片30而示出了功率mosfet的情况。另外,在图10中分别对应于绝缘电路基板20a~20d。图10与图3的情况相同地示出控制侧的布线结构。第二实施方式的半导体装置10的输出侧形成与图4的情况相同的布线结构。

[0126]

半导体芯片30的背面的输入电极(漏极)以及半导体芯片31的背面负电极经由绝缘电路基板20a、20b的电路图案22a7、22b7而与作为d1端子的引线框架电连接。

[0127]

绝缘电路基板20a、20b的半导体芯片30的正面的输出电极30b(源极)以及半导体芯片31的正面正电极经由引线40、电路图案22a8、22b8、22c8、22d8、22c7、22d7而与作为d2s1端子的引线框架电连接。

[0128]

半导体芯片30的背面的输入电极(漏极)以及半导体芯片31的背面的负极电极经由绝缘电路基板20c、20d的电路图案22c7、22d7而与作为d2s1端子的引线框架电连接。

[0129]

绝缘电路基板20c、20d的半导体芯片30的正面的输出电极30b(源极)以及半导体芯片31的正面正电极经由引线40、电路图案22c8、22d8而分别与作为s2端子的引线框架电连接。

[0130]

而且,绝缘电路基板20a的半导体芯片31的正面正电极与绝缘电路基板20b的半导体芯片31的正面正电极通过引线41而直接连接。绝缘电路基板20c的半导体芯片31的正面正电极与绝缘电路基板20d的半导体芯片31的正面正电极通过引线42而直接连接。由此,如利用图9进行说明的那样,在半导体芯片30的控制电极30a的布线电阻以及电感的偏差小的情况下,使各正面正电极之间的电位均匀化。由此,能够向外部的控制装置输出稳定的输出电极30b(源极)。

[0131]

此外,绝缘电路基板20a的半导体芯片30的输出电极30b之间通过引线40a而直接连接。在绝缘电路基板20b~20d也同样地,半导体芯片30的输出电极30b之间通过引线40b~40d而直接连接。由此,使绝缘电路基板20a~20d分别包括的半导体芯片30的输出电极30b间的电位均匀化,从而抑制电感值的增加。

[0132]

因此,半导体装置10具备电阻芯片32,利用引线41、42将不同的绝缘电路基板20a、20b以及不同的绝缘电路基板20c、20d的半导体芯片31的正面正电极间直接连接。此外,利用引线40将同一绝缘电路基板20a~20d的半导体芯片30的输出电极30b间直接连接。由此,能够降低半导体装置10的半导体芯片30的振荡现象,并且能够抑制可靠性的降低。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。