1.本发明涉及半导体技术领域,尤其涉及一种半导体封装。

背景技术:

2.由于移动(mobile)应用新兴市场的快速增长,封装技术变得比以往任何时候都更具挑战性,推动先进的硅(si)节点(node)、更精细的凸块间距(bump pitch)以及更精细的线宽(line width)和间距基板制造能力,以满足移动设备(mobile device)日益增长的需求。

3.封装上封装(package on package,pop)技术已用于组合离散封装(discrete package)。pop通常由两个封装组成,例如包含存储器芯片的顶部封装安装在包含逻辑芯片的底部封装上。顶部封装可以通过中介层连接到底部封装。

4.业界亟需一种新颖的pop封装结构,其中逻辑芯片与存储芯片之间的连接路径的长度需要进一步缩短,以提高电性能。

技术实现要素:

5.有鉴于此,本发明提供一种半导体封装,具有减小的连接长度,以解决上述问题。

6.根据本发明的第一方面,公开一种半导体封装,包括:

7.底部封装,包括由模塑料包围的应用处理器晶粒;

8.顶部封装,安装在该底部封装上;

9.顶部重分布层结构,设置在该顶部封装和该底部封装之间;

10.多个贯穿模制通孔,设置在该模塑料中,用于将该顶部封装与该应用处理器晶粒电连接,其中,该多个贯穿模制通孔中的每一个在俯视时具有椭圆形或矩形形状;以及

11.底部重分布层结构,其中该应用处理器晶粒和该多个贯穿模制通孔互连到该底部重分布层结构。

12.根据本发明的第二方面,公开一种半导体封装,包括:

13.底部封装,包括顶部两层基板、中间模塑料和底部多层基板,用于封装应用处理器晶粒;

14.顶部封装,安装在该底部封装上;

15.多个贯穿模制通孔,设置在该中间模塑料中,用于将该顶部封装与该应用处理器晶粒电连接,其中,当俯视时,该多个贯穿模制通孔中的每一个具有椭圆形或矩形形状。

16.根据本发明的第三方面,公开一种半导体封装,包括:

17.至少一个逻辑芯片,由该模塑料包围;

18.存储器装置,设置在该至少一个逻辑晶粒附近;

19.多个通孔,围绕该至少一个逻辑晶粒,用于将该至少一个逻辑晶粒电连接到该存储器装置,其中当从上方观察时,该多个通孔中的每一个具有椭圆形或矩形形状。

20.本发明的半导体封装由于包括:底部封装,包括由模塑料包围的应用处理器晶粒;

顶部封装,安装在该底部封装上;顶部重分布层结构,设置在该顶部封装和该底部封装之间;多个贯穿模制通孔,设置在该模塑料中,用于将该顶部封装与该应用处理器晶粒电连接,其中,该多个贯穿模制通孔中的每一个在俯视时具有椭圆形或矩形形状;以及底部重分布层结构,其中该应用处理器晶粒和该多个贯穿模制通孔互连到该底部重分布层结构。将贯穿模制通孔中的每一个设置为椭圆形或矩形,并且其中椭圆形或矩形的宽度较长度小,使得贯穿模制通孔之间的间距相对于先前技术中圆形的贯穿模制通孔之间的间距更小,从而使相同数量的贯穿模制通孔占用的宽度(或尺寸)更小,使这些贯穿模制通孔更加向中间位置靠拢,这样就可以让设置在应用处理器晶粒的焊盘连接到贯穿模制通孔时的路径变短,从而缩小了应用处理器晶粒连接到贯穿模制通孔,以及连接到存储器封装的连接长度。

附图说明

21.图1是显示根据本发明实施例的示例性半导体封装的示意性截面图;

22.图2是根据本发明实施例的ap晶粒周围的tmv的局部俯视布局示意图。

23.图3显示了以3x2数组排列的交错tmv;

24.图4显示了示例性hbpop;

25.图5示出了示例性半导体封装;

26.图6示出了另一示例性半导体封装;以及

27.图7示出又一示例性半导体封装。

具体实施方式

28.在下面对本发明的实施例的详细描述中,参考了附图,这些附图构成了本发明的一部分,并且在附图中通过图示的方式示出了可以实践本发明的特定的优选实施例。对这些实施例进行了足够详细的描述,以使本领域技术人员能够实践它们,并且应当理解,在不脱离本发明的精神和范围的情况下,可以利用其他实施例,并且可以进行机械,结构和程序上的改变。本发明。因此,以下详细描述不应被理解为限制性的,并且本发明的实施例的范围仅由所附权利要求限定。

29.将理解的是,尽管术语“第一”、“第二”、“第三”、“主要”、“次要”等在本文中可用于描述各种组件、组件、区域、层和/或部分,但是这些组件、组件、区域、这些层和/或部分不应受到这些术语的限制。这些术语仅用于区分一个组件、组件、区域、层或部分与另一区域、层或部分。因此,在不脱离本发明构思的教导的情况下,下面讨论的第一或主要组件、组件、区域、层或部分可以称为第二或次要组件、组件、区域、层或部分。

30.此外,为了便于描述,本文中可以使用诸如“在...下方”、“在...之下”、“在...下”、“在...上方”、“在...之上”之类的空间相对术语,以便于描述一个组件或特征与之的关系。如图所示的另一组件或特征。除了在图中描述的方位之外,空间相对术语还意图涵盖设备在使用或运行中的不同方位。该设备可以以其他方式定向(旋转90度或以其他定向),并且在此使用的空间相对描述语可以同样地被相应地解释。另外,还将理解的是,当“层”被称为在两层“之间”时,它可以是两层之间的唯一层,或者也可以存在一个或多个中间层。

31.术语“大约”、“大致”和“约”通常表示规定值的

±

20%、或所述规定值的

±

10%、或所述规定值的

±

5%、或所述规定值的

±

3%、或规定值的

±

2%、或规定值的

±

1%、或规定

值的

±

0.5%的范围内。本发明的规定值是近似值。当没有具体描述时,所述规定值包括“大约”、“大致”和“约”的含义。本文所使用的术语仅出于描述特定实施例的目的,并不旨在限制本发明。如本文所使用的,单数术语“一”,“一个”和“该”也旨在包括复数形式,除非上下文另外明确指出。本文所使用的术语仅出于描述特定实施例的目的,并不旨在限制本发明构思。如本文所使用的,单数形式“一个”、“一种”和“该”也旨在包括复数形式,除非上下文另外明确指出。

32.将理解的是,当将“组件”或“层”称为在另一组件或层“上”、“连接至”、“耦接至”或“邻近”时,它可以直接在其他组件或层上、与其连接、耦接或相邻、或者可以存在中间组件或层。相反,当组件称为“直接在”另一组件或层“上”、“直接连接至”、“直接耦接至”或“紧邻”另一组件或层时,则不存在中间组件或层。

33.注意:(i)在整个附图中相同的特征将由相同的附图标记表示,并且不一定在它们出现的每个附图中都进行详细描述,并且(ii)一系列附图可能显示单个项目的不同方面,每个方面都与各种参考标签相关联,这些参考标签可能会出现在整个序列中,或者可能只出现在序列的选定图中。

34.本发明涉及具有减小(或更短)的连接长度的半导体封装,其适用于包括但不限于扇出层叠封装(fan-out package-on-package,扇出pop)和高带宽层叠封装(high-bandwidth package-on-package,hbpop)的应用.

[0035]“扇出(fan-out)”封装可以定义为任何具有从芯片表面扇出连接的封装,从而支持更多的外部i/o(输入/输出,input/output)。传统的扇出封装使用环氧树脂模塑料来完全嵌入晶粒,而不是将它们放置在基板或中介层上。扇出封装通常涉及在硅晶圆(silicon wafer)上切割芯片,然后将已知良好的芯片非常精确地定位在薄的“重组”或载体晶圆上,然后对其进行模制,然后在模制区域(芯片和扇出区域)顶部形成重分布层(redistribution layer,rdl),然后在顶部形成焊球。hbpop通常包括顶部2层(2-layer)基板、中间成型件(middle molding)和底部3层(3-layer)基板(三层基板),以封装应用处理器(application processor,ap)芯片。与扇出pop相比,hbpop的ap封装成本更低。

[0036]

图1是显示根据本发明实施例的示例性半导体封装的示意性截面图。如图1所示,半导体封装1可以是扇出pop,但不限于此。根据一个实施例,半导体封装1可以包括底部封装10和安装在底部封装10上的顶部封装20。例如,底部封装10包括被模塑料110包围(围绕)的应用处理器(ap)晶粒100。介电层dl可以设置在ap晶粒100的有源表面(主动面)100上。多个导电凸块或柱101可以设置在介电层dl中并且可以电耦合到有源表面100a。在执行研磨或化学机械抛光(chemical mechanical polishing,cmp)工艺之后,介电层dl的顶面(上表面)s1可以与周围的模塑料110的顶面(上表面)s2共面(或齐平)。

[0037]

根据本发明一个实施例,重分布层(re-distributed layer,rdl)结构rs可以设置在介电层dl的顶表面(上表面)s1和周围的模塑料110的顶表面s2上。rdl结构rs可以包括多层互连is。根据本发明一个实施例,多个球焊盘pb可以分布在rdl结构rs的顶表面s3上。焊球sb可以安装在每个球焊盘pb上以用于进一步连接。可选地,诸如去耦电容器或任何合适的表面贴装器件(surface mount device,smd)的无源组件(被动组件)pd可以设置在焊球sb之间的rdl结构rs的顶表面s3上。

[0038]

根据本发明一个实施例,多个贯穿模制通孔(through molding via,tmv)110v设

置在模塑料110中以将rdl结构rs电连接到上覆的重分布层(rdl)结构rt(rdl结构rs与rdl结构rt分别设置在模塑料110相对的两侧)。根据一个实施例,rdl结构rt可以至少包括多个凸块焊盘pi和用于连接凸块焊盘pi与tmv 110v的金属迹线pt。顶部封装20通过诸如微凸块的凸块st安装在凸块焊盘pi上。根据本发明一个实施例,例如,顶部封装20可以是dram封装,例如ddr dram封装。在一些实施例中,tmv 110v可以是插入柱或焊点。顶部封装20可以是存储器封装。

[0039]

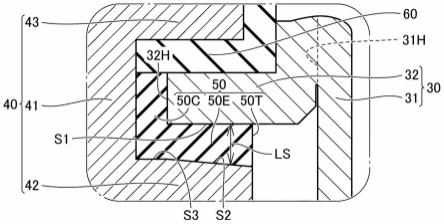

请参考图2。图2为本发明一个实施例的图1中ap晶粒100周围的tmv 110v的局部俯视布局示意图。如图2所示,当从上面看时,每个tmv 110v可以具有椭圆形或矩形形状。每个tmv 110v沿第二方向d2或通孔到晶粒100的方向伸长。每个tmv 110v的最大长度(尺寸)为l,每个tmv 110v的最大宽度(尺寸)为w,其中l大于w;以上这些形状大小的描述适用于椭圆形或矩形形状。

[0040]

根据一个实施例,示例性3x2数组中的tmv 110v可以沿第一方向d1(即与ap晶粒100的相邻侧边缘平行的方向)具有w sh的水平间距p1,其中sh是在沿第一方向d1的两个相邻tmv 110v之间的间距。根据一个实施例,3x2数组中的tmv 110v可具有沿第二方向d2的l sv的垂直间距p2,其中sv是沿第二方向d2的两个相邻tmv 110v之间的间距。根据一个实施例,第一方向d1与第二方向d2正交。根据本发明一个实施例,tmv 110v的垂直间距p2大于水平间距p1。

[0041]

通过提供这样的配置,tmv 110v可以比现有技术更紧密地布置在ap晶粒100周围。由于椭圆形的tmv 110v,特别是那些设置在半导体封装1的外围区域或拐角区域的tmv 100v,可以减少存储器封装(顶部封装)20和ap晶粒100之间的连接长度。具体来说,如图2所示,将每个tmv 110v设置为椭圆形或矩形,并且其中椭圆形或矩形的宽度较长度小,使得tmv 100v之间的间距p1相对于先前技术中圆形的tmv 110v之间的间距更小,从而使相同数量的tmv 110v(椭圆形或矩形)占用的宽度(或尺寸)更小,使这些tmv 110v更加向中间位置靠拢,这样就可以让设置在ap晶粒100的焊盘连接到tmv 110v(椭圆形或矩形)时的路径变短,从而缩小了ap晶粒100连接到tmv 110v(椭圆形或矩形),以及连接到存储器封装(顶部封装)20的连接长度。如图2所示的示例中,上述的焊盘可以是设置在ap晶粒100的与tmv 100v相邻或靠近的一侧的焊盘。对于位于(靠近或相邻)ap晶粒100不同侧的tmv 100v,垂直于ap晶粒100相对应的一侧延伸的方向为tmv 100v的长度方向(第二方向),而平行于ap晶粒100相对应的该一侧延伸的方向为tmv 100v的宽度方向(第一方向),并且将tmv 100v的宽度设置为较长度小,这样就可以使在ap晶粒100相对应的该一侧的宽度方向上设置相同的tmv 100v时,占用该一侧的宽度方向上的距离更小,也即在宽度方向上tmv 100v(数组)设置的更加紧凑,从而让ap晶粒100相对应的该一侧上的焊盘可以以更短的路径(更短的布线长度)连接到tmv 100v,减少连接路径。

[0042]

为简单起见,仅一个3x2数组的tmv 110v如图所示。根据本发明一个实施例,两行tmv 110v可以在第二方向d2上彼此对齐。根据另一个实施例,如图3所示,tmv 110v的3x2数组可以是交错的,即前排与后排错开。采用这种方式可以提供不同的需求设计,增加设计弹性。

[0043]

如图2和图3所示的椭圆形tmv 110v可以适用于其他种类的半导体封装,例如hbpop。图4图示了示例性hbpop。如图4所示,hbpop 2具有底部封装30和顶部封装40,例如安

装在底部封装30上的dram封装。底部封装30包括顶部2层(2-层或两层)基板310、中间模塑料(中间成型件或模塑料)320、以及底部多层基板330,用于封装应用处理器(ap)晶粒300。同样,多个tmv 320v设置在ap晶粒300周围。tmv 320v设置在模塑料320中并且用于电连接顶部2层(2-层或两层)基板310与底部多层基板330。设置在中间模塑料中的tmv 320v将顶部封装与ap晶粒电连接,其中多个tmv中的每一个具有椭圆形状、矩形形状或其组合。如图2-3所示的tmv 110v设置在ap晶粒100的上侧,此时第一方向d1为ap晶粒100的宽度方向,为了使得布置相同的tmv 110v时占用宽度方向上的尺寸更少,根据本发明上述实施例,即可将tmv 110v在第一方向d1(也即此时ap晶粒100的宽度方向,或称为与该tmv 110v靠近或相邻的ap晶粒100的一侧的宽度方向)尺寸进行缩小(例如设置为本实施例中的椭圆形或矩形),而使得每个tmv 110v在第一方向d1上的宽度(或尺寸)小于每个tmv 110v在第二方向d2上的长度(或尺寸),其中第二方向d2垂直于第一方向d1。对于ap晶粒100其他的侧,可以根据上述描述对应设置,也即在对应的ap晶粒100的该一侧的宽度方向上(也即与该一侧平行的方向上),每个tmv 110v的尺寸更小(每个tmv 110v在该宽度方向上的尺寸比每个tmv 110v在于该宽度方向相垂直的方向上(也即与该一侧垂直的方向上)的尺寸小)。采用本发明上述实施例的方式,可以让每个tmv 110v在平行于该ap晶粒100对应的一侧的方向上(也即宽度方向上)的尺寸缩小(小于垂直于该ap晶粒100对应的一侧的方向上(也即长度方向上)的尺寸),从而使布置相同数量的tmv 110v占用的宽度方向上的尺寸更小,tmv 110v的布置更加紧凑,这样该ap晶粒100对应的一侧的焊盘连接到tmv 110v的线路长度将更短,从而显著减小了信号传输路径,提高了半导体封装的电气性能。

[0044]

图5示出了示例性半导体封装。如图5所示,半导体封装3包括由模塑料520封装并由具有多个通孔522v的通孔基板522围绕的ap晶粒500。ap晶粒500和诸如dram封装的存储器装置600以并排方式安装在基板530上。顶部桥接基板(bridge substrate)510设置在通孔基板522和模塑料520上。信号路径pp显示来自ap晶粒500的信号通过左侧的基板530、通孔基板522和通孔522v传输、顶部桥接基板510、右侧的过孔(或通孔)基板522和过孔(或通孔)522v,以及基板530传输到存储器晶粒600。如图2和图3所示的矩形或椭圆形过孔(或通孔)522v可以显著减少信号传输路径pp的连接长度(减少布线的长度),所以提高了半导体封装3的电气性能。

[0045]

图6示出了另一示例性半导体封装。如图6所示,半导体封装4包括安装在基板80上的扇出芯片封装70。扇出芯片封装70和诸如dram封装的存储器封装(顶部封装)90以并排方式安装在基板上。根据一些实施例,扇出芯片封装70可以包括两个逻辑晶粒701和702,它们互连到桥接通孔基板703和围绕桥接通孔基板703的外围通孔结构704。rdl结构705设置在桥接通孔基板703与基板80之间以及外围通孔结构704与基板80之间。如图2和图3所示的矩形或椭圆形通孔704v可以显著提高半导体封装4的电性能,因为连接可以减少信号传输路径的长度。

[0046]

图7示出又一示例性半导体封装。如图7所示,半导体封装5可以包括逻辑晶粒1001和1002,以及通过rdl结构1004互连的存储器晶粒1003。rdl结构1004进一步互连到由模塑料1006包围的硅通孔(tsv)晶粒1005。tsv晶粒1005包括穿过tsv晶粒1005的多个硅通孔1005v。多个tmv 1006v设置在模塑料1006中用于信号传输。tmv 1006v可以通过底部rdl结构1007电连接到tsv晶粒1005。此外,tsv晶粒1005可以通过底部rdl结构1007、tmv 1006v和

rdl结构1004电连接到逻辑晶粒1001和1002以及存储器晶粒1003。如图2和图3所示的矩形或椭圆形过孔(或通孔)1006v可以显著提高半导体封装5的电性能,因为可以减少信号传输路径的连接长度。

[0047]

本领域的技术人员将容易地观察到,在保持本发明教导的同时,可以做出许多该设备和方法的修改和改变。因此,上述公开内容应被解释为仅由所附权利要求书的界限和范围所限制。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。