1.本发明有关于一种半导体结构,且特别是有关于具有测试元件组的半导体结构。

背景技术:

2.为了增加半导体内的元件密度以及改善其整体表现,当目前半导体的制造技术持续朝向元件尺寸的微缩化而努力时,许多挑战随之而生。例如,改善外围电路区的缺陷检测的速度和提供有价值的缺陷信息。

技术实现要素:

3.本发明实施例提供半导体结构包含设置于基底之上的多个垂直导电部件、以及设置于垂直导电部件之上的多个水平导电部件。水平导电部件包含分别电连接第一垂直导电部件和第二垂直导电部件的第一导线以及第二导线、设置于第一垂直导电部件与第二导线之间的第一导电区段、以及设置于第一导线与第二垂直导电部件之间的一第二导电区段。第一导电区段与垂直导电部件电性隔离,且第二导电区段与垂直导电部件电性隔离。

4.本发明实施例提供半导体结构包含设置于基底之上的多个接触插塞、以及设置于接触插塞之上且在第一方向上延伸的第一导线、第二导线、第一导电区段、以及第二导电区段。第一导电区段和第二导电区段设置于第一导线与第二导线之间,第一导线电连接第一接触插塞,第二导线电连接第二接触插塞,第一导电区段朝向第二方向投影至第一导线的投影区域覆盖第一接触插塞,第二方向垂直于第一方向,第二导电区段朝向第三方向投影至第二导线的投影区域覆盖第二接触插塞,第三方向垂直于第一方向且相对于第二方向。

5.本发明实施例提供半导体结构的形成方法包含形成多个接触插塞于基底之上;形成介电层于接触插塞之上;使用第一图案化遮罩层蚀刻该介电层以形成第一沟槽和第二沟槽;使用第二图案化遮罩层蚀刻该介电层以形成第三沟槽和第四沟槽;以及沉积金属材料,以在第一沟槽和第二沟槽中形成第一导电区段和第二导电区段,且在第三沟槽和第四沟槽中形成第一导线和第二导线。第一导电区段与接触插塞电性隔离,第二导电区段与接触插塞电性隔离,且第一导线和第二导线分别电连接第一接触插塞和第二接触插塞。

6.本发明实施例利用不与垂直导电部件电性连接电连接的两个导电区段,作为判断微影光刻制程工艺是否发生叠加偏移的目标线。利用其一导电区段与相邻垂直导电部件之间的配置关系不同于另一导电区段与相邻垂直导电部件之间的配置关系,可实现偏移方向的辨别,从而提供更明确的缺陷资讯信息。

附图说明

7.让本发明的特征和优点能更明显易懂,下文特举不同实施例,并配合所附图式作详细说明如下:

8.图1a、图2a和图3a是根据本发明实施例的半导体结构的水平导电部件的平面示意图。

9.图1a-1是根据本发明实施例的半导体结构的剖面示意图。

10.图1b、图1c、图1d、图2b、图2c、图2d、图2e、图2f、图3b、图3c、图3d、图3e和图3f是根据本发明实施例的水平导电部件在进行电子束检测时的平面示意图。

11.图1c-1和图1d-1是根据本发明实施例的半导体结构的剖面示意图。

12.附图标记

13.100:半导体结构

14.102:基底

15.104:介电结构

16.106:导电元件

17.108,108

1-108

12

:垂直导电部件

18.110:水平导电部件

19.111:介电层

20.1121,1122:导线

21.1161,1162:导电区段

22.210:水平导电部件

23.212

1-212

10

:第一导线

24.214

1-214

10

:第二导线

25.2161,2162:第一导电区段

26.2181,2182:第二导电区段

27.310:水平导电部件

28.312

1-3126:第一导线

29.314

1-3146:第二导线

30.3161,3162:第一导电区段

31.3181,3182:第二导电区段

32.a1:第一方向

33.a2:第二方向

34.a3:第三方向

35.a4:第四方向

36.d1,d2,d3,d4:距离

37.d5,d6,d7,d8:距离

38.d9,d10,d11,d12:距离

具体实施方式

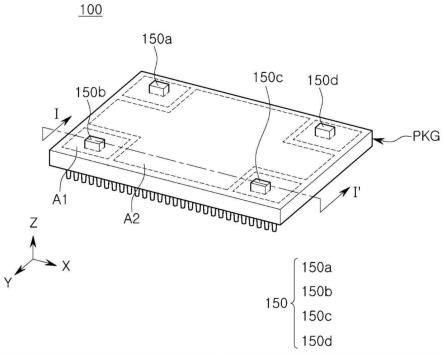

39.图1a是根据本发明实施例的半导体结构100的水平导电部件110的平面示意图。图1a-1是本发明的半导体结构100的剖面示意图,其中图1a-1的左图和右图分别沿着图1a的线i-i和线ii-ii获取。为了易于说明,撷取1a标示参考方向,其中第一方向a1、第二方向a2、第三方向a3和第四方向a4是大致平行于基底主表面的横向方向。第一方向a1相对于第二方向a2,第三方向a3相对于第四方向a4。第一方向a1及第二方向a2大致垂直于第三方向a3及第四方向a4。

40.图1a-1显示半导体结构100,半导体结构100包含基底102、设置于基底102之上的介电结构104、设置于介电结构104中的导电元件106和垂直导电部件108、以及设置于介电结构104之上的介电层111和水平导电部件110。

41.在一些实施例中,基底102可包含形成于半导体基底上的各种主动装置,例如逻辑装置(例如,金属氧化物半导体场效晶体管、双极性接面晶体管、高电子迁移率场效晶体管、或其他逻辑装置)、存储器装置(例如,动态随机存取存储器装置、快闪存储器装置、或其他适合存储器装置)、外围电路装置、或其他适合主动装置。基底102也可包含被动装置,例如电阻、电容、电感、或其他适合被动装置。基底102还包含形成于主动装置和/或被动装置之上且与这些装置电连接的内连线结构。内连线结构可包含一或多个介电层(例如,层间介电层、金属间介电层、或其他适合介电层)、以及形成于一或多个介电层中的垂直导电部件(例如,接触插塞和/或引线孔)和水平导电部件(例如,导线)。

42.在一些实施例中,介电结构104包含一或多个介电层。介电结构104可包含氧化硅(sio)、氮化硅(sin)、氮氧化硅(sion)、碳化硅(sic)、氮碳化硅(sicn)、碳氧化硅(sioc)、氧化铝(alo)、和/或前述之组合。

43.在一些实施例中,导电元件106是形成于半导体基底上的晶体管的栅极结构(例如,多晶硅栅极结构或金属栅极结构),而垂直导电部件108是电连接至栅极结构的接触插塞。在其他实施例中,导电元件106是水平导电部件(例如,导线),其通过内连线结构电连接至主动装置的栅极结构,而垂直导电部件108是电连接至导线的引线孔。上述的接触插塞、导线和引线孔可由一或多个金属材料形成,例如钨(w)、铝(al)、铜(cu)、钛(ti)、钽(ta)、氮化钛(tin)、氮化钽(tan)、或前述之组合。

44.水平导电部件110包含用于晶圆测试的测试元件组(test element group,teg)和/或测试键(test key)。水平导电部件110包含导线1121和1122、以及导电区段1161和1162。水平导电部件110的轴向在第三方向a3和第四方向a4上延伸。每一个导线1121和1122接触并电连接下方的至少一个垂直导电部件108。导电区段1161和1162与垂直导电部件108隔开且电性隔离。导电区段1161与1162彼此隔开且电性隔离。

45.水平导电部件110可由一或多个金属材料形成,例如钨(w)、铝(al)、铜(cu)、钛(ti)、钽(ta)、氮化钛(tin)、氮化钽(tan)、或前述之组合。形成水平导电部件110可包含形成介电层111于介电结构104之上,且通过光刻工艺形成图案化遮罩层(例如,光刻胶或硬遮罩层)于介电层111之上。介电层111的材料可与介电结构104相同或相似。使用图案化遮罩层对介电层111进行蚀刻(etching)工艺,移除介电层111未被图案化遮罩层覆盖的部分,以形成沟槽于介电层中。沉积金属材料于介电层111之上并且填充沟槽,之后进行平坦化工艺(例如,化学机械研磨工艺及/或回蚀刻工艺)从介电层111上移除过量的金属材料。金属材料留在沟槽中的部分形成水平导电部件110。可通过灰化工艺及/或蚀刻工艺移除图案化遮罩层。

46.在其他实施例中,形成水平导电部件110可包含沉积金属材料于介电结构104之上,且通过光刻工艺形成图案化遮罩层(例如,光刻胶或硬遮罩层)于金属材料之上。使用图案化遮罩层对金属材料进行蚀刻工艺,移除金属材料未被图案化遮罩层覆盖的部分。剩余的金属材料形成水平导电部件110。之后,形成介电层111围绕水平导电部件110。

47.导电区段1161和1162配置为在后续电子束(e-beam inspection)检测期间的目标

线,以确认上述形成水平导电部件110的光刻工艺的叠加(overlay)是否发生偏移。此部分将于后续说明。

48.请参考图1a-1,导电区段1161和1162紧邻于导线1121与导线1122设置,且介于导线1121与导线1122之间。导线1121与导电区段1161(或1162)之间没有其他的水平导电部件110,并且导线1122与导电区段1161(或1162)之间没有其他的水平导电部件110。

49.导电区段1161夹设于两个垂直导电部件108之间,这两个垂直导电部件108各自与导线1121和导线1122接触。具体而言,导电区段1161朝向第一方向a1投影至导线1121的投影区域会覆盖导线1121与垂直导电部件108重叠(或接触)的部分,且导电区段1161朝向第二方向a2投影至导线1122的投影区域会覆盖导线1122与垂直导电部件108重叠(或接触)的部分。

50.导电区段1162与接触导线1122的垂直导电部件108相邻设置,但不相邻于接触导线1121的垂直导电部件108。具体而言,导电区段1162朝向第一方向a1投影至导线1121的投影区域不会覆盖导线1121与垂直导电部件108重叠(或接触)的部分,但导电区段1162朝向第二方向a2投影至导线1122的投影区域会覆盖导线1122与垂直导电部件108重叠(或接触)的部分。

51.为了确认形成水平导电部件110的光刻工艺的叠加是否发生偏移,可以在形成水平导电部件110之后进行电子束检测。图1b、图1c、图1d是根据本发明实施例的水平导电部件110在进行电子束检测时的平面示意图。图1c-1和图1d-1是本发明实施例的半导体结构的剖面示意图,其中图1c-1和图1d-1的左图和右图分别对应于图1a中的线i-i和线ii-ii。

52.图1b显示光刻工艺的叠加未发生偏移的实施例。请参考图1b与图1a,由于导线1121和1122通过垂直导电部件108电连接至导电元件106(例如,主动装置的栅极结构),所以导线1121和1122在电子束检测期间会呈现亮线。由于作为目标线的导电区段1161和1162未电连接垂直导电部件108,所以导电区段1161和1162在电子束检测期间会呈现暗线。

53.图1c和图1c-1显示光刻工艺的叠加朝向第一方向a1偏移的实施例。请参考图1c与图1c-1与图1a,因为导电区段1161和1162朝向第一方向a1偏移,所以导电区段1161接触且电连接垂直导电部件108,从而电连接至基底102中的主动装置。然而,导电区段116

2-保持与垂直导电部件108电性隔离。因此,在电子束检测期间,导电区段1161呈现亮线,而导电区段1162呈现暗线。

54.图1d和图1d-1显示光刻工艺的叠加朝向第二方向a2偏移的实施例。请参考图1d与图1d-1与图1a,因为导电区段1161和1162朝向第二方向a2偏移,所以导电区段1161接触且电连接垂直导电部件108,从而电连接至基底102中的主动装置。并且,导电区段116

2-接触且电连接垂直导电部件108,从而电连接至基底102中的主动装置。因此,在电子束检测期间,导电区段1161和1162皆呈现亮线。

55.在对水平导电部件110进行电子束检测时,可以通过观察导电区段1161和1162的亮度,来判断形成水平导电部件110的光刻工艺的叠加是否发生偏移,并且可进一步辨别朝向哪一个方向发生偏移。因此,本发明实施例的水平导电部件的配置有助于在半导体装置制造期间提供更明确的缺陷信息。在一些实施例中,可根据偏移方向调整后续工艺,以补偿水平导电部件的偏移,从而改善所得到的半导体装置的制造成品率。

56.图2a是根据本发明实施例的半导体结构的水平导电部件210的平面示意图。图2a所示的水平导电部件210与图1a所示的水平导电部件110的差异在于水平导电部件210是通

过两次光刻工艺形成。

57.水平导电部件210设置于如图1a-1所示的介电结构104之上,并且包含第一导线212

1-212

10

、第二导线214

1-214

10

、第一导电区段2161和2162、以及第二导电区段2181和2182。水平导电部件210的轴向主要在第三方向a3和第四方向a4上延伸。每一个第一导线212

1-212

10

和第二导线214

1-214

10

接触并电连接下方的至少一个垂直导电部件108。在一些实施例中,一些第一导线212与第二导线214(例如,第一导线2124与第二导线2144)可以彼此接触,并且共用导电部件108。第一导电区段2161、2162与垂直导电部件108隔开且电性隔离,且第二导电区段2181和2182与垂直导电部件108隔开且电性隔离。第一导电区段2161与2162彼此隔开且电性隔离。第二导电区段2181与2182彼此隔开且电性隔离。

58.水平导电部件210可由一或多个金属材料形成,例如钨(w)、铝(al)、铜(cu)、钛(ti)、钽(ta)、氮化钛(tin)、氮化钽(tan)、或前述之组合。形成水平导电部件210可包含形成介电层111于介电结构104之上,且通过第一光刻工艺形成第一图案化遮罩层于介电层111之上。第一图案化遮罩层具有对应于第一导线212

1-212

10

和第一导电区段2161和2162的第一开口图案。使用第一图案化遮罩层对介电层111进行蚀刻工艺,移除介电层111被第一开口图案暴露出来的部分,以形成第一沟槽于介电层111中。可通过灰化工艺和/或蚀刻工艺移除第一图案化遮罩层。

59.接着,通过第二光刻工艺形成第二图案化遮罩层于介电层之上。第二图案化遮罩层具有对应于第二导线214

1-214

10

和第二导电区段2181和2182的第二开口图案。使用第二图案化遮罩层对介电层111进行蚀刻工艺,移除介电层111被第二开口图案暴露出来的部分,以形成第二沟槽于介电层111中。第一沟槽(对应于第一导线212

1-212

10

和第一导电区段2161和2162)与第二沟槽(对应于第二导线214

1-214

10

和第二导电区段2181和2182)在第一方向a1和第二方向a2上交替排列。通过两次光刻工艺可增加水平导电部件210的导线密度。可通过灰化工艺和/或蚀刻工艺移除第二图案化遮罩层。

60.沉积金属材料于介电层111之上并且填充第一沟槽和第二沟槽,之后进行平坦化工艺从介电层111上移除过量的金属材料。金属材料留在第一沟槽中的部分形成第一导线212

1-212

10

和第一导电区段2161和2162,而金属材料留在第二沟槽中的部分形成第二导线214

1-214

10

和第二导电区段2181和2182。

61.第一导电区段2161和2162以及第二导电区段2181和218

2-配置为在电子束检测期间的目标线,以分别确认形成水平导电部件210的第一光刻工艺的叠加和第二光刻工艺的叠加是否发生偏移。

62.第一导电区段2161和第一导电区段2162紧邻于第二导线2141与第二导线2142设置,且介于第二导线2141与第二导线2142之间。第一导电区段2161与接触第二导线2141的垂直导电部件1081间隔距离d1,且与接触第二导线2142的垂直导电部件1082间隔距离d2。距离d1和距离d2小于或等于第一光刻工艺的偏移距离。距离d1可大致等于距离d2。

63.第一导电区段2162与接触第二导线2142的一个垂直导电部件1083间隔距离d3,与接触第二导线2142的另一个垂直导电部件1084间隔距离d4,且与接触第二导线2141的垂直导电部件1085间隔距离d5。距离d3小于或等于第一光刻工艺的偏移距离,距离d5大于第一光刻工艺的偏移距离。距离d3可大致等于距离d2,距离d4大于距离d3,且距离d5大于距离d1。此外,第一导电区段2162与接触第二导线2144的垂直导电部件1086间隔距离d6。距离d6

大于第一光刻工艺的偏移距离,且大于距离d1。

64.第二导电区段2181和第二导电区段2182紧邻于第一导线2122与第一导线2123设置,且介于第一导线2122与第一导线2123之间。第二导电区段2181与接触第一导线2122的垂直导电部件1087间隔距离d7,且与接触第一导线2123的垂直导电部件1088间隔距离d8。距离d7和距离d8小于或等于第二光刻工艺的偏移距离。距离d7可大致等于距离d8。

65.第二导电区段2182与接触第一导线2122的一个垂直导电部件1089间隔距离d9,与接触第一导线2122的另一个垂直导电部件108

10

间隔距离d10,且与接触第一导线2123的垂直导电部件108

11

间隔距离d11。距离d9小于或等于第二光刻工艺的偏移距离,且距离d11大于第二光刻工艺的偏移距离。距离d9可大致等于距离d7,距离d10大于距离d9,且距离d11大于距离d8。此外,第二导电区段2182与接触第一导线2127的垂直导电部件108

12

间隔距离d12。距离d12大于第二光刻工艺的偏移距离,距离d12大于距离d8。

66.为了确认形成水平导电部件210的第一和第二光刻工艺的叠加是否发生偏移,可以在形成水平导电部件210之后进行电子束检测。图2b、图2c、图2d、图2e、2f是根据本发明实施例的水平导电部件210在进行电子束检测时的平面示意图。

67.图2b显示第一光刻工艺与第二光刻工艺的叠加皆未发生偏移的实施例。由于作为目标线的第一导电区段2161和2162和第二导电区段2181和2182未电连接垂直导电部件108,所以导电区段2161、2162、2181和2182在电子束检测期间会呈现暗线。

68.图2c显示第二光刻工艺的叠加朝向第一方向a1偏移且第一光刻工艺的叠加未发生偏移的实施例。请参考图2c与图2a,当偏移距离大于或等于距离d7、d9时,第二导电区段2181接触且电连接垂直导电部件1087,从而电连接至基底102中的主动装置,且第二导电区段218

2-接触且电连接垂直导电部件1089,从而电连接至基底102中的主动装置。因此,在电子束检测期间,第二导电区段2181和2182皆呈现亮线。

69.图2d显示第二光刻工艺的叠加朝向第二方向a2偏移且第一光刻工艺的叠加未发生偏移的实施例。请参考图2d与图2a,当偏移距离大于或等于距离d8且小于距离d11、d12时,第二导电区段2181接触且电连接垂直导电部件1088,从而电连接至基底102中的主动装置。第二导电区段2182保持与垂直导电部件108电性隔离。因此,第二导电区段2181呈现亮线,而第二导电区段2182呈现暗线。

70.图2e显示第一光刻工艺的叠加朝向第一方向a1偏移且第二光刻工艺的叠加未发生偏移的实施例。请参考图2e与图2a,当偏移距离大于或等于距离d1且小于距离d5、d6时,第一导电区段2161接触且电连接垂直导电部件1081,从而电连接至基底102中的主动装置。第一导电区段2162保持与垂直导电部件108电性隔离。因此,第一导电区段2161呈现亮线,而第一导电区段2162呈现暗线。

71.图2f显示第一光刻工艺的叠加朝向第二方向a2偏移且第二光刻工艺的叠加未发生偏移的实施例。请参考图2f与图2a,当偏移距离大于或等于距离d2、d3时,第一导电区段2161接触且电连接垂直导电部件1082,从而电连接至基底102中的主动装置,而第一导电区段2162接触且电连接垂直导电部件1083,从而电连接至基底102中的主动装置。因此,第一导电区段2161和2162皆呈现亮线。

72.在对水平导电部件210进行电子束检测时,可以通过观察导电区段2161、2162、2181、2182的亮度,来判断形成水平导电部件210的第一和第二光刻工艺的叠加是否发生偏

移,并且可进一步辨别朝向哪一个方向发生偏移。

73.图3a是根据本发明实施例的半导体结构的水平导电部件310的平面示意图。图3a所示的水平导电部件310与图2a所示的水平导电部件210的差异在于水平导电部件310的两个导电区段之间插入导线。

74.水平导电部件310设置于如图1a-1所示的介电结构104之上,并且包含第一导线312

1-3126、第二导线314

1-3146、第一导电区段3161和3162、以及第二导电区段3181和3182。水平导电部件310的轴向基本上在第一方向a1与第二方向a2上延伸。每一个第一导线312

1-3126和第二导线314

1-3146电连接下方的至少一个垂直导电部件108。在一些实施例中,一些第一导线312与第二导线314(例如,第一导线3123、3124与第二导线3142)可以彼此接触。第一导电区段3161和3162与垂直导电部件108隔开且电性隔离,且第二导电区段3181和3182与垂直导电部件108隔开且电性隔离。第一导电区段3161与3162彼此隔开且电性隔离。第二导电区段3181与3182彼此隔开且电性隔离。

75.水平导电部件310的材料与形成方法可与图2a所述的水平导电部件210相同或相似。举例而言,可通过第一光刻工艺和蚀刻工艺形成对应于第一导线312

1-3126和第一导电区段3161和3162的第一沟槽,且通过第二光刻工艺和蚀刻工艺形成对应于第二导线314

1-3146和第二导电区段3181和3182的第二沟槽。第一沟槽与第二沟槽在第三方向a3和第四方向a4上交替排列。之后,沉积金属材料填充第一沟槽和第二沟槽,以形成水平导电部件310。

76.第一导电区段3161和3162以及第二导电区段3181和318

2-配置为在电子束检测期间的目标线,以分别确认形成水平导电部件310的第一光刻工艺的叠加和第二光刻工艺的叠加是否发生偏移。

77.第一导电区段3161介于第二导线3141与第二导线3145之间。第一导电区段3162介于第二导线3145与第二导线3143之间。第二导线3145介于第一导电区段3161与第一导电区段3162之间,接触第二导线3145的垂直导电部件108夹设于第一导电区段3161与第一导电区段3162之间。第一导电区段3161与接触第二导线3145的垂直导电部件108相邻设置,但不相邻于接触第二导线3141的垂直导电部件108。第一导电区段3162与接触第二导线3145的垂直导电部件108相邻设置,但不相邻于接触第二导线3143的垂直导电部件108。

78.第二导电区段3181和第二导电区段3182介于第一导线3121与第一导线3122之间。第二导电区段3181与接触第一导线3121的垂直导电部件108相邻设置,但不相邻于接触第一导线3122的垂直导电部件108。第二导电区段3182与接触第一导线3122的垂直导电部件108相邻设置,但不相邻于接触第一导线3121的垂直导电部件108。

79.为了确认形成水平导电部件310的第一和第二光刻工艺的叠加是否发生偏移,可以在形成水平导电部件310之后进行电子束检测。图3b图3c、图3d、图3e、3f是根据本发明实施例的水平导电部件310在进行电子束检测时的平面示意图。

80.图3b显示第一光刻工艺与第二光刻工艺的叠加皆未发生偏移的实施例。由于作为目标线的第一导电区段3161和3162和第二导电区段3181和3182未电连接垂直导电部件108,所以导电区段3161、3162、3181和3182在电子束检测期间会呈现暗线。

81.图3c显示第一光刻工艺的叠加朝向第四方向a4偏移且第二光刻工艺的叠加未发生偏移的实施例。请参考图3c与图3a,因为第一导电区段3161和3162朝向第四方向a4偏移,所以第一导电区段3161保持与垂直导电部件108电性隔离,而第一导电区段3162接触且电连

接第二导线3145的垂直导电部件108。因此,在电子束检测期间,第一导电区段3161呈现暗线,而第一导电区段3162呈现亮线。

82.图3d显示第一光刻工艺的叠加朝向第三方向a3偏移且第二光刻工艺的叠加未发生偏移的实施例。请参考图3d与图3a,因为第一导电区段3161和3162朝向第三方向a3偏移,所以第一导电区段3161接触且电连接第二导线3145的垂直导电部件108,而第一导电区段3162保持与垂直导电部件108电性隔离。因此,在电子束检测期间,第一导电区段3161呈现亮线,而第一导电区段3162呈现暗线。

83.图3e显示第二光刻工艺的叠加朝向第四方向a4偏移且第一光刻工艺的叠加未发生偏移的实施例。请参考图3e与图3a,因为第二导电区段3181和3182朝向第四方向a4偏移,所以第二导电区段3181接触且电连接第一导线3121的垂直导电部件108,而第二导电区段3182保持与垂直导电部件108电性隔离。因此,在电子束检测期间,第二导电区段3181呈现亮线,而第二导电区段3182呈现暗线。

84.图3f显示第二光刻工艺的叠加朝向第三方向a3偏移且第一光刻工艺的叠加未发生偏移的实施例。请参考图3f与图3a,因为第二导电区段3181和3182朝向第三方向a3偏移,所以第二导电区段3181保持与垂直导电部件108电性隔离,而第二导电区段3182接触且电连接第一导线3122的垂直导电部件108。因此,在电子束检测期间,第二导电区段3181呈现暗线,而第二导电区段3182呈现亮线。

85.在对水平导电部件310进行电子束检测时,可以通过观察导电区段3161、3162、3181、3182的亮度,来判断形成水平导电部件310的光刻工艺的叠加是否发生偏移,并且可进一步辨别朝向哪一个方向发生偏移。

86.综上所述,本发明实施例利用不与垂直导电部件电连接的两个导电区段,作为判断光刻工艺是否发生叠加偏移的目标线。利用其一导电区段与相邻垂直导电部件之间的配置关系不同于另一导电区段与相邻垂直导电部件之间的配置关系,可实现偏移方向的辨别,从而提供更明确的缺陷信息。

87.虽然本发明以前述的实施例揭露如上,然其并非用以限定本发明。本领域技术人员,在不脱离本发明的精神和范围内,当可做些许的更动与润饰。因此本发明的保护范围须参考所附的权利要求限定范围。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。