技术特征:

1.一种半导体封装,包括:顺序地一个堆叠在另一个上的第一、第二、第三和第四半导体芯片,其中所述第一、第二、第三和第四半导体芯片中的每个包括在第一方向上交替布置的第一组接合焊盘和第二组接合焊盘,以及输入/输出电路,分别选择性地连接到所述第一组接合焊盘,以及其中所述第一、第二和第三半导体芯片中的每个包括电连接到所述第一组接合焊盘的第一组贯穿电极和电连接到所述第二组接合焊盘的第二组贯穿电极。2.根据权利要求1所述的半导体封装,其中所述第一半导体芯片和所述第三半导体芯片的所述第一组接合焊盘分别电连接到所述第二半导体芯片和所述第四半导体芯片的所述第二组接合焊盘,以及所述第一半导体芯片和所述第三半导体芯片的所述第二组接合焊盘分别电连接到所述第二半导体芯片和所述第四半导体芯片的所述第一组接合焊盘。3.根据权利要求1所述的半导体封装,其中所述第四半导体芯片的所述输入/输出电路被配置为通过所述第三半导体芯片的所述第二组贯穿电极、所述第二半导体芯片的所述第一组贯穿电极和所述第一半导体芯片的所述第二组贯穿电极传输信号。4.根据权利要求3所述的半导体封装,其中所述第三半导体芯片的所述输入/输出电路被配置为通过所述第二半导体芯片的所述第二组贯穿电极和所述第一半导体芯片的所述第一组贯穿电极传输信号。5.根据权利要求4所述的半导体封装,其中所述第二半导体芯片的所述输入/输出电路被配置为通过所述第一半导体芯片的所述第二组贯穿电极传输信号。6.根据权利要求1所述的半导体封装,其中所述第一、第二和第三半导体芯片包括相应的第一组贯穿电极和第二组贯穿电极的相同布置。7.根据权利要求6所述的半导体封装,其中所述第二半导体芯片在所述第一方向上从所述第一半导体芯片偏移一间隔,并且所述第三半导体芯片在所述第一方向的相反方向上从所述第二半导体芯片偏移所述间隔。8.根据权利要求7所述的半导体封装,其中所述间隔是彼此相邻的所述贯穿电极之间的距离。9.根据权利要求1所述的半导体封装,其中所述第一半导体芯片和所述第三半导体芯片的相应的第一组贯穿电极和第二组贯穿电极的第一布置不同于所述第二半导体芯片的所述第一组贯穿电极和所述第二组贯穿电极的第二布置。10.根据权利要求9所述的半导体封装,其中所述第一、第二和第三半导体芯片中的每个进一步包括熔丝部分,所述熔丝部分被配置为将所述输入/输出电路与所述第一组贯穿电极电分离。11.一种半导体封装,包括:顺序地一个堆叠在另一个上的第一、第二、第三和第四半导体芯片,其中所述第一、第二和第三半导体芯片中的每个包括在第一方向上交替布置的第一组贯穿电极和第二组贯穿电极,以及输入/输出电路,分别选择性地连接到所述第一组贯穿电极,其中所述第一半导体芯片和所述第三半导体芯片的所述第一组贯穿电极分别电连接

到所述第二半导体芯片的所述第二组贯穿电极,以及所述第一半导体芯片和所述第三半导体芯片的所述第二组贯穿电极分别电连接到所述第二半导体芯片的所述第一组贯穿电极。12.根据权利要求11所述的半导体封装,其中所述第一、第二和第三半导体芯片包括相应的第一组贯穿电极和第二组贯穿电极的相同布置。13.根据权利要求12所述的半导体封装,其中所述第二半导体芯片在所述第一方向上从所述第一半导体芯片偏移一间隔,并且所述第三半导体芯片在所述第一方向的相反方向上从所述第二半导体芯片偏移所述间隔。14.根据权利要求13所述的半导体封装,其中所述间隔是彼此相邻的所述贯穿电极之间的距离。15.根据权利要求11所述的半导体封装,其中所述第一半导体芯片和所述第三半导体芯片的相应的第一组贯穿电极和第二组贯穿电极的第一布置不同于所述第二半导体芯片的所述第一组贯穿电极和所述第二组贯穿电极的第二布置。16.根据权利要求15所述的半导体封装,其中所述第二半导体芯片与所述第一半导体芯片重叠而不偏离所述第一半导体芯片,并且所述第三半导体芯片与所述第二半导体芯片重叠而不偏离所述第二半导体芯片。17.根据权利要求11所述的半导体封装,其中所述第一、第二和第三半导体芯片中的每个进一步包括熔丝部分,所述熔丝部分被配置为将所述输入/输出电路与所述第一组贯穿电极电分离。18.根据权利要求11所述的半导体封装,其中所述第一、第二、第三和第四半导体芯片中的每个包括分别电连接到所述第一组贯穿电极的第一组接合焊盘和分别电连接到所述第二组贯穿电极的第二组接合焊盘。19.根据权利要求11所述的半导体封装,其中所述第四半导体芯片的输入/输出电路被配置为通过所述第三半导体芯片的所述第二组贯穿电极、所述第二半导体芯片的所述第一组贯穿电极和所述第一半导体芯片的所述第二组贯穿电极传输信号。20.一种半导体封装,包括:第一、第二、第三和第四半导体芯片,顺序地一个堆叠在另一个上并且通过导电连接构件彼此电连接,其中所述第一、第二、第三和第四半导体芯片中的每个包括彼此相反的第一表面和第二表面,在相应的第一表面上沿第一方向交替布置的第一组接合焊盘和第二组接合焊盘,以及分别选择性地连接到所述第一组接合焊盘的输入/输出电路,其中所述第一、第二和第三半导体芯片中的每个进一步包括第一组贯穿电极,电连接到所述第一组接合焊盘,以及第二组贯穿电极,电连接到所述第二组接合焊盘,以及其中所述第一半导体芯片和所述第三半导体芯片的所述第一组接合焊盘分别电连接到所述第二半导体芯片和所述第四半导体芯片的所述第二组接合焊盘,以及所述第一半导体芯片和所述第三半导体芯片的所述第二组接合焊盘分别电连接到所述第二半导体芯片和所述第四半导体芯片的所述第一组接合焊盘。

技术总结

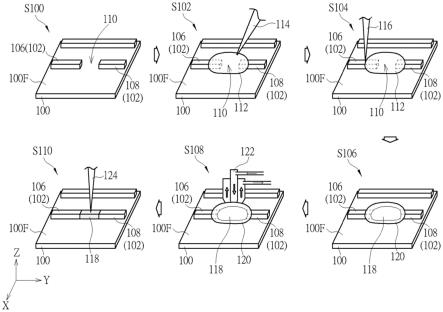

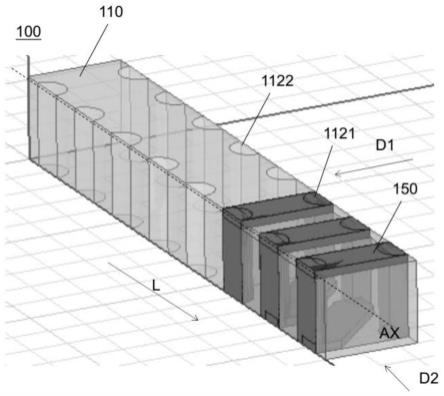

一种半导体封装包括顺序地一个堆叠在另一个上的第一、第二、第三和第四半导体芯片。第一、第二、第三和第四半导体芯片中的每个包括包括在第一方向上交替布置的第一组接合焊盘和第二组接合焊盘以及分别选择性地连接到第一组接合焊盘的输入/输出(I/O)电路。第一、第二和第三半导体芯片中的每个包括电连接到第一组接合焊盘的第一组贯穿电极和电连接到第二组接合焊盘的第二组贯穿电极。二组接合焊盘的第二组贯穿电极。二组接合焊盘的第二组贯穿电极。

技术研发人员:赵升贤 孙俊植 秋喆焕

受保护的技术使用者:三星电子株式会社

技术研发日:2022.08.05

技术公布日:2023/2/17

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。