半导体装置及其制造方法

1.相关申请

2.本技术案享有以日本专利申请案第2021-131344号(申请日:2021年8月11日)为基础申请案的优先权。本技术案通过参照所述基础申请案而包含基础申请案的全部内容。

技术领域

3.本发明的实施方式涉及一种半导体装置及其制造方法。

背景技术:

4.在设计半导体装置内的多条布线的布局时,理想的是降低这些布线的密度。

技术实现要素:

5.实施方式提供一种能够降低布线密度的半导体装置及其制造方法。

6.根据一实施方式,半导体装置具备:衬底;多个晶体管,设置于所述衬底上;及积层膜,设置于所述多个晶体管的上方,包含在第1方向上互相隔开的多个电极层,且具有第1区域、相对于所述第1区域位于与所述第1方向交叉的第2方向侧的第2区域、及相对于所述第1区域位于所述第2方向的相反侧的第3区域。所述装置还具备:多个插塞,在所述第1区域内,分别设置于所述多个电极层;第1柱状部,设置于所述第2区域内,包含在所述第1方向延伸的第1半导体层、及设置于所述第1半导体层与所述多个电极层间的第1电荷累积层;及第2柱状部,设置于所述第3区域内,包含在所述第1方向延伸的第2半导体层、及设置于所述第2半导体层与所述多个电极层间的第2电荷累积层。所述多个电极层中的至少1个电极层是包含所述第1区域内所含的第1部分、所述第2区域内所含的第2部分、及所述第3区域内所含的第3部分,且从所述第2部分经由所述第1部分到达所述第3部分的连续膜。所述多个晶体管包含:第1晶体管,设置于所述第1区域的正下,且电连接于所述多个插塞中的第1插塞;第2晶体管,设置于所述第2区域的正下,且电连接于所述多个插塞中的第2插塞;及第3晶体管,设置于所述第3区域的正下,且电连接于所述多个插塞中的第3插塞。

附图说明

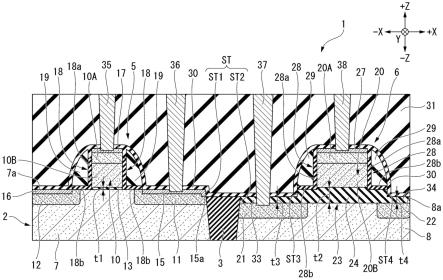

7.图1是表示第1实施方式的半导体装置的构造的剖视图。

8.图2是表示第1实施方式的半导体装置的构造的俯视图。

9.图3是表示第1实施方式的比较例的半导体装置的构造的剖视图。

10.图4是表示第1实施方式的比较例的半导体装置的构造的俯视图。

11.图5是表示第1实施方式的柱状部的构造的剖视图。

12.图6、图7是表示第1实施方式的半导体装置的制造方法的剖视图。

13.图8是表示第1实施方式的第1变化例的半导体装置的构造的俯视图。

14.图9是表示第1实施方式的第2变化例的半导体装置的构造的俯视图。

15.图10是表示第1实施方式的第2变化例的半导体装置的构造的剖视图。

16.图11是表示第1实施方式的第3变化例的半导体装置的构造的俯视图。

17.图12是表示第1实施方式的第3变化例的半导体装置的构造的剖视图。

18.图13是表示第1实施方式的第4变化例的半导体装置的构造的俯视图。

19.图14是表示第1实施方式的第5变化例的半导体装置的构造的俯视图。

20.图15是表示第1实施方式的半导体装置的构造的俯视图。

21.图16是表示第1实施方式的比较例的半导体装置的构造的俯视图。

22.图17(a)、(b)、图18(a)、(b)、图19(a)、(b)、图20(a)、(b)是表示第1实施方式的半导体装置的制造方法的剖视图。

23.图21是表示第2实施方式的半导体装置的构造的剖视图。

24.图22是表示图2所示的区域r1~r3的细节的俯视图。

25.图23是表示图2所示的区域r1~r3等的细节的另一俯视图。

26.图24是表示第1实施方式的变化例的电极层23-1~23-8及接点插塞26-1~26-8的布局的俯视图。

27.图25(a)、(b)是表示图2所示的半导体装置的细节的俯视图。

28.图26(a)、(b)是表示图8所示的半导体装置的细节的俯视图。

29.图27(a)、(b)是表示图9所示的半导体装置的细节的俯视图。

30.图28(a)、(b)是表示图13所示的半导体装置的细节的俯视图。

具体实施方式

31.以下,参照附图说明本发明的实施方式。图1~图28中,对同一构成标注同一符号,省略重复说明。

32.(第1实施方式)

33.图1是表示第1实施方式的半导体装置的构造的剖视图。

34.图1的半导体装置例如是3维半导体存储器。所述半导体装置具备电路部分1、及设置于电路部分1上的阵列部分2。阵列部分2具备包含多个存储单元的存储单元阵列,电路部分1具备控制存储单元阵列的cmos(complementary metal oxide semiconductor:互补金属氧化物半导体)电路。所述半导体装置例如通过使包含电路部分1的电路晶圆、与包含阵列部分2的阵列晶圆贴合而制造。图1示出电路部分1(电路晶圆)与阵列部分2(阵列晶圆)的贴合面s。

35.图1示出互相垂直的x方向、y方向及z方向。本说明书中,将 z方向作为上方向处理,将-z方向作为下方向处理。-z方向可与重力方向一致,也可不与重力方向一致。z方向为第1方向的例子,x方向为与第1方向交叉的第2方向的例子,y方向为与第1及第2方向交叉的第3方向的例子。

36.电路部分1具备衬底11、多个晶体管12、多个晶体管13及层间绝缘膜14。阵列部分2具备层间绝缘膜21、多层绝缘膜22、多个电极层23、多个柱状部24、多层绝缘膜25及多个接点插塞26。各晶体管12包含栅极绝缘膜12a、栅极电极12b、扩散层12c及扩散层12d,各晶体管13包含栅极绝缘膜13a、栅极电极13b、扩散层13c及扩散层13d。图1还示出交替包含多层绝缘膜22与多个电极层23的积层膜p。

37.电路部分1还具备多个接点插塞31、布线层32、多个通孔插塞33、布线层34、多个通

孔插塞35、及多个金属焊垫36。阵列部分2还具备多个金属焊垫41、多个通孔插塞42、布线层43、多个通孔插塞44、布线层45、及多个通孔插塞46。布线层32、34、43、45各自包含多条配线。

38.衬底11例如为硅衬底等半导体衬底。图1中,衬底11的上表面与x方向及y方向平行,与z方向垂直。图1示出衬底11上的区域r1、r2、r3。

39.区域r1、r2、r3各自包含衬底11上的层间绝缘膜14、层间绝缘膜21及积层膜p。区域r1还包含设置于积层膜p内的接点插塞26等。区域r1内的积层膜p相当于本实施方式的半导体装置内的挂钩部。另一方面,区域r2、r3还包含设置于积层膜p内的柱状部24等。区域r2、r3内的积层膜p相当于本实施方式的半导体装置内的存储单元阵列部。区域r1位于区域r2与区域r3之间。区域r2相对于区域r1位于 x方向侧。区域r3相对于区域r1位于-x方向侧。积层膜p内的区域r1为第1区域的例子,积层膜p内的区域r2为第2区域的例子,积层膜p内的区域r3为第3区域的例子。 x方向侧为第2方向侧的例子,-x方向侧为第2方向的相反侧的例子。

40.晶体管12设置于衬底11上。各晶体管12的栅极绝缘膜12a及栅极电极12b依序积层于衬底11上。各晶体管12的扩散层12c及扩散层12d以隔着栅极电极12b的方式形成于衬底11内。扩散层12c及扩散层12d的一个作为源极区域发挥功能,扩散层12c及扩散层12d的另一个作为漏极区域发挥功能。各晶体管12经由金属焊垫36、41等与对应的柱状部24电连接。本实施方式的晶体管12如图1所示,仅设置于区域r1、r2、r3中的区域r2、r3内。

41.晶体管13设置于衬底11上。各晶体管13的栅极绝缘膜13a及栅极电极13b依序积层于衬底11上。各晶体管13的扩散层13c及扩散层13d以隔着栅极电极13b的方式形成于衬底11内。扩散层13c及扩散层13d的一个作为源极区域发挥功能,扩散层13c及扩散层13d的另一个作为漏极区域发挥功能。各晶体管13经由金属焊垫36、41与对应的接点插塞26电连接。本实施方式的晶体管13如图1所示,不仅设置于区域r1内,也设置于区域r2、r3内。区域r1内的晶体管13为第1区域的正下的第1晶体管的例子,区域r2内的晶体管13为第2区域的正下的第2晶体管的例子,区域r3内的晶体管13为第3区域的正下的第3晶体管的例子。

42.层间绝缘膜14设置于衬底11上,覆盖晶体管12与晶体管13。层间绝缘膜14例如为包含氧化硅膜与其它绝缘膜的积层膜。

43.层间绝缘膜21设置于层间绝缘膜14上,夹在层间绝缘膜14与积层膜p之间。层间绝缘膜21例如是包含氧化硅膜与其它绝缘膜的积层膜。

44.所述多层绝缘膜22与所述多个电极层23交替积层于衬底11上方的层间绝缘膜21上,形成积层膜p。这些电极层23在z方向上互相隔开。各绝缘膜22例如为氧化硅膜。各电极层23例如为包含w(钨)层的金属层。各电极层23例如作为字线发挥功能。

45.图1作为所述多个电极层23的例子,示出8个电极层23-1~23-8。积层膜p沿z方向依序包含电极层23-1~23-8。电极层23-1~23-8是第1到第n电极层(n为2以上的整数)的例子。n的值在本实施方式中为8,但也可为8以外的整数。

46.本实施方式的各电极层23成为包含区域r1内所含的部分、区域r2内所含的部分、及区域r3内所含的部分,且连续设置于这3个部分内的连续膜。也就是说,本实施方式的各电极层23成为从区域r3经由区域r1向区域r2在x方向上连续延伸,从区域r3经由区域r1到达区域r2的连续膜。区域r1内所含的部分为第1部分的例子,区域r2内所含的部分为第2部

分的例子,区域r3内所含的部分为第3部分的例子。另外,所述多个电极层23也可包含不与这种连续膜相当的电极层23。

47.柱状部24在区域r2、r3内设置于积层膜p内。各柱状部24具有在z方向延伸的柱状形状,贯通电极层23-1~23-8。各柱状部24如后所述,包含电荷累积层与通道半导体层。各柱状部24内的通道半导体层与对应的晶体管12电连接。区域r2内的柱状部24为第1柱状部的例子,区域r3内的柱状部24为第2柱状部的例子。

48.绝缘膜25与接点插塞26在区域r1内设置于积层膜p内。各绝缘膜25例如为氧化硅膜。各接点插塞26例如为多晶硅层或金属层。各接点插塞26介隔绝缘膜25设置于积层膜p内,与对应的电极层23电连接。而且,各接点插塞26与对应的晶体管13电连接。

49.图1作为接点插塞26的例子,示出8个接点插塞26-1~26-8。图1所示的接点插塞26-1~26-8沿x方向依序排列。接点插塞26-1~26-8分别从积层膜p的下表面向电极层23-1~23-8的下表面延伸,与电极层23-1~23-8电连接。结果,接点插塞26-k(k为满足2≦k≦8的整数)贯通电极层23-1~23-(k-1),与电极层23-k相接。例如,接点插塞26-6贯通电极层23-1~23-5,与电极层23-6相接。接点插塞26-1~26-8为第1到第n连接插塞的例子。此外,接点插塞26-k为第k连接插塞的例子,电极层23-k为第k电极层的例子。

50.图1示出依序设置于衬底11上的接点插塞31、布线层32、通孔插塞33、布线层34、通孔插塞35、金属焊垫36、金属焊垫41、通孔插塞42、布线层43、通孔插塞44、布线层45及通孔插塞46。各接点插塞31在图1中与晶体管12或13的扩散层12c或13c电连接,但也可与晶体管12或13的栅极电极12b或13b电连接。各金属焊垫36与对应的金属焊垫41接合。各通孔插塞46与对应的柱状部24或接点插塞26电连接。

51.结果,各柱状部24经由这些插塞、布线层及焊垫,与对应的晶体管12电连接。另一方面,各接点插塞26经由这些插塞、布线层及焊垫,与对应的晶体管13电连接。布线层45包含将各柱状部24与对应的晶体管12电连接的布线(位线)。本实施方式的位线在y方向延伸。

52.图1以虚线示出将接点插塞26-1~26-8分别与晶体管13电连接的布线51-1~51-8。布线51-1~51-8由接点插塞31、布线层32、通孔插塞33、布线层34、通孔插塞35、金属焊垫36、金属焊垫41、通孔插塞42、布线层43、通孔插塞44、布线层45及通孔插塞46形成。因此,布线51-1~51-8各自包含至少一对金属焊垫36、41。这些金属焊垫36、41互相相接,将电路部分1与阵列部分2电连接。

53.本实施方式的布线51-1~51-8分别相对于接点插塞26-1~26-8位于区域r2侧或区域r3侧。例如,布线51-1相对于接点插塞26-1位于区域r2侧,从区域r1向区域r2延伸,到达区域r2。结果,布线51-1与设置于区域r2内的晶体管13电连接。另一方面,布线51-8相对于接点插塞26-8位于区域r3侧,从区域r1向区域r3延伸,到达区域r3。结果,布线51-8与设置于区域r3内的晶体管13电连接。与区域r1、r2、r3内的晶体管13电连接的接点插塞26分别为第1、第2、第3插塞的例子。

54.本实施方式中,布线51-k1(k1为满足1≦k1≦4的整数)相对于接点插塞26-k1位于区域r2侧,布线51-k2(k2为满足4<k2≦8的整数)相对于接点插塞26-k2位于区域r3侧。例如,布线51-3相对于接点插塞26-5位于区域r2侧,在接点插塞26-3的右侧延伸。另一方面,布线51-6相对于接点插塞26-6位于区域r3侧,在接点插塞26-6的左侧延伸。另外,布线51-3与布线51-6均与设置于区域r1内的晶体管13电连接。布线51-k1为第k1布线的例子,接点插

塞26-k1为第k1连接插塞的例子。而且,布线51-k1为第k2布线的例子,接点插塞26-k2为第k2连接插塞的例子。

55.另外,布线51-k1也可如位于接点插塞26-4的正下的布线51-4,位于接点插塞26-k1的正下。同样,布线51-k2也可如位于接点插塞26-5的正下的布线51-5,位于接点插塞26-k2的正下。

56.根据本实施方式,通过将晶体管13配置于区域r2、r3内,例如能够减少半导体装置内的布线51-1~51-8的密度。参照图2~图4,对所述细节进行说明。

57.另外,接点插塞26-1~26-8在图1中示出于相同的xz剖面内,但也可不设置于相同的xz剖面内。同样,布线51-1~51-8在图1中示出于相同的xz剖面内,但也可不设置于相同的xz剖面内。实际上,后述的图2所示的布线51-1~51-8不设置于相同的xz剖面内。同样,与布线51-1~51-8电连接的晶体管13在图1中示出于相同的xz剖面内,但也可不设置于相同的xz剖面内。

58.图2是表示第1实施方式的半导体装置的构造的俯视图。

59.图2示出图1所示的区域r1、r2、r3。区域r2位于区域r1的 x方向,区域r3位于区域r1的-x方向。图2还示出区域r2内所含的区域r1、r2、r3、r4。区域r1~r4向 x方向依序排列。区域r2~r4例如包含3维半导体存储器的周边电路。更详细来说,本实施方式的区域r2、r4包含周边电路内的感测放大器(s/a),本实施方式的区域r3包含周边电路内的其它部分。本实施方式的区域r1~r3形成1个块b1。

60.图2还示出具有与区域r1~r3同样构造的区域r1’~r3’、或具有与区域r1~r4同样构造的区域r1’~r4’。区域r2’位于区域r1’的 x方向,区域r3’位于区域r1’的-x方向。区域r1’~r4’包含于区域r3’内,向-x方向依序排列。区域r2’~r4’例如包含3维半导体存储器的周边电路。更详细来说,本实施方式的r2’、r4’与区域r2、r4同样,包含周边电路内的感测放大器,本实施方式的区域r3’与区域r3同样,包含周边电路内的其它部分。本实施方式的区域r1’~r3’形成1个块b2。块b2内的各电极层23与块b1内的对应的电极层23,利用块b1与块b2间的缝隙分断。另一方面,布线层45内的各位线设置于块b1及块b2内,设置于任1个感测放大器上,且与所述感测放大器电连接。

61.另外,本实施方式的区域r3具有t字形状,包含夹在区域r2与区域r4间的部分、夹在区域r2与区域r1’间的部分、及夹在区域r4与区域r2’间的部分。同样,本实施方式的区域r3’具有t字形状,包含夹在区域r2’与区域r4’间的部分、夹在区域r2’与区域r1间的部分、及夹在区域r4’与区域r3间的部分。

62.区域r1如上所述,包含接点插塞26-1~26-8。接点插塞26-1~26-8分别与布线51-1~51-8电连接。图2中,布线51-1~51-8各自具有l字型的平面形状,在俯视时具有1个弯折部位。这些布线51-1~51-8各自也可具有更复杂的平面形状,例如,也可在俯视时具有2个以上弯折部位。图1示出沿图2所示的a-a’线的xz剖面。

63.本实施方式的布线51-1~51-8分别如上所述,相对于接点插塞26-1~26-8位于区域r2侧或区域r3侧。例如,布线51-1、51-2、51-3、51-4分别相对于接点插塞26-1、26-2、26-3、26-4位于区域r2侧,从区域r1向区域r2延伸。另一方面,布线51-5、51-6、51-7、51-8分别相对于接点插塞26-5、26-6、26-7、26-8位于区域r3侧,从区域r1向区域r3延伸。例如,布线51-1~51-8用的晶体管13分别在区域r2或区域r3内配置于布线51-1~51-8的前端附近。

64.以下,将布线51-1~51-8都记作布线51。图2示出在本实施方式的区域r2或区域r3内,在y方向彼此相邻的布线51间的距离d1。根据本实施方式,通过降低半导体装置内的布线51的密度,能够加长距离d1。

65.另外,图2所示的布线51-1、51-2、51-3、51-4均到达区域r2,但布线51-1、51-2、51-3、51-4的一部分也可不到达区域r2。例如,图1所示的布线51-2、51-3、51-4不到达区域r2,仅布线51-1到达区域r2。此外,布线51-1、51-2、51-3、51-4的一部分也可相对于接点插塞26-1、26-2、26-3、26-4不位于区域r2侧。例如,布线51-3、51-5、51-7中的至少任一条也可具有在y方向上直线状延伸的平面形状。所述布线51用的晶体管13也可在区域r1内配置于布线51的前端附近。图2所示的布线51-1、51-2、51-3、51-4的前端位于区域r2的区域r1内。

66.同样,图2所示的布线51-5、51-6、51-7、51-8均到达区域r3,但布线51-5、51-6、51-7、51-8的一部分也可不到达区域r3。例如,图1所示的布线51-6、51-7、51-8也可不到达区域r3,仅布线51-8到达区域r3。此外,布线51-5、51-6、51-7、51-8的一部分也可相对于接点插塞26-5、26-6、26-7、26-8不位于区域r3侧。例如,布线51-5、51-6、51-7中的至少任一条也可具有在y方向上直线状延伸的平面形状。所述布线51用的晶体管13也可在区域r1内配置于布线51的前端附近。

67.图2进一步示出区域r1’内的接点插塞26-1’~26-8’、及分别电连接于接点插塞26-1’~26-8’的布线51-1’~51-8’。接点插塞26-1’~26-8’的构造分别与接点插塞26-1~26-8的构造同样。布线51-1’~51-8’的构造分别与布线51-1~51-8的构造同样。例如,接点插塞26-1’~26-8’的z方向的长度分别与接点插塞26-1~26-8的z方向的长度相同。此外,接点插塞26-1’~26-8’分别电连接于设置成与8个电极层23-1~23-8相同高度的8个电极层23。

68.另外,本实施方式的区域r1~r3内的各电极层23如上所述,从区域r3经由区域r1向区域r2在x方向上连续延伸(参照图1)。本实施方式的区域r1~r3内的各电极层23进一步从区域r1经由区域r2、r3向区域r4在x方向上连续延伸。同样,本实施方式的区域r1’~r3’内的各电极层23从区域r2’经由区域r1’、r1’、r2’、r3’向区域r4’在-x方向上连续延伸。

69.图22是表示图2所示的区域r1~r3的细节的俯视图。

70.如图22所示,本实施方式的区域r1~r3包含在x方向延伸的多个单元u。这些单元u在y方向上彼此相邻。这些单元u各自包含图2所示的接点插塞26-1~26-8及布线51-1~51-8。换句话说,图2示出区域r1~r3所含的多个单元u中的1个。各单元u例如与3维半导体存储器的1个块对应。

71.另外,本实施方式的区域r1’~r3’也与区域r1~r3同样,包含多个单元u。但,区域r1’~r3’的各单元u包含图2所示的接点插塞26-1’~26-8’及布线51-1’~51-8’。此外,后述的图4、图8、图9、图11、图13及图14所示的半导体装置各自也同样包含多个单元u。

72.图23是表示图2所示的区域r1~r3等的细节的另一俯视图。

73.图23例示区域r1~r3所含的12个单元u、及区域r1’~r3’所含的12个单元u。但,图23所示的各单元u包含12个接点插塞26(或26’)与12条布线51(或51’)。区域r1~r3内的单元u彼此在y方向上互相相邻。同样,区域r1’~r3’内的单元u彼此在y方向上互相相邻。

74.图24是表示第1实施方式的变化例的电极层23-1~23-8及接点插塞26-1~26-8的布局的俯视图。图24示出从下朝上观察电极层23-1~23-8及接点插塞26-1~26-8的情况。

75.图1所示的电极层23-1~23-8及接点插塞26-1~26-8也可以如图24所示的变化例那样的布局配置。图24中,电极层23-8的下表面的一部分从电极层23-7露出,电极层23-7的下表面的一部分从电极层23-6露出。而且,电极层23-6的下表面的一部分从电极层23-5露出,电极层23-5的下表面的一部分从电极层23-4露出。而且,电极层23-4的下表面的一部分从电极层23-3露出,电极层23-3的下表面的一部分从电极层23-2露出,电极层23-2的下表面的一部分从电极层23-1露出。

76.接点插塞26-8~26-2分别配置于电极层23-8~23-2的露出部分下。同样,接点插塞26-1配置于电极层23-1下。这些接点插塞26-1~26-8如图25所示,沿着在x方向延伸的直线l配置。

77.图25是表示图2所示的半导体装置的细节的俯视图。

78.图25(a)示出电路部分1的构造。如上所述,区域r2、r4、r2’、r4’包含周边电路内的感测放大器,区域r3、r3’包含周边电路内的其它部分。此外,电路部分1包含跨过区域r1、r3、r1的挂钩区域(wlhu)、及跨过区域r1’、r2’、r1’的挂钩区域。感测放大器包含所述的晶体管12,挂钩区域包含所述的晶体管13(参照图1)。

79.图25(b)示出阵列部分2的构造。如上所述,区域r1包含接点插塞26,区域r1~r3内的各电极层23在符号k所示的范围内在x方向连续延伸。同样,区域r1’包含接点插塞26’,区域r1’~r3’内的各电极层23在符号k所示的范围内在x方向连续延伸。

80.图3是表示第1实施方式的比较例的半导体装置的构造的剖视图。

81.本比较例的半导体装置(图3)具有与第1实施方式的半导体装置(图1)大致同样的构造。然而,本比较例的积层膜p在区域r1内具有阶梯构造,在积层膜p的阶梯构造下设有层间绝缘膜52。结果,本比较例的接点插塞26-k(k为满足2≦k≦8的整数)不贯通电极层23-1~23-(k-1),而与电极层23-k相接。本比较例的接点插塞26-k取代电极层23-1~23-(k-1),贯通层间绝缘膜52。

82.本比较例的半导体装置(图3)具备区域r1、r2,但不具备区域r3。因此,本比较例的晶体管12设置于区域r2内,不设置于区域r3内。此外,本比较例的晶体管13设置于区域r1、r2内,不设置于区域r3内。此外,本比较例的布线51-1~51-8分别相对于接点插塞26-1~26-8位于区域r2侧。另外,图3为了容易观看附图,而省略形成布线51-2、51-4、51-5、51-7的一部分插塞、布线层及焊垫的图示。

83.图4是表示第1实施方式的比较例的半导体装置的构造的俯视图。

84.图4与图2同样,示出区域r1、r2、r1、r2、r3,但未示出区域r3、r4。而且,图4与图2同样,示出区域r1’、r3’、r1’、r2’、r3’,但未示出区域r2’、r4’。本比较例的半导体装置不具备区域r3、r4、r2’、r4’。图3示出沿图4所示的b-b’线的xz剖面。

85.本比较例的布线51-1~51-8分别如上所述,相对于接点插塞26-1~26-8位于区域r2侧。图4示出在本比较例的区域r2内在y方向彼此相邻的布线51间的距离d2。本比较例的距离d2短于第1实施方式的d1。由此,在本比较例的半导体装置内,布线51的密度变高。

86.图4所示的布线51-1~51-8均到达区域r2。由此,图4所示的区域r2包含8条布线51,区域r2内的布线51间的距离d2变短。另一方面,图2所示的布线51-1~51-8到达区域r2或区域r3。由此,图2所示的区域r2、r3各自仅包含4条布线51,区域r2、r3内的布线51间的距离d1变长。如此,根据本实施方式,将布线51-1~51-8的一部分向区域r2延长,将布线51-1

~51-8的另一部分向区域r3延长,由此能够减少半导体装置内的布线51-1~51-8的密度。图2所示的距离d1为图4所示的距离d2的2倍左右。

87.另外,本实施方式的布线51-1~51-8如上所述,也可包含既未到达区域r2也未到达区域r3的布线51。所述情况下,区域r2、r3内的布线51间的距离d1能够进一步变长。

88.以上对于布线51-1’~51-8’也同样。根据本实施方式,将布线51-1’~51-8’的一部分向区域r2’延长,将布线51-1’~51-8’的另一部分向区域r3’延长,由此能够减少半导体装置内的布线51-1’~51-8’的密度。

89.图5是表示第1实施方式的柱状部24的构造的剖视图。

90.本实施方式的各柱状部24(参照图1)具有图5所示的构造。图5所示的柱状部24包含依序形成于积层膜p的侧面的块绝缘膜24a、电荷累积层24b、通道绝缘膜24c、通道半导体层24d及核心绝缘膜24e。

91.块绝缘膜24a例如为氧化硅膜。电荷累积层24b例如为氮化硅膜等绝缘膜。电荷累积层24b也可为多晶硅层等半导体层。通道绝缘膜24c例如为氧化硅膜。通道半导体层24d例如为多晶硅层。核心绝缘膜24d例如为氧化硅膜。

92.图6及图7是表示第1实施方式的半导体装置的制造方法的剖视图。

93.图6示出电路晶圆所含的电路部分1、及阵列晶圆所含的阵列部分2。图6所示的阵列部分2的朝向与图1所示的阵列部分2的朝向为反方向。本实施方式的半导体装置如上所述,通过使电路晶圆与阵列晶圆贴合而制造。图6示出为了贴合而使朝向反转前的阵列部分2,图7示出为了贴合而使朝向反转,与电路部分1贴合后的阵列部分2。

94.图6示出电路部分1的上表面s1与阵列部分2的上表面s2。图6所示的阵列部分2具备设置于积层膜p下的衬底53。衬底53例如为硅衬底等半导体衬底。衬底11为第1衬底的例子,衬底53为第2衬底的例子。

95.本实施方式的半导体衬底例如如下所述制造。首先,在衬底11上形成多个晶体管12、多个晶体管13、层间绝缘膜14、多个接点插塞31、布线层32、多个通孔插塞33、布线层34、多个通孔插塞35及多个金属焊垫36(图6)。此外,在衬底53上形成层间绝缘膜21、多层绝缘膜22、多个电极层23、多个柱状部24、多层绝缘膜25、多个接点插塞26、多个金属焊垫41、多个通孔插塞42、布线层43、多个通孔插塞44、布线层45及多个通孔插塞46(图6)。

96.接着,如图7所示,使电路晶圆(电路部分1)与阵列晶圆(阵列部分2)通过机械性压力而贴合。由此,将层间绝缘膜14与层间绝缘膜21接着。接着,将电路晶圆及阵列晶圆以400℃进行退火。由此,将金属焊垫36与金属焊垫41接合。金属焊垫36、41例如为包含cu(铜)层的金属层。

97.结果,各柱状部24与对应的晶体管12电连接,各接点插塞26与对应的晶体管13电连接(图7)。此外,在衬底11与积层膜p间形成布线51-1~51-8(图7)。

98.图7示出区域r1~r3。图7所示的区域r1~r3的构造分别与图1所示的区域r1~r3的构造相同。例如,接点插塞26设置于区域r1内,柱状部24设置于区域r2、r3内。此外,晶体管12设置于区域r2、r3内,晶体管13设置于区域r1~r3内。此外,布线51-1~51-8分别在接点插塞26-1~26-8的右侧或左侧延伸。

99.之后,将衬底11通过cmp(chemical mechanical polishing:化学机械研磨)而薄膜化,将衬底53通过cmp去除后,将电路晶圆及阵列晶圆切断成多个芯片。如此,制造图1所

示的半导体装置。

100.另外,图1示出层间绝缘膜14与层间绝缘膜21的边界面、或金属焊垫36与金属焊垫41的边界面,但一般来说,在所述退火后将观察不到这些边界面。然而,存在这些边界面的位置能够通过检测金属焊垫36的侧面的倾斜度、金属焊垫41的侧面的倾斜度、或金属焊垫36与金属焊垫41的位置偏差而推定。

101.接着,参照图8~图14,针对第1实施方式的各种变化例进行说明。对于这些变化例,以与第1实施方式的不同点为中心进行说明,适当省略与第1实施方式的共通点的说明。

102.(1)第1变化例

103.图8是表示第1实施方式的第1变化例的半导体装置的构造的俯视图。

104.本变化例中,区域r1包含互相分离的区域r1a、r1b。区域r1a为第1部分区域的例子,区域r1b为第2部分区域的例子。区域r2位于区域r1a的 x方向,区域r3位于区域r1b的-x方向。区域r2包含区域r1、r2、r3。区域r1位于区域r1的 x方向,区域r2位于区域r1的 x方向,区域r3位于区域r1的 x方向及区域r2的 y方向。图8还示出位于区域r1b的 x方向的区域r4。区域r4示出位于区域r1b的 x方向的区域r4、与位于区域r1b的 x方向及位于区域r4的-y方向的区域r5。

105.本变化例的接点插塞26-1~26-8设置于区域r1a、r1b内。具体来说,接点插塞26-1~26-4设置于区域r1a内,接点插塞26-5~26-8设置于区域r1b内。接点插塞26-1~26-4为第ka到第kb连接插塞的例子,接点插塞26-5~26-8为第kc到第kd连接插塞的例子(ka、kb、kc、kd为满足1≦ka≦kb≦kc≦kd≦8的整数)。本变化例中,ka=1,kb=4,kc=5,kd=8。

106.本变化例的布线51-1~51-8分别相对于接点插塞26-1~26-8位于区域r2侧或区域r3侧。例如,布线51-1~51-4分别相对于接点插塞26-1~26-4位于区域r2侧,从区域r1a向区域r2延伸。此外,布线51-5~51-8分别相对于接点插塞26-5~26-8位于区域r3侧,从区域r1b向区域r3延伸。

107.图8示出在本变化例的区域r2或区域r3内在y方向彼此相邻的布线51间的距离d3。本变化例的布线51-5~51-8与第1实施方式的情况同样,配置于区域r2、r3内。由此,能够加长距离d3,并能够降低半导体装置内的布线51的密度。图8所示的距离d3与图2所示的距离d1为相同程度。

108.本变化例中,还使区域r1’包含互相分离的区域r1a’、r1b’,使区域r3’包含区域r1’、r2’、r3’。区域r1a’、r1b’、r1’、r2’、r3’的构造分别与区域r1a、r1b、r1、r2、r3的构造同样。图8还示出位于区域r1a’的-x方向的区域r4’,区域r4’包含区域r4’、r5’。区域r4’、r4’、r5’的构造分别与区域r4、r4、r5的构造同样。本变化例中,区域r2位于区域r1a’与区域r4’之间,区域r3’位于区域r1b与区域r4之间。

109.图26是表示图8所示的半导体装置的细节的俯视图。

110.图26(a)示出电路部分1的构造。区域r2、r4、r2’、r4’包含周边电路内的感测放大器,区域r3、r5、r3’、r5’包含周边电路内的其它部分。此外,电路部分1包含跨过区域r1a、r1的挂钩区域(wlhu)、跨过区域r1b、r3的挂钩区域、跨过区域r1a’、r2’的挂钩区域、及跨过区域r1b’、r1’的挂钩区域。

111.图26(b)示出阵列部分2的构造。区域r1a、r1a’包含接点插塞26、26’,区域r1a、r1a’、r2、r2’、r4’内的各电极层23在符号k所示的范围内在x方向上连续延伸。同样,区域

r1b、r1b’包含接点插塞26、26’,区域r1b、r1b’、r3、r3’、r4内的各电极层23在符号k所示的范围内在x方向上连续延伸。

112.(2)第2变化例

113.图9是表示第1实施方式的第2变化例的半导体装置的构造的俯视图。

114.与第1变化例的情况同样,本变化例的区域r1包含互相分离的区域r1a、r1b。本变化例中,还使区域r2包含互相分离的区域r2a、r2b,使区域r3包含互相分离的区域r3a、r3b。本变化例的区域r2a与第1变化例的区域r2同样,包含区域r1、r2、r3。

115.区域r2a位于区域r1a的 x方向,区域r2b位于区域r1b的 x方向。区域r2a为第3部分区域的例子,区域r2b为第4部分区域的例子。区域r3a位于区域r1a的-x方向,区域r3b位于区域r1b的-x方向。区域r3a为第5部分区域的例子,区域r3b为第6部分区域的例子。区域r5a位于区域r4a的 x方向,区域r5b位于区域r4b的 x方向。区域r6a位于区域r4a的-x方向,区域r6b位于区域r4b的-x方向。

116.本变化例的接点插塞26-1~26-8设置于区域r1a、r1b内。具体来说,接点插塞26-1~26-4设置于区域r1a内,接点插塞26-5~26-8设置于区域r1b内。接点插塞26-1~26-4为第ka到第kb连接插塞的例子,接点插塞26-5~26-8为第kc到第kd连接插塞的例子。本变化例中,ka=1,kb=4,kc=5,kd=8。

117.本变化例的布线51-1~51-8分别相对于接点插塞26-1~26-8位于区域r2a、r2b、r3a或r3b侧。例如,布线51-1、51-2分别相对于接点插塞26-1、26-2位于区域r2a侧。此外,布线51-5、51-6分别相对于接点插塞26-5、26-6位于区域r2b侧。此外,布线51-3、51-4分别相对于接点插塞26-3、26-4位于区域r3a侧。此外,布线51-7、51-8分别相对于接点插塞26-7、26-8位于区域r3b侧。

118.图9示出在本变化例的区域r2a、r2b、r3a或r3b内在y方向上彼此相邻的布线51间的距离d4。第1实施方式或第1变化例的布线51-1~51-8配置于2个区域r2、r3内,相对于此,本变化例的布线51-1~51-8配置于4个区域r2a、r2b、r3a、r3b内。由此,能够使距离d4长于距离d1或距离d3,且能够进一步降低半导体装置内的布线51的密度。图9所示的距离d4为图2所示的距离d1或图8所示的距离d3的2倍左右。

119.另外,图9所示的区域r1a’、r1b’的构造与区域r1a、r1b的构造同样。此外,图9所示的区域r2a’、r2b’、r3a’、r3b’的构造与区域r2a、r2b、r3a、r3b的构造同样。此外,图9所示的区域r1’、r2’、r3’的构造分别与区域r1、r2、r3的构造同样。

120.图10是表示第1实施方式的第2变化例的半导体装置的构造的剖视图。

121.图10示出沿图9所示的c-c’线的xz剖面。图10中,8个接点插塞26依接点插塞26-1、26-2、26-3、26-4、26-5、26-6、26-7、28-8的顺序排列。

122.图27是表示图9所示的半导体装置的细节的俯视图。

123.图27(a)示出电路部分1的构造。区域r2、r2’包含周边电路内的感测放大器,区域r3、r3’包含周边电路内的其它部分。此外,电路部分1包含跨过区域r1a、r1、r3a的挂钩区域(wlhu)、跨过区域r1b、r2b、r3b的挂钩区域、跨过区域r1a’、r2a’、r3a’的挂钩区域;及跨过区域r1b’、r2b’、r3’的挂钩区域。

124.图27(b)示出阵列部分2的构造。区域r1a、r1b包含接点插塞26,区域r1a、r2a、r3a、r1b、r2b、r3b内的各电极层23在符号k所示的范围内在x方向上连续延伸。同样,区域r1a、

1、26-2设置于一区域r1a内,接点插塞26-3、26-4设置于另一区域r1a内。此外,接点插塞26-5、26-6设置于一区域r1b内,接点插塞26-7、26-8设置于另一区域r1b内。接点插塞26-1~26-4为第ka到第kb连接插塞的例子,接点插塞26-5~26-8为第kc到第kd连接插塞的例子。本变化例中,ka=1,kb=4,kc=5,kd=8。

140.本变化例的布线51-1~51-8分别相对于接点插塞26-1~26-8位于区域r2a、r2b、r3a或r3b侧。例如,布线51-1、51-2分别相对于接点插塞26-1、26-2位于区域r2a侧。此外,布线51-3、51-4分别相对于接点插塞26-3、26-4位于区域r3a侧。此外,布线51-5、51-6分别相对于接点插塞26-5、26-6位于区域r2b侧。此外,布线51-7、51-8分别相对于接点插塞26-7、26-8位于区域r3b侧。

141.图13示出在本变化例的区域r2a、r2b、r3a或r3b内在y方向上彼此相邻的布线51间的距离d6。本变化例的布线51-1~51-8与第2及第3变化例的情况同样,配置于4个区域r2a、r2b、r3a、r3b内。由此,能够加长距离d6,并能够降低半导体装置内的布线51的密度。图13所示的距离d6与图9及图11所示的距离d4、d5为相同程度。

142.另外,图13所示的区域r1a’、r1b’、r2a’、r2b’、r3a’、r3b’、r4’的构造与区域r1a、r1b、r2a、r2b、r3a、r3b、r4的构造同样。此外,图13所示的区域r1a’、r2a’、r3a’、r1b’、r2b’、r3b’、r4’、r5’、r6’、r7’、r8’的构造与区域r1a、r2a、r3a、r1b、r2b、r3b、r4、r5、r6、r7、r8的构造同样。例如,块b1的积层膜p内的区域r1a、r3a、r3b’为第1积层膜内的第1、第2、第3区域的例子,块b2的积层膜p内的区域r1a、r2b、r2a为第2积层膜内的第4、第5、第6区域的例子。块b1内的接点插塞26为第1电极层插塞的例子,块b2内的接点插塞26为第2电极层插塞的例子。

143.此外,本变化例的区域r5具有l字形状,包含夹在区域r4与区域r1a’间的部分、及夹在区域r4与区域r2a’间的部分。同样,本变化例的区域r5’具有l字形状,包含夹在区域r4’与区域r1b间的部分、及夹在区域r4’与区域r3b间的部分。

144.图28是表示图13所示的半导体装置的细节的俯视图。

145.图28(a)示出电路部分1的构造。区域r2a、r2b、r4、r7、r2a’、r2b’、r4’、r7’包含周边电路内的感测放大器,区域r3a、r3b、r5、r8、r3a’、r3b’、r5’、r8’包含周边电路内的其它部分。此外,电路部分1包含跨过区域r1a、r1a的挂钩区域(wlhu)、跨过区域r1b、r1b的挂钩区域、跨过区域r1a、r6的挂钩区域、及跨过区域r1b、r3b的挂钩区域。此外,电路部分1包含跨过区域r1a’、r1a’的挂钩区域、跨过区域r1b’、r1b’的挂钩区域、跨过区域r1a’、r2a’的挂钩区域、及跨过区域r1b’、r6’的挂钩区域。

146.图28(b)示出阵列部分2的构造。 y方向的区域r1a、r1b、r1a’、r1b’包含接点插塞26, y方向的区域r1a、r1b、r1a’、r1b’内的各电极层23在符号k所示的范围内在x方向上连续延伸。同样,-y方向的区域r1a、r1b、r1a’、r1b’包含接点插塞26,-y方向的区域r1a、r1b、r1a’、r1b’内的各电极层23在符号k所示的范围内在x方向上连续延伸。

147.(5)第5变化例

148.图14是表示第1实施方式的第5变化例的半导体装置的构造的俯视图。

149.与第4变化例的情况同样,本变化例的区域r1~r3包含区域r1a~r3b,本变化例的区域r1包含互相分离的2个区域r1a及2个区域r1b。此外,区域r2a包含区域r1a、r2a、r3a。区域r2b包含区域r1b、r2b、r3b。区域r4包含区域r4、r5。区域r3a包含区域r6、r6、r8。区域r1a、

r2a、r3a、r1b、r2b、r3b、r4、r5、r6、r7、r8如图14所示,包含周边电路内的感测放大器或其它部分。

150.本变化例的接点插塞26-1~26-8设置于区域r1a、r1b内。具体来说,接点插塞26-1、26-3设置于一区域r1a内,接点插塞26-5、26-7设置于另一区域r1a内。此外,接点插塞26-2、26-4设置于一区域r1b内,接点插塞26-6、26-8设置于另一区域r1b内。接点插塞26-1、26-3、26-5、26-7为第k1连接插塞的例子。接点插塞26-2、26-4、26-6、26-8为第k2连接插塞的例子。

151.本变化例的布线51-1~51-8分别相对于接点插塞26-1~26-8位于区域r2a、r2b、r3a或r3b侧。例如,布线51-1、51-3分别相对于接点插塞26-1、26-3位于区域r2a侧。此外,布线51-5、51-7分别相对于接点插塞26-5、26-7位于区域r3a侧。此外,布线51-2、51-4分别相对于接点插塞26-2、26-4位于区域r2b侧。此外,布线51-6、51-8分别相对于接点插塞26-6、26-8位于区域r3b侧。

152.图14示出在本变化例的区域r2a、r2b、r3a或r3b内在y方向上彼此相邻的布线51间的距离d7。本变化例的布线51-1~51-8与第2到第4变化例的情况同样,配置于4个区域r2a、r2b、r3a、r3b内。由此,能够加长距离d7,并能够降低半导体装置内的布线51的密度。图14所示的距离d7与图9、图11及图13所示的距离d4、d5、d6为相同程度。

153.另外,图14所示的区域r1a’、r1b’、r2a’、r2b’、r3a’、r3b’、r4’的构造与区域r1a、r1b、r2a、r2b、r3a、r3b、r4的构造同样。此外,图14所示的区域r1a’、r2a’、r3a’、r1b’、r2b’、r3b’、r4’、r5’、r6’、r7’、r8’的构造与区域r1a、r2a、r3a、r1b、r2b、r3b、r4、r5、r6、r7、r8的构造同样。

154.此外,图28所示的构造也适用于本变化例。此外,第4或第5变化例的区域r1也可包含互相分离的m个区域r1a及m个区域r1b(m为2以上的整数)。

155.接着,参照图15及图16,再次将第1实施方式与它的比较例进行比较。

156.图15是表示第1实施方式的半导体装置的构造的俯视图。

157.本实施方式的半导体装置如图1及图2所示,具备区域r1、r2、r3等。所述半导体装置也可具有图15所示的构造。图15所示的半导体装置在区域r2与区域r3间具备2个区域r1。以下,针对图15的细节进行说明。

158.图15所示的半导体装置在区域r1、r2、r3内具备区域k1、k2、k3、k4。区域k1~k4在x方向延伸,由绝缘膜54互相分离。绝缘膜54嵌入到以贯通积层膜p(参照图1)的方式形成的缝隙内。

159.区域k1~k4各自在一区域r1内具备8个接点插塞26,在另一区域r1内具备8个接点插塞55。图15作为接点插塞26的例子,示出区域k1内的接点插塞26-1~26-8,作为接点插塞55的例子,示出区域k2内的接点插塞55-1~55-8。以下,针对接点插塞26、55的构造,以接点插塞26-1~26-8、55-1~55-8为例进行说明。

160.如上所述,接点插塞26-1~26-8分别与电极层23-1~23-8(图1)电连接。另一方面,接点插塞55-1~55-8均贯通积层膜p。如图15所示,接点插塞26-1~26-8分别由布线层43内的8条布线与接点插塞55-1~55-8电连接。这些布线各自经由金属焊垫41,与电路部分1(图1)电连接。根据本实施方式,能够将积层膜p上方的电路与接点插塞26-1~26-8经由接点插塞55-1~55-8电连接。

161.图16是表示第1实施方式的比较例的半导体装置的构造的俯视图。

162.本比较例的半导体装置如图3及图4所示,具备区域r1、r2等。所述半导体装置也可具有图16所示的构造。图16所示的半导体装置具备所述的区域r1与区域r2,还具备区域r3与另一区域r1。图16中,区域r2、r3夹在2个区域r1间。以下,针对图16的细节进行说明。

163.图16所示的半导体装置也在区域r1、r2、r3内具备区域k1、k2、k3、k4。图16所示的区域k1~k4的构造与图15所示的区域k1~k4的构造大致同样。

164.本比较例中,区域k1内的接点插塞26均与向区域r3延伸的布线51(图3及图4)电连接。由此,区域k1内的布线51在区域r3内变为高密度。此外,区域k2内的接点插塞26均与向区域r2延伸的布线51电连接。由此,区域k2内的布线51在区域r2内变为高密度。

165.另一方面,第1实施方式中,区域k1内的接点插塞26与向区域r2延伸的布线51(图1及图2)、及向区域r3延伸的布线51电连接。由此,区域k1内的布线51在区域r2、r3内变为低密度。同样,区域k2内的接点插塞26与向区域r2延伸的布线51、及向区域r3延伸的布线51电连接。由此,区域k2内的布线51在区域r2、r3内变为低密度。如此,根据本实施方式,能够减少半导体装置内的布线51的密度。

166.图17~图20是表示第1实施方式的半导体装置的制造方法的剖视图。具体来说,图17~图20示出图6所示的贴合前的阵列部分2(阵列晶圆)的制造方法。

167.首先,在衬底53上形成积层膜p(图17(a))。此时,积层膜p以交替包含多层绝缘膜22与多个牺牲层56的方式形成。这些牺牲层56在z方向上互相隔开。这些牺牲层56在后述的步骤中置换成多个电极层23。各牺牲层56例如为氮化硅膜。

168.图17(a)作为这些牺牲层56的例子,示出4个牺牲层56-1~56-4。积层膜p沿z方向依序包含牺牲层56-1~56-4。但,牺牲层56-1成为图17(a)中的最上级层,牺牲层56-4成为图17(a)中的最下级层。牺牲层56-1~56-4为第1到第n层(n为2以上的整数)的例子。n的值在图17(a)中为4,但也可为4以外的整数(例如8)。

169.图17(a)还示出衬底53上的区域r1、r2、r3。后述的步骤中,多个接点插塞26形成于区域r1内,多个柱状部24形成于区域r2、r3内。这些区域r1~r3之后转印于衬底11上。

170.图17(a)中,最上级的绝缘膜22的厚度设定为厚于其它绝缘膜22的厚度。各绝缘膜22例如为氧化硅膜。

171.接着,在积层膜p内形成多个柱状部24(图17(b))。如上所述,这些柱状部24形成于区域r2、r3内。各柱状部24通过在贯通积层膜p的开口部内依序嵌入块绝缘膜24a、电荷累积层24b、通道绝缘膜24c、通道半导体层24d及核心绝缘膜24e而形成(参照图5)。

172.接着,通过rie(reactive ion etching:反应性离子蚀刻),在积层膜p内形成多个开口部h1(图18(a))。这些开口部h1形成于区域r1内。图18(a)示出到达牺牲层56-1的开口部h1、到达牺牲层56-2的开口部h1、到达牺牲层56-3的开口部h1、及到达牺牲层56-4的开口部h1。如此,这些开口部h1以到达互不相同的牺牲层56的方式形成。

173.接着,在衬底53的整面形成绝缘膜25(图18(b))。结果,在各开口部h1的侧面及底面形成绝缘膜25。绝缘膜25例如为氧化硅膜。

174.接着,在衬底53的整面形成牺牲层57,在开口部h1内及开口部h1外形成牺牲层57后,将开口部h1外的牺牲层57利用蚀刻去除(图19(a))。结果,在各开口部h1内介隔绝缘膜25嵌入牺牲层57。牺牲层57例如为非晶硅层。

175.接着,在积层膜p内形成多个缝隙(未图示),使用这些缝隙,将所述多个牺牲层56置换成多个电极层23(图9(b))。如此,交替包含多个绝缘膜22与多个电极层23的积层膜p形成于衬底53上。牺牲层56-1~56-4分别置换成电极层23-1~23-4。

176.所述置换例如如下所述进行。首先,利用湿蚀刻将牺牲层56从缝隙去除。结果,在积层膜p内的绝缘膜23间形成多个空洞。接着,从缝隙将电极层23的材料嵌入这些空洞内。结果,在这些空洞内形成电极层23。另外,缝隙例如形成于图15所示的绝缘膜54的位置,在实施所述置换后以绝缘膜54嵌埋。

177.接着,将牺牲层57从各开口部h1去除(图20(a))。而且,利用rie将绝缘膜25从各开口部h1的底部去除(图20(a))。结果,在各开口部h1的底部露出电极层23的上表面。

178.接着,在衬底53的整面形成接点插塞26的材料,在开口部h1内及开口部h1外形成所述材料后,将开口部h1外的所述材料利用cmp去除(图20(b))。结果,在各开口部h1内介隔绝缘膜25嵌入接点插塞26。各接点插塞26例如为包含w(钨)层的金属层。

179.图20(b)作为接点插塞26的例子,示出4个接点插塞26-1~26-4。接点插塞26-1~26-4分别形成于电极层23-1~23-4的上表面,电连接于电极层23-1~23-4。

180.之后,进行图6所示的剩余步骤,或图7所示的步骤。如此,制造图1所示的半导体装置。

181.如上所述,本实施方式的半导体装置具备具有多个接点插塞26的区域r1、及具有多个柱状部24的区域r2、r3,区域r1设置于区域r2与区域r3之间。本实施方式中,还在至少区域r2、r3内设有接点插塞26用的晶体管13。由此,根据本实施方式,能够减少半导体装置内的布线51-1~51-8的密度。例如,通过将布线51-1~51-8中的一部分从区域r1向区域r2延伸,将布线51-1~51-8中的另一部分从区域r1向区域r3延伸,不论在区域r2内或区域r3内都能够减少布线51的密度。

182.(第2实施方式)

183.图21是表示第2实施方式的半导体装置的构造的剖视图。

184.本实施方式的半导体装置(图21)与第1实施方式的半导体装置(图1)同样,具备互相贴合的电路部分1及阵列部分2。图21的电路部分1具备衬底11、多个晶体管12、多个晶体管13、层间绝缘膜14、多个接点插塞31、布线层32、多个通孔插塞33、布线层34、多个通孔插塞35及多个金属焊垫36。图21的阵列部分2具备层间绝缘膜21、多个绝缘膜22、多个电极层23、多个柱状部24、多个绝缘膜25、多个接点插塞26、多个金属焊垫41、多个通孔插塞42、布线层43、多个通孔插塞44、布线层45及多个通孔插塞46。图21还示出电路部分1及阵列部分2的贴合面s、与阵列部分2内的积层膜p。

185.但,图21为容易观看附图,省略绝缘膜25、接点插塞31、布线层32、通孔插塞33、布线层34、通孔插塞35、金属焊垫36、金属焊垫41、通孔插塞42、布线层43、通孔插塞44、布线层45及通孔插塞46的图示。图21进一步示意性以实线示出接点插塞26。

186.本实施方式的半导体装置与图16所示的比较例的半导体装置同样,具备2个区域r1、1个区域r2及1个区域r3。图21中,区域r2、r3夹在所述区域r1间。

187.本实施方式的左侧的区域r1具有与图3所示的比较例的区域r1大致同样的构造。具体来说,本实施方式的积层膜p在左侧的区域r1内具有阶梯构造,在积层膜p的阶梯构造下设有层间绝缘膜52。结果,本实施方式的接点插塞26-k(k为满足2≦k≦8的整数)不贯通

电极层23-1~23-(k-1),而与电极层23-k相接。本实施方式的接点插塞26-k取代电极层23-1~23-(k-1),贯通层间绝缘膜52。

188.本实施方式的区域r2也具有与图3所示的比较例的区域r2大致同样的构造。此外,本实施方式的右侧的区域r1及区域r3分别具有与本实施方式的左侧的区域r1及区域r2同样的构造。具体来说,本实施方式的积层膜p在右侧的区域r1内具有阶梯构造,在所述阶梯构造下也设有层间绝缘膜52。

189.然而,本实施方式的柱状部24用的晶体管12设置于区域r1、r2、r3内。另一方面,本实施方式的接点插塞26用的晶体管13仅设置于区域r1、r2、r3中的区域r1内。本实施方式的积层膜p内的区域r1为第1区域的例子,本实施方式的积层膜p内的区域r2、r3为第2区域的例子。此外,区域r1内的晶体管12为第1区域的正下的第1晶体管的例子,区域r2、r3内的晶体管12为第2区域的正下的第2晶体管的例子。此外,本实施方式的 x方向侧或-x方向侧为第2方向侧的例子。

190.图21示出包含晶体管12的2个区域t1、包含晶体管13的1个区域t2、及包含晶体管13的1个区域t3。区域t1大致设置于与区域r1相同的位置,但设定得比区域r1小。区域t2、t3大致设置于与区域r2、r3相同的位置,但设定得比区域r2、r3大。

191.图21以实线例示将接点插塞26与晶体管13电连接的布线51、及将柱状部24与晶体管12电连接的布线61。本实施方式的接点插塞26-1~26-8分别与第1实施方式的情况同样,经由布线51-1~51-8与晶体管13电连接。图21以实线表示布线51-1~51-8中的布线51-1、51-8,布线51-2~51-7的图示由虚线省略。布线51、61由接点插塞31、布线层32、通孔插塞33、布线层34、通孔插塞35、金属焊垫36、金属焊垫41、通孔插塞42、布线层43、通孔插塞44、布线层45及通孔插塞46形成。

192.根据本实施方式,不仅将晶体管12配置于区域r2、r3内,也配置于区域r1内,借此例如能够缩小俯视时区域r1的面积。由此,能够将晶体管12或布线61配置于足够大的区域内,或缩小俯视时衬底11的面积。结果,能够提高本实施方式的半导体装置的集成度。

193.另外,第1或第2实施方式的半导体装置也可为3维半导体存储器以外的装置。此外,第1或第2实施方式的半导体装置可将电路晶圆及阵列晶圆以外的晶圆彼此贴合而制造,也可不将晶圆彼此贴合而制造。

194.以上,说明了若干实施方式,但这些实施方式仅作为例子而提出,并非意在限定发明的范围。本说明书中说明的新颖的装置及方法能够以其它各种方式实施。此外,对于本说明书中说明的装置及方法的方式,能够在不脱离发明主旨的范围内进行各种省略、置换、变更。附加的权利要求书及与其均等的范围意在包含发明范围或主旨所含的这种方式或变化例。

195.[符号说明]

[0196]1ꢀꢀꢀꢀꢀ

电路部分

[0197]2ꢀꢀꢀꢀꢀ

阵列部分

[0198]

11

ꢀꢀꢀꢀ

衬底

[0199]

12

ꢀꢀꢀꢀ

晶体管

[0200]

12a

ꢀꢀꢀ

栅极绝缘膜

[0201]

12b

ꢀꢀꢀ

栅极电极

[0202]

12c

ꢀꢀꢀ

扩散层

[0203]

12d

ꢀꢀꢀ

扩散层

[0204]

13

ꢀꢀꢀꢀ

晶体管

[0205]

13a

ꢀꢀꢀ

栅极绝缘膜

[0206]

13b

ꢀꢀꢀ

栅极电极

[0207]

13c

ꢀꢀꢀ

扩散层

[0208]

13d

ꢀꢀꢀ

扩散层

[0209]

14

ꢀꢀꢀꢀ

层间绝缘膜

[0210]

21

ꢀꢀꢀꢀ

层间绝缘膜

[0211]

22

ꢀꢀꢀꢀ

绝缘膜

[0212]

23

ꢀꢀꢀꢀ

电极层

[0213]

24

ꢀꢀꢀꢀ

柱状部

[0214]

24a

ꢀꢀꢀ

块绝缘膜

[0215]

24b

ꢀꢀꢀ

电荷累积层

[0216]

24c

ꢀꢀꢀ

通道绝缘膜

[0217]

24d

ꢀꢀꢀ

通道半导体层

[0218]

24e

ꢀꢀꢀ

核心绝缘膜

[0219]

25

ꢀꢀꢀꢀ

绝缘膜

[0220]

26

ꢀꢀꢀꢀ

接点插塞

[0221]

31

ꢀꢀꢀꢀ

接点插塞

[0222]

32

ꢀꢀꢀꢀ

布线层

[0223]

33

ꢀꢀꢀꢀ

通孔插塞

[0224]

34

ꢀꢀꢀꢀ

布线层

[0225]

35

ꢀꢀꢀꢀ

通孔插塞

[0226]

36

ꢀꢀꢀꢀ

金属焊垫

[0227]

41

ꢀꢀꢀꢀ

金属焊垫

[0228]

42

ꢀꢀꢀꢀ

通孔插塞

[0229]

43

ꢀꢀꢀꢀ

布线层

[0230]

44

ꢀꢀꢀꢀ

接点插塞

[0231]

45

ꢀꢀꢀꢀ

布线层

[0232]

46

ꢀꢀꢀꢀ

通孔插塞

[0233]

51

ꢀꢀꢀꢀ

布线

[0234]

52

ꢀꢀꢀꢀ

层间绝缘膜

[0235]

53

ꢀꢀꢀꢀ

衬底

[0236]

54

ꢀꢀꢀꢀ

绝缘膜

[0237]

55

ꢀꢀꢀꢀ

接点插塞

[0238]

56

ꢀꢀꢀꢀ

牺牲层

[0239]

57

ꢀꢀꢀꢀ

牺牲层

[0240]

61

ꢀꢀꢀꢀ

布线。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。