半导体装置的制造方法

1.关联申请

2.本技术享有以日本专利申请2021-131790号(申请日:2021年8月12日)为基础申请的优先权。本技术通过参照该基础申请从而包含基础申请的全部内容。

技术领域

3.本发明的实施方式涉及半导体装置的制造方法。

背景技术:

4.在半导体装置的制造中,期望实现将半导体层在低温下氧化从而形成厚的氧化膜的方法。

技术实现要素:

5.本发明的实施方式提供将半导体层在低温下氧化从而形成厚的氧化膜的半导体装置的制造方法。

6.实施方式的半导体装置的制造方法,在包含硅(si)的半导体层之上形成包含金属元素和氧(o)且具有第1厚度的第1膜,利用自由基氧化在所述半导体层与所述第1膜之间形成包含硅(si)和氧(o)且具有比所述第1厚度厚的第2厚度的第2膜。

附图说明

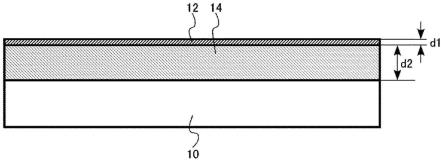

7.图1(a)~(c)是第1实施方式的半导体装置的制造方法的说明图。

8.图2是第1实施方式的半导体装置的制造方法的作用和效果的说明图。

9.图3(a)~(c)是第2实施方式的半导体装置的制造方法的说明图。

10.图4是第2实施方式的半导体装置的制造方法的作用和效果的说明图。

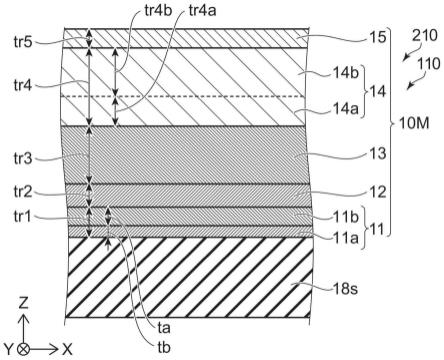

11.图5是利用第3实施方式的半导体装置的制造方法制造的半导体装置的示意截面图。

12.图6(a)~(d)是第3实施方式的半导体装置的制造方法的说明图。

13.图7(a)~(d)是第3实施方式的半导体装置的制造方法的变形例的说明图。

14.图8是利用第4实施方式的半导体装置的制造方法制造的半导体装置的示意截面图。

15.图9(a)~(d)是第4实施方式的半导体装置的制造方法的说明图。

16.图10是利用第5实施方式的半导体装置的制造方法制造的半导体装置的示意截面图。

17.图11(a)~(d)是第5实施方式的半导体装置的制造方法的说明图。

18.图12是利用第6实施方式的半导体装置的制造方法制造的半导体装置的示意截面图。

19.图13(a)~(d)是第6实施方式的半导体装置的制造方法的说明图。

20.附图标记说明

21.10

ꢀꢀꢀ

半导体层

22.10a

ꢀꢀ

第一p型半导体区域(第1区域)

23.10b

ꢀꢀ

第二p型半导体区域(第2区域)

24.12

ꢀꢀꢀ

氧化铝膜(第1膜)

25.14

ꢀꢀꢀ

氧化硅膜(第2膜)

26.16

ꢀꢀꢀ

氮氧化硅膜(第3膜)

27.18

ꢀꢀꢀ

氧化铪膜(第4膜)

28.102

ꢀꢀ

第1栅电极

29.202

ꢀꢀ

第2栅电极

30.d1

ꢀꢀꢀ

第1厚度

31.d2

ꢀꢀꢀ

第2厚度

32.d3

ꢀꢀꢀ

第3厚度

33.d4

ꢀꢀꢀ

第4厚度

具体实施方式

34.以下,参照附图对本发明的实施方式进行说明。再者,在以下的说明中,对相同或类似的构件等标记相同的符号,对于已说明过一次的构件等有时适当省略其说明。

35.另外,在本说明书中,为了方便起见,有时使用“上”或“下”这样的术语。所谓“上”或“下”例如是表示在图中的相对位置关系的术语。“上”或“下”这样的术语不一定是规定相对于重力的位置关系的术语。

36.本说明书中的构成半导体装置的构件的化学组成的定性分析和定量分析,例如能够采用二次离子质谱法(secondary ion mass spectrometry:sims)、能量分散型x射线光谱法(energy dispersive x-ray spectroscopy:edx)来进行。另外,在构成半导体装置的构件的厚度、构件间的距离等的测定中能够使用例如透射型电子显微镜(transmission electron microscope:tem)。

37.(第1实施方式)

38.第1实施方式的半导体装置的制造方法,在包含硅(si)的半导体层之上形成包含金属元素和氧(o)且具有第1厚度的第1膜,利用自由基氧化在半导体层与第1膜之间形成包含硅(si)和氧(o)且具有比第1厚度厚的第2厚度的第2膜。

39.图1(a)~(c)是第1实施方式的半导体装置的制造方法的说明图。

40.首先,准备半导体层10(图1(a))。半导体层10包含硅(si)。半导体层10例如以硅(si)为主成分。半导体层10例如为单晶硅层或多晶硅层。

41.半导体层10不限定于单晶硅层或多晶硅层。半导体层10例如可以为锗化硅层或碳化硅层。以下,以半导体层10为单晶硅层的情况为例进行说明。

42.接着,在半导体层10之上形成氧化铝膜12(图1(b))。氧化铝膜12是第1膜的一例。铝(al)是金属元素的一例。

43.氧化铝膜12例如采用化学气相生长法(cvd法)形成。氧化铝膜12例如采用原子层堆积法(ald法)形成。

44.第1膜包含金属元素和氧(o)。第1膜中所含的金属元素例如为选自铝(al)、铪(hf)、锆(zr)、镧(la)、钇(y)、钛(ti)、镍(ni)、锌(zn)、铟(in)、锡(sn)、镓(ga)和钨(w)中的至少一种金属元素。第1膜例如以上述金属元素和氧(o)为主成分。第1膜例如为金属氧化物膜。第1膜例如为上述金属元素的氧化物膜。

45.第1膜例如为氧化铝膜、氧化铪膜、氧化锆膜、氧化镧膜、氧化钇膜、氧化钛膜、氧化镍膜、氧化锌膜、氧化铟膜、氧化锡膜、氧化镓膜或氧化钨膜。

46.第1膜例如为绝缘膜或半导体膜。第1膜例如为非晶质膜。第1膜例如包含选自氮(n)、碳(c)、氢(h)、氟(f)和氯(cl)中的至少一种元素。

47.第1膜具有第1厚度(图1(b)、图1(c)中的d1)。第1厚度d1例如为1nm以上且5nm以下。氧化铝膜12的第1厚度d1例如为1nm以上且5nm以下。

48.第1膜并不一定限定于氧化铝膜。以下,以第1膜为氧化铝膜的情况为例进行说明。

49.接着,利用自由基氧化在半导体层10与氧化铝膜12之间形成具有比第1厚度d1厚的第2厚度(图1(c)中的d2)的氧化硅膜14(图1(c))。通过利用自由基氧化将半导体层10氧化从而形成氧化硅膜14。氧化硅膜14为第2膜的一例。

50.自由基氧化在包含氧自由基(oxygen radical)或羟基自由基(hydoroxyl radical)的气氛中进行。自由基氧化例如在将氧气、氢气以及氩气等离子体化了的气氛中进行。自由基氧化例如在将水蒸气等离子体化了的气氛中进行。

51.生成在自由基氧化中所使用的氧自由基、羟基自由基的方法并不特别限定。氧自由基、羟基自由基例如采用电感耦合等离子体方式、微波等离子体方式、电子回旋共振方式、螺旋波方式或热丝(hot filament)方式来生成。

52.在自由基氧化的气氛中例如包含氢(h)和氧(o)。自由基氧化的气氛中所包含的氢(h)相对于氢(h)与氧(o)之和的原子比率(h/(h o))例如为40%以下。自由基氧化的气氛中所包含的氢(h)相对于氢(h)与氧(o)之和的原子比率(h/(h o))例如为2%以上且5%以下。

53.自由基氧化的气氛中所包含的氢(h)相对于氢(h)与氧(o)之和的原子比率(h/(h o)),例如利用向自由基氧化的气氛中导入的氢气(h2)和氧气(o2)的流量来调整。向自由基氧化的气氛中导入的氢气(h2)相对于氢气(h2)与氧气(o2)之和的摩尔比率(h2/(h2 o2))例如为40%以下。向自由基氧化的气氛中导入的氢气(h2)相对于氢气(h2)与氧气(o2)之和的摩尔比率(h2/(h2 o2))例如为2%以上且5%以下。

54.自由基氧化的温度例如为300℃以上且900℃以下。自由基氧化的压力例如为50pa以上且3000pa以下。

55.第2膜包含硅(si)和氧(o)。第2膜例如以硅(si)和氧(o)为主成分。

56.第2膜具有第2厚度(图1(c)中的d2)。第2厚度d2比第1膜的第1厚度d1厚。第2厚度d2例如为第1膜的第1厚度d1的10倍以上。第2厚度d2例如为10nm以上且300nm以下。

57.氧化硅膜14的第2厚度d2比氧化铝膜12的第1厚度d1厚。氧化硅膜14的第2厚度d2例如为氧化铝膜12的第1厚度d1的10倍以上。氧化硅膜14的第2厚度d2例如为10nm以上且300nm以下。

58.接着,对第1实施方式的半导体装置的制造方法的作用和效果进行说明。

59.在半导体装置的制造中,期望实现将半导体层在低温下氧化从而形成厚的氧化膜的方法。例如,通过将半导体层在低温下氧化,能够抑制形成于半导体层的器件的特性劣

化。

60.例如,在具备晶体管的半导体装置的制造中,若在形成晶体管之后施加高温的热处理,则有因热处理而使杂质扩散、因热处理而使构成晶体管的材料变质等从而晶体管的特性劣化之恐。如果能够在低温下进行形成晶体管之后的氧化膜的形成,则能够抑制晶体管的特性的劣化。

61.第1实施方式的半导体装置的制造方法,在半导体层的氧化中利用自由基氧化。通过利用自由基氧化,例如与热氧化相比,能够在低温下将半导体层氧化。

62.图2是第1实施方式的半导体装置的制造方法的作用和效果的说明图。图2是表示通过自由基氧化来将半导体层氧化而形成的氧化膜的膜厚度的图。

63.图2是比较在半导体层之上形成第2膜的情况和未形成第2膜的情况的氧化膜厚度的图。图2示出半导体层为单晶硅层、第2膜为氧化铝膜的情况。图2示出氧化铝膜的膜厚度为3nm、自由基氧化的温度为700℃的情况。

64.由图2明确可知:在半导体层10之上形成氧化铝膜12而进行自由基氧化的情况下,与未形成氧化铝膜12的情况相比,氧化膜厚度成为7倍以上。换言之,可知:通过在半导体层10之上形成氧化铝膜12而进行自由基氧化,发生了大的增速氧化。

65.发生图2所示那样的大的增速氧化的机理未必明确。但是认为:通过在包含硅的半导体层10之上存在共存金属元素和氧(o)的膜,形成氧化膜的活化能降低,发生增速氧化。另外认为:金属氧化物中的氧欠缺部被氧自由基、羟基自由基填充,金属氧化物中的氧因在其后侵入到金属氧化物中来的氧自由基、羟基自由基而吐出,发生增速氧化。

66.在第1实施方式的半导体装置的制造方法中,第1膜优选为非晶质。通过第1膜为非晶质,增速氧化的程度变大。

67.在第1实施方式的半导体装置的制造方法中,第1膜的第1厚度d1优选为0.5nm以上,更优选为1nm以上。通过第1厚度d1为0.5nm以上,增速氧化的程度变大,通过第1厚度d1为1nm以上,增速氧化的程度进一步变大。

68.另外,在第1实施方式的半导体装置的制造方法中,第1膜的第1厚度d1优选为5nm以下,更优选为3nm以下。通过第1厚度d1为5nm以下,增速氧化的程度变大。另外,通过第1厚度d1为3nm以下,增速氧化的程度进一步变大。

69.在第1实施方式的半导体装置的制造方法中,自由基氧化的温度优选为300℃以上,更优选为400℃以上,进一步优选为500℃以上。通过自由基氧化的温度变高,增速氧化的程度变大。

70.在第1实施方式的半导体装置的制造方法中,自由基氧化的温度优选为900℃以下,更优选为800℃以下,进一步优选为700℃以下。通过自由基氧化的温度变低,例如能够抑制在半导体层之上形成的器件的特性劣化。

71.在第1实施方式的半导体装置的制造方法中,第1膜优选包含选自氮(n)、碳(c)、氢(h)和氯(cl)中的至少一种元素。通过第1膜包含上述元素,第1膜的结晶化被抑制,增速氧化的程度变大。

72.在第1实施方式的半导体装置的制造方法中,在自由基氧化的气氛中包含氢(h)和氧(o),所包含的氢(h)相对于氢(h)与氧(o)之和的原子比率(h/(h o))优选为40%以下,更优选为2%以上且5%以下。通过原子比率(h/(h o))满足上述范围,增速氧化的程度变大。

73.以上,根据第1实施方式的半导体装置的制造方法,能够将半导体层在低温下氧化从而形成厚的氧化膜。

74.(第2实施方式)

75.第2实施方式的半导体装置的制造方法,在半导体层之上形成第1膜之前,在半导体层之上形成包含硅(si)、氧(o)和氮(n)的第3膜,在这一点上与第1实施方式的半导体装置的制造方法不同。以下,对于与第1实施方式重复的内容,有时省略一部分记述。

76.图3(a)~(c)是第2实施方式的半导体装置的制造方法的说明图。

77.首先,准备半导体层10(图3(a))。半导体层10包含硅(si)。半导体层10例如以硅(si)为主成分。半导体层10例如为单晶硅层或多晶硅层。

78.接着,在半导体层10之上形成氮氧化硅膜16。氮氧化硅膜16为第3膜的一例。

79.氮氧化硅膜16例如采用cvd法形成。氮氧化硅膜16例如采用ald法形成。

80.第3膜包含硅(si)、氧(o)和氮(n)。第3膜例如以硅(si)、氧(o)和氮(n)为主成分。

81.第3膜的厚度例如为1nm以上且10nm以下。氮氧化硅膜16的厚度例如为1nm以上且10nm以下。

82.接着,在半导体层10之上形成氧化铝膜12(图3(b))。氧化铝膜12为第1膜的一例。

83.第1膜包含金属元素和氧(o)。第1膜中所包含的金属元素例如为选自铝(al)、铪(hf)、锆(zr)、镧(la)、钇(y)、钛(ti)、镍(ni)、锌(zn)、铟(in)、锡(sn)、镓(ga)和钨(w)中的至少一种金属元素。第1膜例如以上述金属元素和氧(o)为主成分。第1膜例如为金属氧化物膜。

84.第1膜具有第1厚度(图3(b)、图3(c)中的d1)。第1厚度d1例如为1nm以上且5nm以下。氧化铝膜12的第1厚度d1例如为1nm以上且5nm以下。

85.接着,通过自由基氧化在半导体层10与氧化铝膜12之间形成具有比第1厚度d1厚的第2厚度(图3(c)中的d2)的氧化硅膜14(图3(c))。氧化硅膜14形成于半导体层10与氮氧化硅膜16之间。

86.通过利用自由基氧化将半导体层10氧化从而形成氧化硅膜14。氧化硅膜14为第2膜的一例。

87.第2膜包含硅(si)和氧(o)。第2膜例如以硅(si)和氧(o)为主成分。

88.第2膜具有第2厚度(图3(c)中的d2)。第2厚度d2比第1膜的第1厚度d1厚。第2厚度d2例如为第1膜的第1厚度d1的10倍以上。第2厚度d2例如为10nm以上且600nm以下。第2厚度d2比第3膜的厚度厚。

89.氧化硅膜14的第2厚度d2比氧化铝膜12的第1厚度d1厚。氧化硅膜14的第2厚度d2例如为氧化铝膜12的第1厚度d1的10倍以上。氧化硅膜14的第2厚度d2例如为10nm以上且600nm以下。第2厚度d2比氮氧化硅膜16的厚度厚。

90.接着,对第2实施方式的半导体装置的制造方法的作用和效果进行说明。

91.图4是第2实施方式的半导体装置的制造方法的作用和效果的说明图。图4是示出通过自由基氧化将半导体层氧化而形成的氧化膜的膜厚度的图。

92.图4是比较在半导体层之上形成第3膜和第2膜的情况、仅形成第2膜的情况和未形成第3膜和第2膜的情况的氧化膜厚度的图。图4示出半导体层为单晶硅层、第3膜为氮氧化硅膜、第2膜为氧化铝膜的情况。图4示出氮氧化硅膜的膜厚度为8nm、氧化铝膜的膜厚度为

3nm、自由基氧化的温度为700℃的情况。

93.由图4明确可知:在半导体层10之上形成氮氧化硅膜16和氧化铝膜12而进行自由基氧化的情况下,与未形成氮氧化硅膜16和氧化铝膜12的情况相比,氧化膜厚度成为26倍以上。另外可知:在半导体层10之上形成氮氧化硅膜16和氧化铝膜12而进行自由基氧化的情况下,与仅形成氧化铝膜12而进行自由基氧化的情况相比,氧化膜厚度成为3倍以上。可知:通过在半导体层10之上形成氮氧化硅膜16和氧化铝膜12而进行自由基氧化,发生了显著大的增速氧化。

94.以上,根据第2实施方式的半导体装置的制造方法,能够将半导体层在低温下氧化从而形成厚的氧化膜。

95.(第3实施方式)

96.第3实施方式的半导体装置的制造方法,在包含硅(si)且包含第1区域和第2区域的半导体层的至少第1区域之上形成包含第1金属元素和氧(o)且具有第1厚度的第1膜,利用自由基氧化在第1区域与第1膜之间以及第2区域之上形成包含硅(si)和氧(o)且在第1区域之上的第2厚度比第1厚度厚、在第2区域之上的第3厚度比第2厚度薄的第2膜。第1膜选择性地形成于第1区域之上。以下,对于与第1实施方式重复的内容有时省略一部分记述。

97.图5是利用第3实施方式的半导体装置的制造方法制造的半导体装置的示意截面图。半导体装置具备第1晶体管100和第2晶体管200。第1晶体管100和第2晶体管200为金属氧化物场效应晶体管(metal oxide field effect transistor(mosfet))。

98.第1晶体管100包含半导体层10、第1栅绝缘层101和第1栅电极102。半导体层10包含第一p型半导体区域10a、和n型半导体区域10x。第1栅绝缘层101包含第1下部膜101a和第1上部膜101b。

99.半导体层10例如为单晶硅层。第一p型半导体区域10a的与第1栅电极102对向的部分作为第1晶体管100的沟道区域发挥功能。n型半导体区域10x作为第1晶体管100的源极

·

漏极区域发挥功能。

100.第1栅绝缘层101的第1下部膜101a包含硅(si)和氧(o)。第1下部膜101a例如为氧化硅膜。第1栅绝缘层101的第1上部膜101b包含第1金属元素和氧(o)。第1上部膜101b例如为氧化铝膜。铝(al)为第1金属元素的一例。

101.第1栅电极102为导电体。第1栅电极102例如为包含p型杂质或n型杂质的多晶硅。

102.第2晶体管200包含半导体层10、第2栅绝缘层201和第2栅电极202。半导体层10包含第二p型半导体区域10b和n型半导体区域10x。

103.第二p型半导体区域10b的与第2栅电极202对向的部分作为第2晶体管200的沟道区域发挥功能。n型半导体区域10x作为第2晶体管200的源极

·

漏极区域发挥功能。

104.第2栅绝缘层201包含硅(si)和氧(o)。第2栅绝缘层201例如为氧化硅膜。

105.第2栅电极202为导电体。第2栅电极202例如为包含p型杂质或n型杂质的多晶硅。

106.第1晶体管100的第1栅绝缘层101的厚度比第2晶体管200的第2栅绝缘层201的厚度厚。

107.通过第1晶体管100的第1栅绝缘层101比第2晶体管200的第2栅绝缘层201厚,例如能够使第1晶体管100在比第2晶体管200高的驱动电压下工作。

108.图6(a)~(d)是第3实施方式的半导体装置的制造方法的说明图。

109.首先,准备半导体层10(图6(a))。半导体层10包含硅(si)。半导体层10例如以硅(si)为主成分。半导体层10例如为单晶硅层或多晶硅层。

110.半导体层10不被限定于单晶硅层或多晶硅层。半导体层10例如也可以为锗化硅层或碳化硅层。以下,以半导体层10为单晶硅层的情况为例进行说明。

111.半导体层10包含第一p型半导体区域10a和第二p型半导体区域10b。

112.接着,在半导体层10之上形成氧化铝膜12(图6(b))。氧化铝膜12为第1膜的一例。氧化铝膜12的一部分最终成为第1上部膜101b。铝(al)为第1金属元素的一例。

113.氧化铝膜12例如采用cvd法形成。氧化铝膜12例如采用ald法形成。

114.第1膜包含第1金属元素和氧(o)。第1膜中所包含的第1金属元素例如为选自铝(al)、铪(hf)、锆(zr)、镧(la)、钇(y)、钛(ti)、镍(ni)、锌(zn)、铟(in)、锡(sn)、镓(ga)和钨(w)中的至少一种金属元素。第1膜例如以上述第1金属元素和氧(o)为主成分。第1膜例如为金属氧化物膜。第1膜例如为上述第1金属元素的氧化物膜。

115.第1膜例如为绝缘膜或半导体膜。第1膜例如为非晶质膜。第1膜例如包含选自氮(n)、碳(c)、氢(h)和氯(cl)中的至少一种元素。

116.第1膜具有第1厚度(图6(b)的d1)。第1厚度d1例如为1nm以上且5nm以下。氧化铝膜12的第1厚度d1例如为1nm以上且5nm以下。

117.第1膜并不一定限定于氧化铝膜。以下,以第1膜为氧化铝膜的情况为例进行说明。

118.接着,将第二p型半导体区域10b之上的氧化铝膜12除去(图6(c))。第二p型半导体区域10b之上的氧化铝膜12例如使用湿蚀刻法除去。通过将第二p型半导体区域10b之上的氧化铝膜12除去,氧化铝膜12选择性地形成于第一p型半导体区域10a之上。

119.接着,利用自由基氧化在半导体层10之上形成氧化硅膜14(图6(d))。氧化硅膜14形成于第一p型半导体区域10a之上。氧化硅膜14形成于第一p型半导体区域10a与氧化铝膜12之间。氧化硅膜14形成于第二p型半导体区域10b之上。

120.第一p型半导体区域10a之上的氧化硅膜14最终成为第1下部膜101a。另外,第二p型半导体区域10b之上的氧化硅膜14最终成为第2栅绝缘层201。

121.第一p型半导体区域10a与氧化铝膜12之间的氧化硅膜14的第2厚度(图6(d)中的d2)比氧化铝膜12的第1厚度d1厚。第二p型半导体区域10b之上的氧化硅膜14的第3厚度(图6(d)中的d3)比氧化硅膜14的第2厚度d2薄。

122.通过利用自由基氧化将半导体层10氧化从而形成氧化硅膜14。氧化硅膜14为第2膜的一例。

123.第一p型半导体区域10a之上的氧化硅膜14因增速氧化而变得比第二p型半导体区域10b之上的氧化硅膜14厚。

124.自由基氧化在包含氧自由基(oxygen radical)或羟基自由基(hydoroxyl radical)的气氛中进行。自由基氧化例如在将氧气、氢气以及氩气等离子体化了的气氛中进行。自由基氧化例如在将水蒸气等离子体化了的气氛中进行。

125.生成在自由基氧化中所使用的氧自由基、羟基自由基的方法并不特别限定。氧自由基、羟基自由基例如采用电感耦合等离子体方式、微波等离子体方式、电子回旋共振方式、螺旋波方式或热丝方式来生成。

126.在自由基氧化的气氛中例如包含氢(h)和氧(o)。自由基氧化的气氛中所包含的氢

(h)相对于氢(h)与氧(o)之和的原子比率(h/(h o))例如为40%以下。自由基氧化的气氛中所包含的氢(h)相对于氢(h)与氧(o)之和的原子比率(h/(h o))例如为2%以上且5%以下。

127.自由基氧化的气氛中所包含的氢(h)相对于氢(h)与氧(o)之和的原子比率(h/(h o))例如利用向自由基氧化的气氛中导入的氢气(h2)和氧气(o2)的流量来调整。向自由基氧化的气氛中导入的氢气(h2)相对于氢气(h2)与氧气(o2)之和的摩尔比率(h2/(h2 o2))例如为40%以下。向自由基氧化的气氛中导入的氢气(h2)相对于氢气(h2)与氧气(o2)之和的摩尔比率(h2/(h2 o2))例如为2%以上且5%以下。

128.自由基氧化的温度例如为300℃以上且900℃以下。自由基氧化的压力例如为50pa以上且3000pa以下。

129.第2膜包含硅(si)和氧(o)。第2膜例如以硅(si)和氧(o)为主成分。

130.第一p型半导体区域10a之上的第2膜具有第2厚度(图6(d)中的d2)。第二p型半导体区域10b之上的第2膜具有第3厚度(图6(d)中的d3)。

131.第2厚度d2比第1膜的第1厚度d1厚。第2厚度d2例如为第1膜的第1厚度d1的10倍以上。第2厚度d2例如为10nm以上且300nm以下。

132.氧化硅膜14的第2厚度d2比氧化铝膜12的第1厚度d1厚。氧化硅膜14的第2厚度d2例如为氧化铝膜12的第1厚度d1的10倍以上。氧化硅膜14的第2厚度d2例如为10nm以上且300nm以下。

133.第2厚度d2比第3厚度d3厚。第2厚度d2例如为第3厚度d3的7倍以上。

134.氧化硅膜14的第2厚度d2比氧化硅膜14的第3厚度d3厚。氧化硅膜14的第2厚度d2例如为氧化硅膜14的第3厚度d3的7倍以上。

135.其后,通过采用公知的工艺技术形成第1栅电极102、第2栅电极202以及n型半导体区域10x,能够制造出图5所示的半导体装置。第1栅电极102形成于第一p型半导体区域10a之上的氧化硅膜14的上方。第2栅电极202形成于第二p型半导体区域10b之上的氧化硅膜14的上方。

136.(变形例)

137.第3实施方式的半导体装置的制造方法的变形例,在形成第1膜之前,在第1区域之上形成包含硅(si)、氧(o)和氮(n)的第3膜,在这一点上与第3实施方式的半导体装置的制造方法不同。

138.图7(a)~(d)是第3实施方式的半导体装置的制造方法的变形例的说明图。

139.首先,准备半导体层10(图7(a))。半导体层10包含第一p型半导体区域10a和第二p型半导体区域10b。

140.接着,在半导体层10之上形成氮氧化硅膜16。氮氧化硅膜16为第3膜的一例。接着,在半导体层10之上形成氧化铝膜12(图7(b))。氧化铝膜12为第1膜的一例。

141.接着,将第二p型半导体区域10b之上的氮氧化硅膜16以及氧化铝膜12除去(图7(c))。第二p型半导体区域10b之上的氮氧化硅膜16以及氧化铝膜12例如使用湿蚀刻法除去。通过将第二p型半导体区域10b之上的氮氧化硅膜16以及氧化铝膜12除去,氮氧化硅膜16以及氧化铝膜12选择性地形成于第一p型半导体区域10a之上。

142.接着,利用自由基氧化在半导体层10之上形成氧化硅膜14(图7(d))。氧化硅膜14形成于第一p型半导体区域10a之上。氧化硅膜14形成于第二p型半导体区域10b之上。

143.通过利用自由基氧化将半导体层10氧化从而形成氧化硅膜14。氧化硅膜14为第2膜的一例。

144.第一p型半导体区域10a之上的氧化硅膜14因增速氧化而变得比第二p型半导体区域10b之上的氧化硅膜14厚。特别是通过在第一p型半导体区域10a之上设置氮氧化硅膜16,与第3实施方式的半导体装置的制造方法比较,增速氧化被促进。因此,与第3实施方式的半导体装置的制造方法比较,使第一p型半导体区域10a之上的氧化硅膜14的第2厚度(图7(b)中的d2)比第二p型半导体区域10b之上的氧化硅膜14的第3厚度(图7(b)中的d3)厚变得容易。

145.其后,通过采用公知的工艺技术形成第1栅电极102、第2栅电极202和n型半导体区域10x,能够制造出与图5所示的半导体装置同样的半导体装置。

146.以上,根据第3实施方式的半导体装置的制造方法及其变形例,能够将半导体层在低温下氧化从而在半导体层之上形成厚度不同的氧化膜。

147.(第4实施方式)

148.第4实施方式的半导体装置的制造方法,在形成第1膜之前,在第1区域之上形成包含硅(si)、氧(o)和氮(n)的第3膜。以下,对于与第3实施方式重复的内容,有时省略一部分记述。

149.图8是利用第4实施方式的半导体装置的制造方法制造的半导体装置的示意截面图。半导体装置具备第1晶体管100和第2晶体管200。第1晶体管100和第2晶体管200为mosfet。

150.第1晶体管100包含半导体层10、第1栅绝缘层101和第1栅电极102。半导体层10包含第一p型半导体区域10a、和n型半导体区域10x。第1栅绝缘层101包含第1下部膜101a、中间膜101c和第1上部膜101b。

151.第4实施方式的第1晶体管100,其第1栅绝缘层101包含中间膜101c,在这一点上与第3实施方式的第1晶体管100不同。

152.第1栅绝缘层101的第1下部膜101a包含硅(si)和氧(o)。第1下部膜101a例如为氧化硅膜。第1栅绝缘层101的中间膜101c包含硅(si)、氧(o)和氮(n)。中间膜101c例如为氮氧化硅膜。第1栅绝缘层101的第1上部膜101b包含第1金属元素和氧(o)。第1上部膜101b例如为氧化铝膜。

153.第2晶体管200包含半导体层10、第2栅绝缘层201和第2栅电极202。半导体层10包含第二p型半导体区域10b、和n型半导体区域10x。第2栅绝缘层201包含第2下部膜201a和第2上部膜201b。

154.第2栅绝缘层201包含硅(si)和氧(o)。第2栅绝缘层201的第2下部膜201a例如为氧化硅膜。第2栅绝缘层201的第2上部膜201b包含第1金属元素和氧(o)。第2上部膜201b例如为氧化铝膜。

155.第1晶体管100的第1栅绝缘层101的厚度比第2晶体管200的第2栅绝缘层201的厚度厚。

156.图9(a)~(d)为第4实施方式的半导体装置的制造方法的说明图。

157.首先,准备半导体层10(图9(a))。半导体层10包含第一p型半导体区域10a和第二p型半导体区域10b。

158.接着,在半导体层10之上形成氮氧化硅膜16。氮氧化硅膜16为第3膜的一例。接着,将第二p型半导体区域10b之上的氮氧化硅膜16除去(图9(b))。氮氧化硅膜16选择性地形成于第一p型半导体区域10a之上。氮氧化硅膜16最终成为中间膜101c。

159.接着,在半导体层10之上形成氧化铝膜12(图9(c))。氧化铝膜12为第1膜的一例。氧化铝膜12的一部分最终成为第1上部膜101b。氧化铝膜12的另外的一部分最终成为第2上部膜201b。

160.接着,利用自由基氧化在半导体层10之上形成氧化硅膜14(图9(d))。氧化硅膜14形成于第一p型半导体区域10a之上。氧化硅膜14形成于第二p型半导体区域10b之上。

161.第一p型半导体区域10a之上的氧化硅膜14最终成为第1下部膜101a。另外,第二p型半导体区域10b之上的氧化硅膜14最终成为第2下部膜201a。

162.第一p型半导体区域10a与氧化铝膜12之间的氧化硅膜14的第2厚度(图9(d)中的d2)比氧化铝膜12的第1厚度(图9(c)、图9(d)中的d1)厚。第二p型半导体区域10b之上的氧化硅膜14的第3厚度(图9(d)中的d3)比氧化硅膜14的第2厚度d2薄。

163.通过利用自由基氧化将半导体层10氧化从而形成氧化硅膜14。氧化硅膜14为第2膜的一例。

164.第一p型半导体区域10a之上的氧化硅膜14因增速氧化而变得比第二p型半导体区域10b之上的氧化硅膜14厚。

165.其后,通过采用公知的工艺技术形成第1栅电极102、第2栅电极202以及n型半导体区域10x,能够制造出图8所示的半导体装置。

166.以上,根据第4实施方式的半导体装置的制造方法,能够将半导体层在低温下氧化从而在半导体层之上形成厚度不同的氧化膜。

167.(第5实施方式)

168.第5实施方式的半导体装置的制造方法,在形成第1膜之前、或者在形成第1膜之后且形成第2膜之前,在第2区域之上形成包含与第1金属元素不同的第2金属元素和氧(o)且具有第4厚度的第4膜,第3厚度比第4厚度厚,在上述点上与第3实施方式的半导体装置的制造方法不同。以下,对于与第3实施方式重复的内容,有时省略一部分记述。

169.图10是利用第5实施方式的半导体装置的制造方法制造的半导体装置的示意截面图。半导体装置具备第1晶体管100和第2晶体管200。第1晶体管100和第2晶体管200为mosfet。

170.第1晶体管100包含半导体层10、第1栅绝缘层101和第1栅电极102。半导体层10包含第一p型半导体区域10a、和n型半导体区域10x。第1栅绝缘层101包含第1下部膜101a和第1上部膜101b。

171.第1栅绝缘层101的第1下部膜101a包含硅(si)和氧(o)。第1下部膜101a例如为氧化硅膜。第1下部膜101a例如为氧化硅膜。第1栅绝缘层101的第1上部膜101b包含第1金属元素和氧(o)。第1上部膜101b例如为氧化铝膜。铝(al)为第1金属元素的一例。

172.第2晶体管200包含半导体层10、第2栅绝缘层201和第2栅电极202。半导体层10包含第二p型半导体区域10b、和n型半导体区域10x。第2栅绝缘层201包含第2下部膜201a和第2上部膜201b。

173.第5实施方式的第2晶体管200,其第2栅绝缘层201包含第2下部膜201a和第2上部

膜201b,在这一点上与第3实施方式的第2晶体管200不同。

174.第2栅绝缘层201包含硅(si)和氧(o)。第2栅绝缘层201的第2下部膜201a例如为氧化硅膜。第2栅绝缘层201的第2上部膜201b包含与第1金属元素不同的第2金属元素和氧(o)。第2上部膜201b例如为氧化铪膜。铪(hf)为第2金属元素的一例。

175.第1晶体管100的第1栅绝缘层101的厚度比第2晶体管200的第2栅绝缘层201的厚度厚。

176.图11(a)~(d)为第5实施方式的半导体装置的制造方法的说明图。

177.首先,准备半导体层10(图11(a))。半导体层10包含第一p型半导体区域10a和第二p型半导体区域10b。

178.接着,在半导体层10的第一p型半导体区域10a之上形成氧化铝膜12(图11(b))。氧化铝膜12为第1膜的一例。氧化铝膜12最终成为第1上部膜101b。铝(al)为第1金属元素的一例。

179.第1膜具有第1厚度(图11(b)中的d1)。氧化铝膜12具有第1厚度d1。

180.接着,在半导体层10的第二p型半导体区域10b之上形成氧化铪膜18。氧化铪膜18为第4膜的一例。氧化铪膜18选择性地形成于第二p型半导体区域10b之上。氧化铪膜18最终成为第2上部膜201b。

181.第4膜包含与第1金属元素不同的第2金属元素和氧(o)。铪(hf)为第2金属元素的一例。

182.第4膜具有第4厚度(图11(c)、图11(d)中的d4)。氧化铪膜18具有第4厚度d4。

183.再者,也可以在形成第1膜之前形成第4膜。例如也可以通过在形成氧化铝膜12之前形成氧化铪膜18来制造图11(c)所示的结构。

184.接着,利用自由基氧化在半导体层10之上形成氧化硅膜14(图11(d))。氧化硅膜14形成于第一p型半导体区域10a之上。氧化硅膜14形成于第二p型半导体区域10b之上。

185.通过利用自由基氧化将半导体层10氧化从而形成氧化硅膜14。氧化硅膜14为第2膜的一例。

186.第一p型半导体区域10a之上的氧化硅膜14最终成为第1下部膜101a。另外,第二p型半导体区域10b之上的氧化硅膜14最终成为第2下部膜201a。

187.第一p型半导体区域10a与氧化铝膜12之间的氧化硅膜14的第2厚度(图11(d)中的d2)比氧化铝膜12的第1厚度d1厚。第二p型半导体区域10b之上的氧化硅膜14的第3厚度(图11(d)中的d3)比氧化硅膜14的第2厚度d2薄。第二p型半导体区域10b之上的氧化硅膜14的第3厚度d3比氧化铪膜18的第4厚度d4厚。

188.第一p型半导体区域10a之上的氧化硅膜14因增速氧化而变得比第二p型半导体区域10b之上的氧化硅膜14厚。

189.增速氧化的程度根据在自由基氧化之前形成于半导体层10之上的膜中所包含的金属元素的种类而不同。例如,在膜包含铝(al)的情况下,与膜包含铪(hf)的情况相比,增速氧化被促进。另外,例如,在膜包含铪(hf)的情况下,与膜包含锆(zr)的情况相比,增速氧化被促进。另外,例如,在膜包含锆(zr)的情况下,与膜包含钛(ti)的情况相比,增速氧化被促进。

190.增速氧化的程度根据在自由基氧化之前形成于半导体层10之上的膜的种类而不

同。例如,在膜为氧化铝膜的情况下,与膜为氧化铪膜的情况相比,增速氧化被促进。另外,例如,在膜为氧化铪膜的情况下,与膜为氧化锆膜的情况相比,增速氧化被促进。另外,例如,在膜为氧化锆膜的情况下,与膜为氧化钛膜的情况相比,增速氧化被促进。

191.在第5实施方式的半导体装置的制造方法中,通过第1膜为氧化铝膜12、第4膜为氧化铪膜18,第一p型半导体区域10a的增速氧化与第二p型半导体区域10b的增速氧化相比被促进。因此,第一p型半导体区域10a之上的氧化硅膜14变得比第二p型半导体区域10b之上的氧化硅膜14厚。

192.其后,通过采用公知的工艺技术形成第1栅电极102、第2栅电极202以及n型半导体区域10x,能够制造出图10所示的半导体装置。

193.以上,根据第5实施方式的半导体装置的制造方法,能够将半导体层在低温下氧化从而在半导体层之上形成厚度不同的氧化膜。

194.(第6实施方式)

195.第6实施方式的半导体装置的制造方法,在第2区域之上也形成第1膜,第1膜的在第2区域之上的厚度与第1膜的在第1区域之上的厚度不同,在上述点上与第3实施方式的半导体装置的制造方法不同。以下,对于与第3实施方式重复的内容,有时省略一部分记述。

196.图12是利用第6实施方式的半导体装置的制造方法制造的半导体装置的示意截面图。半导体装置具备第1晶体管100和第2晶体管200。第1晶体管100和第2晶体管200为mosfet。

197.第1晶体管100包含半导体层10、第1栅绝缘层101和第1栅电极102。半导体层10包含第一p型半导体区域10a、和n型半导体区域10x。第1栅绝缘层101包含第1下部膜101a和第1上部膜101b。

198.第1栅绝缘层101的第1下部膜101a包含硅(si)和氧(o)。第1下部膜101a例如为氧化硅膜。第1下部膜101a例如为氧化硅膜。第1栅绝缘层101的第1上部膜101b包含第1金属元素和氧(o)。第1上部膜101b例如为氧化铝膜。铝(al)为第1金属元素的一例。

199.第2晶体管200包含半导体层10、第2栅绝缘层201和第2栅电极202。半导体层10包含第二p型半导体区域10b、和n型半导体区域10x。第2栅绝缘层201包含第2下部膜201a和第2上部膜201b。

200.第6实施方式的第2晶体管200,其第2栅绝缘层201包含第2下部膜201a和第2上部膜201b,在这一点上与第3实施方式的第2晶体管200不同。

201.第2栅绝缘层201包含硅(si)和氧(o)。第2栅绝缘层201的第2下部膜201a例如为氧化硅膜。第2栅绝缘层201的第2上部膜201b包含第1金属元素和氧(o)。第2上部膜201b例如为氧化铝膜。铝(al)为第1金属元素的一例。

202.第1晶体管100的第1栅绝缘层101的厚度比第2晶体管200的第2栅绝缘层201的厚度厚。第1晶体管100的第1上部膜101b的厚度与第2晶体管200的第2上部膜201b的厚度不同。第1晶体管100的第1上部膜101b的厚度比第2晶体管200的第2上部膜201b的厚度薄。

203.图13(a)~(d)是第6实施方式的半导体装置的制造方法的说明图。

204.首先,准备半导体层10(图13(a))。半导体层10包含第一p型半导体区域10a和第二p型半导体区域10b。

205.接着,在半导体层10的第二p型半导体区域10b之上选择性地形成氧化铝膜12(图

13(b))。

206.接着,在半导体层10的第一p型半导体区域10a和第二p型半导体区域10b之上形成氧化铝膜12(图13(c))。在结果上,第二p型半导体区域10b之上的氧化铝膜12的厚度(图13(b)中的d1’)变得比第一p型半导体区域10a之上的氧化铝膜12的厚度(图13(b)中的d1)厚。

207.氧化铝膜12为第1膜的一例。第一p型半导体区域10a之上的氧化铝膜12最终成为第1上部膜101b。第二p型半导体区域10b之上的氧化铝膜12最终成为第2上部膜201b。铝(al)为第1金属元素的一例。

208.接着,利用自由基氧化在半导体层10之上形成氧化硅膜14(图13(d))。氧化硅膜14形成于第一p型半导体区域10a之上。氧化硅膜14形成于第二p型半导体区域10b之上。

209.通过利用自由基氧化将半导体层10氧化从而形成氧化硅膜14。氧化硅膜14为第2膜的一例。

210.第一p型半导体区域10a之上的氧化硅膜14最终成为第1下部膜101a。另外,第二p型半导体区域10b之上的氧化硅膜14最终成为第2下部膜201a。

211.第一p型半导体区域10a与氧化铝膜12之间的氧化硅膜14的第2厚度(图13(d)中的d2)比氧化铝膜12的第1厚度d1厚。第二p型半导体区域10b之上的氧化硅膜14的第3厚度(图13(d)中的d3)比氧化硅膜14的第2厚度d2薄。

212.第一p型半导体区域10a之上的氧化硅膜14因增速氧化而变得比第二p型半导体区域10b之上的氧化硅膜14厚。

213.增速氧化的程度根据形成于半导体层10之上的第1膜的厚度而不同。例如,若第1膜变得比规定的厚度厚,则增速氧化被抑制。该情况下的规定的厚度例如为5nm。另外,例如,若第1膜变得比规定的厚度薄,则增速氧化被抑制。该情况下的规定的厚度例如为1nm。

214.根据第6实施方式的半导体装置的制造方法,通过使第二p型半导体区域10b之上的氧化铝膜12的厚度比第一p型半导体区域10a之上的氧化铝膜12的厚度厚,增速氧化被抑制。因此,第一p型半导体区域10a之上的氧化硅膜14变得比第二p型半导体区域10b之上的氧化硅膜14厚。

215.其后,通过采用公知的工艺技术形成第1栅电极102、第2栅电极202和n型半导体区域10x,能够制造出图12所示的半导体装置。

216.以上,根据第6实施方式的半导体装置的制造方法,能够将半导体层在低温下氧化从而在半导体层之上形成厚度不同的氧化膜。

217.在第3实施方式~第6实施方式中,以形成不同的厚度的栅绝缘层的情况为例进行了说明,但是,例如在形成不同的厚度的电容绝缘层的情况等的、在同一半导体层之上形成不同的厚度的氧化膜的其他的情况下也能够应用本发明的半导体装置的制造方法。

218.以上,对本发明的好几个实施方式进行了说明,但这些实施方式是作为例子而示出的,并不意图限定发明的范围。这些新的实施方式能够以其他的各种方式来实施,能够在不脱离发明的要旨的范围内进行各种的省略、置换、变更。例如,也可以将一实施方式的构成要素置换或变更为其他的实施方式的构成要素。这些实施方式及其变形包含在发明的范围、要旨中,并且包含在权利要求书所记载的发明及其均等的范围内。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。