1.本发明属于半导体制造领域,尤其涉及一种图像传感器及其形成方法。

背景技术:

2.cmos图像传感器(cmos image sensor, cis)是将光学图像转化为电信号的半导体器件。cis包括用于感光的光电二极管(photodiode, pd)和用于将所感测的光处理为电信号的逻辑电路。

3.现有半导体工艺中,一般先在基底表面形成用于光刻的对准标记(例如单独的对准标记,或者在有源区掩模中带有对准标记图形),作为起始步骤,然后再进行其他步骤。但cis是对于或者其他需要在有源区形成之前进行外延的工艺,由于外延完成之后,浅层的对准标记会因为平坦化处理过程而受到影响,导致对准信号衰减或者消失。

4.为解决在有源区形成之前进行外延的半导体工艺中的对准问题,可以先在对准区域形成浅沟槽并填充介质层作为对准标记,再在器件区域形成深沟槽并外延,然后在外延层中形成有源区,虽然对准标记不会因为外延之后的平坦化处理过程而受到影响,但是该方案的缺点是增加了浅沟槽光刻刻蚀步骤,增加了嵌套对准的误差;并且由于对准标记与基底背面距离较远,进行背面工艺时对准信号较弱,无法应用于需要进行背面处理的半导体工艺,例如背照式图像传感器工艺中。

技术实现要素:

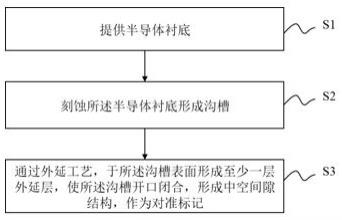

5.基于现有技术存在的问题,本发明提供了一种图像传感器的形成方法,包括:提供半导体衬底;刻蚀所述半导体衬底形成沟槽;通过外延工艺,于所述沟槽表面形成至少一层外延层,使所述沟槽开口闭合,形成中空间隙结构,作为对准标记。

6.可选的,所述中空间隙结构作为图像传感器背面工艺过程中的对准标记。

7.可选的,所述刻蚀所述半导体衬底形成沟槽包括:定义出像素区域和对准区域;于所述半导体衬底正面形成图形化的掩膜层;刻蚀所述像素区域和所述对准区域,分布于所述像素区域和所述对准区形成沟槽。

8.可选的,所述通过外延工艺,于所述沟槽表面形成至少一层外延层,使所述沟槽开口闭合,形成中空间隙结构,作为对准标记包括:通过外延工艺,于所述像素区域和所述对准区域的沟槽表面形成至少一层外延层,形成侧向pn结,并使所述像素区域和所述对准区域的沟槽开口闭合,形成中空间隙结构;其中,所述对准区域的中空间隙结构作为对准标记;所述像素区域的中空间隙结构用于隔离所述像素区域的感光单元。

9.可选的,所述通过外延工艺,于所述像素区域和所述对准区域的沟槽表面形成至少一层外延层包括:在去除所述掩膜层后,于所述像素区域和所述对准区域的沟槽表面,以及所述半导体衬底表面形成第一外延层;于所述第一外延层表面形成第二外延层;于所述半导体衬底上形成第三外延层,使使所述像素区域和所述对准区域的沟槽开口闭合,形成中空间隙结构。

10.可选的,所述方法还包括:对所述第三外延层进行平坦化处理;于所述第三外延层上形成晶体管。

11.可选的,所述方法还包括:于所述半导体衬底背面形成滤光片和微透镜。

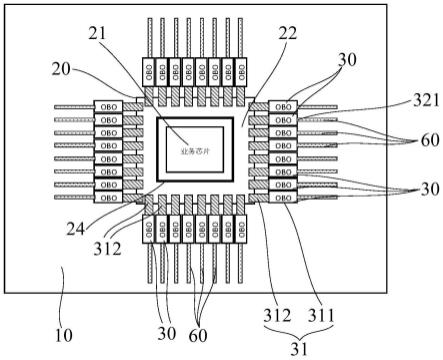

12.本发明还提供了一种通过上述方法形成的图形传感器。

13.与现有技术相比,本发明实施例具有以下有益效果:本发明实施例在像素区域和对准区域同时刻蚀形成沟槽,在对准区域的沟槽内通过至少一次外延工艺,使沟槽的开口封闭,形成中空间隙结构,作为图像传感器的背面工艺过程中的对准标记。具体的,本发明实施例具有如下优点:(1)无需额外增加光刻步骤,无需增加对准误差;(2)通过探测中空间隙结构的边沿即可获取对准信号,该方法获得的信号清晰,且精度高。

附图说明

14.本发明附图构成本说明书的一部分、用于进一步理解本发明,附图示出了本发明的实施例,并与说明书一起用来说明本发明的原理。

15.图1为本发明一实施例的一种图像传感器的形成方法;图2至图6为本发明一实施例的图像传感器的形成方法过程中的截面示意图。

具体实施方式

16.以下详细说明都是例示性的,旨在对本发明提供进一步的说明。除非另有指明,本文使用的所有技术和科学术语具有与本发明所属技术领域的普通技术人员通常理解的相同含义。

17.需要注意的是,这里所使用的术语仅是为了描述具体实施例,而非意图限制根据本发明的示例性实施例。如在这里所使用的,除非上下文另外明确指出,否则单数形式也意图包括复数形式,此外,还应当理解的是,当在本说明书中使用属于“包含”和/或“包括”时,其指明存在特征、步骤、操作、器件、组件和/或它们的组合。

18.图1为本发明一实施例的一种图像传感器的形成方法。该方法包括:步骤s1:提供半导体衬底;步骤s2:刻蚀所述半导体衬底形成沟槽;步骤s3:通过外延工艺,于所述沟槽表面形成至少一层外延层,使所述沟槽开口闭合,形成中空间隙结构,作为对准标记。

19.以下结合附图2至图6对图1的图像传感器的形成方法进行详细描述。

20.参考图2,提供半导体衬底11;半导体衬底11可以是掺杂或未掺杂的半导体材料,诸如硅、锗、硅锗、绝缘体上锗硅(sgoi)或其组合。半导体衬底11可以包括多层外延层的衬底。作为示例说明,在该实施例中,半导体衬底11可以在硅晶圆111上形成外延层112、外延层113、外延层114。其中,外延层112可以是p型外延层;外延层113可以是低掺杂的p型缓冲层;外延层114可以是n型外延层;外延层114可以用于形成感光单元,即光电二极管的n型区域。

21.参考图3至图5,刻蚀半导体衬底11形成沟槽130。可选的,刻蚀半导体衬底11形成沟槽130可以包括:定义出像素区域和对准区域;于半导体衬底11正面形成图形化的掩膜层

12(如图3);刻蚀像素区域和对准区域,分布于像素区域和对准区形成沟槽130(如图4)。像素区域的沟槽130可以将像素单元互相分离;即将光电二极管的n区域相互分离。如图5,可以将掩膜层12去除。可选的,掩膜层12可以为氮化硅、氧化硅、氮氧化硅中的一种或多种组合。可选的,掩膜层12可以光阻材料。

22.参考图6,通过外延工艺,于沟槽12表面形成至少一层外延层13,使沟槽12开口闭合,形成中空间隙结构14,作为对准标记。

23.具体的,通过外延工艺,于像素区域和对准区域的沟槽12表面和半导体衬底11表面形成至少一层外延层13,形成侧向pn结,并使像素区域和对准区域的沟槽12开口闭合,形成侧向pn结,并使像素区域和对准区域的沟槽12开口闭合,形成中空间隙结构14。仅作为示例说明,侧向pn结可以用于相邻的感光单元之间的电性隔离。像素区域的中空间隙结构14可以用于光学隔离像素区域的感光单元。光线照射到中空间隙结构14上,可以在中空间隙结构14的界面发生全反射,从而避免相邻的感光单元之间的光学串扰。对准区域的中空间隙结构14可以作为对准标记。可选的,对准区域的中空间隙结构14可以作为图像传感器背面工艺过程中的对准标记。通过探测中空间隙结构14的边沿即可获取对准信号,且信号清晰,精度高。

24.可选的,通过外延工艺,于像素区域和对准区域的沟槽表面形成至少一层外延层包括:在去除掩膜层12后,于像素区域和对准区域的沟槽130表面,以及半导体衬底11表面形成第一外延层131;于第一外延层131表面形成第二外延层132;于半导体衬底11上形成第三外延层133,使像素区域和对准区域的沟槽开口闭合,形成中空间隙结构14。

25.可选的,第一外延层131可以为本征型外延层作为缓冲层、第二外延层132可以为p型外延层。外延层114、第一外延层131和第二外延层132可以形成侧向pn结。

26.进一步的,图1的图像传感器的形成方法还包括:对第三外延层133进行平坦化处理;于第三外延层133上形成晶体管,例如,转移晶体管、复位晶体管等(图中未示出)。

27.进一步的,图1的图像传感器的形成方法还包括:于半导体衬底11背面形成滤光片和微透镜。

28.对于本领域技术人员而言,显然本发明不限于上述示范性实施例的细节,而且在不背离本发明的精神或基本特征的情况下,能够以其他的具体形式实现本发明。因此,无论如何来看,均应将实施例看作是示范性的,而且是非限制性的。此外,明显的,“包括”一词不排除其他元素和步骤,并且措辞“一个”不排除复数。第一,第二等词语用来表示名称,而并不表示任何特定的顺序。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。